最初在纸上画原理图时,通常将其放在足以铺满一张大绘图桌的单张纸上,然后用一台专用大幅面复印机复印。但时过境迁,现在原理图在台式个人计算机上绘制,存储在服务器上,并在小型激光打印机上打印。

这种改变意味着如果在多张原理图表上进行展示,即使是简单的设计也可以更容易显示和理解。即使设计不是特别复杂,在多张表上进行组织也有很多优点。

举例来说,该设计可以包括各种模块化元素。如果将所述模块作为单个文档进行维护,多名设计人员可以同时处理一个项目。将设计分解为逻辑模块大大提高了设计的可读性,这对那些随后需要在该产品的生命周期中解读原理图的人来说是一个重要的考虑因素。另一个优点是,在多张表上构建元器件较少的设计时,可采用小幅面打印,例如采用激光打印机打印。

如果您计划在多张表单上进行设计,则需要做出两项决定:

您的选择将根据每个项目的大小和类型以及您的个人喜好而有所不同。

扁平化或层次化设计

如上文所述,作为设计人员,您需要决定如何组织原理图表以及如何在原理图表之间建立连接。这不是独立的决定,因为在选择结构时,您同时还需要考虑如何创建原理图表之间的连接。

有两种构建多表设计的方法:扁平化或层次化。

用于将子表单连接到父表单的技术对于扁平化和层次化设计是相同的 - 通过各自创建连接的方式以确定它是扁平化设计还是层次化设计。

扁平化设计

您可以将扁平化设计想象成一个大的原理图表被切割成多个较小的表单——扁平化设计中的所有表单均在同一级别出现。扁平化设计中的连接直接从任何表创建到另一张表——这种连接类型称为水平连接。

扁平化设计中也可选用顶层图表。如果包含一张顶层图表,设计中的每张图表就会带有一个sheet symbol,但不能包含任何接线。扁平化设计中的图表数量不限。

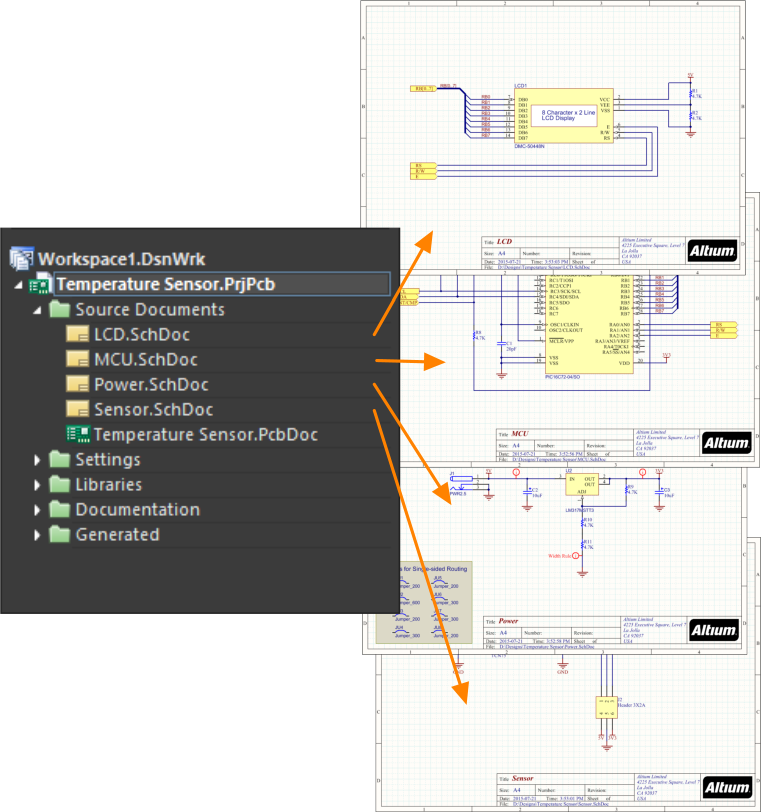

左侧的扁平化设计没有顶层图表,右侧的扁平化设计有一张顶层图表。请注意,顶层图表没有接线,只显示了设计中的图表。

左侧的扁平化设计没有顶层图表,右侧的扁平化设计有一张顶层图表。请注意,顶层图表没有接线,只显示了设计中的图表。

上面的两个图像显示了扁平化设计,左侧图像没有顶层图表,右侧图像有顶层图表。对于只有两张或三张原理图表的小型设计,您可能会决定顶层图表不添加任何值。一旦图表数量增加,顶层图表可以帮助读者通过图表上的逻辑块(图表符)排列方式了解电路设计的功能。因为没有层次结构,所以设计中的所有图表均在Projects面板中的同一级别出现。

层次化设计

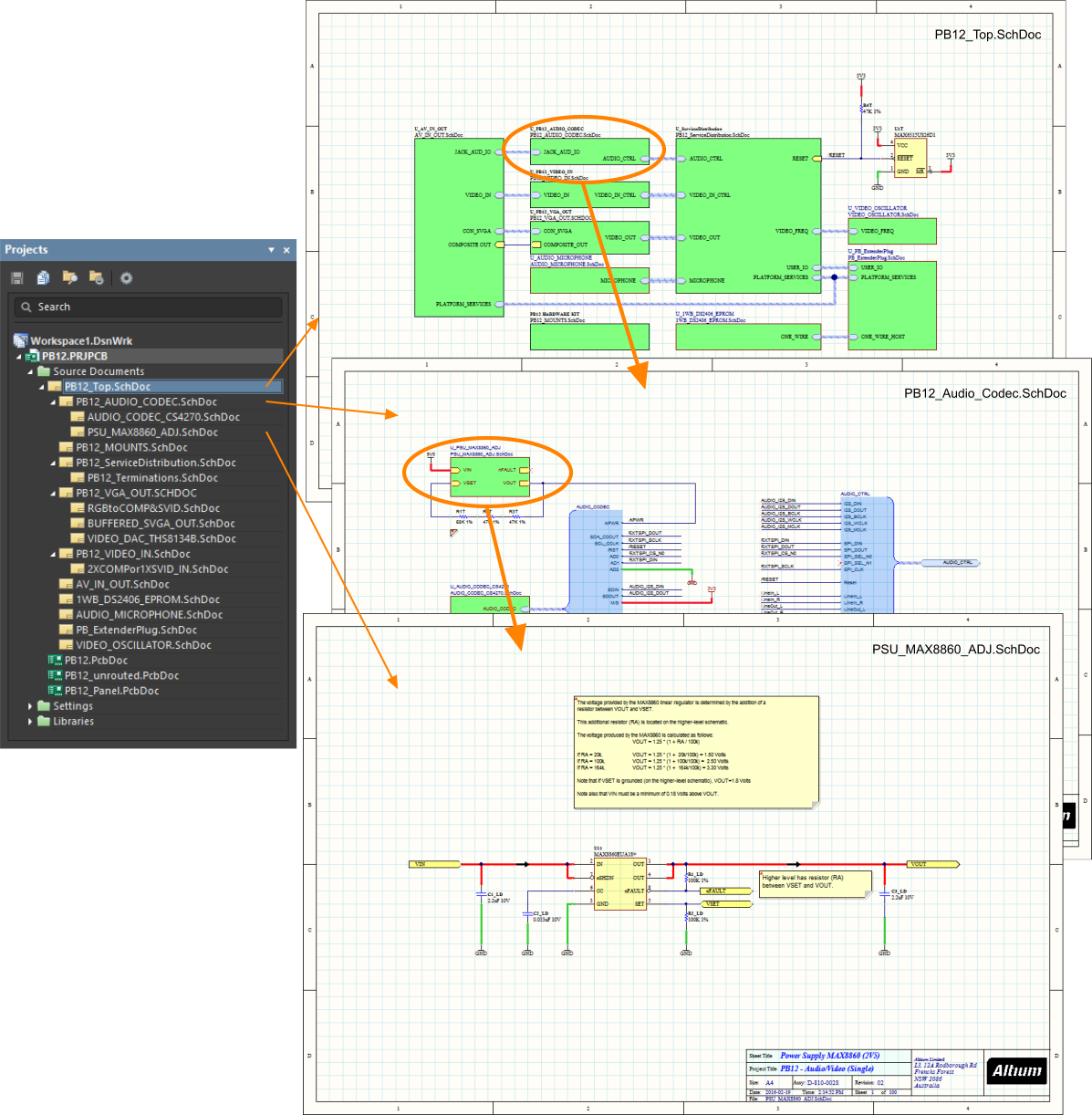

层次化设计采用图表符创建图表之间的父-子关系,连接是通过图表符中的Sheet Entry,而不是直接从一张图表上的端口到另一张图表上的端口创建的。

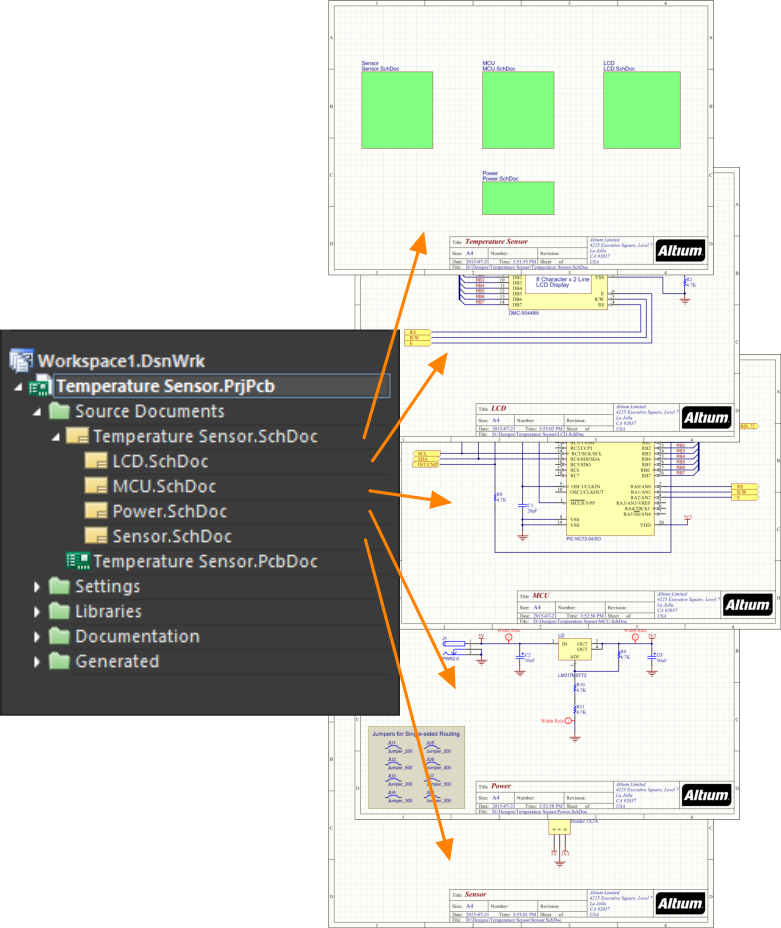

正如在扁平化设计中一样,通过在图表符中定义其文件名来标识子表。在层次化设计中,子表也可以包含图表符,引用较低级别的图表,从而在层次结构中创建另一个级别。下图显示了层次化设计,层次结构中有3个层级。

在层次化设计中,树形结构由图表符创建的父子关系确定。设计进行编译后,便可得出相应关系并进行更新。

在层次化设计中,树形结构由图表符创建的父子关系确定。设计进行编译后,便可得出相应关系并进行更新。

在层次化设计中,子表上的信号通过Port输出图表,该端口向上连接到父表上的匹配 Sheet Entry。父表包含将信号传送到另一个图表符中的Sheet Entry,然后下行至第二张子表上的匹配Port的接线,如下图所示。

这种亲-子图表结构可以被定义为任意深度,层次化设计中的图表数量不限。

图表之间的连接由网络标识符范围确定。这在Options for Project对话框的Options选项卡中设置。要了解有关创建连接的更多信息,请参考文章 Creating Connectivity。请注意,网络标识符范围包含Automatic选项,除非您有特殊连接要求,否则此选项是一个不错的选择。

层次化设计的另一个优点是为实现复杂的设计复用系统提供了平台。根据数据的存储方式,该系统有两种实现方式:基于文件或基于Altium数据保险库。

- 基于文件的系统称为器件图表,您可以将器件图表库中的现有原理图直接放置到正在创建的设计中。要了解有关器件图表的更多信息,请参考文章Device Sheets。

- 基于数据保险库的系统称为托管图表,您可以将Altium数据保险库中的现有原理图直接放置到正在创建的设计中。要了解有关托管图表的更多信息,请参考文章Managed Sheets。

创建多表单设计

只要向项目中添加第二个原理图表,就可以创建多表单设计。如果您打算在没有顶层图表的情况下创建扁平化设计,只需向项目中添加原理图表,并确认网络标识符范围设置正确。

如果要使用图表符来引用较低级别的图表,则可以放置图表符并进行手动编辑以正确引用较低级别的图表,或者可以使用各种内置命令来提供帮助,如下文所述。

引用子表

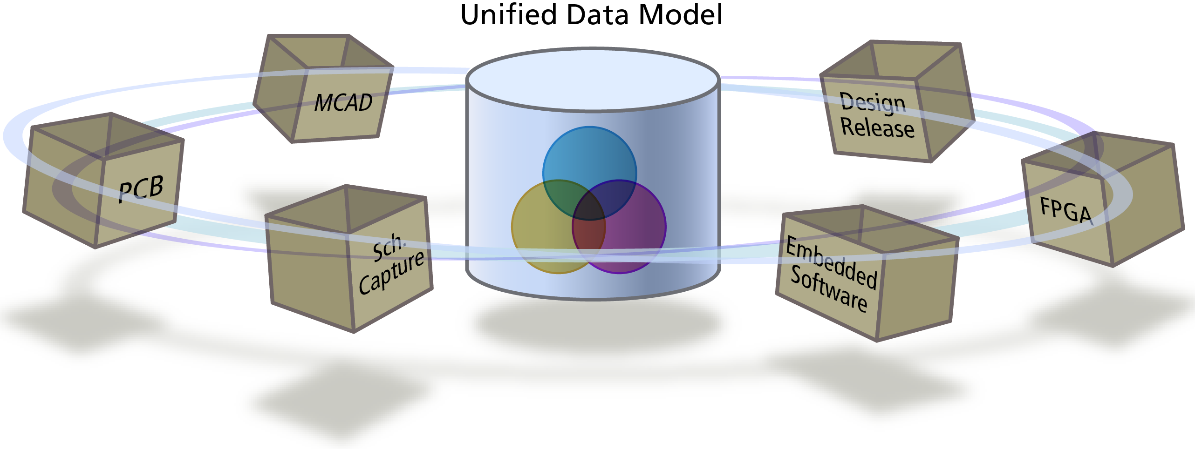

图表符的文件名属性引用较低级别的图表。请注意,该字段仅应包含原理图文件名,而不包含该文件位置的路径(该位置数据实际存储在项目文件中)。

文件名属性将此图表符链接到子原理图表。

文件名属性将此图表符链接到子原理图表。

请注意,子原理图不必与父原理图一样存储在相同的文件夹中。如果子原理图存储在父原理图存储文件夹下面的文件夹中,则使用相对文件引用(如果存储在另一个位置,则使用绝对文件引用)。在重新放置此项目中的文件时要小心,或使用项目包程序压缩文件,并按照原样解决文件路径。

创建层次结构

软件包含许多命令,可以让您快速高效地构建多文档层次结构。您使用的命令将取决于您的个人设计方法,可以大致分为自上而下或自下而上。这些命令可以更高效地手动创建层次结构,因为它们处理在此过程中需要的所有元素,例如添加Sheet Entry,创建新的原理图表,放置Port等等。

使用此命令以自上而下的方式构建层次结构:

- Design » Create Sheet From Sheet Symbol – 使用此命令在指定图表符下面创建新的原理图表。将Port添加到子表以匹配Sheet Symbol中找到的任何Sheet Entry。如果您还没有将所有Sheet Entry纳入Sheet Symbol中,请不要担心。如果随着时间的推移添加了更多Sheet Entry,您可以重新同步Sheet Entry和Port,如下文所述。

使用此命令以自下而上的方式构建层次结构:

- Design » Create Sheet Symbol From Sheet or HDL – 使用此命令从指定原理图表(或VHDL或Verilog文件)创建图表符。要使用此命令,首先切换到将保存新Sheet Symbol的图表,然后启动该命令。Sheet Symbol将包含一个Sheet Entry,以匹配找到的每个Port。如果稍后添加或删除Port或Sheet Entry,则可以重新同步,如下文所述。

使用此命令来重新组织如何将电路放置在设计中:

- Edit » Refactor » Move Selected Sub-circuit to Different Sheet - 使用此命令将选定的元器件和接线移动到项目中的其它图表。Choose Destination Document对话框将打开,使您能够选择项目中的任何现有原理图。下面将更详细地对该命令进行说明。

如果您想知道为什么有专门的命令将元器件从一张图表移动到另一张图表,则会提供所述命令,因为标准的剪切和复制命令会自动重置每个元器件中的唯一标识符。

重构设计

Main article: Design Refactoring

设计过程通常无结构但有组织,设计人员可以同时构想设计的多个组成部分,随着想法的发展实现各个部分。这意味着最初条理清晰、布局整齐的原理图可能会变得拥挤而结构混乱。虽然可以通过剪切、复制和粘贴来重新整理原理图设计,但这并不总是最好的方法。

这是为什么呢?因为每放置一个元器件,就会分配一个唯一标识符,并且只要剪切/复制和粘贴元器件,该标识符就会自动重置。完成唯一标识符管理是为了确保设计中使用的每个唯一标识符只有一个实例,因为唯一标识符是将原理图元器件链接到PCB元器件的关键字段。如果设计没有传输到PCB编辑器,那么剪切/复制/粘贴方法就没有问题,但如果设计已经传输到PCB编辑器,那么最好使用重构工具。

将子电路移至另一张表

将一段电路从一张图表移动到另一张图表最简单的方法是选择该电路,然后运行Edit » Refactor » Move Selected Sub-circuit to Different Sheet命令(如果有选择,也可以通过右键点击菜单)。Choose Destination Document 对话框将打开,选择目标图表后点击OK选项,该图表将出现,同时子电路浮动在光标上,准备定位。

通过Move Selected Subcircuit to Different Sheet命令,可以轻松地将选定电路部分移至项目中的其他图表。

通过Move Selected Subcircuit to Different Sheet命令,可以轻松地将选定电路部分移至项目中的其他图表。

► Learn more about Design Refactoring.

使Port和Sheet Entry同步

如果您已经移动元器件和接线,作为重构设计的一部分,那么您可能还需要将子表重新同步到其Sheet Symbol,以便每个Port均具有匹配的Sheet Entry。这是通过Synchronize Sheet Entries and Ports命令完成的,该命令位于:

- Design » Synchronize Sheet Entries and Ports menu - 选择此命令分析整个设计中的所有Sheet Symbol,对话框将包含设计中每个Sheet Symbol的选项卡,符合对话框底部的Only Show unmatched sheet symbols选项。

- Right click » Sheet Symbol Actions » Synchronize Sheet Entries and Ports - 选择此命令仅分析光标下面的Sheet Symbol。

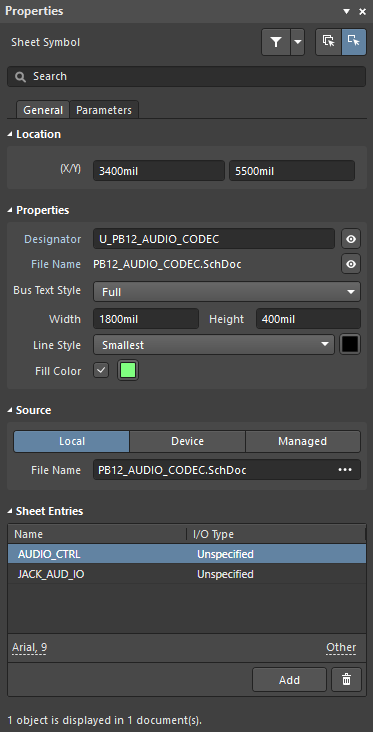

对于这两个命令,Synchronize Ports to Sheet Entries 对话框将打开。将在对话框右侧列出已经匹配的Port/Sheet Entry,在对话框左侧分两列列出不匹配的Port和Sheet Entry。

Synchronize Ports to Sheet Entrie对话框用于确保Sheet Entry与子表上的Port匹配。注意这两个选项卡,这意味着在该设计中有两个Sheet Entry/Port匹配的图表符。

关注对话框左侧显示的不匹配项,方法是在第一列中选择Sheet Entry,然后在第二列中选择正确的Port,然后点击正确的按钮更新其中一项,使它们同步(移到对话框右侧的列表中)。按钮的功能如下:

-

- 使用Sheet Entry属性,并将其推送到选定的Port。

- 使用Sheet Entry属性,并将其推送到选定的Port。

-

- 使用Port属性,并将其推送到选定的Sheet Entry。

- 使用Port属性,并将其推送到选定的Sheet Entry。

如果在左栏中选择多个Sheet Entry,软件会将每个Sheet Entry与第二栏中的相邻Port同步。如果没有相邻Port(或Sheet Entry),则会创建一个新的Port(或Sheet Entry)。

如果该工具添加了Sheet Entry或Port,则在操作完成时需要在原理图表上正确定位Sheet Entry或Port。

多通道设计

电子设计包含重复电路部分并不罕见。可能是立体声放大器,也可能是64通道调音台。Altium Designer通过称为多通道设计的功能集完全支持这种类型的设计。

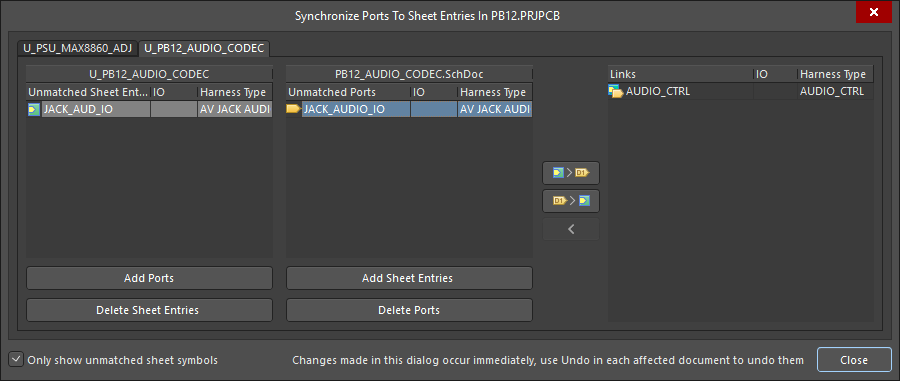

视频多路复用器的两个解码器通道采用多通道设计结构意味着解码器通道仅捕获一次。

视频多路复用器的两个解码器通道采用多通道设计结构意味着解码器通道仅捕获一次。

在多通道设计中,您可以捕获重复电路一次,然后指示软件重复所需次数。设计进行编译时,会在内存中扩展,所有元器件和连接重复所需次数,这与用户自定义通道命名方案一致。

您捕获的逻辑设计永远不会成为扁平化设计,源始终保持为多通道原理图。如果将其传输到PCB布局时,物理元器件和网络会自动按照所需次数进行步进。您可以充分利用可在原理图和PCB之间使用的标准交叉搜索和交叉选择工具。PCB编辑器中还有一个工具可以在所有其他通道中复制一个通道的布局布线,并且可以轻松移动和重新调整整个通道。

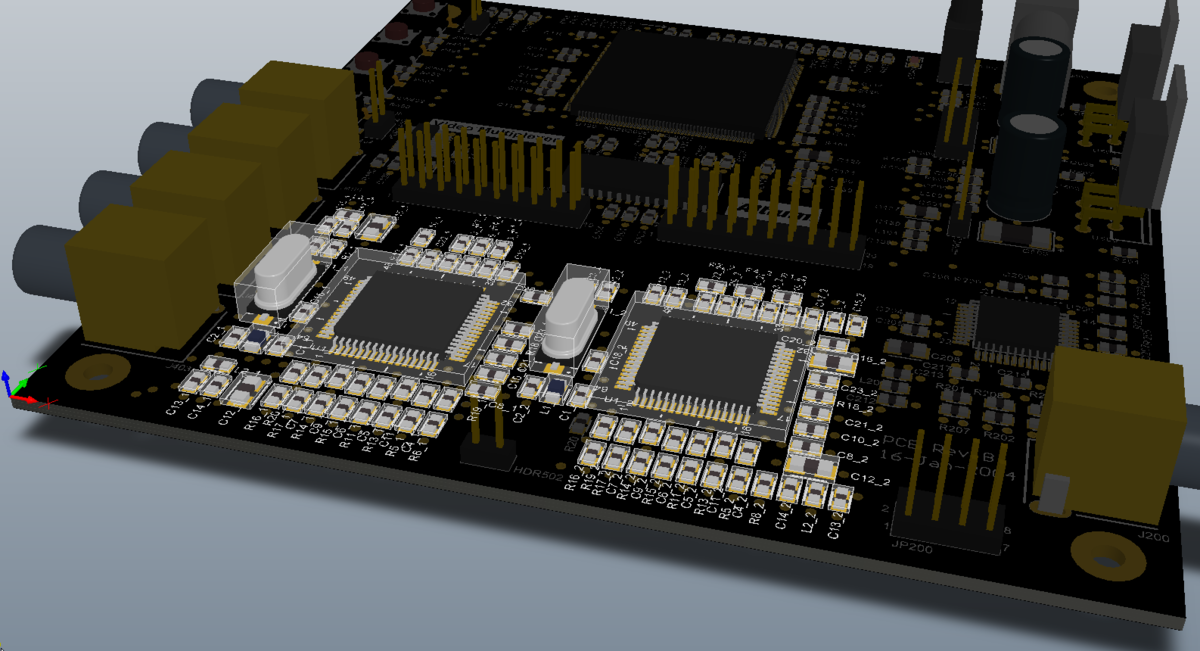

统一数据模型

了解多通道设计有助于了解设计数据的管理方式。统一数据模型(UDM)是软件的基本元素。在编译项目时,会创建一个单一的内聚模型,这是设计过程的核心所在。然后可以使用软件中的各种编辑器和服务来访问和操作模型中的数据。统一数据模型经构建能容纳来自设计方方面面的信息(包括元器件及其连接),而不是将单独的数据存储运用于各类设计领域。

统一数据模型可将所有设计数据提供给所有编辑器,并有助于提供诸如多通道设计等复杂功能。

统一数据模型可将所有设计数据提供给所有编辑器,并有助于提供诸如多通道设计等复杂功能。

统一数据模型与层次化设计系统相结合,充分发挥多通道设计功能。“通道”是图表符内的电路——此图表符下面可以是单个图表,也可以是项目结构的整个分支,包含其他子表。您还可以在通道内创建通道,在2级多通道设计中,上级通道称为Bank,较低级别的通道称为通道。

因为内存中存在这种完整的PCB结构的描述,所以只要有系统的方法来处理重复的对象,例如元器件标号和网络,就可能重复一段电路。系统命名在Options for Project对话框的Multi-Channel选项卡中进行了定义,如下文所述。

创建多通道设计

一段电路重复时,设计为多通道设计。这是在图表符级完成的,或者通过:

-

放置引用相同子原理图的多个Sheet Symbol,或

-

配置单个Sheet Symbol,以重复引用的子电路图所需次数。

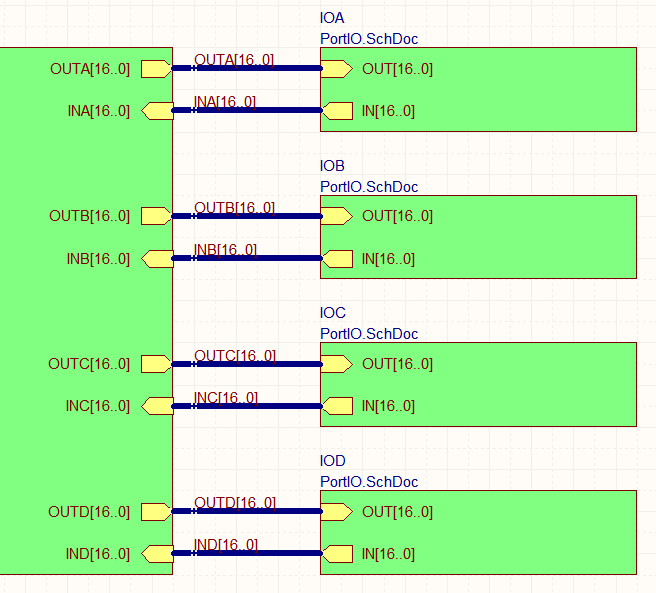

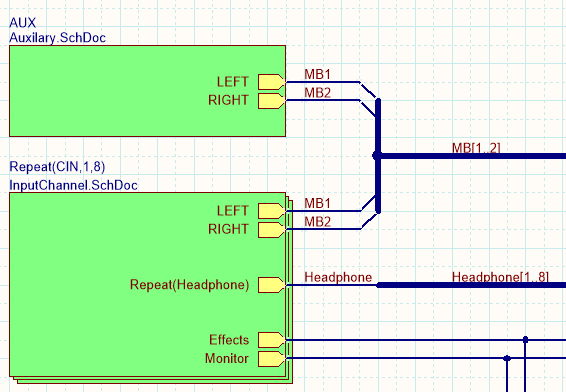

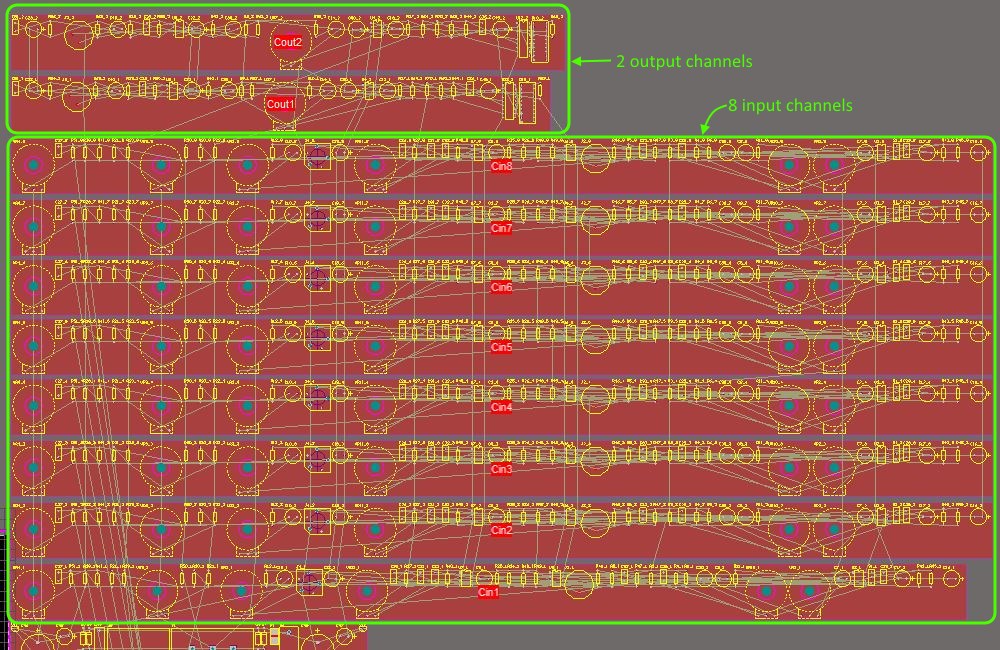

左侧的4个Sheet Symbol均引用同一张子表(PortIO.SchDoc)。按重复关键字,右侧的InputChannel.SchDoc重复8次,OutputChannel.SchDoc重复2次。

左侧的4个Sheet Symbol均引用同一张子表(PortIO.SchDoc)。按重复关键字,右侧的InputChannel.SchDoc重复8次,OutputChannel.SchDoc重复2次。

这两种创建多通道设计的方法如上图所示。左图中有四个Sheet Symbols引用同一张子表(PortIO.SchDoc)。按图表符标号字段中的重复关键字,右图中InputChannel.SchDoc重复8次,OutputChannel.SchDoc重复2次。

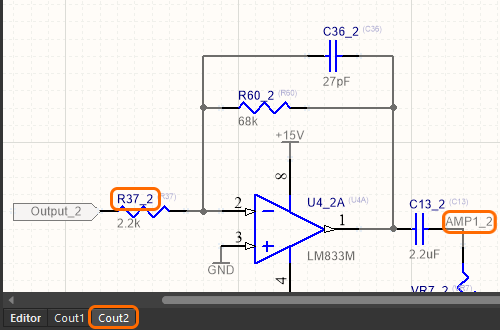

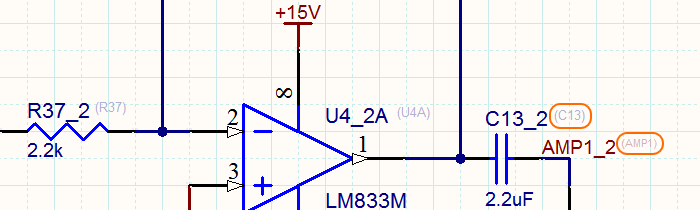

在编译项目时,通过应用标准命名方案来解决重复的元器件标号和网络名。例如,一个命名方案是为重复元器件和网络标号(Net Labels和Ports)添加通道索引,如下图中的突出部分所示。

在编译项目时,注意出现在原理图底部的选项卡。Editor选项卡包含您捕获的逻辑设计,其他选项卡(COUT1和COUT2)在项目编译完成后出现,包含将传输到PCB编辑器的物理设计。每个物理通道均有一个选项卡。

已编译的项目显示逻辑视图的选项卡以及每个通道的选项卡。注意如何管理重复标号和网络标识符。

已编译的项目显示逻辑视图的选项卡以及每个通道的选项卡。注意如何管理重复标号和网络标识符。

通道命名方案在Options for Project对话框的Multi-Channel选项卡中进行定义,请在对话框中按F1获取更多信息。

重复关键字

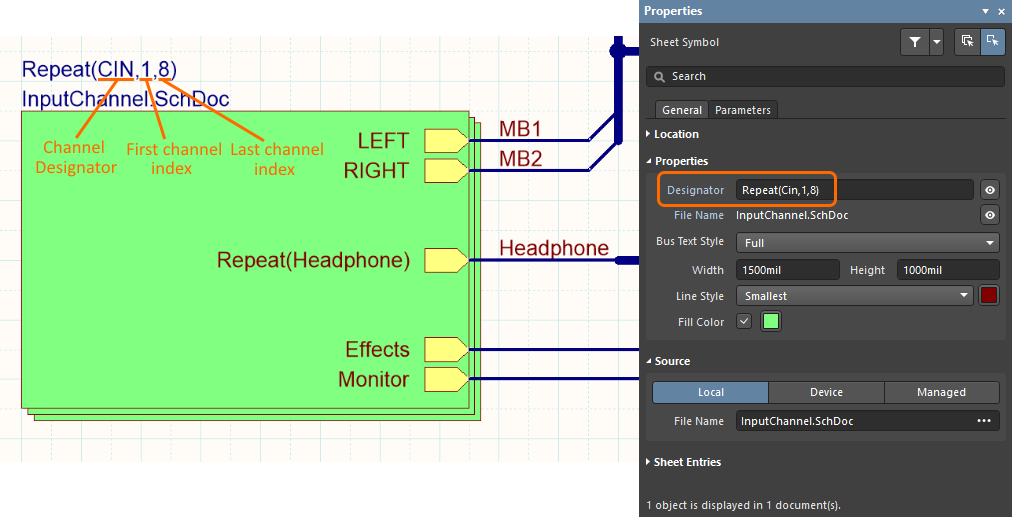

如上文所述,通过放置引用同一张子表的多个Sheet Symbol或通过在Sheet Symbol的标号字段中包含Repeat关键词来重复通道。

Repeat语句定义了通道标号和通道数量。注意Sheet Symbol如何绘制为一组堆叠符,用以表示重复通道。

Repeat语句定义了通道标号和通道数量。注意Sheet Symbol如何绘制为一组堆叠符,用以表示重复通道。

每个通道由源自Sheet Symbol Designator的通道标号标识。如果设计通过放置多个Sheet Symbol进行通道化,则通道标号是为每个Sheet Symbol定义的标号值。如果设计通过使用重复关键字进行通道化,则通道标号是由重复关键字定义的ChannelIdentifier+ChannelIndex。

使用Repeat关键字时,Designator字段的语法如下所示:

Repeat(<ChannelIdentifier>,<ChannelIndex_1>,<LastChannelIndex_n>)

注意,索引范围必须从1开始,不支持从0(零)开始。

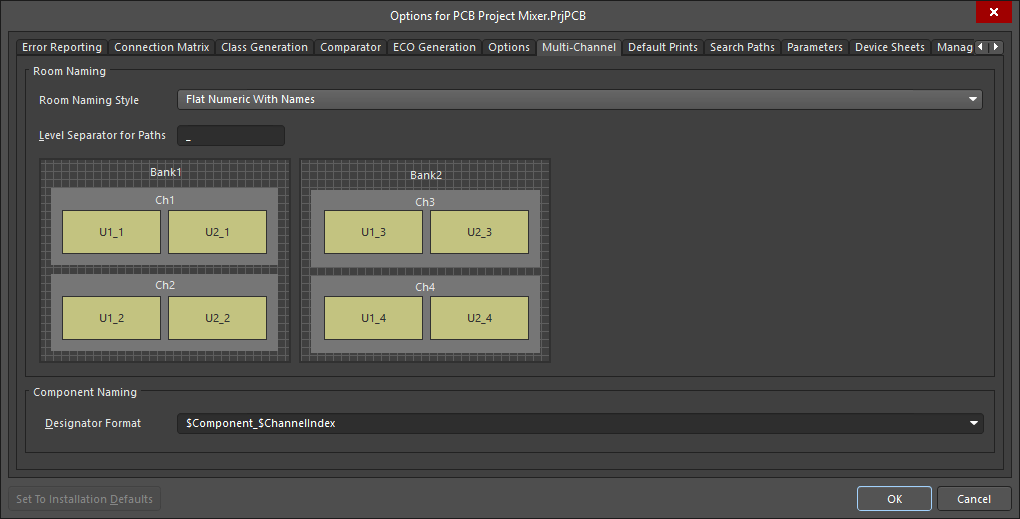

多通道命名

通过建立在软件的统一数据模型(UDM)之上传达能够捕获一次然后重复的概念——多通道设计。使用系统命名方案命名重复元器件,这在Options for Project对话框的Multi-Channel tab选项卡中进行配置,如下所示。

该对话框包含用于控制Room命名的上半部分以及用于控制Room内元器件命名的下半部分。在Room层面,有2种扁平化命名风格和3种层次化命名风格,如果设计的通道内还有通道,通常只需要选择层次化命名风格。要不然,扁平化Room命名风格更短,更易于理解。

对于元器件命名$Component$ChannelAlpha或$Component_$ChannelIndex选项将提供最短的、最容易解释的元器件名称。也可以使用可用关键词构建您自己的标号命名方案。

通过应用系统命名方案管理重复元器件,该方案在Options for Project对话框的Multi-Channel选项卡中选择。

通过应用系统命名方案管理重复元器件,该方案在Options for Project对话框的Multi-Channel选项卡中选择。

Room的作用

Room是用于限定电路板上的某个区域的PCB设计对象,可以以两种方式使用Room:

- 包含对象——如果Room像任何多边形形状对象一样放置,它实际上被创建为放置design rule。Room定义的一部分是指定必须包含在该Room内的对象——通常为元器件。当该Room移动时,Room内的所有元器件也会移动。

- 确定其它设计规则的范围——以及本身的规则,Room也可用于确定其他它设计规则的范围。举例来说,一个布线宽度设计规则定义了一类网络的布线宽度,那么优先级较高的设计规则(范围为Room)可以指定在该Room内应用于该类网络的不同宽度。

Room与多通道设计能很好的融合。根据Options for Project对话框的 Class Generation tab选项卡中的选项,设计从原理图编辑器传输到PCB编辑器时,可以自动创建Room,并为每个图表符提供一个Room。除了聚集该通道中的元器件外,Room还可用于该Room内元器件的命名。本文Multi-Channel PCB Design部分将进一步讨论Room及其在电路板设计过程中的作用。

如果您更喜欢扁平化元器件编号系统,则可以通过执行Board Level Annotation来替换系统命名方案。之所以称为Board Level Annotation,是因为元器件标号仅适用于注定要成为PCB的完整编译设计(物理设计)。

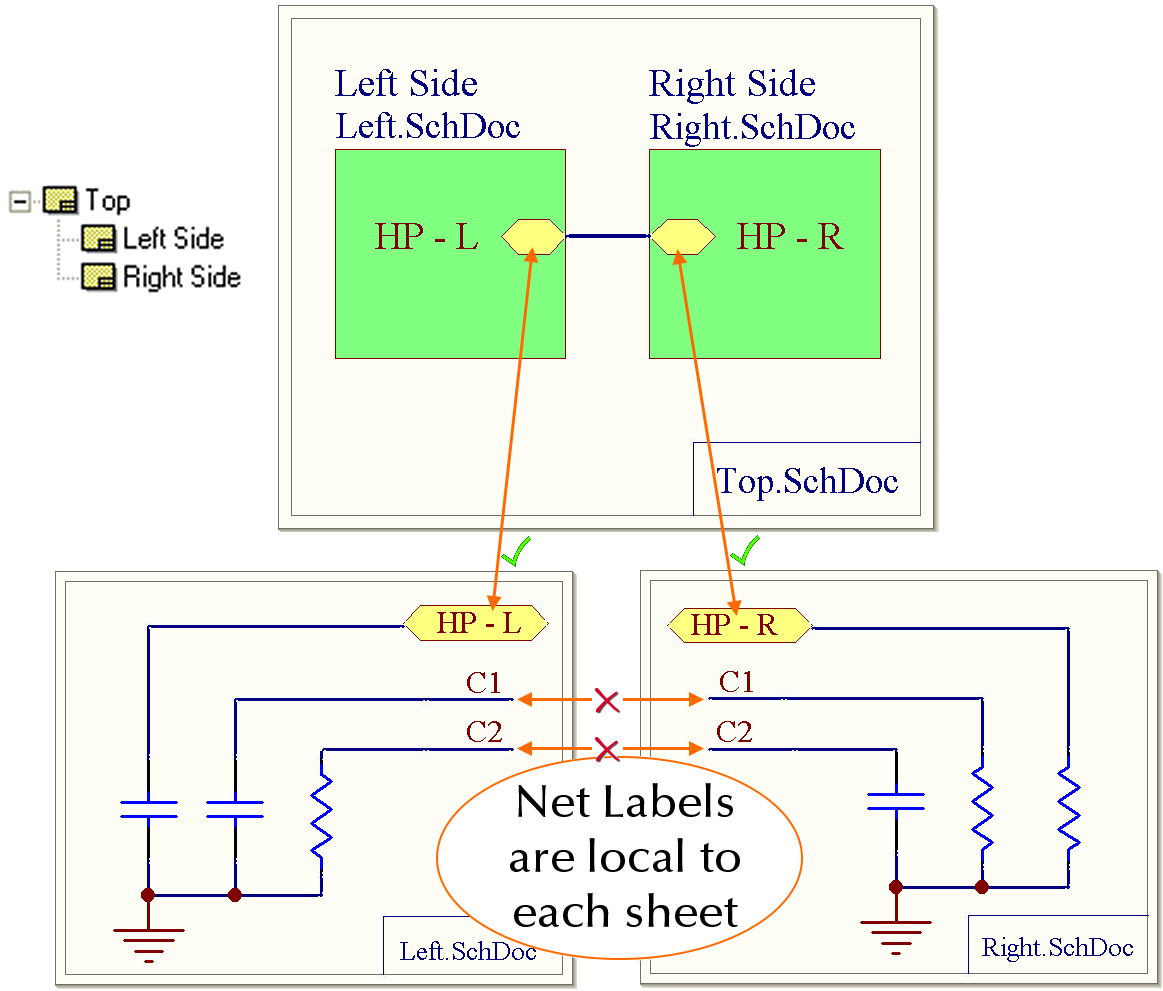

多通道设计中的连接

对于多通道设计,将网络Net Identifier Scope设置为Automatic、Hierarchical或Strict Hierarchical。多通道设计必须也是层次化设计,因为软件使用这种结构模型在编译设计时实例化内存中的通道。

软件必须支持两种不同的连接要求,以便连接到重复通道的网络,网络将是:

对此的支持程度取决于使用哪种方法定义通道(多个图表符号,或通过Repeat关键字)。 如果设计使用多个图表符号(每个通道的单个图表符号),则网络连接是明确的,由设计人员放置的布线定义。

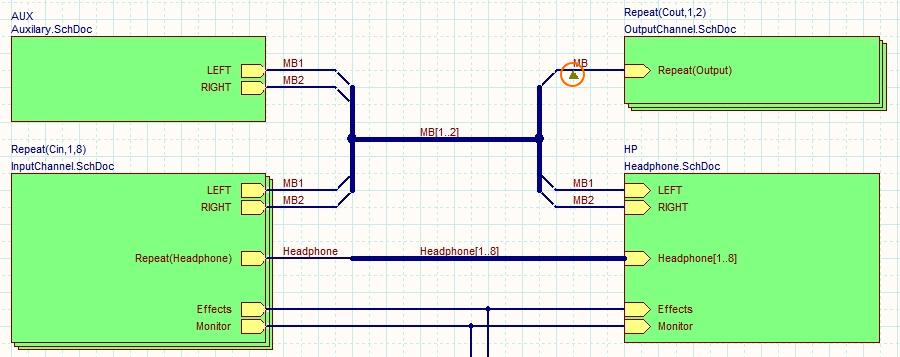

本设计使用重复关键字来创建多个通道。

本设计使用重复关键字来创建多个通道。

如果设计使用重复关键字,则以下连接约定适用。

|

将网络传递给所有通道 |

If a net needs to be available in all channels it is simply wired to a Sheet Entry, as shown for the Monitor net connected to the InputChannel.SchDoc Sheet Symbol in the image above. The nets Effects,

MB1 and MB2 will also be available on all of the channels. Nets in a bus are handled the same way, when a bus is connected to a Sheet Entry then each element in that bus is available on all of the channels. |

|

将网络传递给特定通道 |

To allocate a single net from a bus to each channel, the Repeat keyword is used in the Sheet Entry, as is shown for the Headphone bus in the image above, where the Sheet Entry has the name Repeat(Headphone). In this

case, the net Headphone1 will connect to the channel CIN1, Headphone2 will connect to channel CIN2, and so on. It is not possible to pass an individual net to just one channel if the

Repeat keyword has been used to create the channels. If this is required, you must place an individual Sheet Symbol for each channel. |

如何命名网络

每个网络基本上在PCB上只能有一个名称(一个PCB网络不能有两个名称),并且每个网络名称只应在PCB上使用一次(两个不同的PCB网络不得具有相同名称)。在编译项目时,软件会自动解析具有多个名称的网络,使每个网络只有一个名称——在多通道设计中配置命名选项非常重要,能够确保您的网络以对您有意义的方式进行标记。网络命名选项位于Options for Project对话框Options选项卡的Netlist Options部分。

在多通道设计中设置这些选项的一个好方法是启用更高级别名称优先级(Higher Level Names Take Priority)选项,并在所有连接到通道化子表单的网络上放置网络标签。

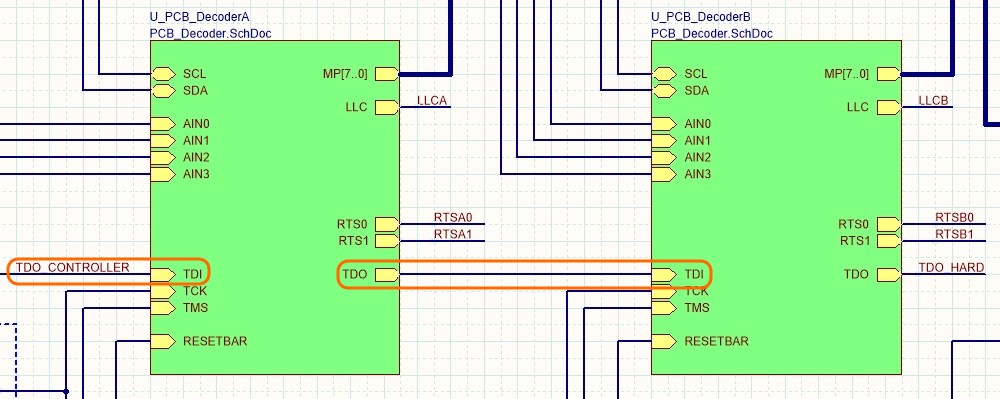

例如,请考虑下图。注意,两个Sheet Symbol均指向图表PCB_Decoder.SchDoc,因此该电路有两个通道,分别标识为U_PCB_DecoderA和U_PCB_DecoderB。

Sheet Symbol包含一个称为TDI的Sheet Entry,该Sheet Entry是JTAG边界扫描链中的测试数据输入线。来自DecoderA的TDO(测试数据输出)连接到链中的下一个器件的TDI,它位于DecoderB通道中。

两个解码器通道是通过放置两个Sheet Symbol创建的,两个Sheet Symbol均引用相同的原理图PCB_Decoder.SchDoc。

两个解码器通道是通过放置两个Sheet Symbol创建的,两个Sheet Symbol均引用相同的原理图PCB_Decoder.SchDoc。

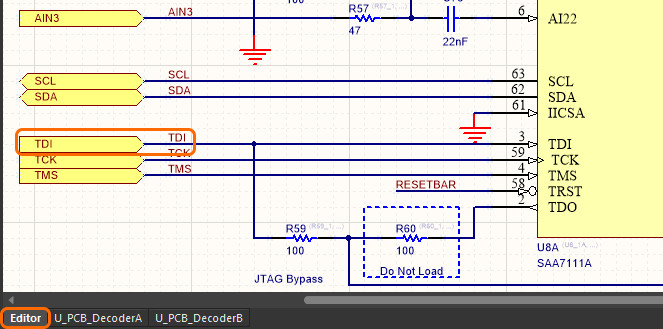

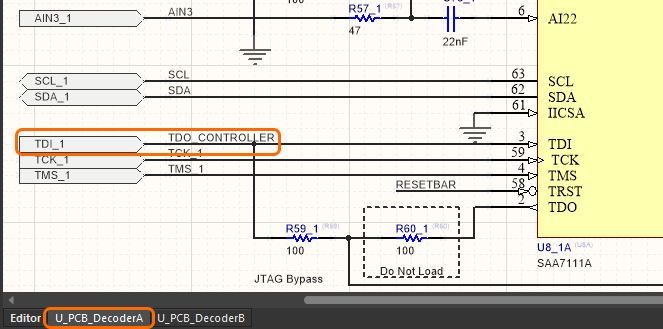

在编译项目时,通道选项卡U_PCB_DecoderA和U_PCB_DecoderB出现在原理图底部。物理设计传递给PCB编辑器时,选项卡进行显示。在下图中,捕获的解码器电路原理图在左下方的Editor选项卡中显示,随后是该原理图的两个物理通道U_PCB_DecoderA和U_PCB_DecoderB。

在原始捕获的原理图中,设计人员将网络标记为TDI(第一幅图)。注意软件如何在DecoderA选项卡(第二幅图)中应用更高级别的网络名称TDO_CONTROLLER(已在此设计中设置为具有优先级)。对于DecoderB,没有定义更高级别的名称,因此原始网络名称TDI在此通道中标识为TDI_2(第三幅图),因为这是在Options for Project对话框的Multi-Channel选项卡中定义的命名方案(元器件命名方案用于识别每个通道内的元器件和网络)。

PCB_Decoder.SchDoc原理图(捕获的原理图)位于左侧,两个通道的编译视图分别位于中间和右侧。

PCB_Decoder.SchDoc原理图(捕获的原理图)位于左侧,两个通道的编译视图分别位于中间和右侧。

显示编译的名称

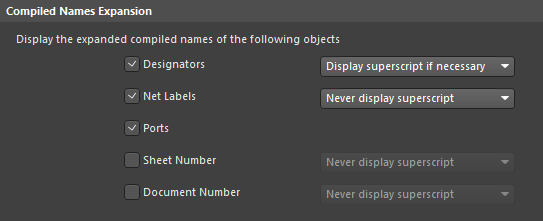

在多通道设计中追踪和分析网络可能会引起混淆,因为为了识别重复但仍然是唯一的网络,必须更改名称。为了解决这个问题,有许多选项可以控制编译对象名称的显示,包括元器件Designator、Net Label和Port。还可以选择Sheet和Document Number,这在准备好生成打印输出时很重要。

编译对象名称的显示在Preferences对话框的 Schematic - Compiler页面中进行配置,如下图所示。

配置编译对象名称的显示,上标对元器件标号很有帮助。

配置编译对象名称的显示,上标对元器件标号很有帮助。

通常情况下,您需要显示标号和Net Label,如果您正在诊断问题,则Port非常方便。如果启用了Superscript选项,则当前文档视图将以不可见视图中的对象标识符作为上标。根据您的偏好配置所述选项。

多通道设计的通道2(CIN2)视图,注意原始逻辑原理图的标号和网络名称显示为上标的方式。

多通道设计的通道2(CIN2)视图,注意原始逻辑原理图的标号和网络名称显示为上标的方式。

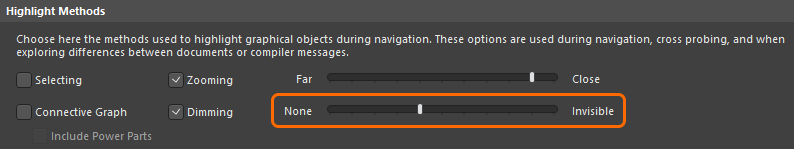

您是否想知道为什么一些原理图元素在通道(物理)选项卡中会变暗?默认设置是在标准显示强度下显示可在通道选项卡中编辑的对象,不可编辑的对象变暗。变暗在Preferences对话框的System - Navigation页面中设置。变暗的好处在于它有助于防止您尝试执行无法支持的编辑操作,例如在一个通道中移动Net Label。可根据需要设置Dim级别。

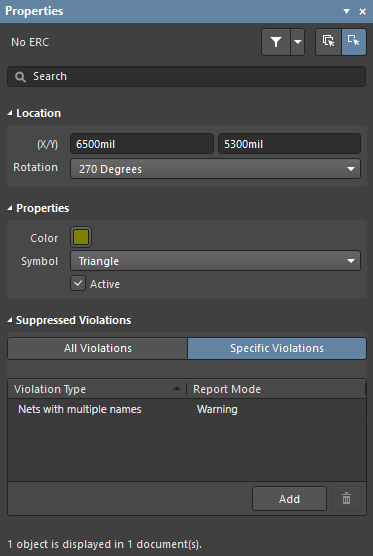

解决多个网络名称错误

原理图编辑器的错误校验选项默认标记具有多个名称的网络的每个实例。当您有意更改名称时可能会发生这种情况。例如,当网络输入图表符并且您更愿意在该图表中使用其它名称时。下图显示了一些示例,其中左侧和右侧输出绑定到顶层图表中的总线上,但在Sheet Entry中称为“Left”和 “Right”。

因为总线允许两个输出通道由具有Repeat关键字的一个图表符表示,所以使用了一根总线。如果左右通道使用不同的导线,则设计人员需要为左右输出通道(均指向相同的子原理图表)放置单独的图表符,然后将每个输出连接到其各自的输出图表符。

您必须指示软件如何处理多个网络标识符。为此,您需要:

- 在Options for Project对话框的 Error Reporting tab中,将具有多个名称错误校验的Net设置为No Report。这不是首选项,因为它在整个设计过程中妨碍了对该错误条件的所有校验。或者,您可以,

- 在受影响的网络上放置一个 Specific No ERC marker ,通过右键点击Messages 面板中的Error/Warning并选择Place Specific No ERC Marker for this violation命令便可轻松完成操作。该操作会使您进入NoERC对象放置模式,并且预先配置的特定NoERC标记会附加到光标上,准备好放置在错误网络上。放置后,双击配置样式和颜色。

注意用橙色圈出的小三角形,这是一个特定的No ERC标记,用于禁用MB1和MB2网络上的重复网络名称错误。

注意用橙色圈出的小三角形,这是一个特定的No ERC标记,用于禁用MB1和MB2网络上的重复网络名称错误。

多通道PCB设计

将设计从原理图编辑器传输到PCB编辑器时,如果在Project Options中Room可以创建,则每个图表中的所有元器件会聚集在PCB中相应的Room中。

在多通道设计中使用Room的一大优点是PCB编辑器支持将布局布线从一个Room(通道)复制到其它Room(通道)。Room也可以像单个对象一样移动,从而简化了在PCB上布置通道的过程。

设计完成后,将8路输入和2路输出通道从原理图编辑器传输到PCB编辑器,红色区域是Room。

设计完成后,将8路输入和2路输出通道从原理图编辑器传输到PCB编辑器,红色区域是Room。

PCB Room的作用

Room是用于限定电路板上的某个区域的PCB设计对象,可以以两种方式使用Room:

- 包含对象——如果Room像任何多边形形状对象一样放置,它实际上被创建为放置Design rule。Room定义的一部分是指定必须包含在该Room内的对象——通常为元器件。当该Room移动时,Room内的所有元器件也会移动。

-

确定其他设计规则的范围——以及本身的规则,Room也可用于确定其它设计规则的范围。举例来说,一个布线宽度设计规则定义了一类网络的布线宽度,那么优先级较高的设计规则(范围为Room)可以指定在该Room内应用于该类网络的不同宽度。

Room与多通道设计能很好的融合。根据Options for Project对话框的 Class Generation tab选项卡中的选项,设计从原理图编辑器传输到PCB编辑器时,可以自动创建Room,并为每个图表符提供一个Room。除了聚集该通道中的元器件外,Room还可用于该Room内元器件的命名。本文Multi-Channel PCB Design部分将进一步讨论Room及其在电路板设计过程中的作用。

有用的Room操作命令

- Design » Rooms - 此子菜单有许多用于定义和修改Room的有用命令。

- Design » Rooms » Copy Room Formats - 使用此命令将布局布线从一个Room(通道)复制到其它Room(通道)。

- Design » Rooms » Move Room - 通过点击并按住光标下方没有其它设计对象的地方,可以移动Room。光标将捕捉到最近的元器件焊盘或Room顶点(以较近者为准)。

- Edit » Select » Room Connections - 使用此命令选择所有始于焊盘并在Room内终止的铜片。

元器件如何链接Expand折叠

Each schematic component links to its PCB component through a Unique Identifier (UID). The UID is assigned when the schematic component is placed on the sheet, and is then assigned to the PCB component when the design is transferred to the PCB editor.

This scheme would be adequate for a simple design, but is not capable of supporting a multi-channel design, where the same schematic component is repeated in each physical channel (so the PCB components would have the same UID).

To cater for this, the UID for the PCB component is created by combining the UID of the parent Sheet Symbol with the UID of the schematic component. The syntax of the PCB UID changes slightly, depending on how the multi-channel design has been created.

For a multi-channel design created by placing multiple Sheet Symbols that all reference the same schematic sheet, then each Sheet Symbol can provide a unique ID, so the PCB UID has the format:

\SheetSymbolUID\SchComponentUID

For a multi-channel design created using the Repeat keyword, there is only 1 Sheet Symbol UID available, so the PCB UID also includes the ChannelIndex, in the format:

\ChannelIndex+SheetSymbolUID\SchComponentUID

Component links are managed via the Edit Component Links dialog (Project » Component Links command in the PCB editor). When changes are applied in this dialog, the PCB UIDs are updated to match

the schematic UIDs.

The explanation just given describes how components are linked, however newer versions of Altium Designer (from 18.0) no longer display the UID in panels and dialogs.

在PCB上显示标号

因为标号串最终可能会很长,所以在多通道设计中定位标号串可能很困难。除了选择生成短名称的命名选项外,另一种选择是仅显示原始逻辑元器件名称。举例来说,C30_CIN1将显示为C30。这需要将一些其它符号添加到电路板中,以指示单独的通道,例如在元器件丝印层上的每个通道周围绘制一个框。

您可以在PCB editor Properties面板(View » Panels » Properties)的Other部分选择PCB上的Logical和Physical标号显示。如果您选择在多通道设计中显示元器件的逻辑标号,则将在PCB上以及生成的任何输出中显示所述标号,例如图纸和Gerber文件。但在生成物料清单时,始终使用唯一物理标号。

如果您更喜欢扁平化元器件编号系统,则可以通过执行Board Level Annotation来替换系统命名方案。之所以称为板级标注,是因为元器件标号仅适用于注定要成为PCB的完整编译设计(物理设计)。

所述板级标注存储在.Annotation文件中,该文件将每个逻辑标号映射到指定的物理标号。该文件是项目的一部分,因此系统会提示您保存该文件。

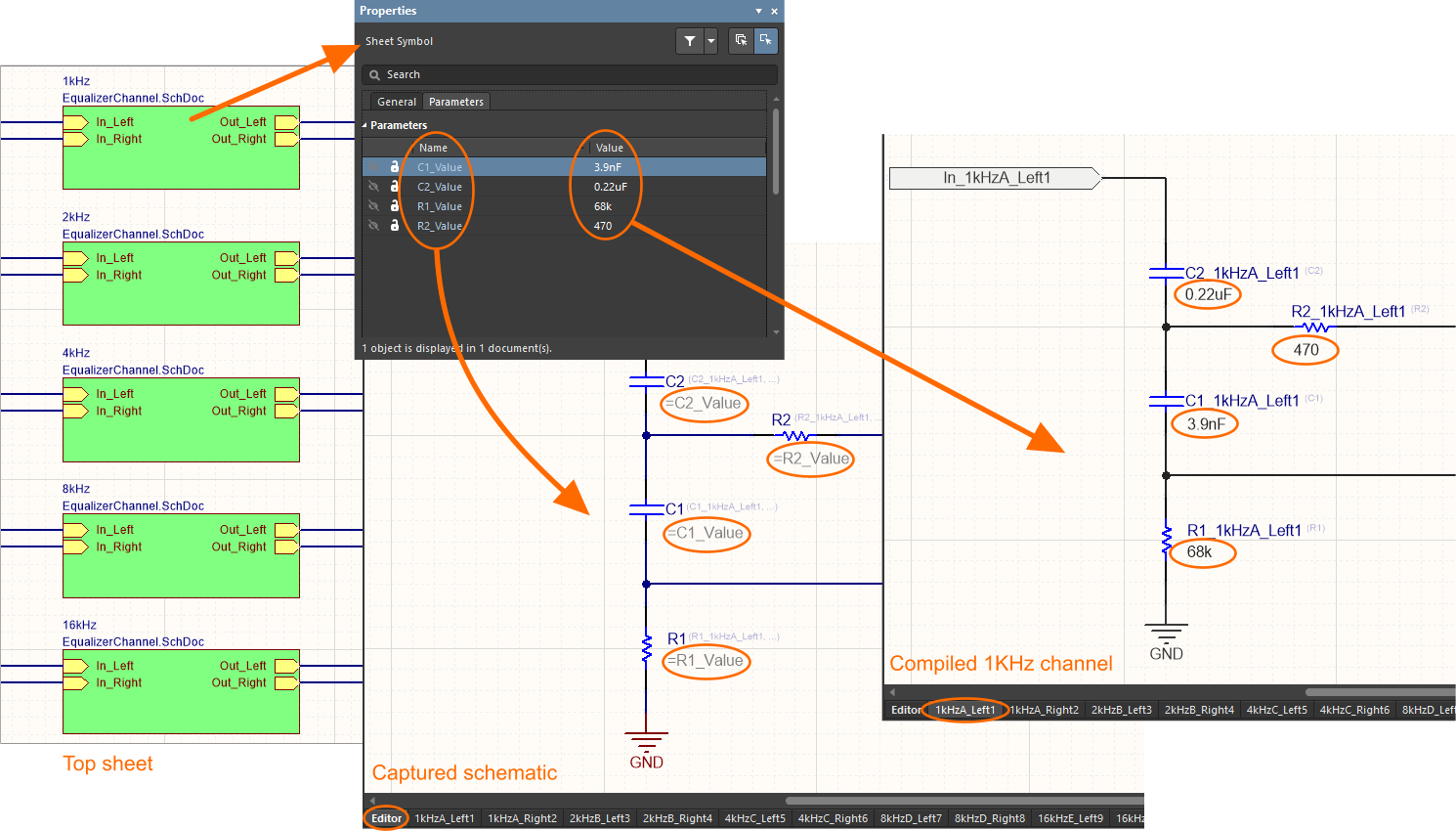

参数化多通道层次式设计

重复使用一部分设计(例如将当前项目中的图表符链接到公司的首选电源原理图)的挑战在于,元件的值并不总是从一个设计固定到下一个设计。

参数化层次式设计解决了这个问题——参数化层次式设计使您能够将原理图表中元器件值的规格移动到引用该图表的图表符中。此功能也适用于多通道设计,使您能够在每个通道中获得不同的元器件值。注意,一定要求每个通道均有自己的图表符,因为图表符是存储元器件值的地方。

例如,图形均衡器可以让相同电路重复多次,每个通道之间的唯一区别是元器件值。因此,不同通道中的电容可能取值为0.12µF、0.056µF和0.033µF。实现这一点很简单,因为您可以在引用每个通道的图表符中指定所述值,从而不需要具有许多类似的原理图,只需要元器件值不同即可。

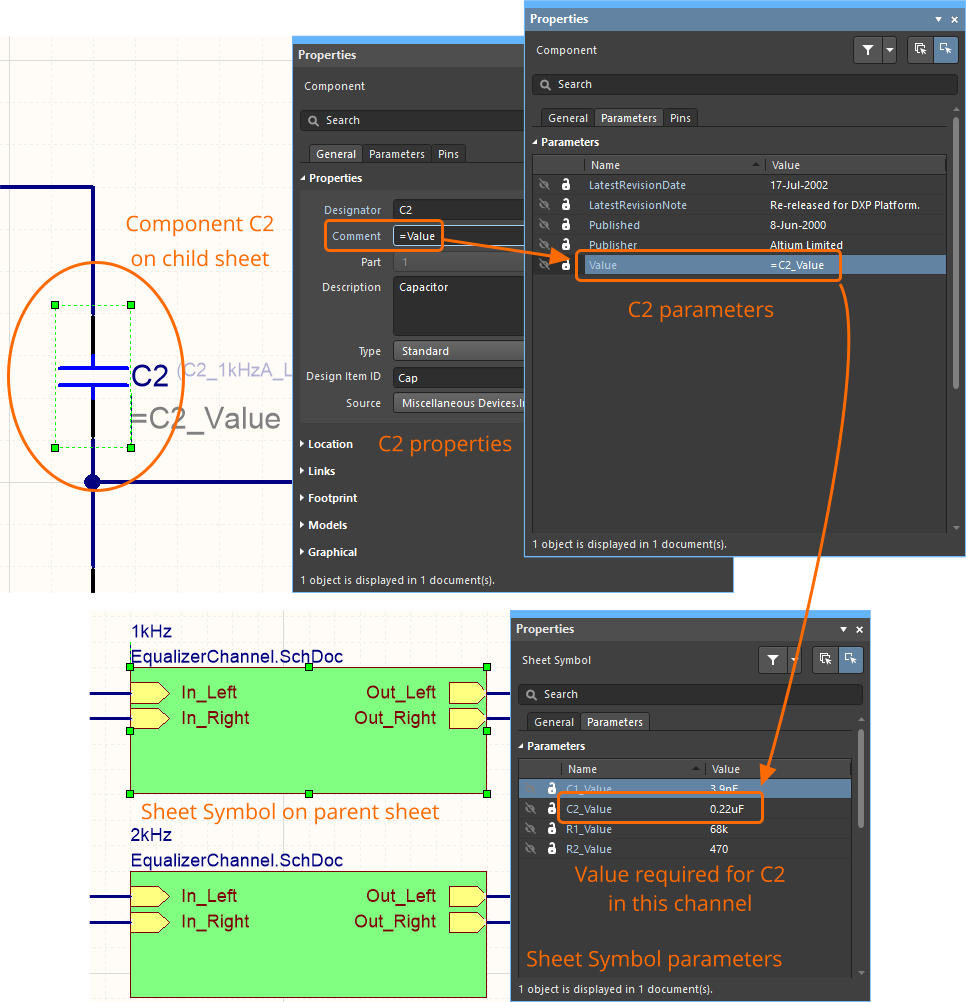

通过将参数化元器件的值作为上述图表符的参数,然后在目标元器件上引用该参数来定义参数化元器件。下图显示了左侧图形均衡器的顶层图表,旁边为1KHz图表符的参数。该图还显示了捕获的低级别原理图和编译后的1KHz通道。

图形均衡器在每个通道中具有不同的电容和电阻值,实际元器件值在图表符中进行定义,因此只需要捕获1个较低级别的电路图。

图形均衡器在每个通道中具有不同的电容和电阻值,实际元器件值在图表符中进行定义,因此只需要捕获1个较低级别的电路图。

每个Sheet Symbol参数还被定义为较低级别图表上原理图元器件中的参数值,如下图所示。在编译项目时,每个Sheet Symbol参数的Value将传递到相关原理图元器件,然后映射到元器件的Comment字段。

由于Value参数的值为=C2_Value,因此编译器知道必须在更高级别的Sheet Symbol中查找实际元器件值。

参数化层次结构不限于元器件值,您可以参考任何元器件参数或原理图表上的任何文本标签。您也可以从层次结构中多个图表中的符号中引用参数,系统将搜索层次结构,直到找到匹配的参数。

下载reference design \Parametric Hierarchy\AudioEqualizer.PrjPcb,了解如何正确配置图表符和元器件参数的示例。