Configuring the Layer Stack for Controlled Impedance Routing in Altium NEXUS

When the Routing Becomes Part of the Circuit

As device switching speeds increase, so too do the demands on the printed circuit board designer and the fabricator. As the length of the signal switching edge becomes shorter than the length of the PCB trace that carries it, the trace has to be treated as part of the circuit. That trace has an impedance, which is referred to as the characteristic impedance (Zo).

The best way to manage the impact of these additional circuit elements is to design the trace routing so that the characteristic impedance is consistent over the length - a technique called controlled impedance routing.

The impedance of the trace routing is defined by the:

- Cross-sectional area of the trace - determined from the width, the height (copper thickness), and the slope of the trace edges created during the etching process.

- Distance from the trace to the reference plane(s) - the return path of the signal energy is as important as the signal's path, this return path follows the signal path in the adjacent reference plane(s).

- Properties of the surrounding materials - the energy in the signal is not contained within the copper of the trace, due to the skin effect, it also travels down the dielectric material that surrounds the trace. The permittivity of the dielectric material gives a measure of how much the dielectric impacts on the flow of that energy.

In a traditional PCB design, the designer specifies the width/clearance of the trace to satisfy the current/voltage requirements.

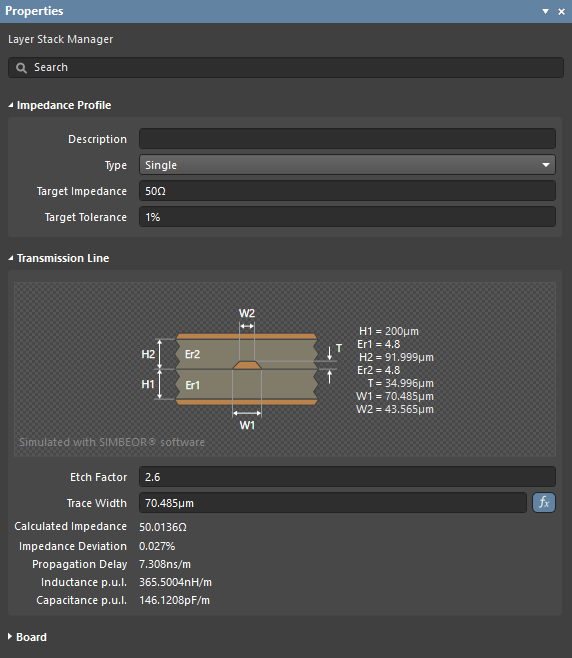

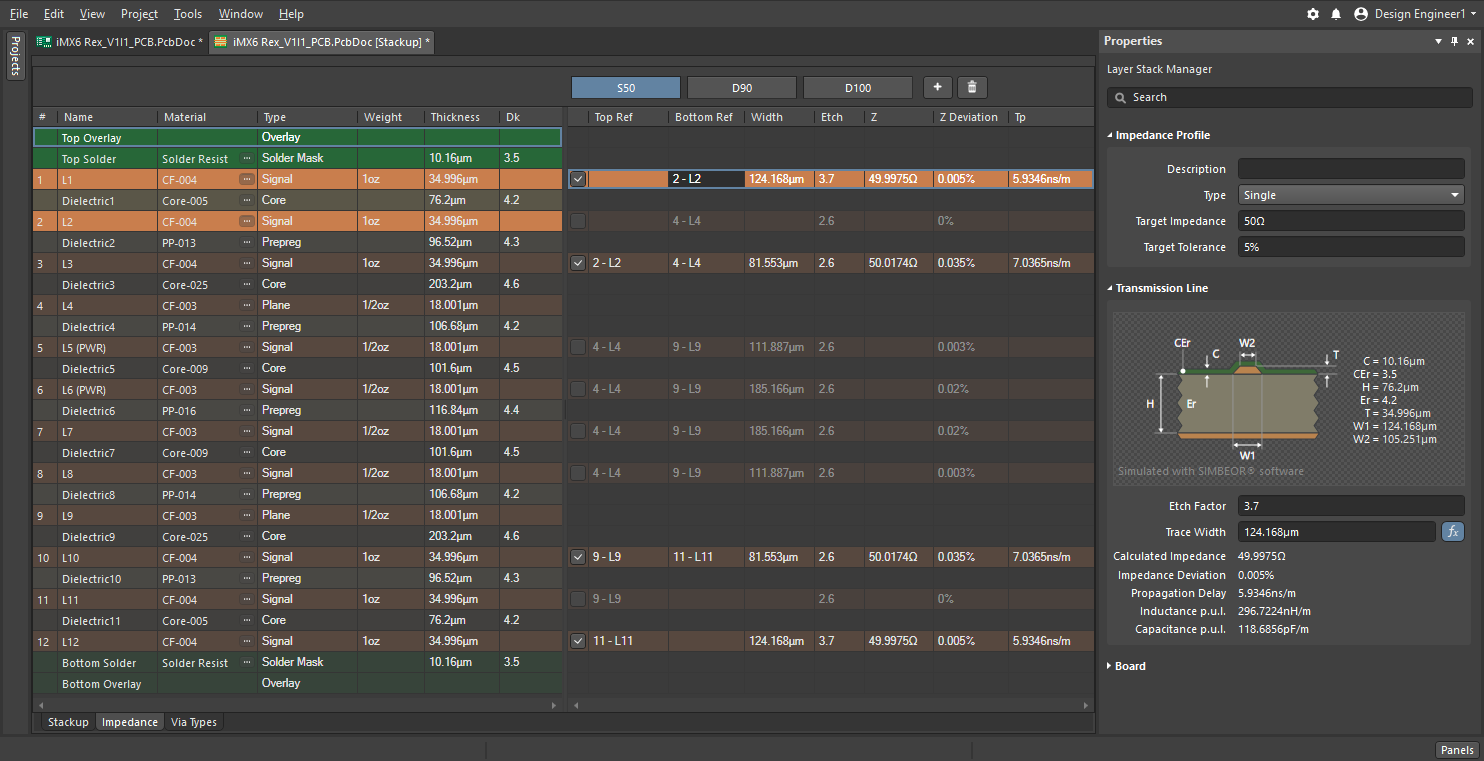

In a controlled impedance design the designer specifies the impedance rather than the trace width. Using the built-in Simbeor® impedance calculator, the PCB editor's Layer Stack Manager calculates the trace width needed to deliver the specified impedance.

Calculating the Impedance

The trace width required to deliver a specific impedance can be calculated as part of an impedance profile, in the Impedance tab of the Layer Stack Manager.

Based on:

- The values of the Target Impedance and Target Tolerance that you enter in the Impedance tab, and

- the materials settings defined in the Stackup tab, including:

- the thickness of the signal layer,

- the thickness of the surrounding dielectric layers (the distances from the reference plane(s)), and

- the properties of the dielectric material (permittivity Dk, and dissipation factor Df).

When these are correctly configured, the impedance calculator has sufficient information to calculate the:

- Trace Width

- Calculated Impedance (Z)

- Impedance Deviation (Z Deviation)

- Propagation Delay (Tp)

- Inductance per unit length (p.u.l.)

- Capacitance per unit length (p.u.l.)

Supported PCB Structures

- Microstrip

- Symmetrical Stripline

- Asymmetrical Stripline

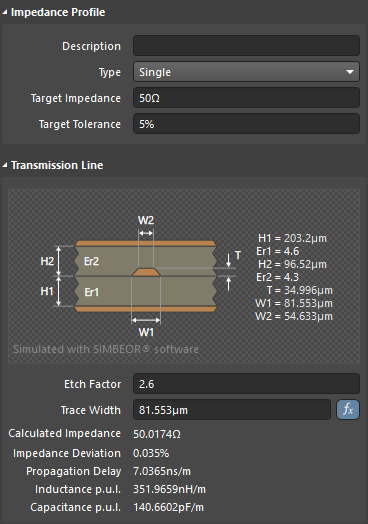

The calculated values are displayed in the Transmission Line section of the Properties panel when the Impedance tab is selected in the Layer Stack Manager, as shown below.

A 50Ω impedance profile defined for single nets routed on the top layer, hover the cursor over the image to display the settings for the same profile for layer L3.

A 50Ω impedance profile defined for single nets routed on the top layer, hover the cursor over the image to display the settings for the same profile for layer L3.

(image courtesy FEDEVEL Open Source, www.fedevel.com).

Creating and Configuring an Impedance Profile

- In the Layer Stack Manager switch to the Impedance tab, as shown above.

- Click the

button (or the

button (or the  button if there are profiles defined already), to add a new profile.

button if there are profiles defined already), to add a new profile. - Define the required impedance Type, Target Impedance and Target Tolerance in the Properties panel. The Description is optional, it will be displayed wherever the Impedance Profile name is displayed.

- The grid of layers is divided into 2 regions, the layers in the stackup are displayed on the left, then for each signal layer in the stackup there is a layer displayed in the Impedance Profile region on the right. Use the layer checkbox in the Profile region to enable impedance calculation for that layer.

- Select the enabled layer in the Profile region, all layers in the layer stack will fade except those being used to calculate the impedance for that selected signal layer (as shown in the image above). Edit that layer's reference layer(s) in the Top Ref and Bottom Ref columns. Note that reference layer(s) can be of Type Plane or Signal.

- Enable the Impedance Profile checkbox for each other layer that will carry routing at this impedance, and configure the reference plane(s). Hover the cursor over the image above to display the S50 Impedance Profile for layer L3.

Tuning the Width and Gap Settings

From the target impedance and target tolerance, the software calculates the Trace Width. It is likely that the calculated trace width will be a value that cannot be ordered, for example, 0.0683mm. The fabricator will advise what material thicknesses are available and what precision they can achieve for trace widths. Then it becomes a process of starting at the desired values, then testing the impact on the calculated impedance values when the dimensions are adjusted to what is available.

To support this process of testing and tuning the settings, the impedance calculators support forward and reverse impedance calculations. The default mode is forward (enter the impedance, the software calculates the width). The  icon indicates the calculated variable.

icon indicates the calculated variable.

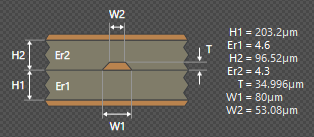

A Target Impedance of 50Ω gives a width of 81.553µm, hover to see the results when the width is changed to 80µm.

A Target Impedance of 50Ω gives a width of 81.553µm, hover to see the results when the width is changed to 80µm.

To reverse the calculation and explore different trace widths for the selected layer, type in the new Trace Width value and press Enter on the keyboard. The calculated values will update to reflect the impact of changing to that width. Click the  button to return the calculator to forward calculation mode.

button to return the calculator to forward calculation mode.

To explore the differential pair transmission line results, nominate the calculated variable - either the Trace Width or Trace Gap - by clicking the appropriate  button. Edit the other variable to change the Target Impedance, or alternatively change the Target Impedance to explore the impact on the other variable.

button. Edit the other variable to change the Target Impedance, or alternatively change the Target Impedance to explore the impact on the other variable.

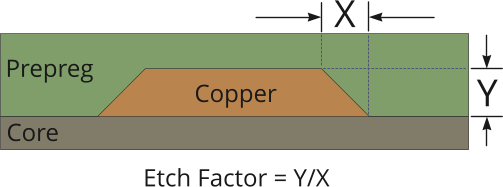

Etch Factor

The signal traces on a PCB are fabricated by etching away unwanted copper. Because the etchant starts etching away the copper at the surface, this copper spends more time in contact with the etchant. The result is the finished edges of the trace will have a slope, reducing the cross-sectional area of the finished trace, as shown in the image below.

The area of trace-edge copper lost (on both edges) during etching = X * Y

The amount of slope is referred to as the Etch Factor, where:

Etch Factor = Y/X

If Y = X, then the Etch Factor = 1

Refering to the image shown in the Properties panel:

Etch Factor = T/[(W1-W2)/2]

Selecting the Layer Material

In a controlled impedance design, the selection of the materials used in the layer stackup is very important.

For example, the most common material used to fabricate PCBs is glass fiber (fiberglass) reinforced epoxy resin, with copper foil bonded onto each side. The tightness of the weave of the glass fiber fabric affects the value and consistency of the dielectric constant Dk (permittivity) and Loss Tangent Df. Surrounding the woven glass fabric is resin - the percentage of resin used is also important in the performance of the material.

There is a large range of glass fiber weaves available. To help ensure the predictability and performance of the glass fiber-based materials used in PCB fabrication, the IPC has a standard for weaves:

IPC standard IPC-4412B: Specification for Finished Fabric Woven from "E" Glass for Printed Boards

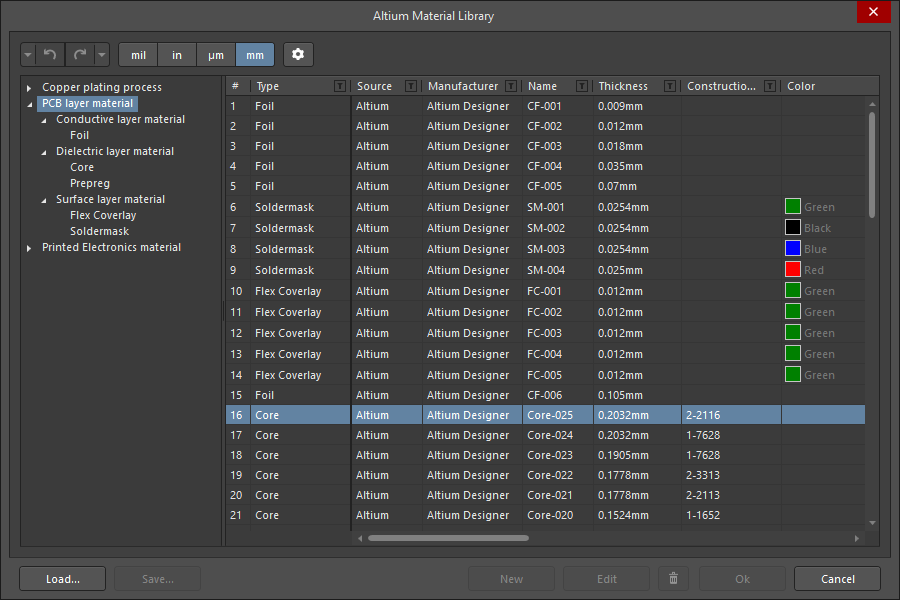

The Material Library

As the designer, you can either edit the material properties directly in the Layer Stack Manager, or select materials from the Altium Material Library.

The entire library can be viewed (and added to) in the Altium Material Library dialog (Tools » Altium Material Library).

The materials are organized into usage categories, accessed through a tree structure on the left of the dialog. Below this level, each usage category is broken into functional categories, such as Conductive layer material, Dielectric layer material and Surface Layer Material; in the PCB layer material category.

Adding, Saving and Loading Material

New material can be added to the library when a specific material category is selected in the tree. Materials defined in an external material library can be loaded (Load button), and user-defined material that has been added in the Altium Material Library dialog can also be saved to a user-library (Save button). Only user-defined material is saved.

Adding Custom Properties to Material

Custom properties can be added to material detailed in the library (default and user-defined material). To add a custom property, first, select the correct node in the tree on the left to define the material(s) it is to be added to, then click the ![]() button to open the Material Library Settings dialog.

button to open the Material Library Settings dialog.

The required value can then be added to the selected material in the Altium Material Library dialog, select the row and click the Edit button.

Dielectric Material Behavior

The Dk/Df of PCB dielectrics are frequency dependent - for composite dielectrics Dk decreases with frequency while Df increases slightly (due to the relaxation-type of atomic polarization in such dielectrics).

The dispersion over frequency can be described with a multi-pole Debye model - which requires multiple frequency points to build. For PCB dielectrics, a simpler pole-continuous model has been developed - called Djordjevic-Sarkar or the Wideband Debye model. The model is analytical, causal and can be built with measurement of Dk/Df at just one frequency point - a much simpler but still accurate approach (for more information refer to the Material World tutorial #2016_01 in the Simberian Technical Presentations Library).

The Layer Stack Manager's impedance calculator uses the Wideband Debye model, with a default frequency value of 1 GHz. If a different frequency is required, pick the Dk/Df values from one frequency point from 1 to 10 GHz from the laminate specs and then use the characteristic impedance value computed at 1 GHz.

Applying the Impedance Profile to the Routing

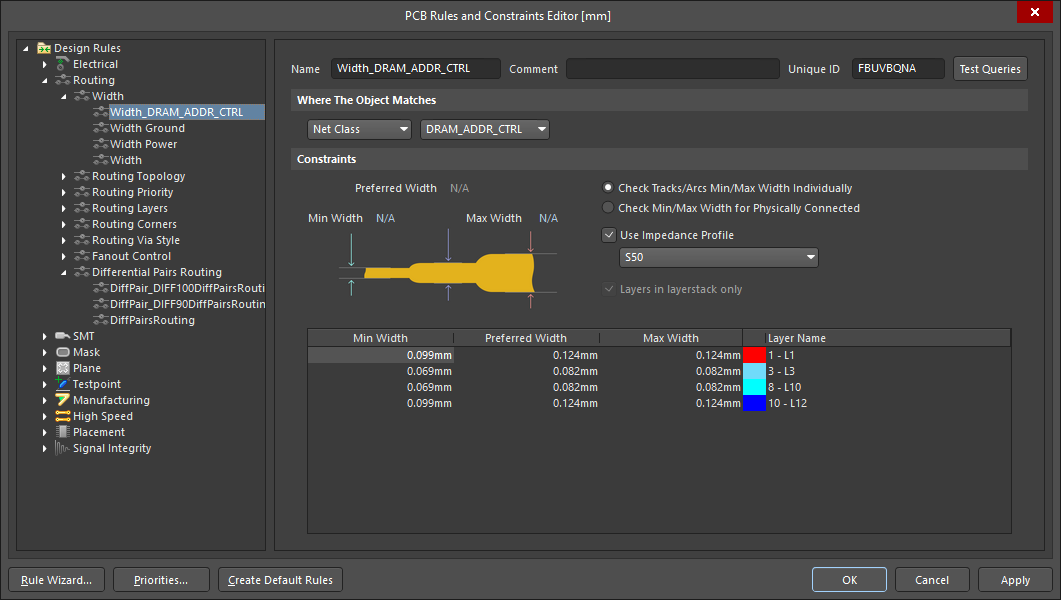

Controlled impedance routing is all about configuring the routing width to deliver the correct impedance, which means the routing width may be different on each signal layer. This is managed by assigning an Impedance Profile instead of a specific routing width when the design rule is configured in the PCB Rules and Constraints Editor (Design » Rules). When this is done the software automatically sets the width to suit the layer.

The required Impedance Profile is selected in the applicable Routing Width design rule (for individual nets), or Differential Pairs Routing design rule.

This routing width rule targets a class of DRAM nets. The S50 Impedance Profile is defining the routing widths, which will change according to the layer.

This routing width rule targets a class of DRAM nets. The S50 Impedance Profile is defining the routing widths, which will change according to the layer.

Enable the Use Impedance Profile option in the Constraints region of the design rule. The dropdown list will include all available Impedance Profiles of the appropriate Type (Single or Differential), select the profile required by the nets being targeted by this design rule.

When a profile is selected, that profile's Width settings are applied to the Preferred Width setting in the rule. This is done for each signal layer enabled for the profile, all other signal layers that are not enabled for that profile, are removed.

When an Impedance Profile has been applied, the Preferred Width settings can no longer be edited. The Min Width and Max Width settings can still be edited, set these to suitable smaller/larger values.

The nets can then be interactively routed, in the usual way.

► Learn more about Controlled Impedance Routing