Electrical - Clearance

Rule category: Electrical

Rule classification: Binary

Summary

This rule defines the minimum clearance allowed between any two primitive objects on a copper layer. Either a single value for clearance can be specified, or different clearances for different object pairings, through use of a dedicated Minimum Clearance Matrix. The latter, in combination with rule-scoping, provides the flexibility to build a concise and targeted set of clearance rules to meet even the most stringent of clearance needs.

Constraints

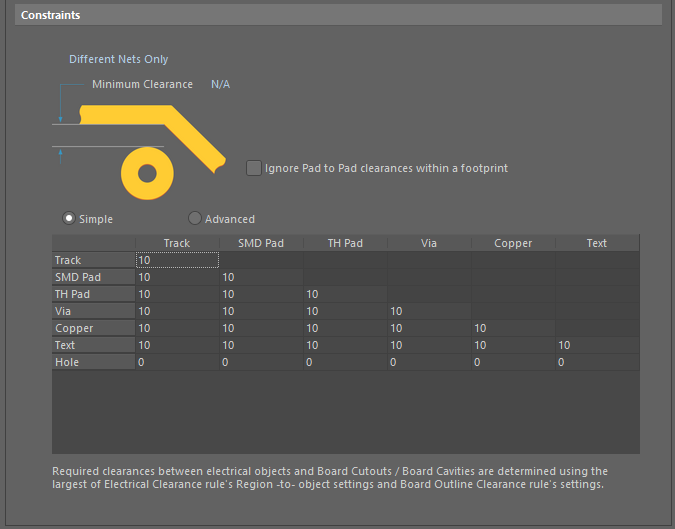

Default constraints for the Clearance rule. Roll the mouse over the image to compare the two modes available.

Default constraints for the Clearance rule. Roll the mouse over the image to compare the two modes available.

- Connective Checking - the scope of the rule with respect to the nets in the design. Can be set to one of the following:

Different Nets Only- constraint is applied between any two primitive objects belonging to different nets (e.g. two tracks on two different nets).Same Net Only- constraint is applied between any two primitive objects belonging to the same net (e.g. between a via and pad on the same net, or within the same track of a differential pair).Any Net- constraint is applied between any two primitive objects belonging to any net in the design. This is the most comprehensive of the three options and covers the possibility of the objects belonging to the same net or different nets.- Different Differential Pair - constraint is applied between any two primitive objects belonging to different nets of different differential pairs (e.g. a track in TX_P and a track in RX_P).

- Same Differential Pair - constraint is applied between any two primitive objects belonging to different nets of the same differential pair (e.g. a track in TX_P and a track in TX_N).

- Ignore Pad to Pad Clearances within a footprint - toggle this option on/off to specify whether clearances between pads in the same component footprint are ignored. This option is disabled by default.

- Minimum Clearance - the value for the minimum clearance required. A value entered here will be replicated across all cells in the Minimum Clearance Matrix. Conversely, when a different clearance value is entered for one or more object pairings in the matrix, the Minimum Clearance constraint will change to N/A, to reflect that a single clearance value is not being applied across the board.

- Minimum Clearance Matrix - provides the ability to fine tune clearances between the various object-to-object clearance combinations in the design.

Working with the Clearance Matrix

For many users, there is no great difference between Track and Arc primitives. And when it comes to Fill, Region, and Polygon objects, most users just see these as more 'copper.' With this in mind, the minimum clearance matrix for the Clearance rule has been enhanced to operate in two modes:

- Simple - in this mode, Track and Arc objects are combined into the single Track entry. Fill, Poly, and Region objects are combined into the single Copper entry. The Simple mode is the default mode, regardless of whether opening an existing design or a new design.

- Advanced - this mode is the traditional matrix, present in previous versions of the software, with all objects presented.

Definition of clearance values in the matrix can be performed in the following ways:

- Single cell editing - to change the minimum clearance for a specific object pairing. Simply click on a cell to select it for editing.

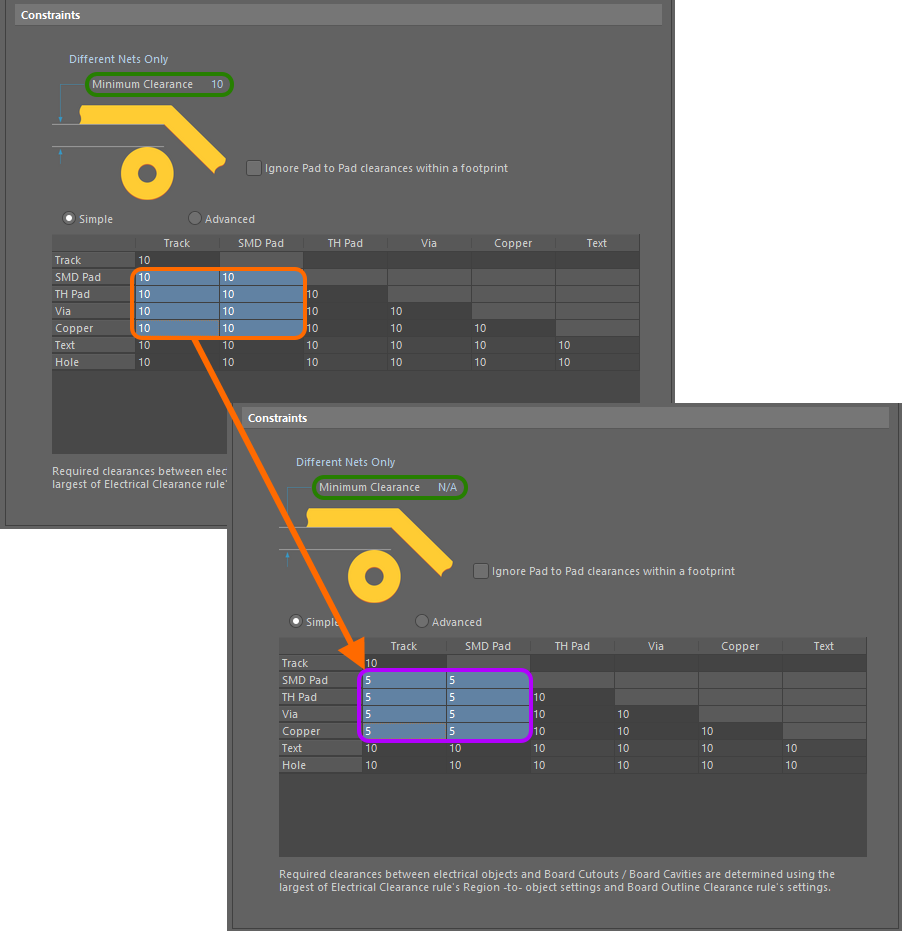

- Multi-cell editing - to change the minimum clearance for multiple object pairings:

- Use Ctrl+Click, Shift+Click, and Click+Drag to select multiple cells in a column.

- Use Shift+Click, and Click+Drag to select multiple contiguous cells in a row.

- Use Click+Drag to select multiple contiguous cells across multiple rows and columns

- Click on a row header to quickly select all cells in that row.

- Click on a column header to quickly select all cells in that column.

With the required selection made (either a single cell or multiple cells), making a change to the current value is simply a case of typing the new value required. To submit the newly entered value, either click away on another cell, or press Enter. All cells in the selection will be updated with the new value.

Example multi-cell editing. Notice that as different values for clearance now exist for one or more object pairings, the Minimum Clearance constraint has

Example multi-cell editing. Notice that as different values for clearance now exist for one or more object pairings, the Minimum Clearance constraint has

changed to N/A, to reflect that a single clearance value is no longer being applied for all object-to-object clearance combinations.

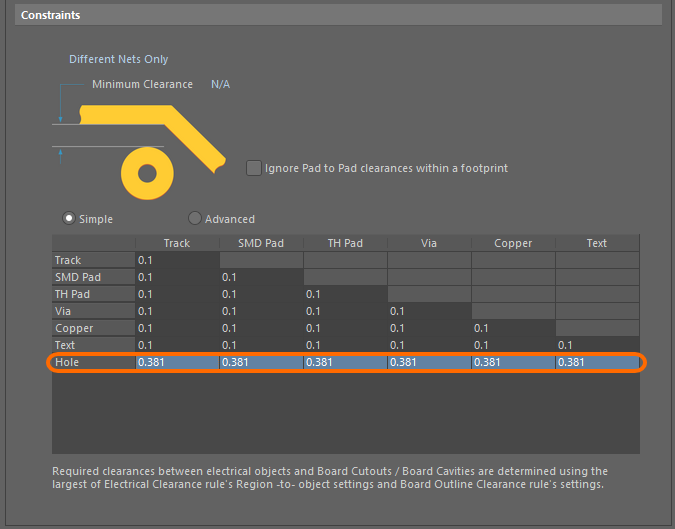

Hole-to-Object Clearance Checking

Designers can check clearances between the edges of drill holes and neighboring copper objects on signal layers. This is particularly beneficial in preventing the routing of track too near to a drilled hole, which could otherwise suffer from any potential wandering of the drill during board fabrication. The row at the bottom of the Clearance rule's minimum clearance matrix is used to define the desired clearances.

Set clearance values to catch any copper objects that are too close to the edges of drill holes in the design.

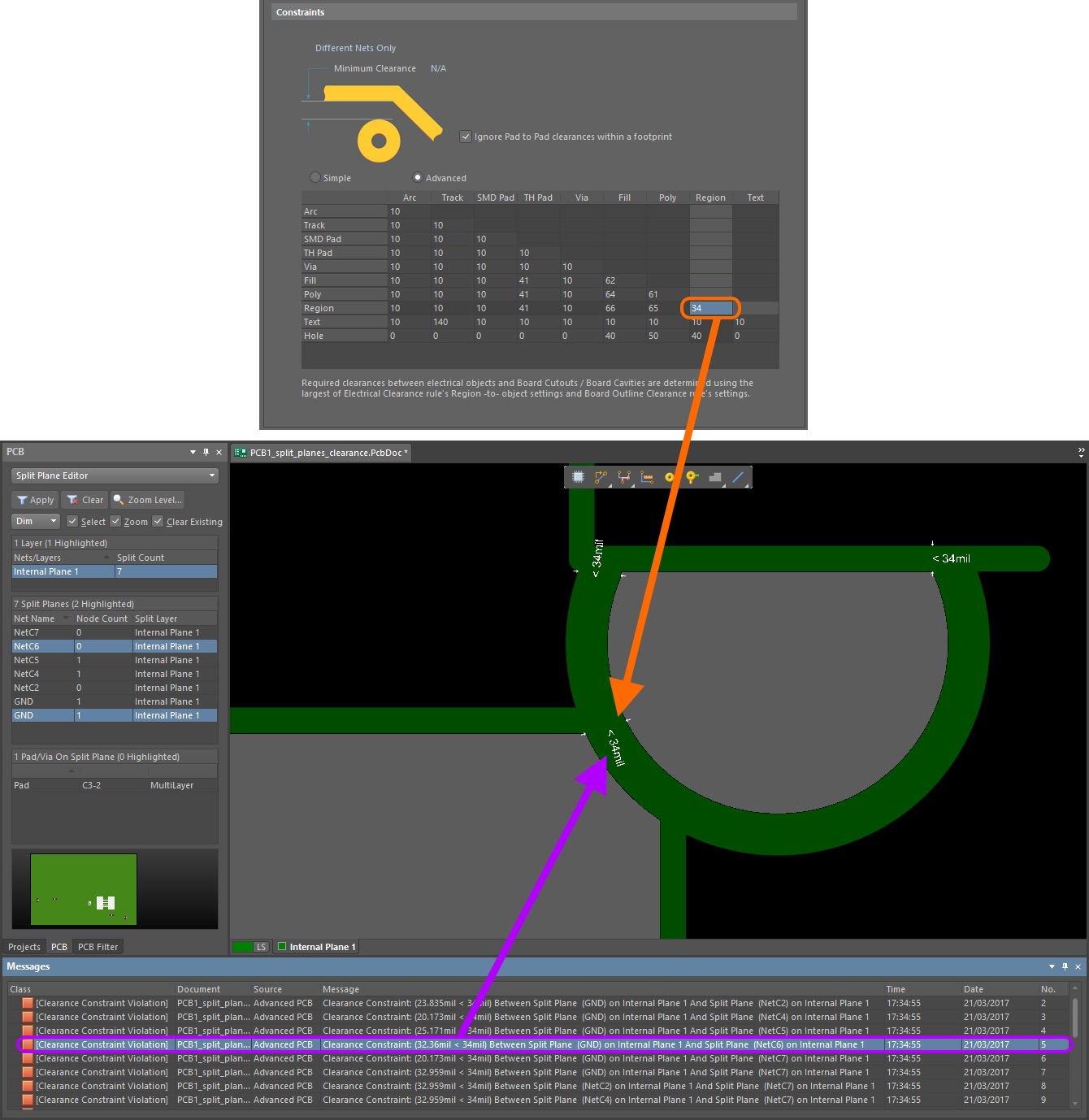

Split Plane Clearance Checking

Designers can also check clearances between split plane regions on internal plane layers. How clearance is defined depends on the mode in which you are using the minimum clearance matrix:

- Simple mode - specify the required split plane-to-split plane clearance value using the Copper-Copper cell.

- Advanced mode - specify the required split plane-to-split plane clearance value using the Region-Region cell.

A violation will appear in the form:

Clearance Constraint: (<CurrentClearance> < <DefinedClearance>) Between Split Plane (<NetName>) on <InternalPlaneLayerName> And Split Plane (<NetName>) on <InternalPlaneLayerName>,

for example:

Clearance Constraint: (32.36mil < 34mil) Between Split Plane (GND) on Internal Plane 1 And Split Plane (NetC6) on Internal Plane 1

Clearance checking between split plane regions on an internal layer. In this case, the clearance value of 34mil has been entered in the Region-Region cell, as clearances

Clearance checking between split plane regions on an internal layer. In this case, the clearance value of 34mil has been entered in the Region-Region cell, as clearances

are being defined using the Advanced mode of the matrix.

How Duplicate Rule Contentions are Resolved

All rules are resolved by the priority setting. The system goes through the rules from highest to lowest priority and picks the first one whose scope expressions match the objects being checked.

Rule Application

Online DRC, Batch DRC, interactive routing, autorouting, and during polygon placement.

Tips

- When defining the constraints for the rule, the Connective Checking option would typically be set to

Different Nets Only. An example of whenSame Net OnlyorAny Netcould be used is to test for vias being placed too close to pads or other vias on the same net, or any other net. - The minimum clearance matrix applies irrespective of the connective checking method specified. If different clearances are required between objects on the same net, to those defined for objects on different nets, be sure to define separate clearance rules as required to suit.

- The applicable use of the clearance matrix depends on the rule scoping. For example with scoping of ALL-ALL, all cells in the matrix are applicable (i.e. all possible object pairings). However, if scoping were set to IsVia-IsTrack, then only the single cell for the Via-Track object pairing would be applicable, and all other cells in the matrix left unused.

- When defining a clearance rule for a polygon, it is the primitives of the polygon that the rule is actually applied to, rather than the polygon itself. The keyword entry

InPolygon(orInPoly) should be included in the Full Query in this case, instead ofIsPolygon(orIsPoly). The specific polygon clearance rule must also be given a higher priority than any general clearance rule, if it is to have any effect.