操作FPGA管脚映射器

The Altium Designer Pin Mapper dialog allows you to create a link between an external pin file (such as one exported from FPGA or Microcontroller (MC) tools) with a schematic component, and then compare the pin signals between those two domains (FPGA and PCB).

As a result of this pin comparison, any changes or updates in the external pin file can be transferred to the schematic, or the pin data from the schematic can be passed back to the pin file. The main purpose for using the Pin Mapper is to obtain additional information about component pins from external tools (particularly FPGA and MC), so this data can used for Pin Swapping in the Configure Pin Swapping dialog. It replaces the need to manually transfer pin data between the two domains.

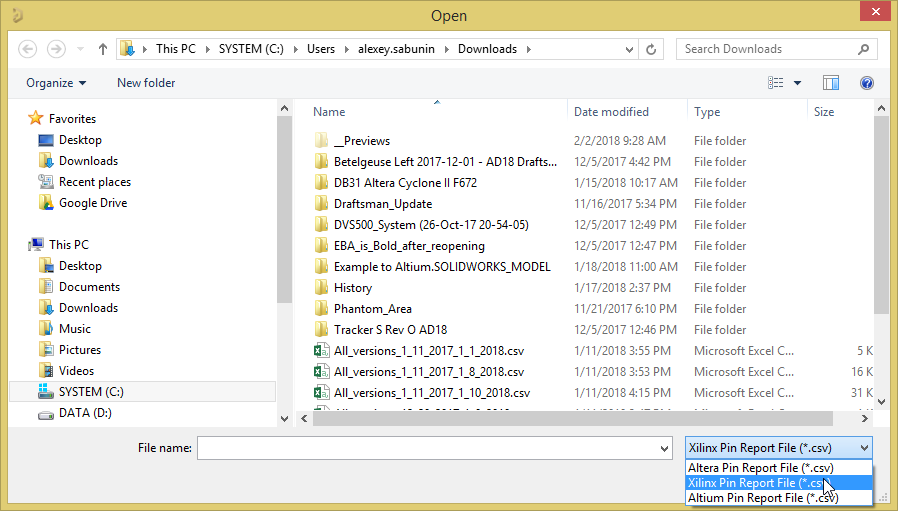

Currently, the Altium Designer Pin Mapping feature directly supports two FPGA vendors – Altera and Xilinx. The intention is to expand this vendor list in the future. Also supported is Altium's own Pin Info file format, which can be used as a FPGA/MC pin description for any third party FPGA tools, or for other types of components.

Process Flow

- Source Pin data file from FPGA tools

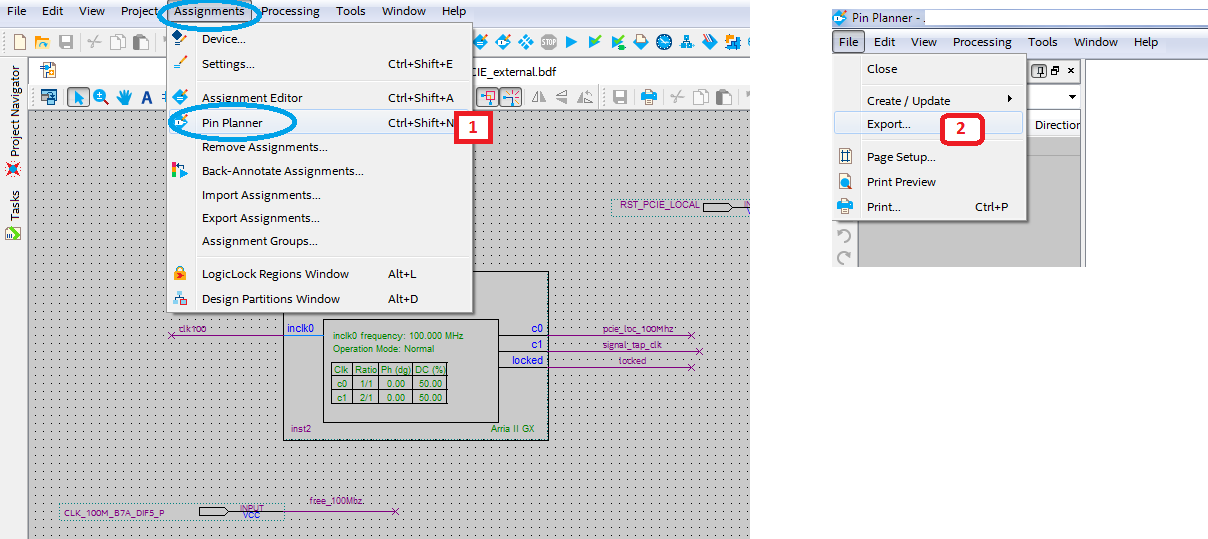

- For Altera Quartus® II v13.1:

- For Xilinx Vivado® 2017.4:

- Open the implemented design in Vivado.

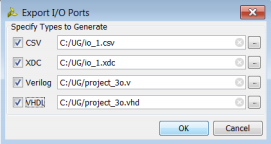

- Select File » Export » Export I/O Ports.

- In the Export I/O Ports dialog, specify

csvas type of I/O port to generate, and click OK.

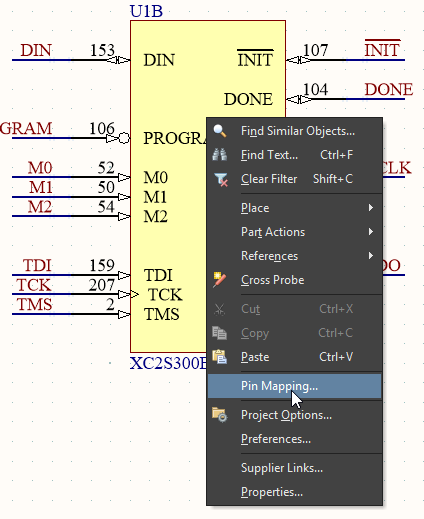

- Access FPGA/MC data from the external pin file in Altium Designer:

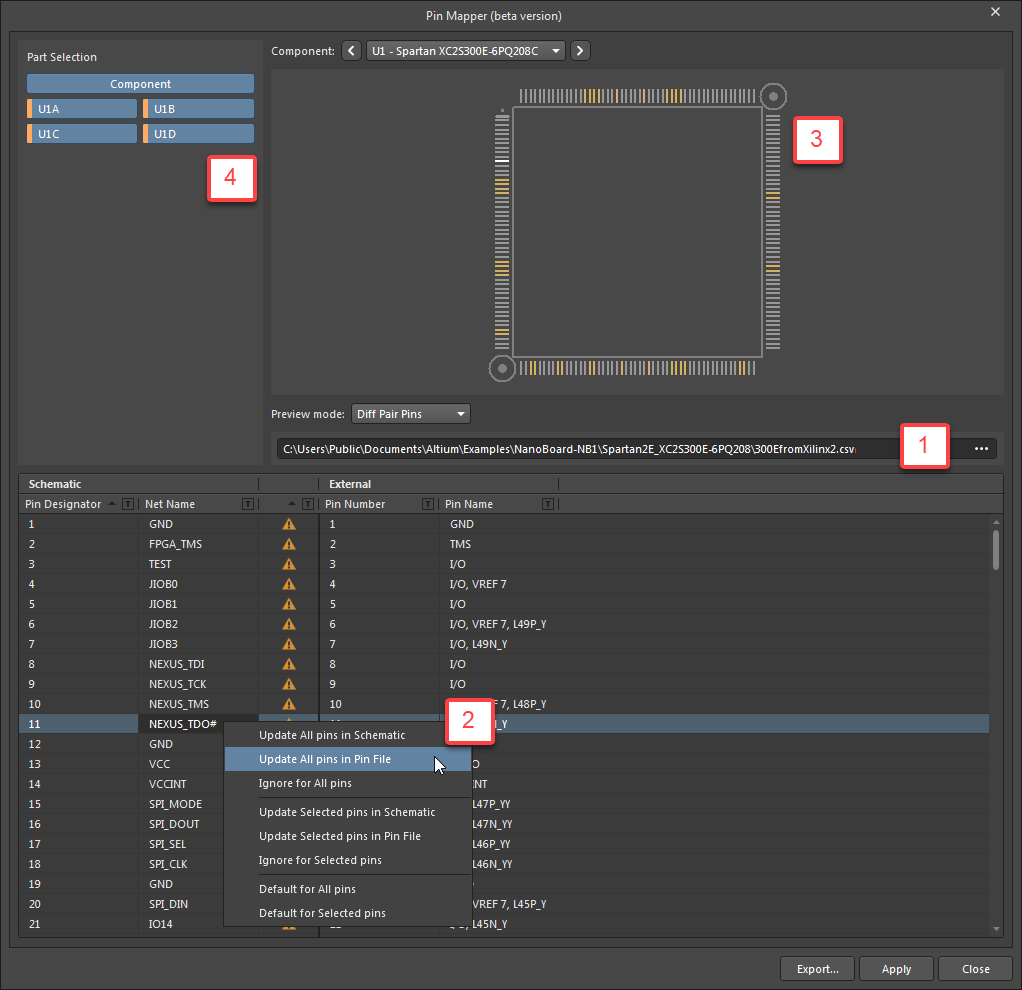

- The Pin Mapper dialog contains the following parts (see image labels):

- Shows the file name and path of the source FPGA/MC pin file. The link is established through the file browser (

).

). - The Pin Table where source pin assignment changes can be found and applied to the Schematic component, or back. Use the arrow next to the right of each column header name to sort the column in ascending/descending order. Click the filter icon in the column header to access a drop-down to filter the column contents.

- The Footprint preview, where the selected pins are highlighted and pins can be displayed by groups using the Preview mode drop-down. Choices include None, Bank Number, IO Pins, and Diff Pair Pins.

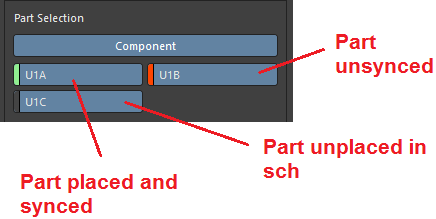

- The Component Part Selection, which filters the table by part. This also indicates if a part is placed on the schematic, and if each part is synchronized to match the external file data (see details below).

- Shows the file name and path of the source FPGA/MC pin file. The link is established through the file browser (

- Choose an external pin file in the Pin Mapper dialog:

- Depending on the previous action, the Pin Mapper dialog will offer solution options for each pin:

-

(Synced) – pins net names are synchronized, no changes are required.

(Synced) – pins net names are synchronized, no changes are required. -

(Update Pin File) – transfer net name from the schematic to the external FPGA pin file (which is updated). Net names from the Schematic will be copied to the Signal names in the FPGA pin file; the source

(Update Pin File) – transfer net name from the schematic to the external FPGA pin file (which is updated). Net names from the Schematic will be copied to the Signal names in the FPGA pin file; the source csvpin file is rewritten. -

(Update Schematic) – change the schematic net name to match the Signal name in the external FPGA pin file (schematic is updated). Net labels in Schematic will change to match the source FPGA Signal names.

(Update Schematic) – change the schematic net name to match the Signal name in the external FPGA pin file (schematic is updated). Net labels in Schematic will change to match the source FPGA Signal names. -

(Ignore) – reject changes, no updates will be performed.

(Ignore) – reject changes, no updates will be performed. -

(Warning) – there is a non-critical difference in pin name matching between the schematic and external (FPGA) file. If desired, select an update option (or Ignore) from the drop-down menu.

(Warning) – there is a non-critical difference in pin name matching between the schematic and external (FPGA) file. If desired, select an update option (or Ignore) from the drop-down menu. -

(Fatal Error) – there is a critical difference in pin name matching between the schematic and external (FPGA) file. Note that this Fatal Error must be resolved before making any updates.

(Fatal Error) – there is a critical difference in pin name matching between the schematic and external (FPGA) file. Note that this Fatal Error must be resolved before making any updates.

-

- Choose the appropriate action from the icon drop-down menu for each entry (row) in the table and select Apply.

- When the

action is selected, net names from the Schematic will be copied to the Signal names in the FPGA pin file – the source

action is selected, net names from the Schematic will be copied to the Signal names in the FPGA pin file – the source csvpin file is rewritten. - When the

action is selected, net labels in Schematic will change to match the source FPGA Signal names.

action is selected, net labels in Schematic will change to match the source FPGA Signal names.

- When the

Note that the right-click menu for a table entry offers a range of bulk selection options for pin name updates.

Additional Abilities

- The dialog's Part Selection allows the pins that are listed in the mapping table to be filtered by the selected Part. You can also check for Parts that are not placed in the schematic, and Parts that are not synced with the external FPGA file (red indicator).

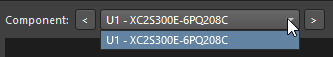

- If there are multiple component parts linked with the external file, the Pin Mapper dialog allows you to switch between options for this kind of component.

- The grid tables include the following right-click menu commands:

- Update All pins in Schematic - choose to update all pin names in the schematic.

- Update All pins in Pin File - choose to update all pin names in the pin file.

- Ignore for All pins - choose to ignore for all pins.

- Update Selected pins in Schematic - choose to update selected pin names in the schematic.

- Update Selected pins in Pin File - choose to update selected pin names in the pin file.

- Ignore for Selected pins - choose to ignore for selected pins.

- Default for All pins - choose to use the default for all pins.

- Default for Selected pins - choose to use the default for selected pins.

- If there are pins where different net names are assigned in the Schematic and FPGA sides, then this can be checked in an ERC where they are displayed as violation in the Messages panel (not yet implemented).

- If you would like to start the workflow with a FPGA pin file from the schematic side, then an Altium Pin Report file can be generated – select the Export button in the Pin Mapper dialog.

- Currently, only general pin parameters can be copied, however support for more advanced data such as Swap group etc is planned. Swapping must be defined manually at the moment by importing changes from the FPGA pin file data.

- Since the external pin file is linked to a component, a new component model (Pin Info) is created and shown in the Models list in the Component Properties panel. In the future, this will provide an easy way to add FPGA pin data to a Library component. The panel's Models section also allows the Pin Info to removed or modified.

-

When a component has model Pin Info, additional pin parameters and options will be available for that component in the Configure Pin Swapping dialog.