Altium Designer 全新功能

本页详细介绍了Altium Designer 23初始版本中的改进内容,以及后续更新中添加的改进内容。除了提供一系列有助于推动现有技术的发展和成熟的改进内容外,每次更新也根据客户通过AltiumLive社区的BugCrunch 系统提出的反馈,在整个软件中整合大量修复和强化功能,以帮助您继续创造前沿电子技术。

Altium Designer 24.4

发布时间:2024年4月16日 – 版本24.4.1(build 13)

原理图输入改进

具有备用模式的多部件元件的使用

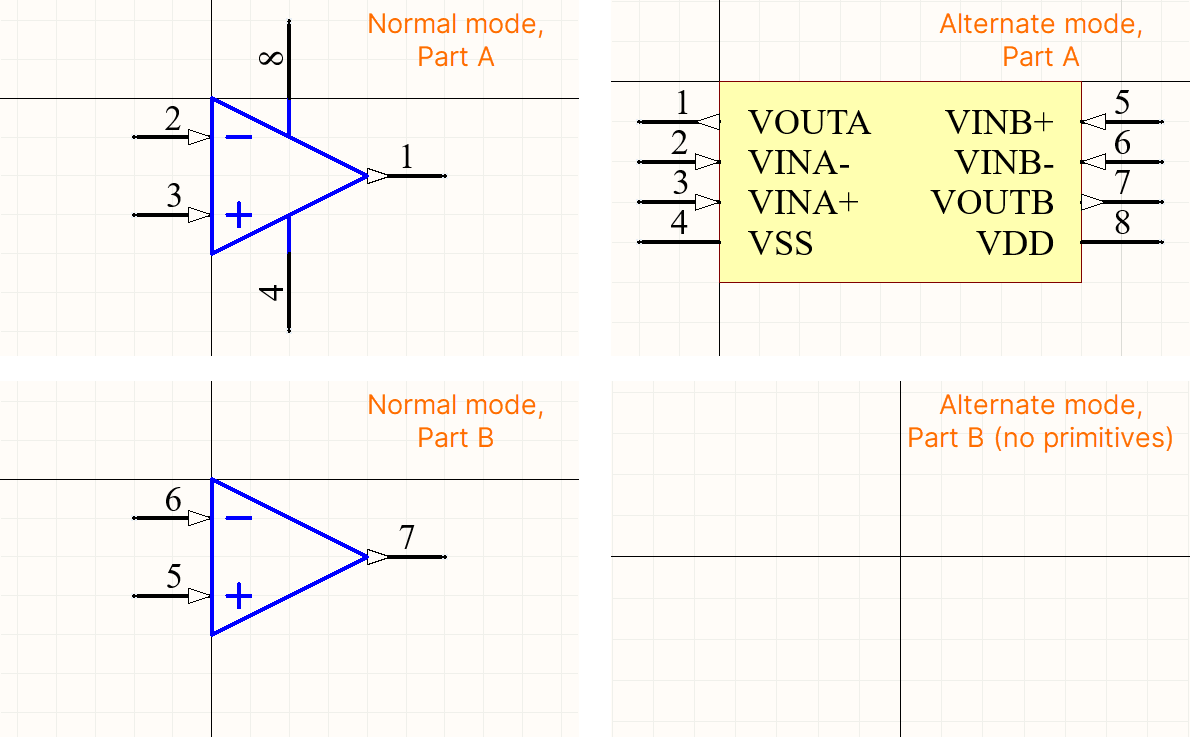

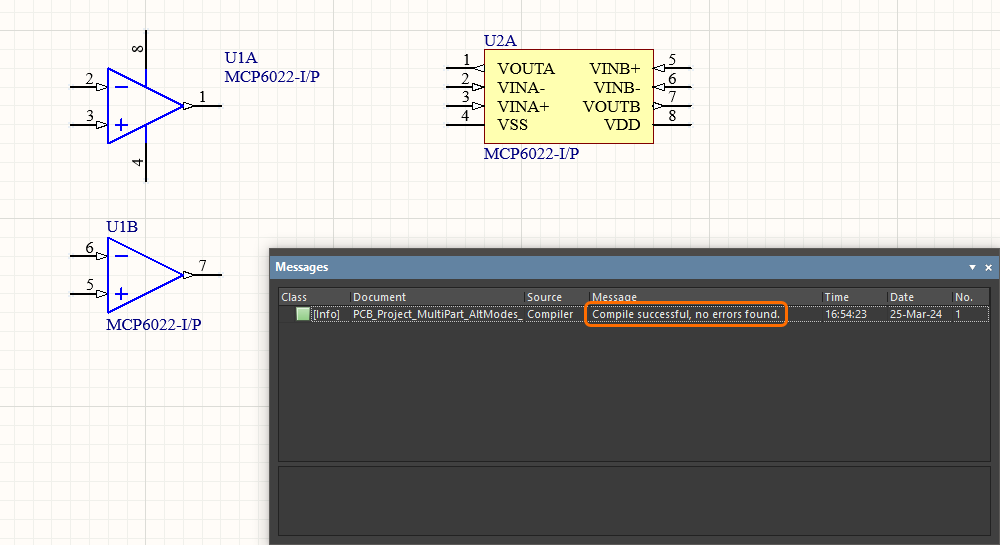

在本次发布中,宣布支持通过定义的Normal Mode和Alternate Mode仅使用单个元件,即可将多部件元件显示为单个符号(所有子部件)或多个符号(每个单独子部件均为一个符号)。

双运算放大器元件的原理图符号示例。在正常模式下,将以两个符号表示元件。在备用模式下,将以单个符号表示元件。

如果元件现在具有不含基元的子部件,则在运行设计验证时,未将这些子部件放置在原理图上将不会再导致元件发生Unused子部件冲突(前提是,不含基元的部件被列在可通过SCH Library面板查看的符号部件列表中包含基元的所有部件下方)。

PCB设计改进

元件‘Push’和‘Avoid’的选定框

当在Push或Avoid Obstacles模式下进行元件移动时,现在将按照元件选定边界框的用户定义几何形状进行处理(遵循PCB.ComponentSelection高级设置 – 了解更多)。

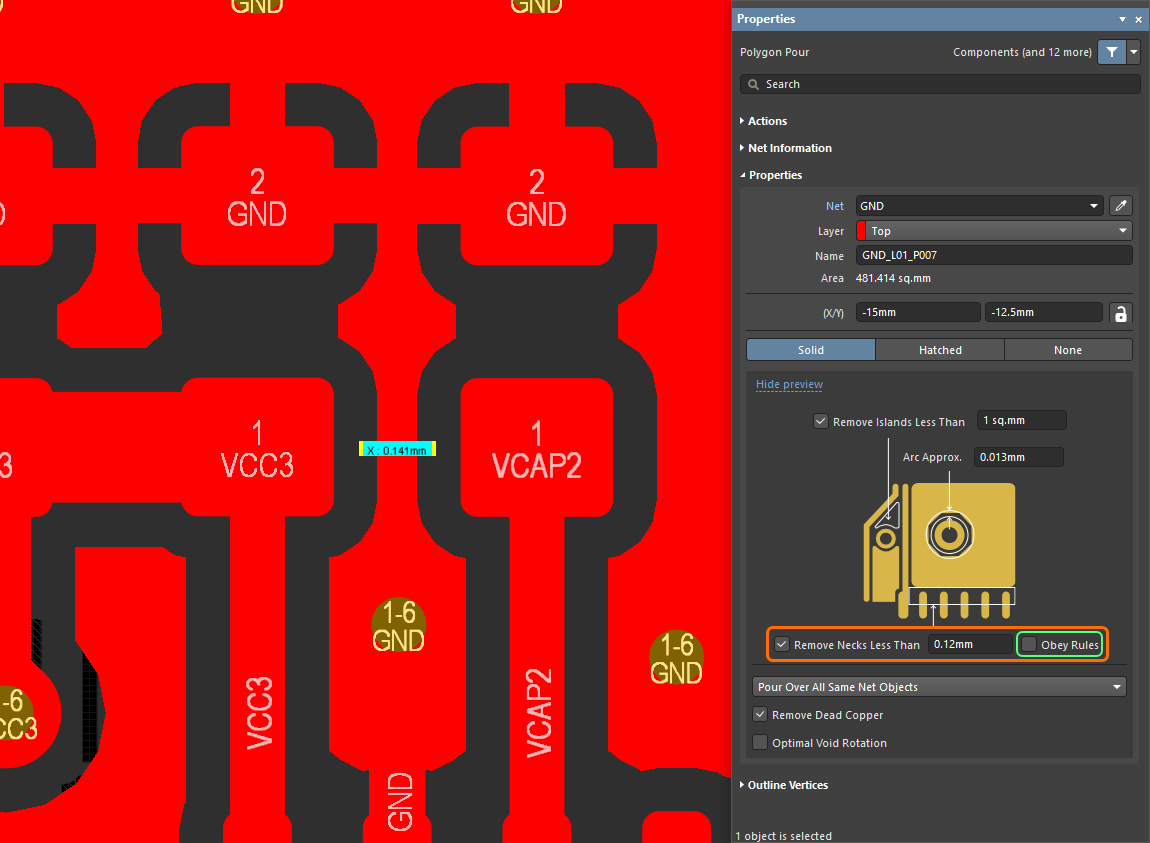

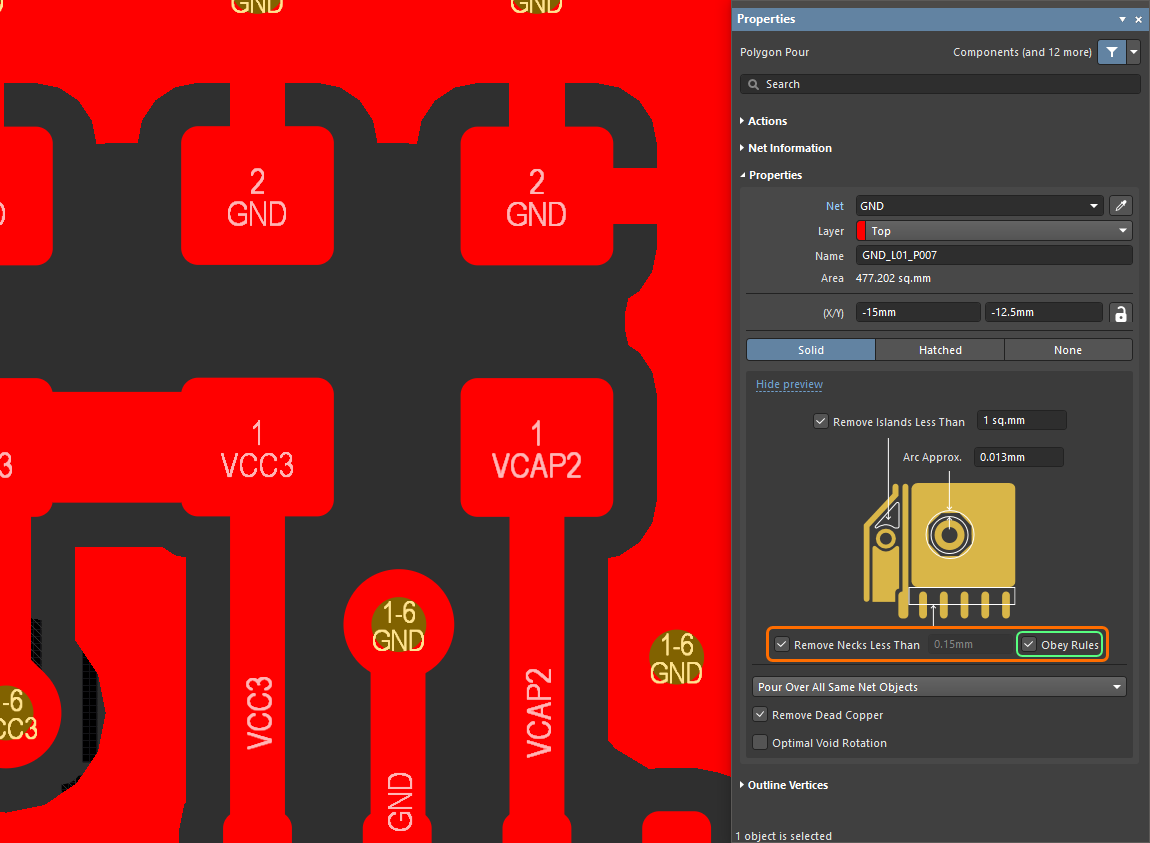

添加了适用于多边形铺铜属性的‘Obey Rules’选项

对于已放置的实心多边形铺铜,新的“Obey Rules”选项可作为其属性的一部分,在移除小于特定宽度的颈部时使用该选项。默认情况下对新多边形启用,它从适用的最小宽度约束中获取值。

当将多边形铺铜的Obey Rules选项禁用时,允许的颈部最小宽度将由Remove Necks Less Than字段确定。在本示例中,该值为0.12毫米,而允许的颈部宽度约为0.14毫米。

当启用Obey Rules选项时,允许颈部的最小宽度由适用的“宽度”约束中的最小宽度值决定。在本例中,该值为0.15mm,小于此值的颈部将被移除。

约束管理器改进

添加了指令同步状态指示

在本次发布中,添加了Constraint Manager内约束与原理图上已放置指令中定义的等效约束之间的同步状态指示器。

-

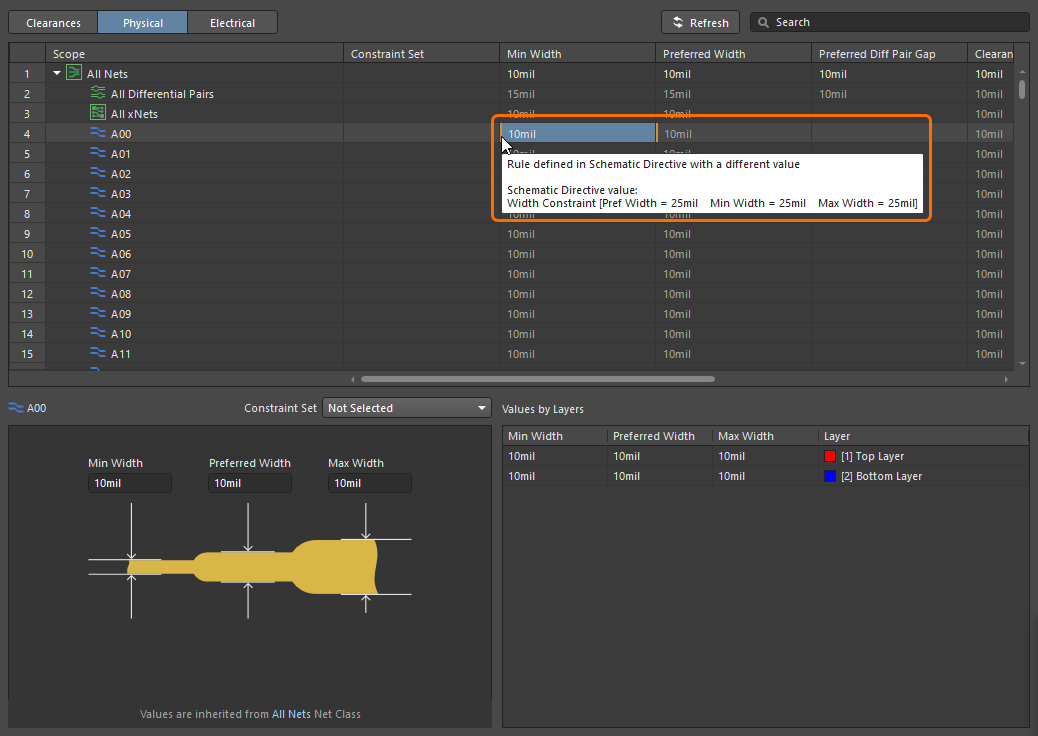

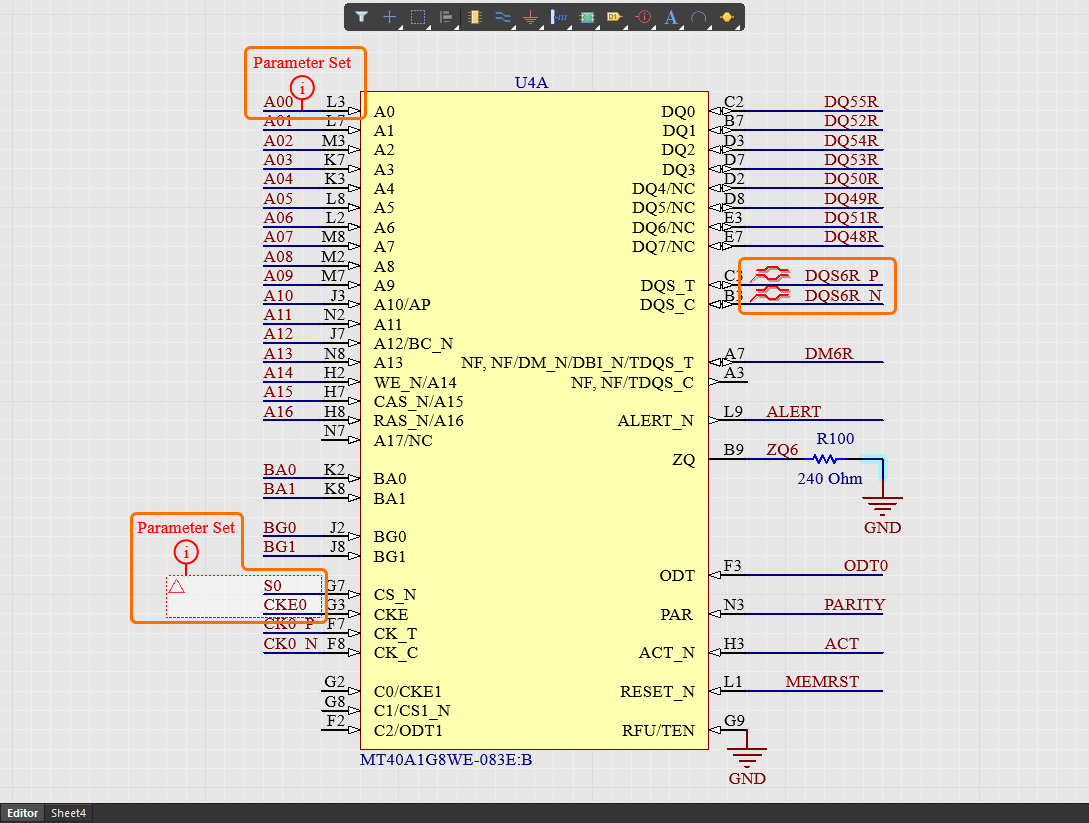

如果已将参数集或差分对指令放置到原理图中的某个对象上,且该指令的约束值不同于Constraint Manager中针对同一对象定义的值,则当从原理图访问Constraint Manager时,将在Constraint Manager的Physical或Electrical视图中的相应单元格左侧,使用橙色指示条对这些值进行标记(例如,

)。

)。 -

当约束值在Constraint Manager与指令之间实现同步时,指示条将变为绿色(例如,

)。

)。

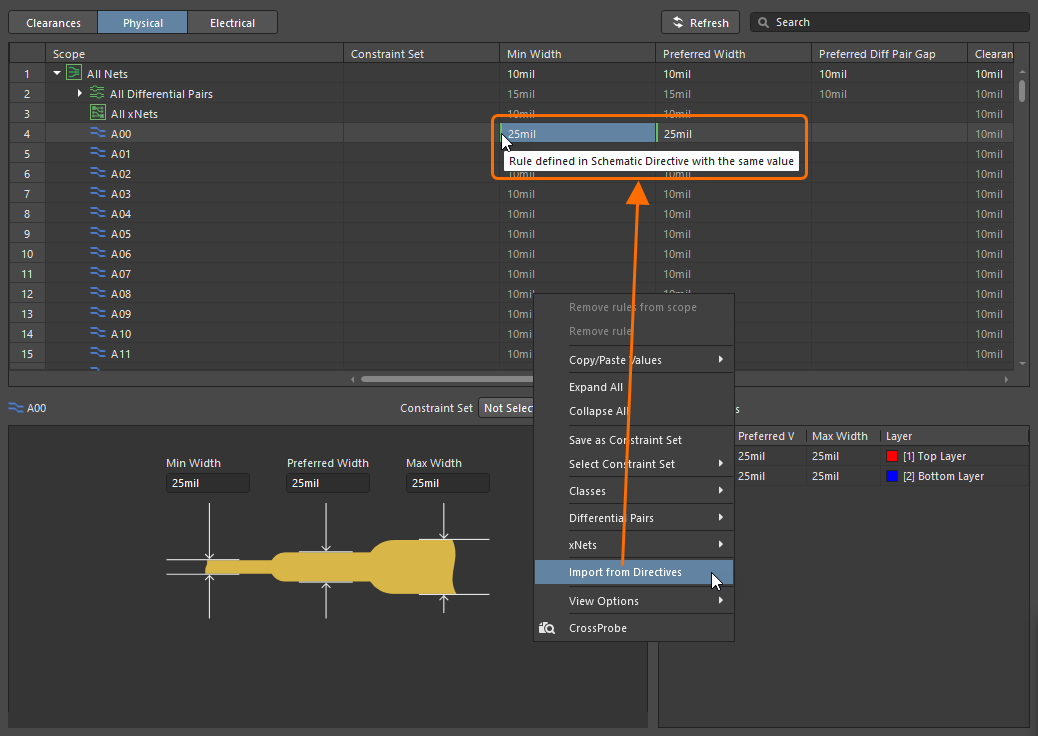

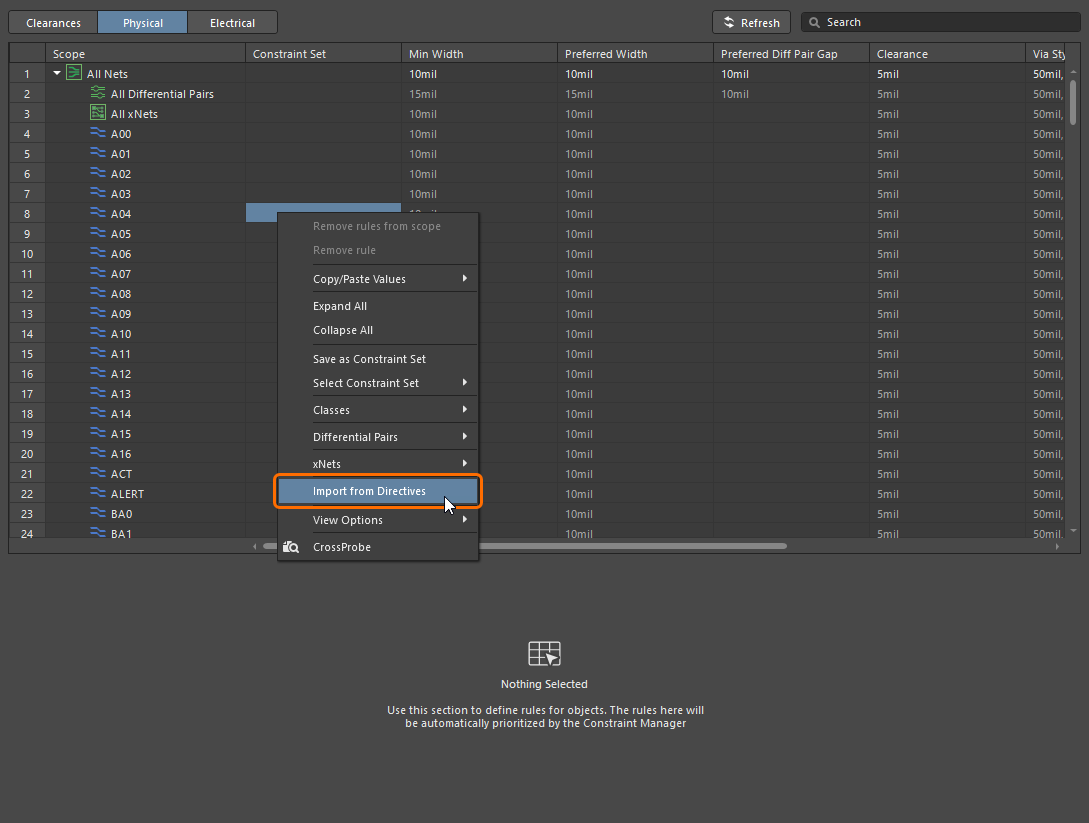

当对象不含现有约束时,请使用视图右键菜单中的Import from Directives命令,将数据从指令导入到Constraint Manager。请注意,如果在使用Import from Directives命令后,在Constraint Manager中针对已与指令同步的约束值进行了编辑,则在随后再次使用Import from Directives命令时,该约束值将不会进行同步。

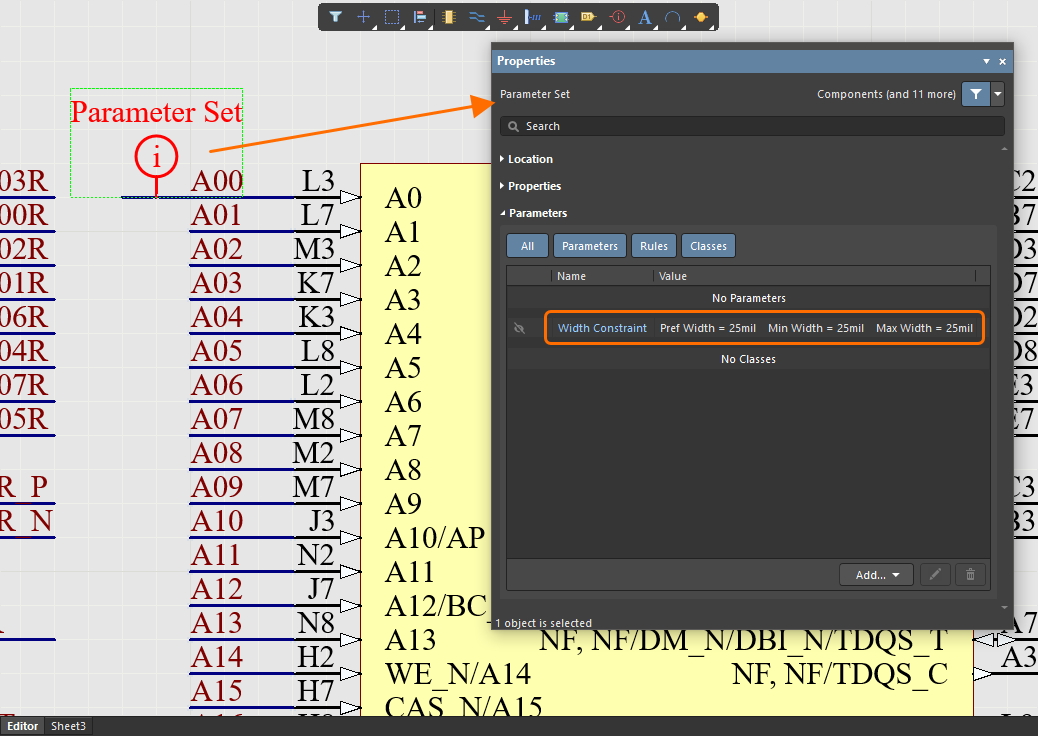

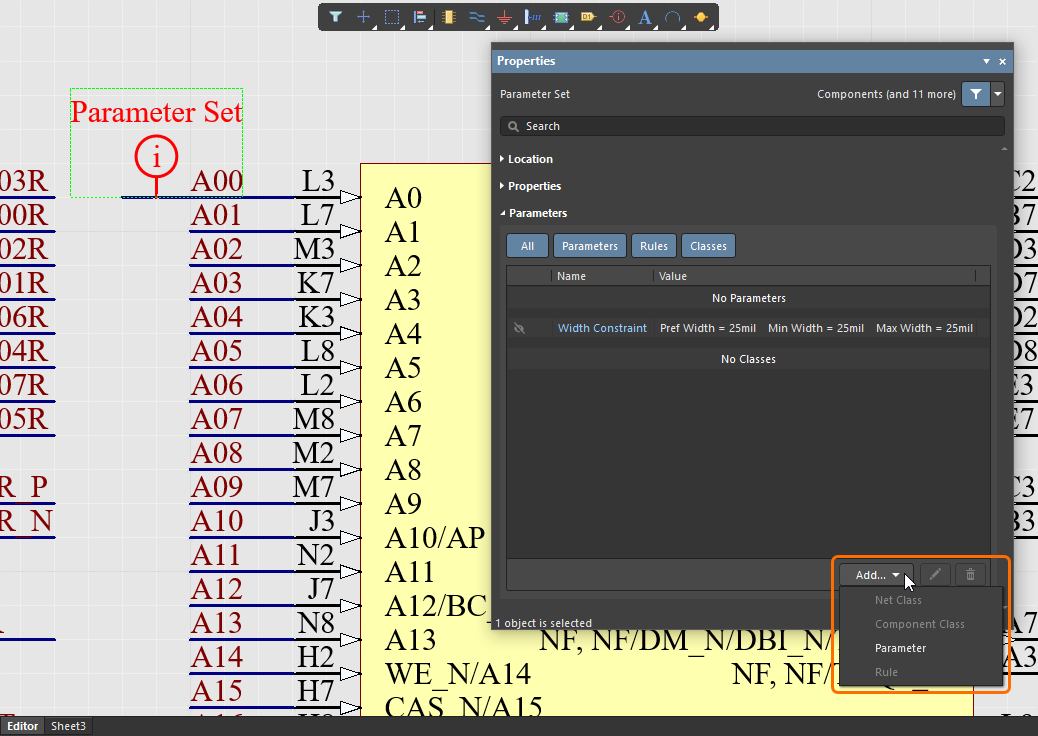

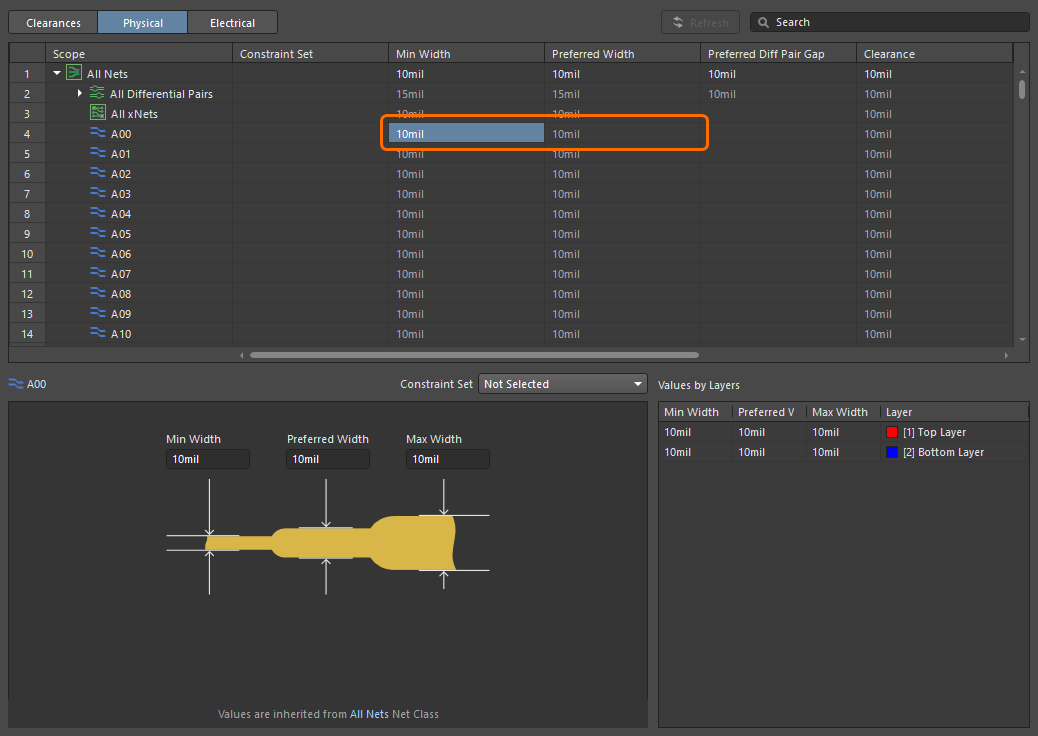

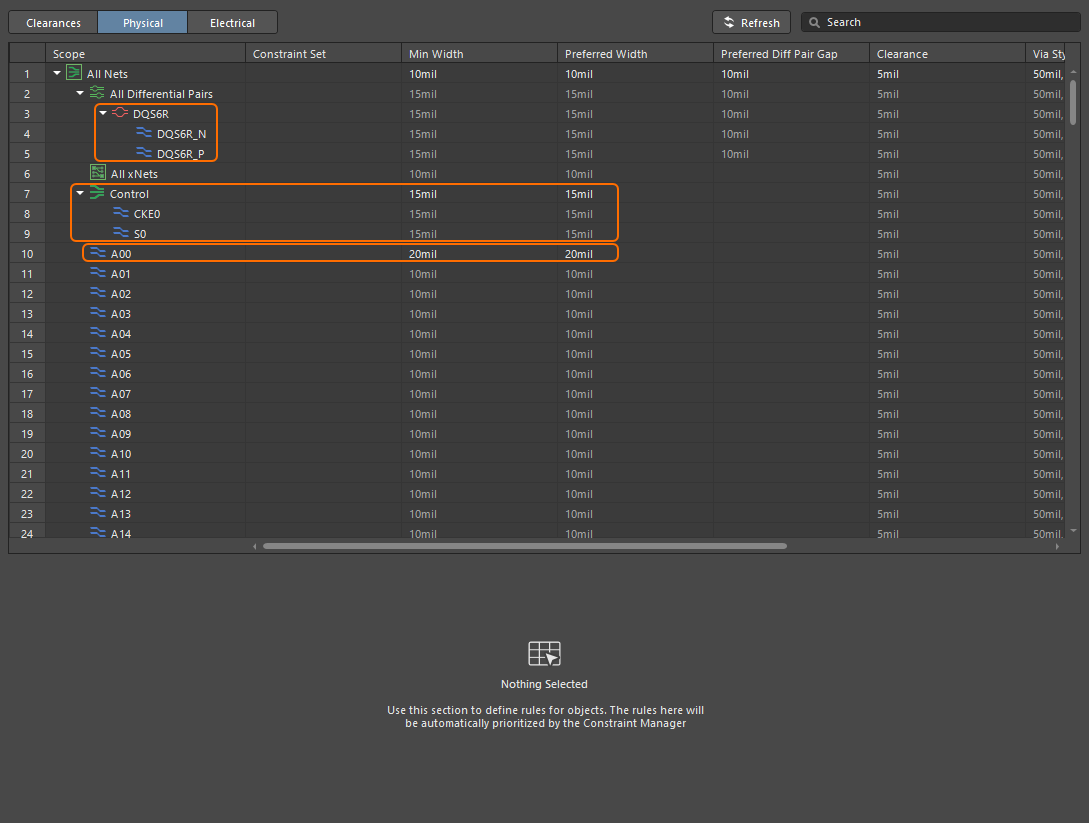

Net A00上放置了一个Parameter Set指令,且该指令被分配了一个Width约束。

在约束管理器的物理视图中,与Net A00的宽度约束相关的单元格有一个橙色条,表示这些值与指令不同步。

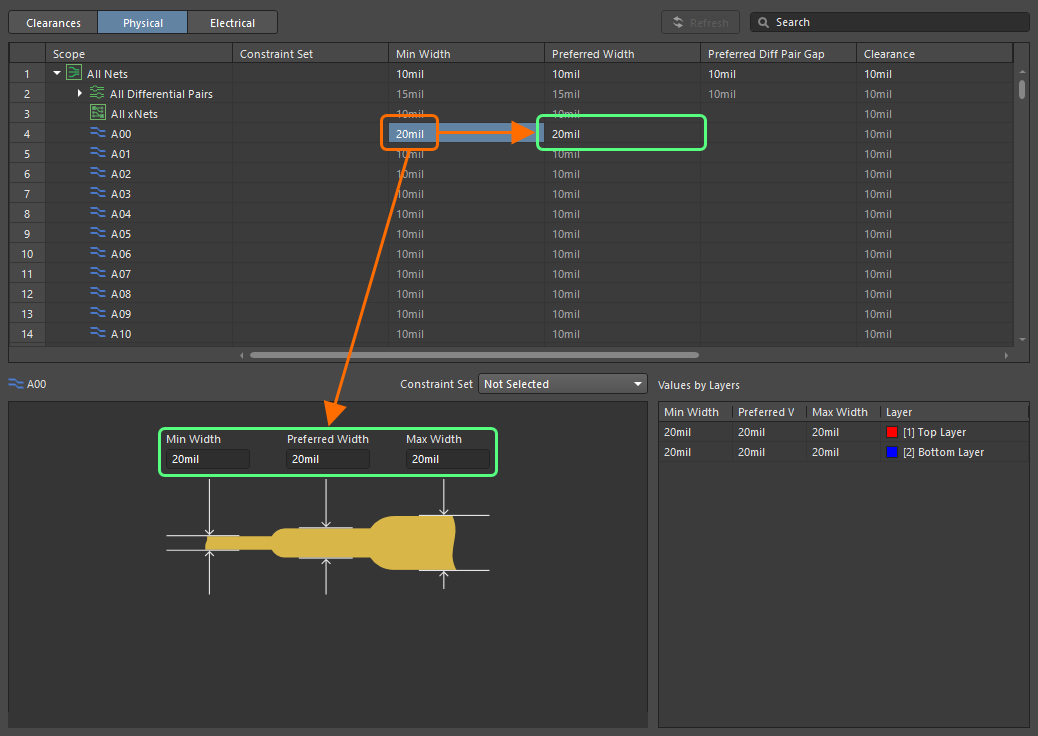

使用Import from Directives命令后,指令中的数据将被导入到约束管理器中,此时单元格将显示一个绿色条,表示这些值与指令同步。

请注意,在指令属性中,用于添加、编辑和删除类别和规则的控件现在已变为灰色,无法操作。

传播宽度/间距值

现在将在Constraint Manager的Physical视图中,通过顶部栅格将单个网络或xNet(Min Width或Preferred Width)、差分对(Min Width、Preferred Width或Preferred Diff Pair Gap)或网络/xNet/差分对类的输入值传播到以下约束区域内的相应宽度(Min Width/Preferred Width/Max Width)或间距(Min Gap/Preferred Gap/Max Gap)字段。请注意,仅当对象未定义特定规则时,输入值才会被传播到其他字段。

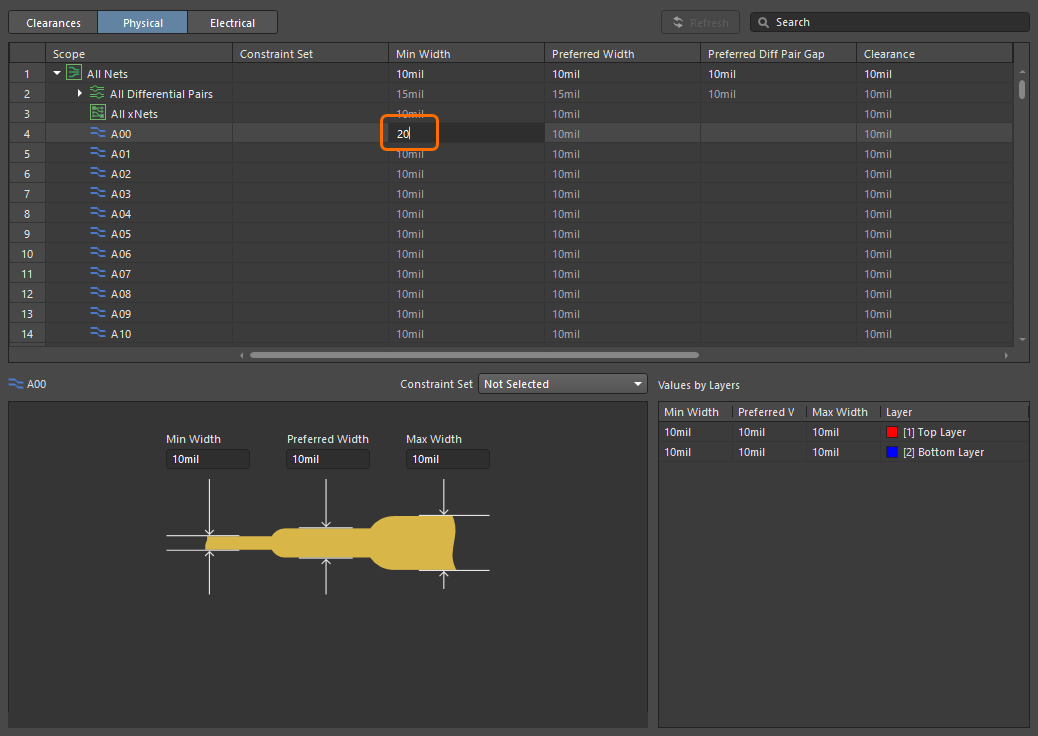

Net A00目前尚未被分配宽度约束(即,将从All Nets网络类继承这些约束)。

在网络的宽度约束中输入一个值后(例如,在本例中为“最小宽度”约束)...

...该值将传播到宽度约束的其他字段(首选宽度和最大宽度)。

Draftsman改进

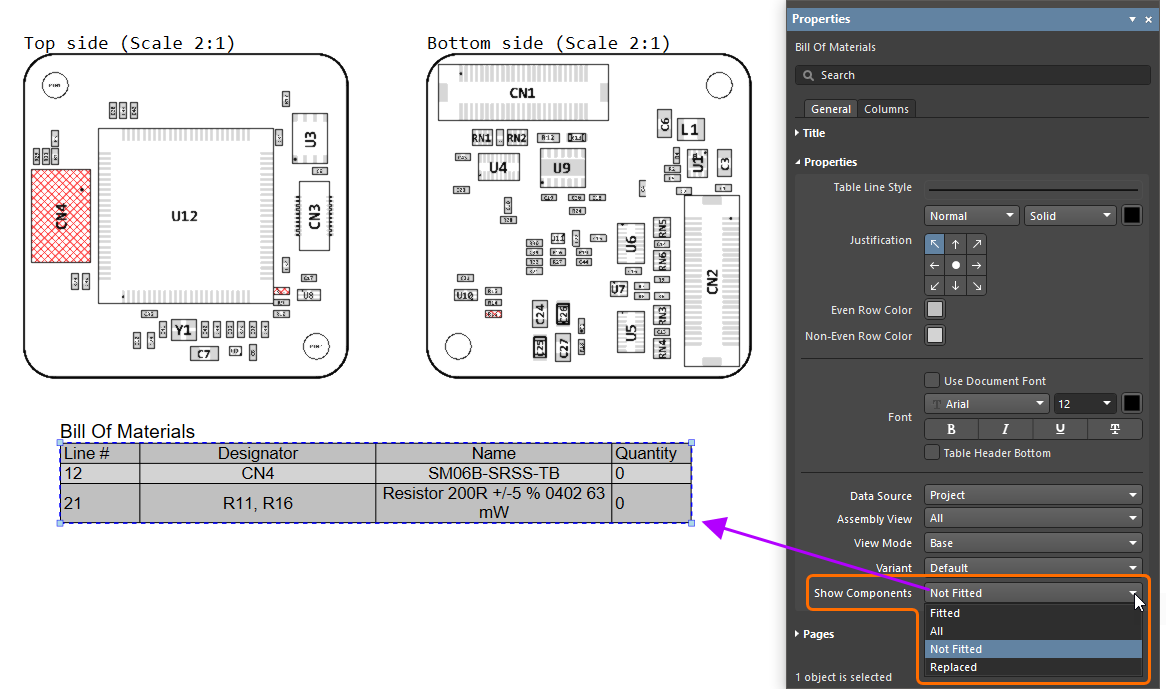

在BOM表中仅显示未安装元件

现在支持将BOM表放置到为PCB设计项目(*.PCBDwf)创建的制造图中,并仅显示当前所选设计变量的Not Fitted元件。为此,请从Properties面板的Show Components下拉列表中,选定所选BOM表的Not Fitted选项。

您还可以从下拉列表中选定Replaced选项,以仅显示已为其选定备用部件的元件或在当前变量中具有不同参数值的已安装元件。

数据管理改进

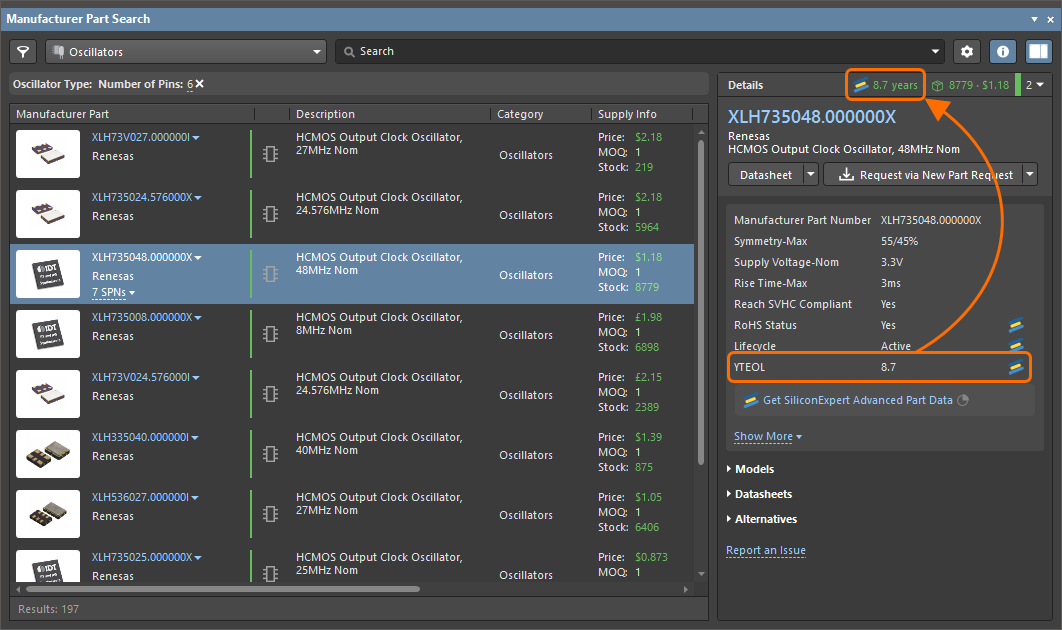

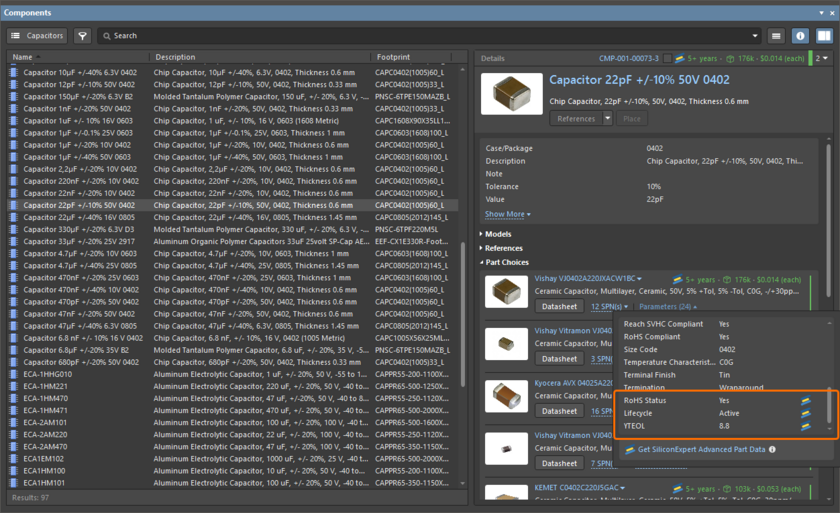

显示SiliconExpert YTEOL参数的实际值

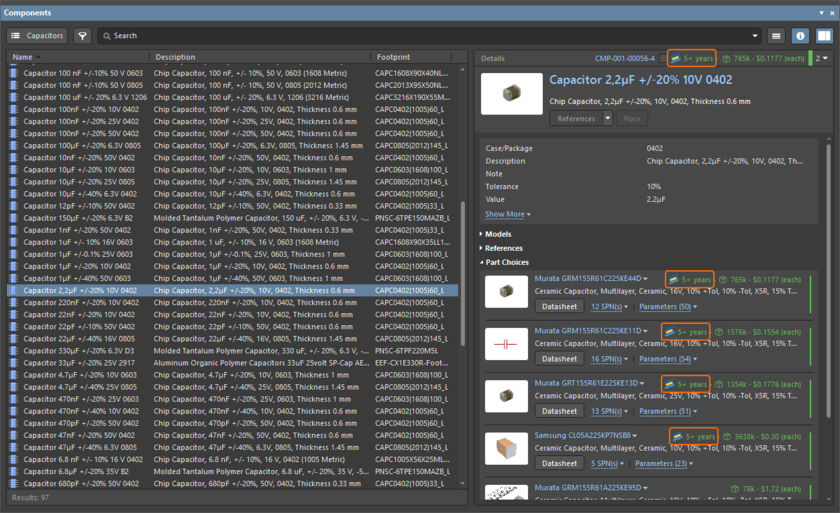

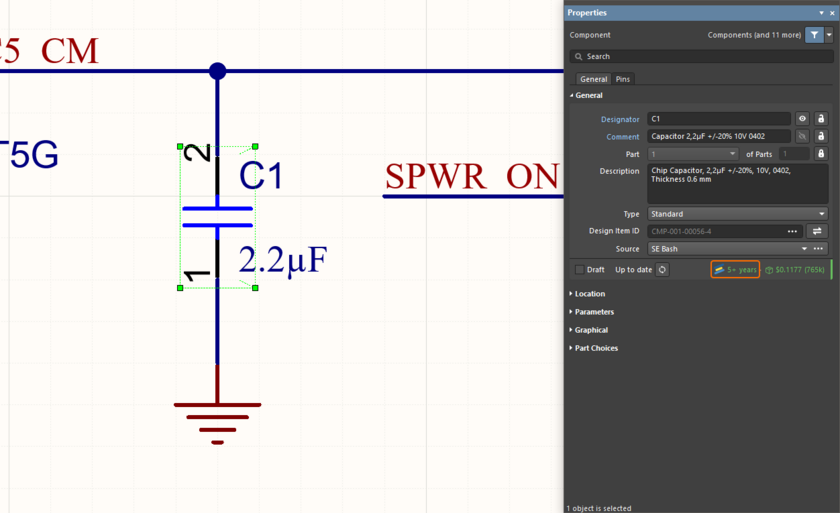

当某个部件具有由 SiliconExpert 提供的值大于 5 年的 YTEOL 参数时,该参数的实际值现在会显示在显示该部件的汇总数据的所有位置(例如,制造商中“详细信息”窗格的标题)零件搜索或元件面板,或零件选择)而不是 5 年以上条目。

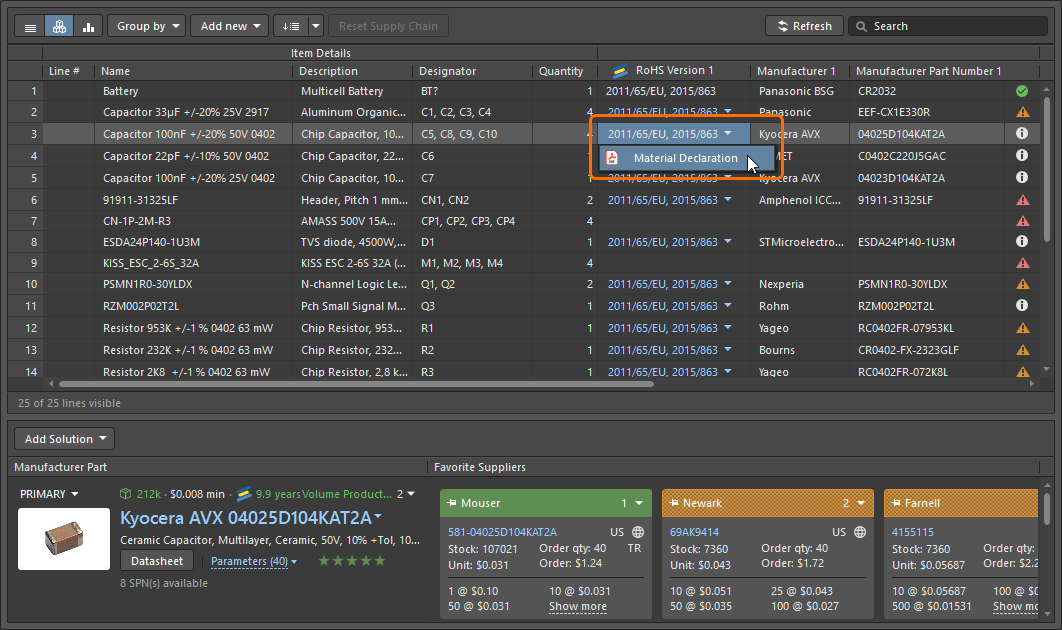

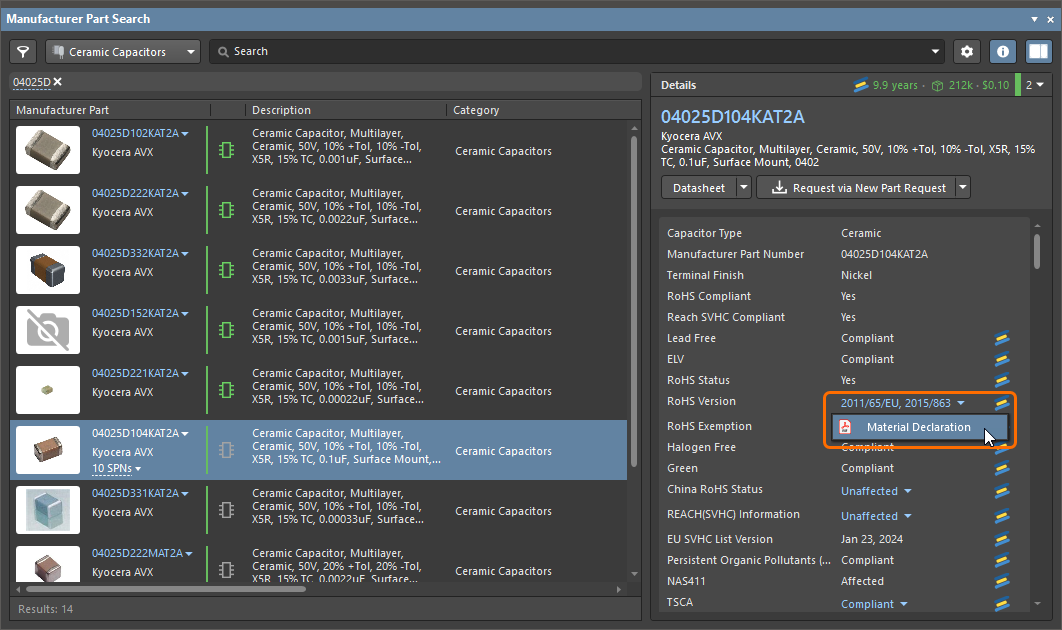

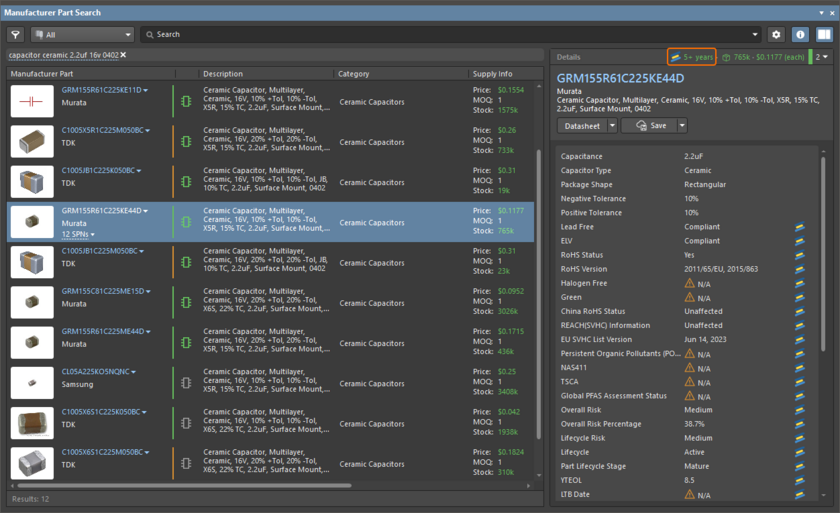

SiliconExpert合规性数据表单引用

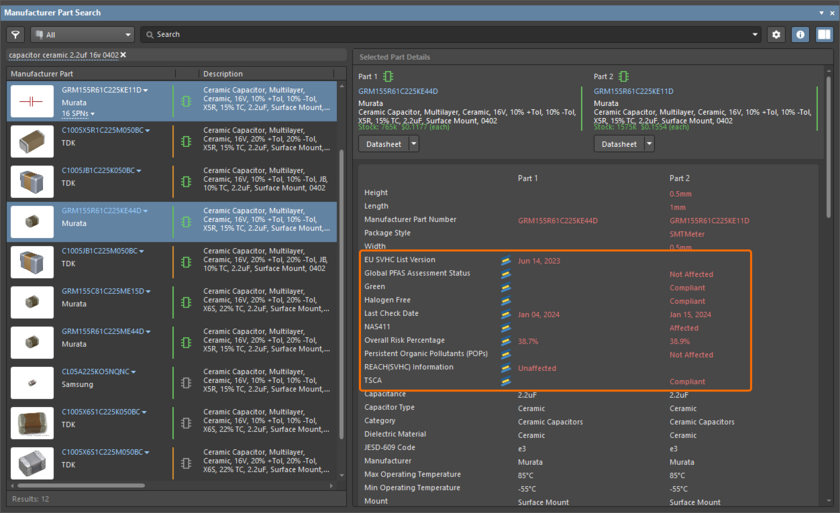

添加了对SiliconExpert合规性数据表单引用的支持,其中这些数据表单可用于使用SiliconExpert数据的各个位置,包括ActiveBOM(*.BomDoc)、Manufacturer Part Search、Components和Explorer面板,以及通过Output Job(以PDF或Excel格式)生成BOM输出时。

通过ActiveBOM文档访问合规性数据表单示例。

通过Manufacturer Part Search面板访问合规性数据表单示例。

显示工作区内容的条目名称

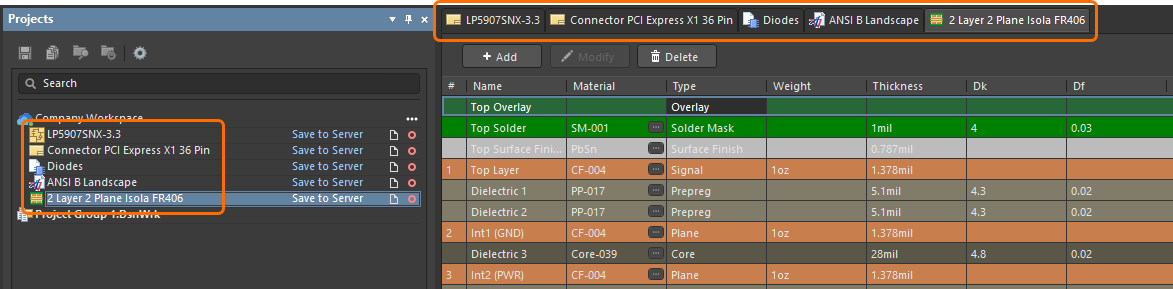

对于可直接进行编辑的Workspace内容类型,现在将在Projects面板和文档选项卡中显示正在进行创建、克隆或编辑的条目名称,而不是其Item-Revision ID。

进行Workspace内容(原理图片段、托管原理图、元件模板、Draftsman图纸模板和层堆栈)编辑并在Projects面板和文档选项卡中显示条目名称示例。

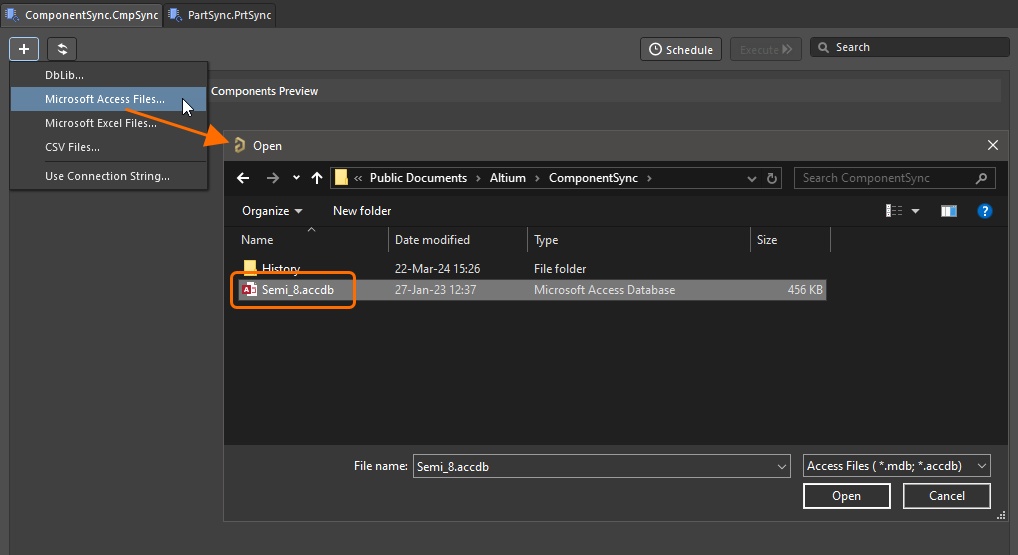

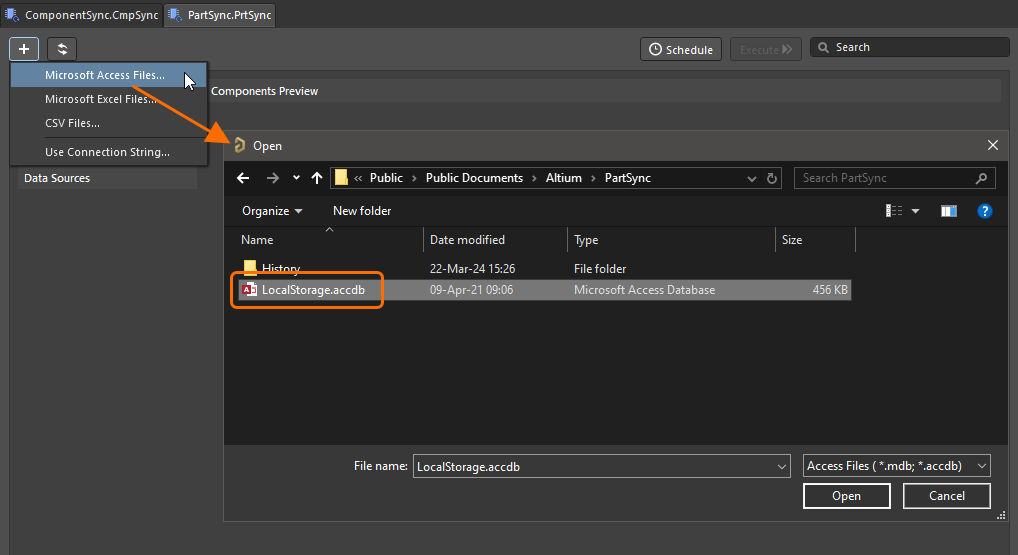

添加了对最新MS访问数据库文件格式的支持

当使用Database to Workspace元件同步(*.CmpSync)和部件供应商同步(*.PrtSync)功能时,现在可以将具有最新MS Access数据库格式(*.accdb)的文件用作数据源。

Altium Designer 24.4中完全公开的功能

以下功能现已在本次发布中正式Public:

- Self-intersected Regions的渲染 – 自22.8版开始提供

- 防止Self-Intersections – 自22.8版开始提供

- 元件模板继承功能 – 自23.10版开始提供

Altium Designer 24.3

发布日期:2024年3月19日 - 版本24.3.1(Build 35)

PCB设计改进

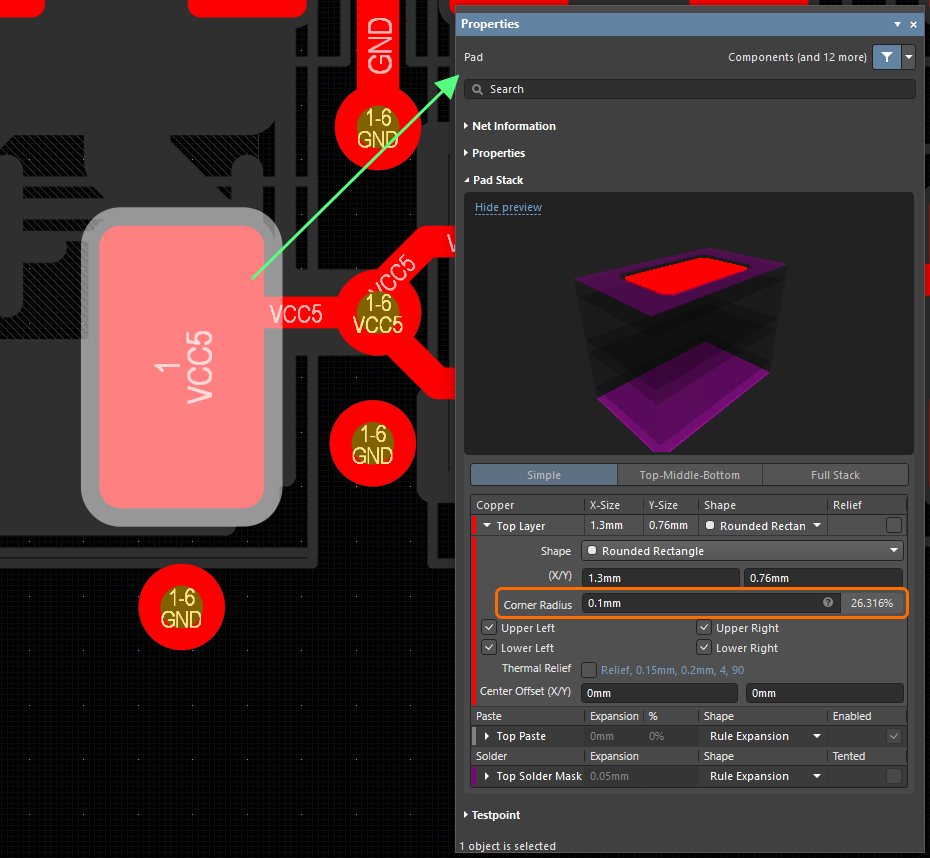

在本次发布中,我们新增了将焊盘转角半径/倒角定义为绝对值(单位:密耳或毫米)的功能。

当在PCB或PCB Footprint编辑器中选择Rounded Rectangle或Chamfered Rectangle作为焊盘形状(在铜质电路层、助焊层或阻焊层上)时,在Corner Radius字段输入一个值,以将半径/倒角定义为绝对值(带默认测量单位)。请注意,焊盘转角半径/倒角的绝对值必须小于或等于焊盘最短边的一半。计算得出的百分比值将显示在字段右侧。

在Corner Radius字段中输入一个值,以将其定义为绝对值。

输入一个值,后跟 % 符号,将半径/倒角定义为焊盘最短边一半的百分比(与以前的版本相同)

PCB List和PCBLIB List面板、Find Similar Objects对话框,以及Pad/Via Template编辑器亦支持定义焊盘转角半径/倒角绝对值。另外,现在还可以在查询表达式中使用下列关键词:

| KEYWORD | SUMMARY |

|---|---|

|

|

返回相应层上Pad Corner Radius Size属性符合查询条件的焊盘对象。 |

|

|

返回相应层上Pad Corner Radius Uses Percent属性符合查询条件的焊盘对象。 |

另外,Import Wizard现在亦支持在导入Xpedition设计时,将焊盘转角半径/倒角定义为绝对值。

PCB复制改进

增强的错误通知

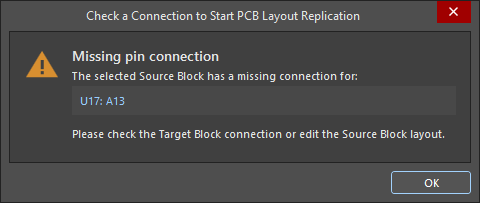

运行Layout Replication工具时,如果检测到选定Source Block中的管脚连接丢失,则警告对话框将通知您连接丢失。

单击对话框中的链接,交叉探测违规对象。

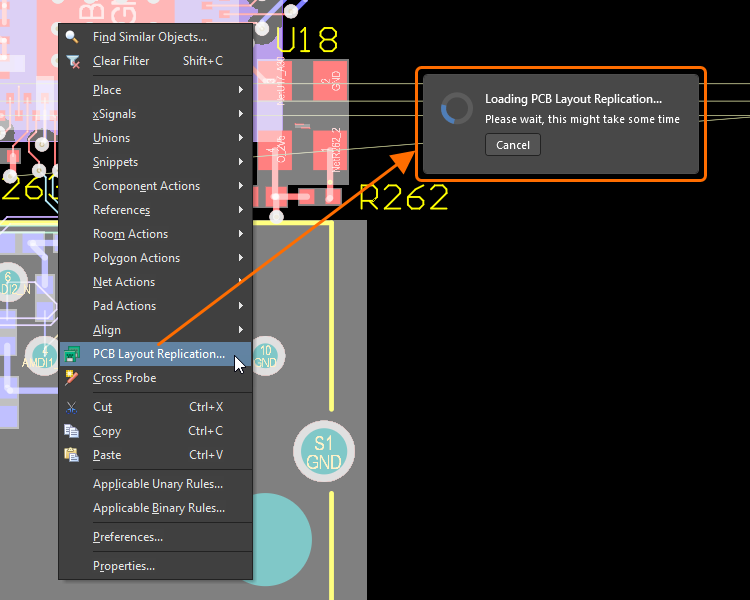

为PCB复制添加了“忙碌”状态

为了提升PCB复制过程用户界面的响应性,在本次发布中,添加了功能“忙碌”状态指示器。

-

运行Layout Replication工具时,在打开PCB Layout Replication对话框之前,屏幕上会出现正在加载复制数据的指示,以及取消复制的选项。

-

点击PCB Layout Replication对话框中的Replicate按钮后,在放置第一个块(或准备在交互模式下放置)之前,光标会指示‘in progress' (

)。

)。

约束管理器改进

添加了对导入设计指令的支持(公测版本)

现在,您可以将设计指令的约束(在源文档中放置和定义)导入Constraint Manager中。您可以使用Directives命令的新Import(通过右键上下文菜单),从Physical或Electrical视图中执行此项功能。目前,该功能支持规则、网络类、差分对和差分对类指令。

已在一张原理图上放置了若干Parameter Set和Differential Pair指令,这些指令定义了一个差分对、一个网络类,以及Width规则。

已在一张原理图上放置了若干Parameter Set和Differential Pair指令,这些指令定义了一个差分对、一个网络类,以及Width规则。

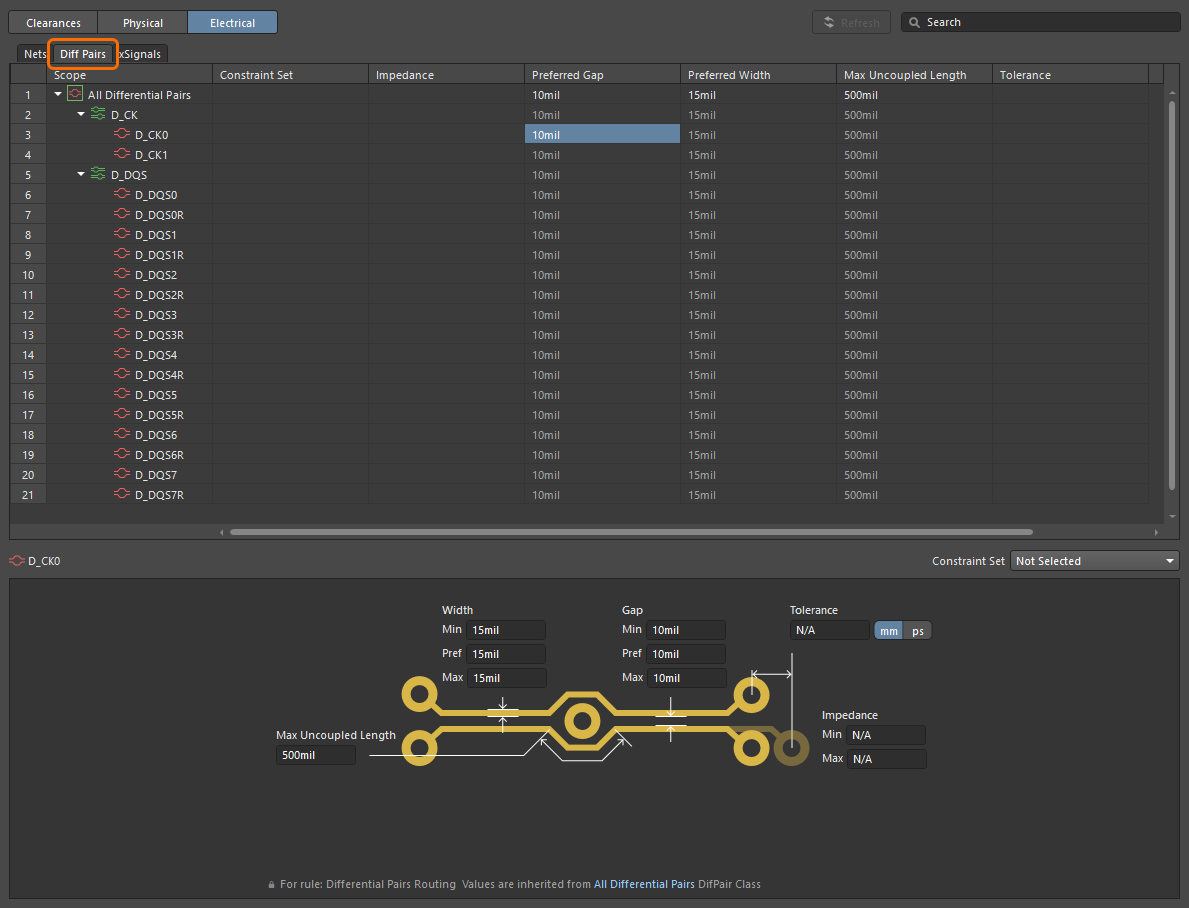

新增“差分对”选项卡

现在,在Electrical约束视图中新增了一个Diff Pairs选项卡,以便于清楚定义和管理差分对。该选项卡将显示设计中所有差分对的分级列表。为差分对或差分对类选择一个单元格,以便在Constraint Manager底部区域展示适用于该差分对或差分对类的约束。

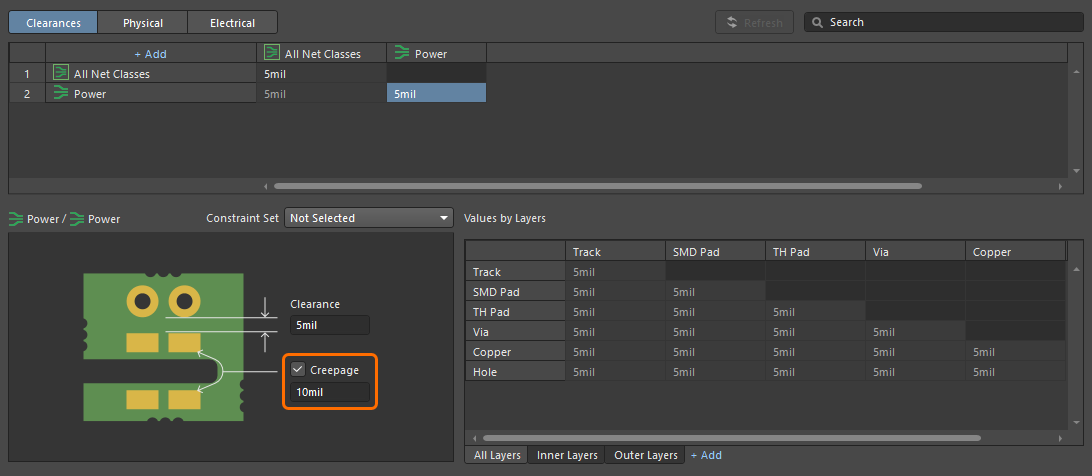

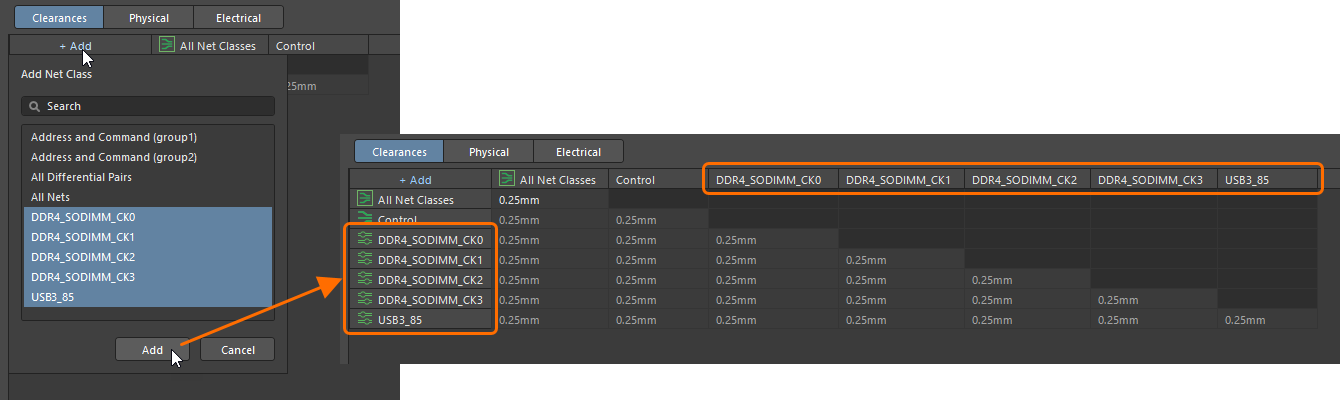

在间距矩阵中支持爬电距离

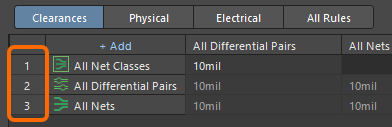

现在,当定义网络类和/或差分对间的电气间距时,可以使用Clearances视图中的矩阵,对Creepage规则作出规定。

在间距矩阵中支持多重编辑

在间距矩阵(Clearance视图)中添加了对在选定的同一行/列内进行多重编辑的支持。在Constraint Manager的详细间距设置中,选择一行或一列,键入所需值,然后按Enter或单击,将该值应用于该行/列所有单元格。

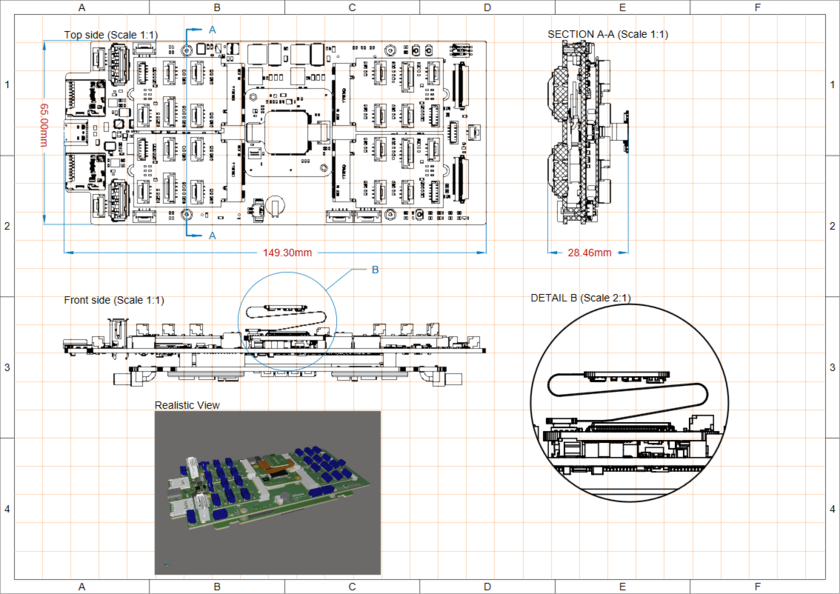

Draftsman改进

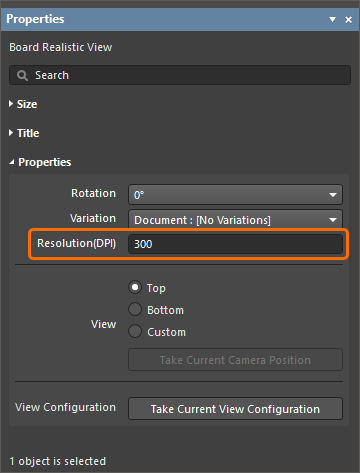

新增更改电路板写实视图分辨率的功能

现在,可以通过在Properties面板Properties区域的Resolution(DPI)字段中输入所需分辨率,对已放置的Board Realistic View分辨率进行配置。在此之前,电路板写实视图属于静态渲染图像,并且无法修改分辨率。最低分辨率为75 DPI,默认分辨率为300 DPI。

线束设计改进

型腔增强

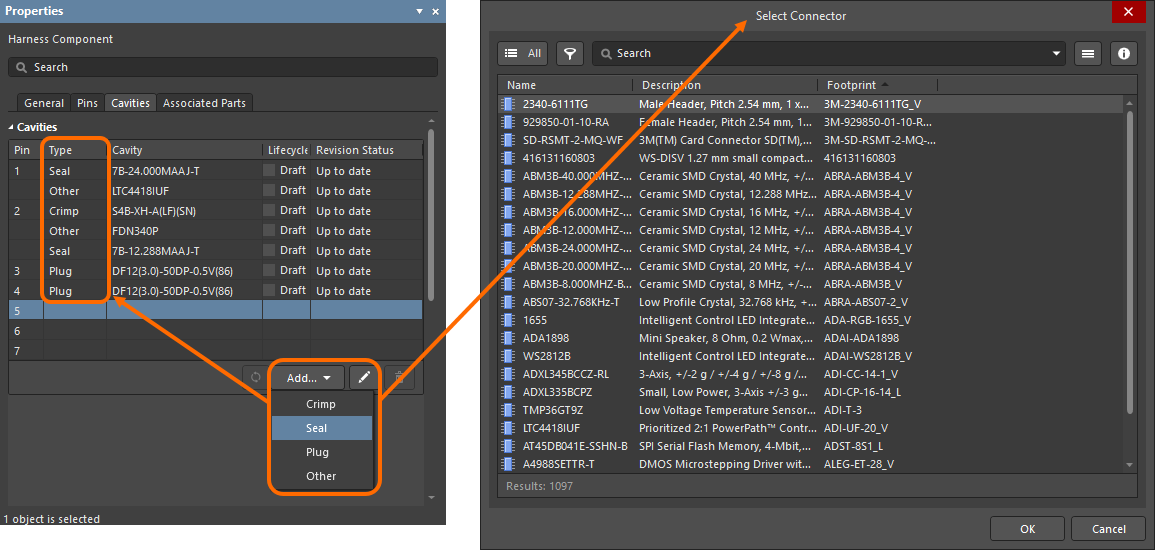

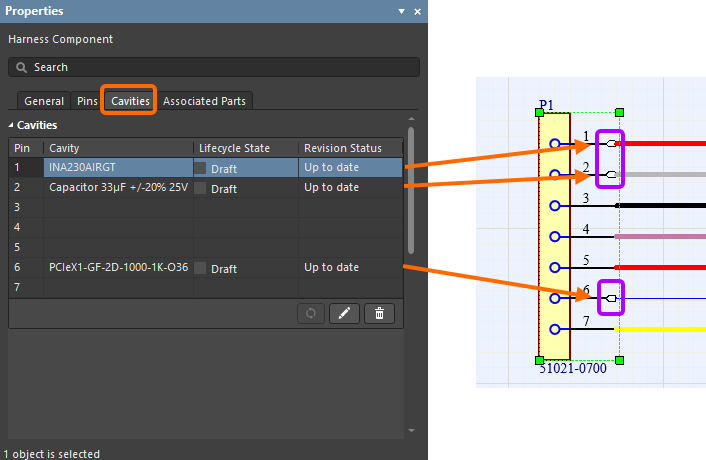

指定型腔类型

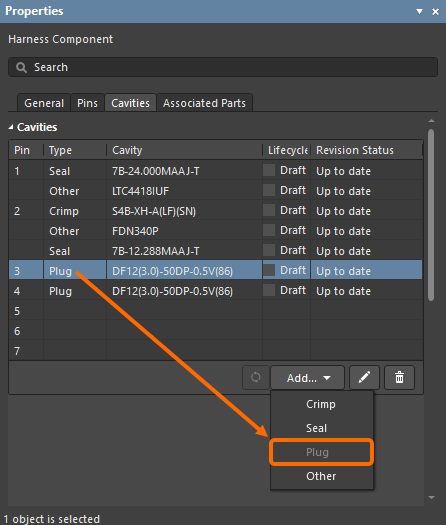

现在,您可以在Wiring Diagram(*.WirDoc)中,为线束元件的每个管脚指定型腔类型。在Properties面板的Cavities选项卡上,选择所需管脚,然后点击Add。从下拉菜单中选择型腔类型。在打开的Select Connector对话框中,为管脚选择所需的具体连接器。

仅允许为每个管脚添加一个型腔类型。添加具体的型腔类型后,下拉菜单中的对应入口变为不可用(变灰),具体如下图所示(Pin 3)。

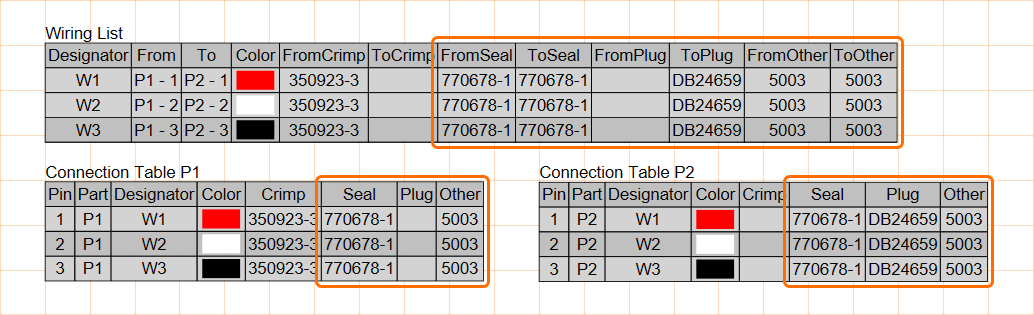

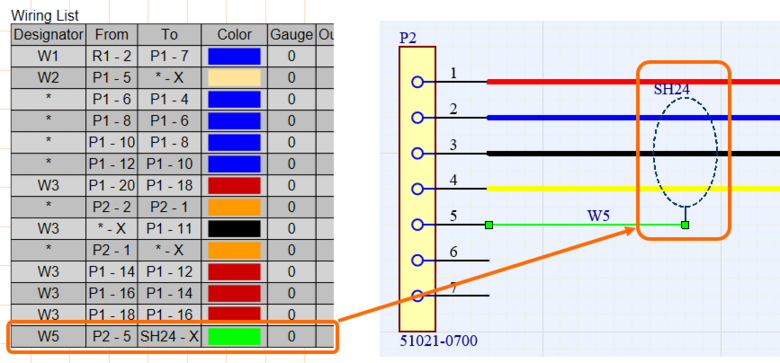

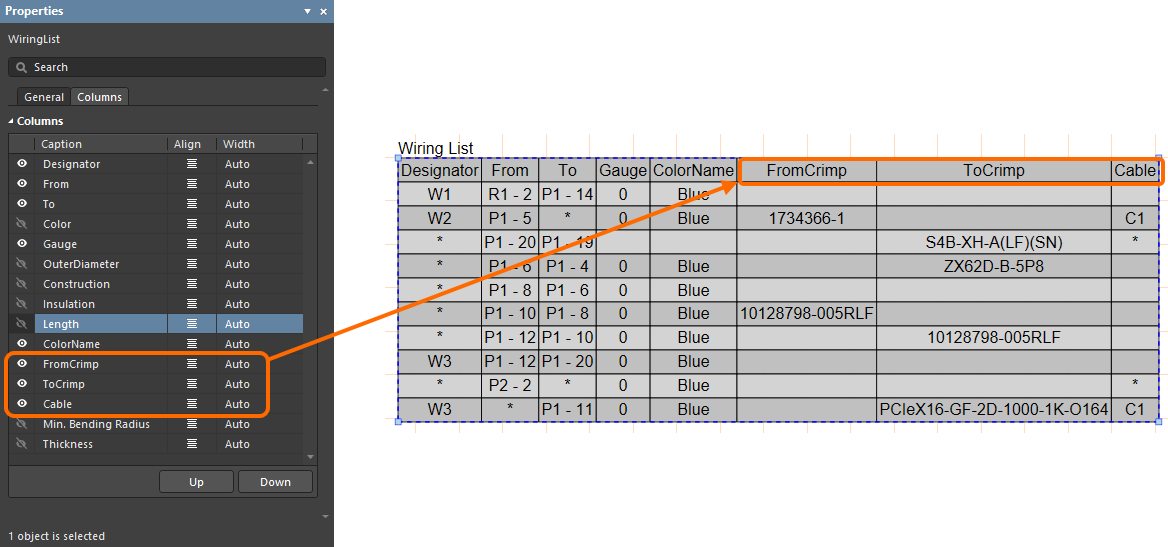

在布线列表和连接表中添加了新的型腔类型

现在,可以在制造图纸中的布线列表和连接表中显示密封件、插头和其他型腔部件。当在设计区内选中放置表时,在Properties面板Columns选项卡中启用所需列的可见性选项。

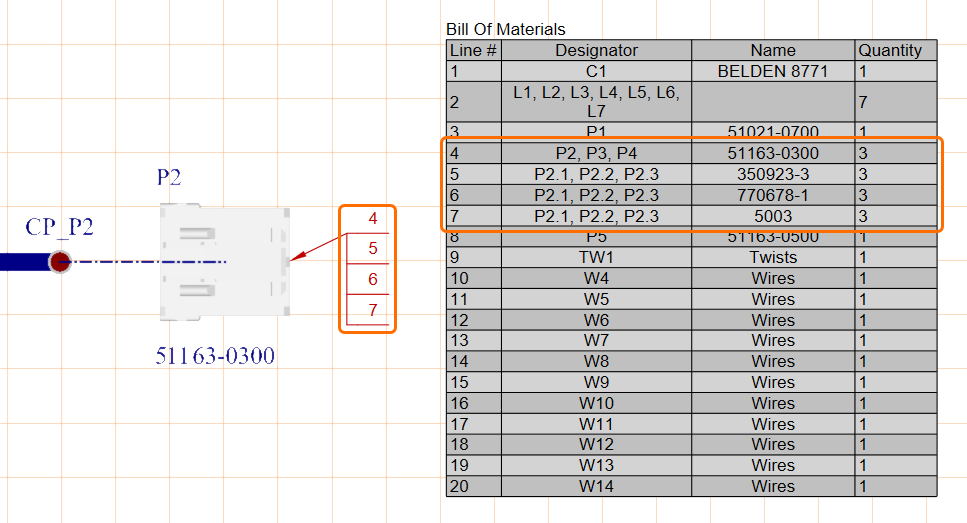

在制造图纸图注中添加了型腔BOM行号

为布局图纸视图上的元件物理视图添加设为显示BOM Item的图注后,该视图将包含所有已分配型腔的BOM行号。

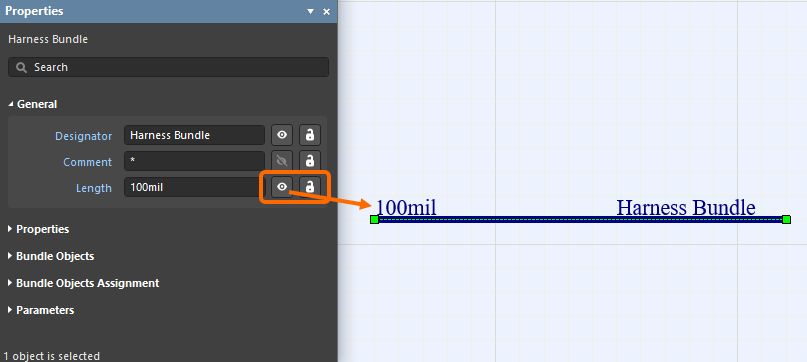

线束长度参数可视性和锁定选项

现在,Layout Drawing(*.LdrDoc)中的线束Length参数包含可视性和锁定选项。

高亮显示导线来自分接线缆的线束

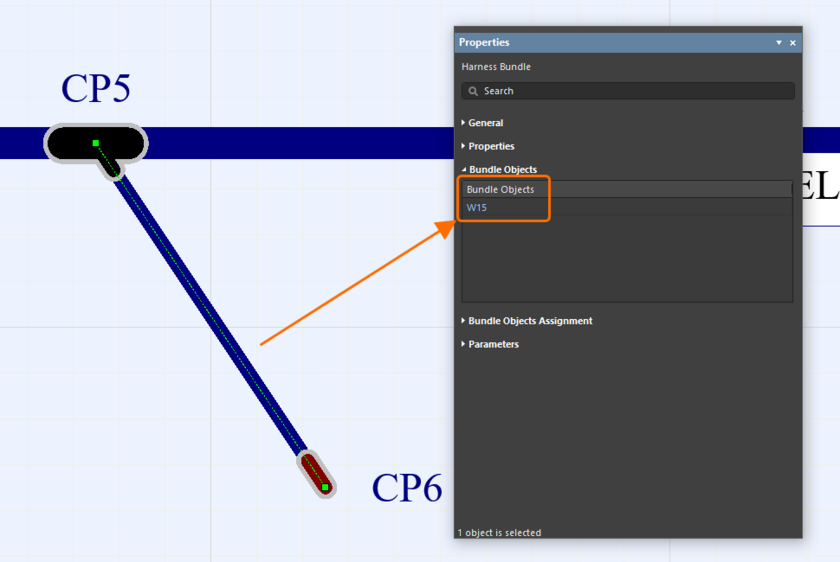

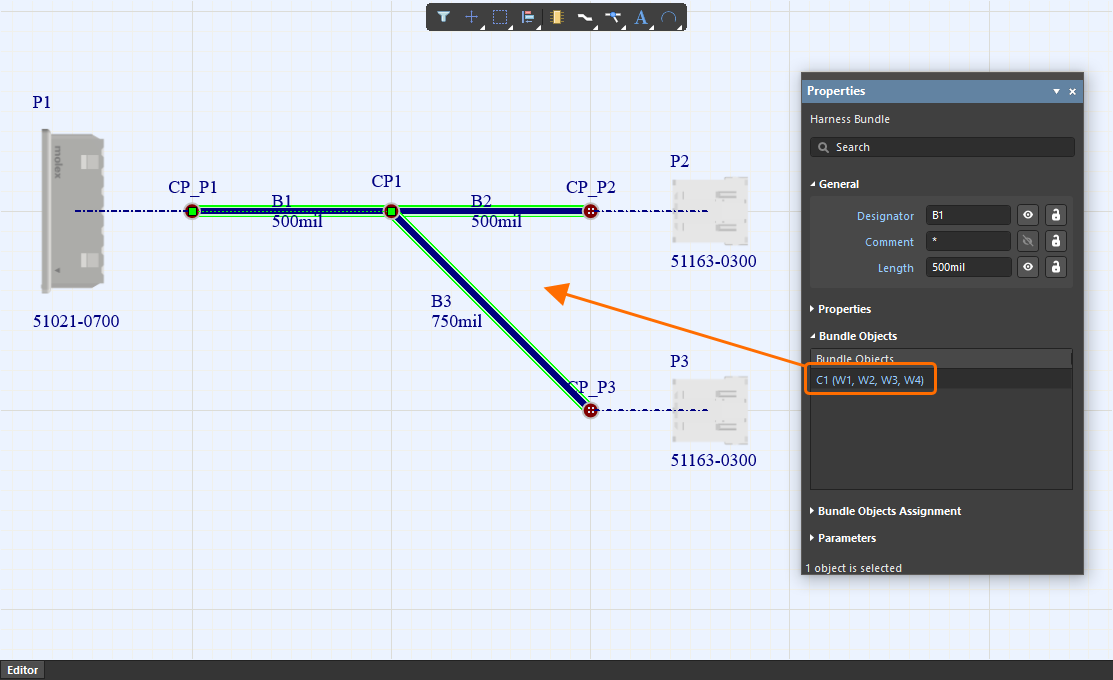

现在,当在Properties面板Bundle Objects区域中选中线缆后,Layout Drawing将高亮显示导线来自分接线缆的线束。对于分接线缆,最长导线的长度显示在BOM中。

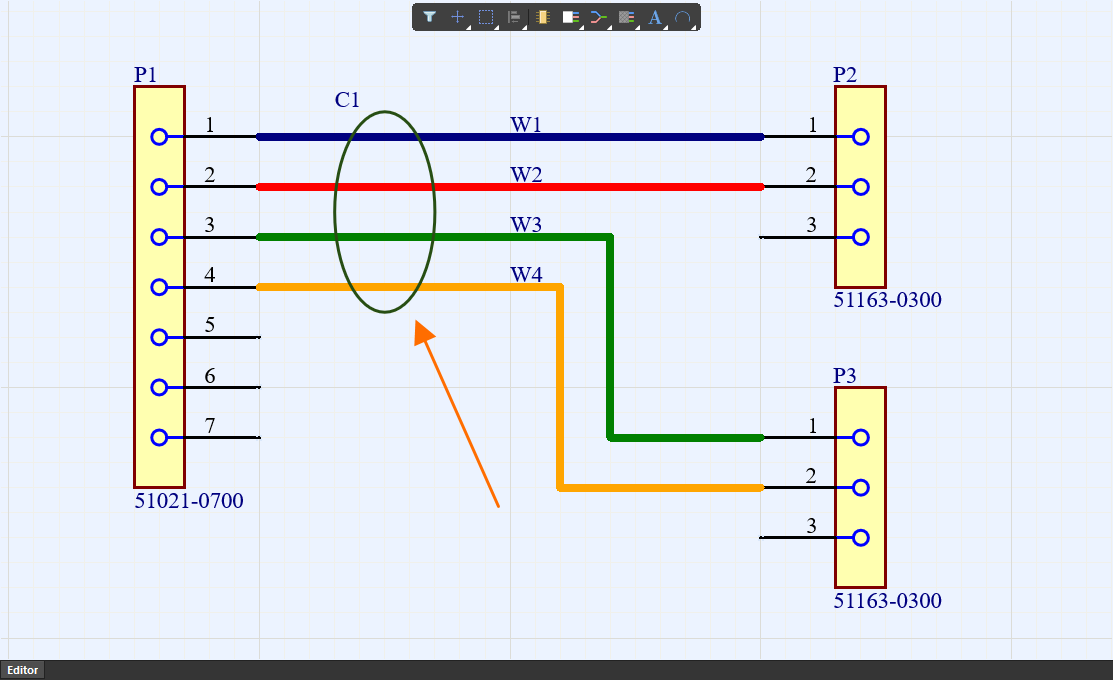

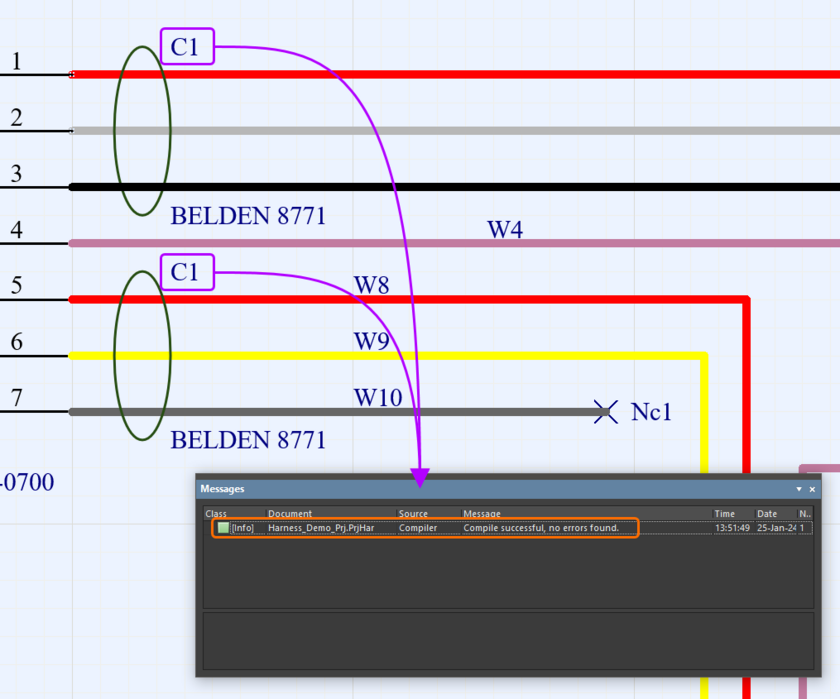

现在,当在所选线束的属性面板的“Bundle Objects”区域中点击线缆条目时,所有包含来自C1的导线的线束都会被高亮显示。

现在,当在所选线束的属性面板的“Bundle Objects”区域中点击线缆条目时,所有包含来自C1的导线的线束都会被高亮显示。

在BOM中,C1显示了最长导线的长度(在此示例中,该导线穿过线束B1和B3)。

在BOM中,C1显示了最长导线的长度(在此示例中,该导线穿过线束B1和B3)。

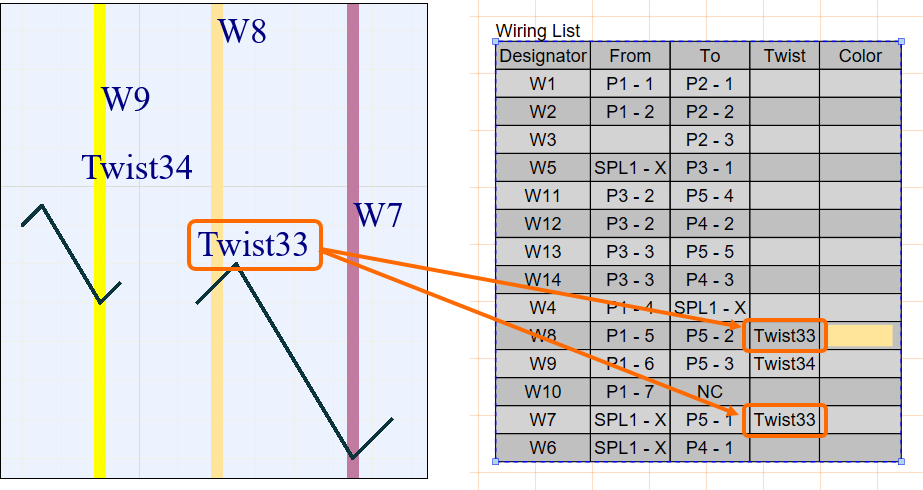

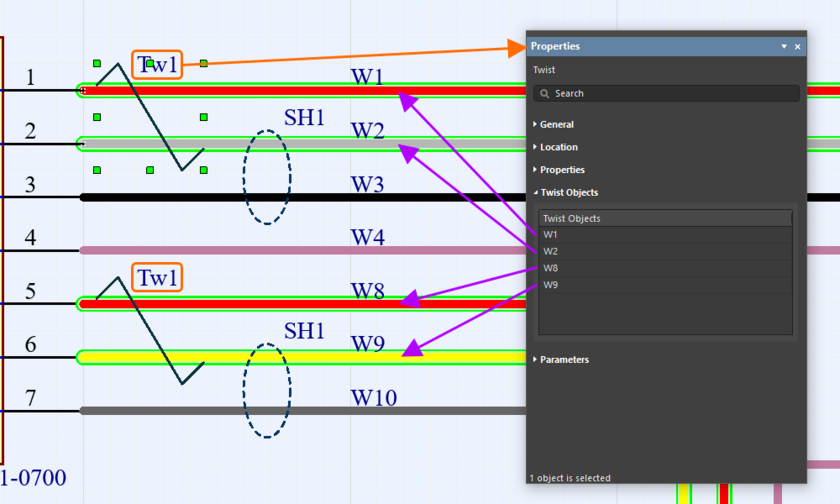

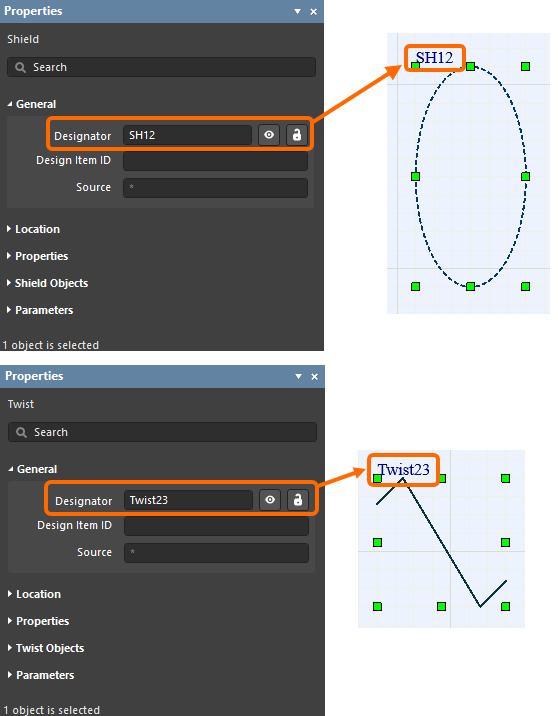

在布线列表中添加了绞合对象位号标识符

现在,绞合对象位号标识符会如下图所示,在布线列表中显示。

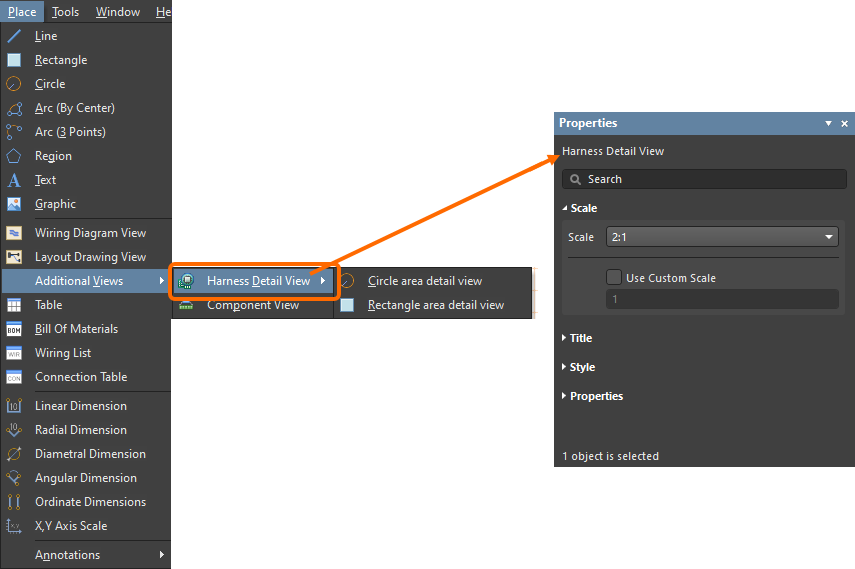

电路板详细视图重命名为线束详细视图

Harness Draftsman文档(*.HarDwf)中的Board Detail View重命名为Harness Detail View。

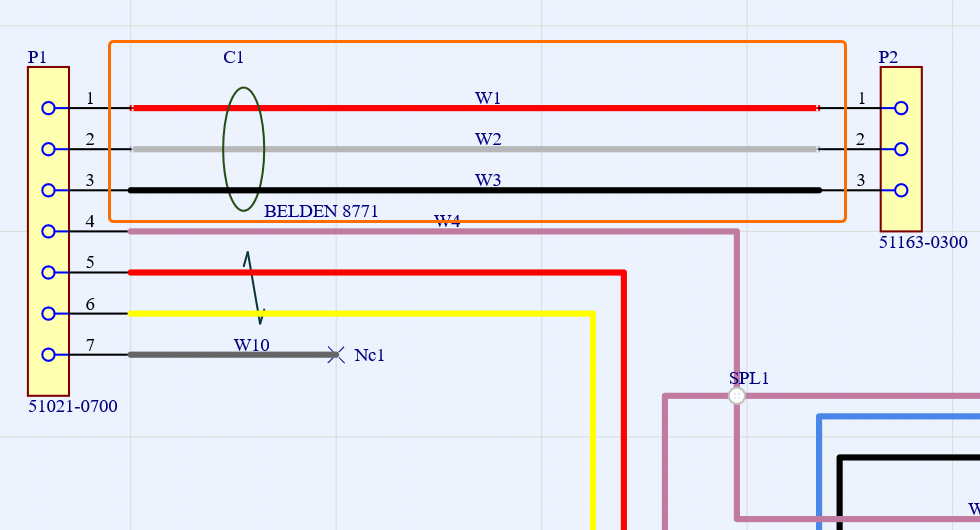

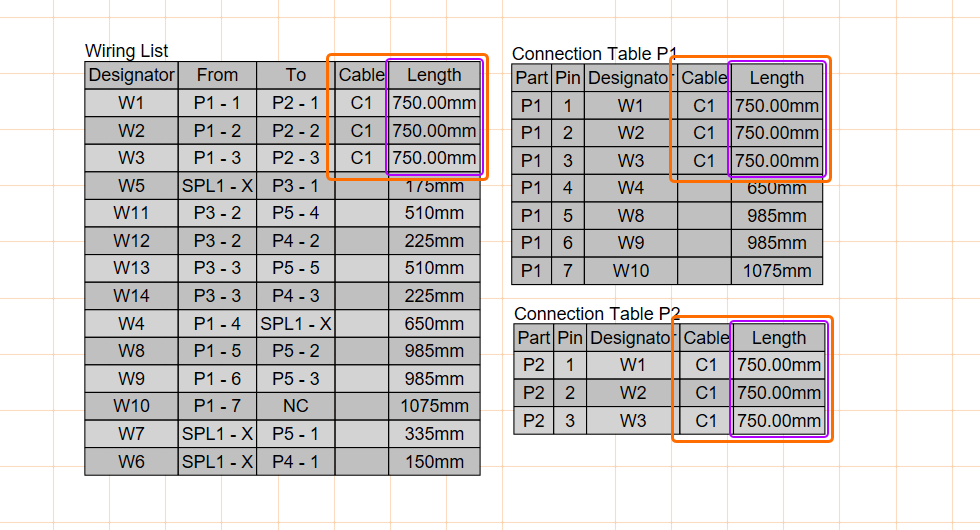

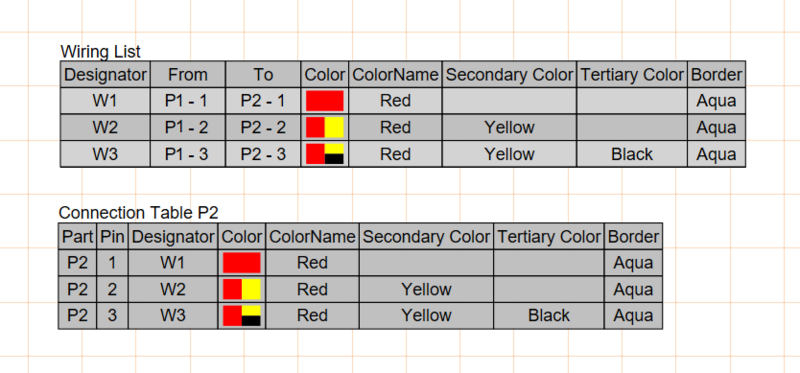

在Wiring List和Connection Table中显示每根导线长度

现在,Wiring List和Connection Table中的Length列会显示线缆中每根导线的长度。

|

导线W1、W2和W3均属于线缆的一部分。 |

|

|

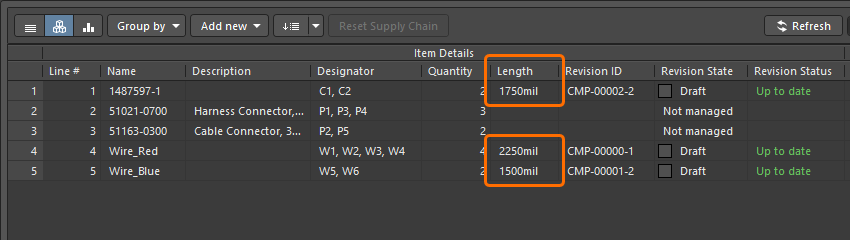

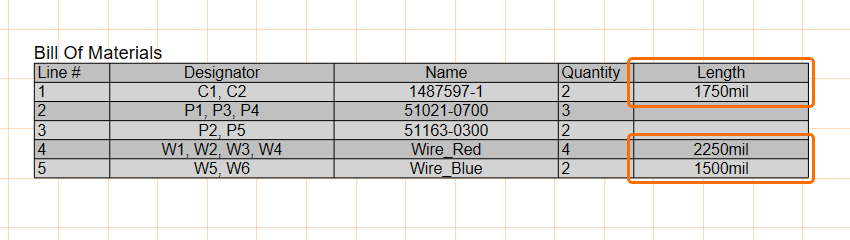

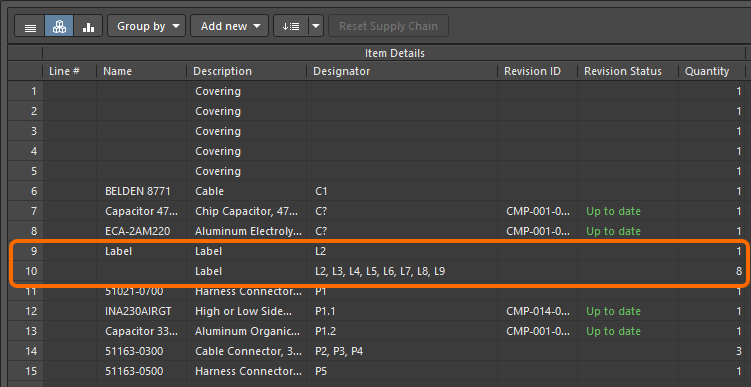

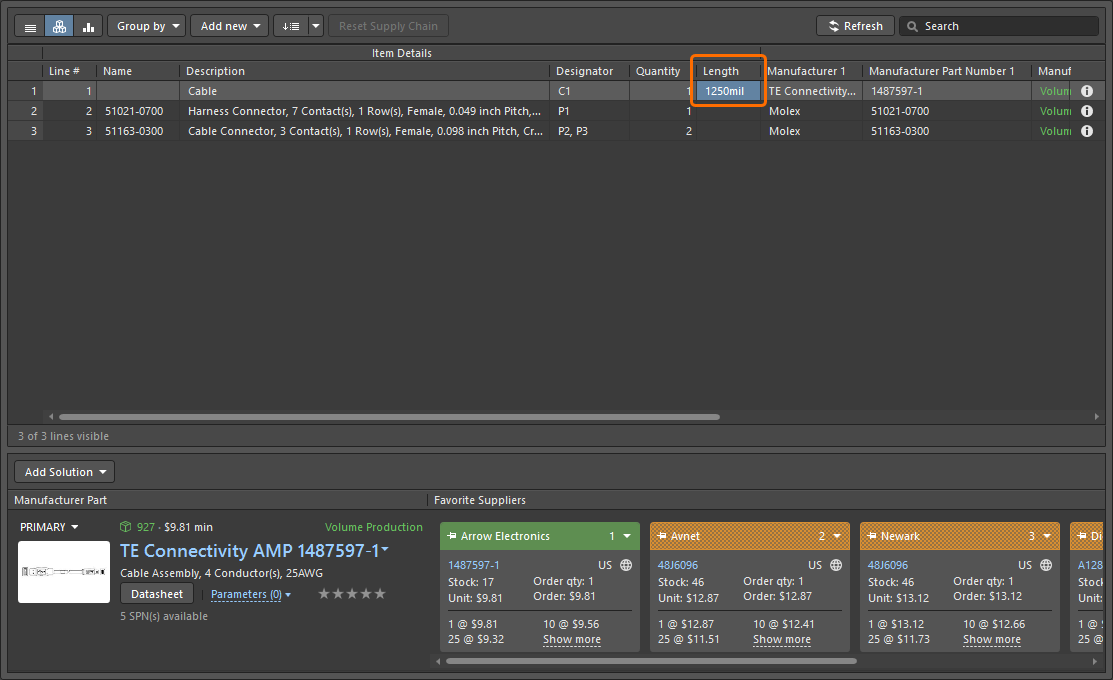

在BOM中显示导线和线缆的总长度

现在,对于线束布线元件,ActiveBOM文档中的Length列和制造图纸中的BOM Table会显示同个BOM条目的导线/线缆总长度,而非每条导线/线缆的长度。

数据管理改进

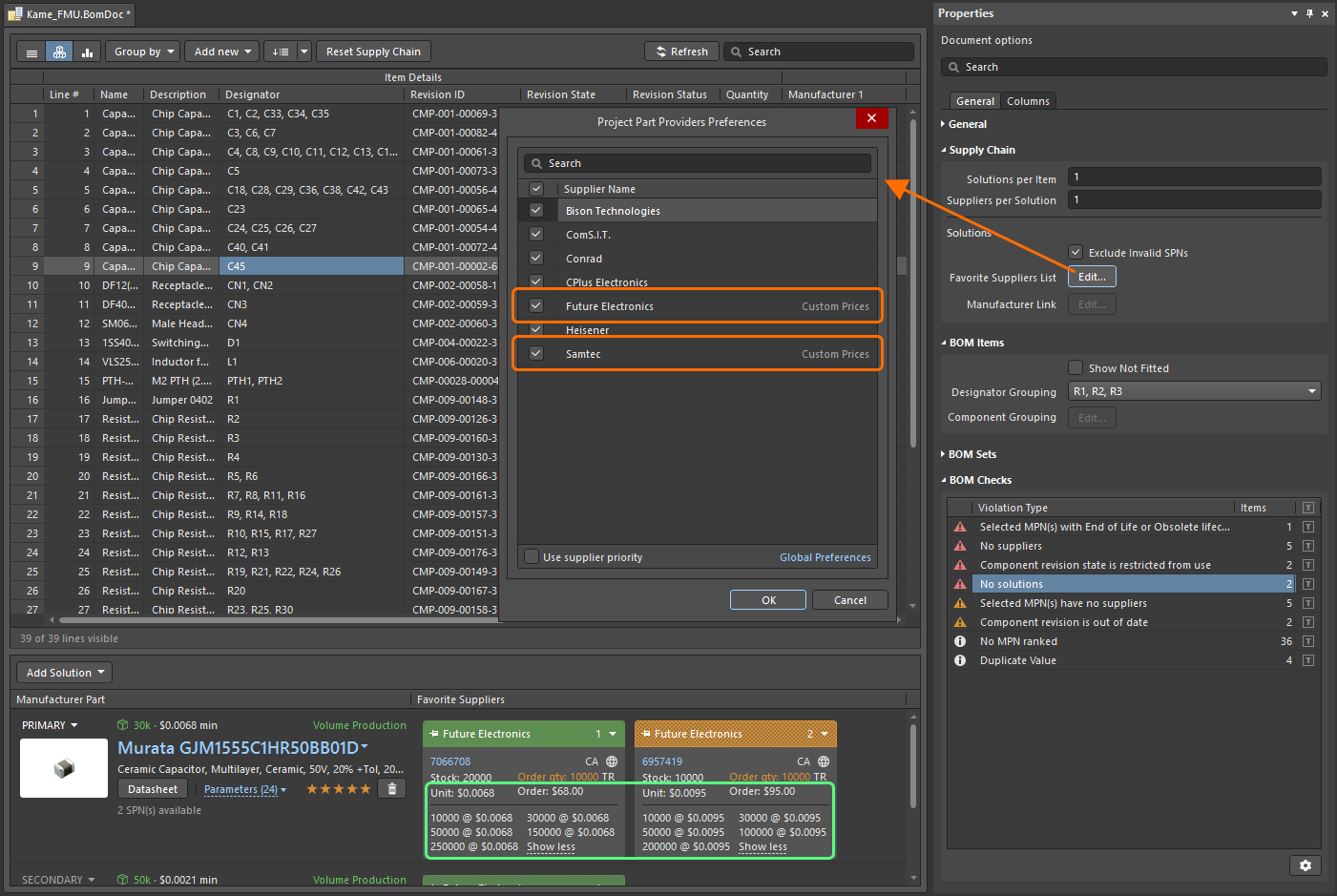

支持自定义定价

现在,当您通过Altium 365 Workspace浏览器界面配置与特定供应商帐户的连接后(了解更多),您会在ActiveBOM以及可访问部件选项的所有位置看到适用的自定义定价。另外,Project Part Providers Preferences对话框还将标出提供自定价价格的供应商。您可以通过点击ActiveBOM文档Properties面板Favorite Suppliers List字段中的Edit按钮,访问该对话框。

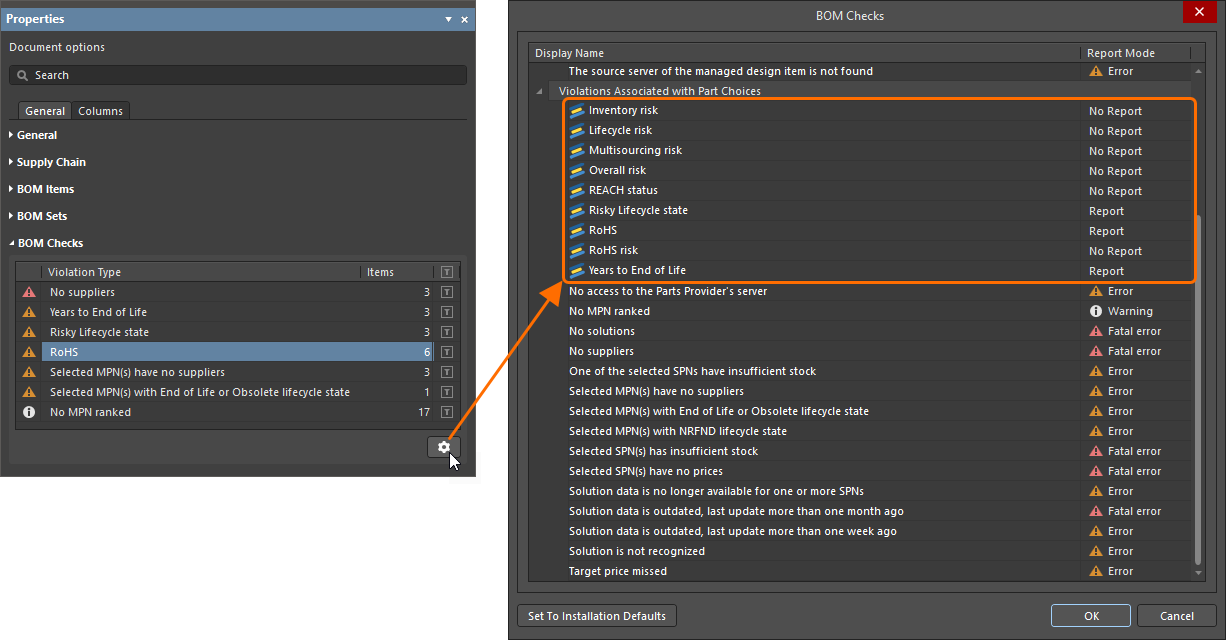

添加了SiliconExpert参数的BOM检查

现在,ActiveBOM支持一系列基于SiliconExpert参数的检查。您可以在BOM Checks对话框的Violations Associated with Part Choices类别中,启用或禁用这些检查。单击Properties面板BOM Checks区域中的![]() 按钮,即可打开对话框。

按钮,即可打开对话框。

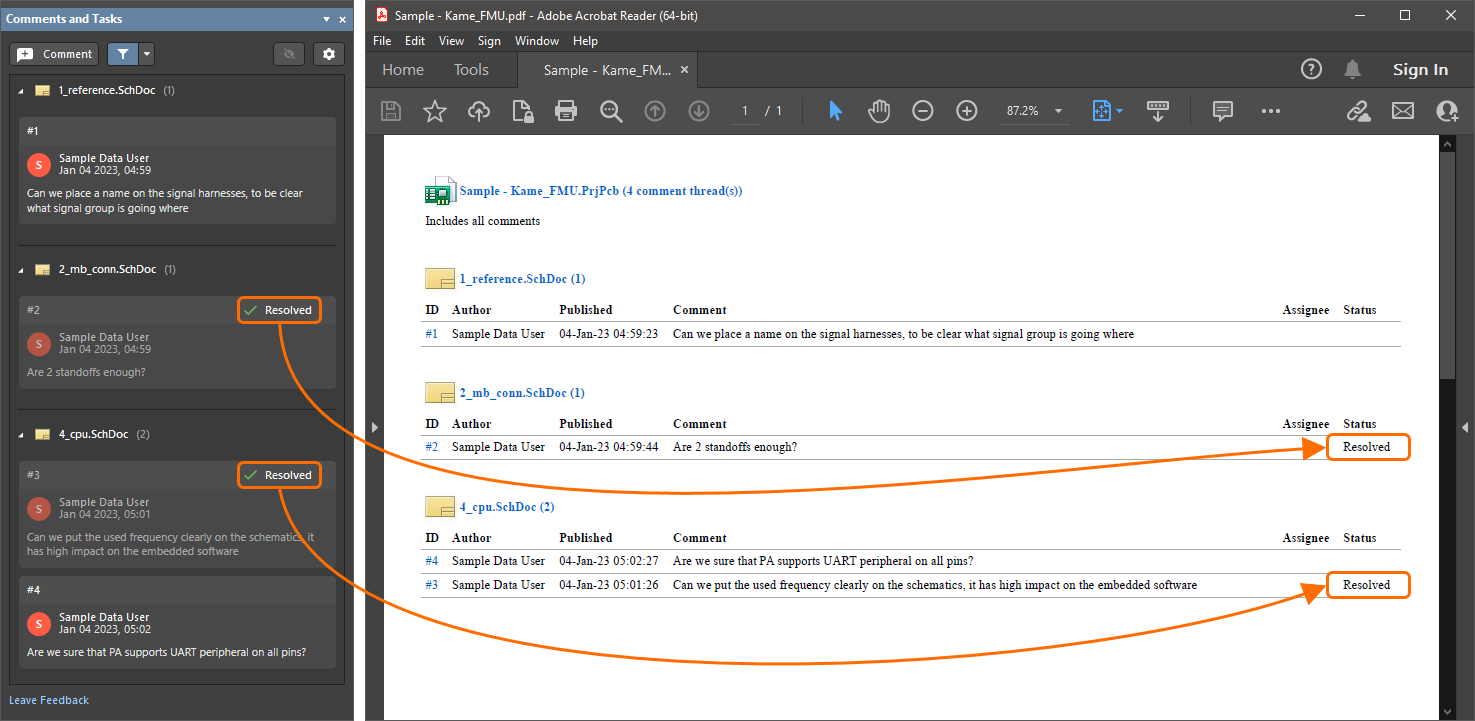

为导出PDF文件添加了注释已解决状态

现在,将注释导出至PDF时,导出文件中会包含已解决简单注释(即,未被指定为“任务”的注释)的状态。

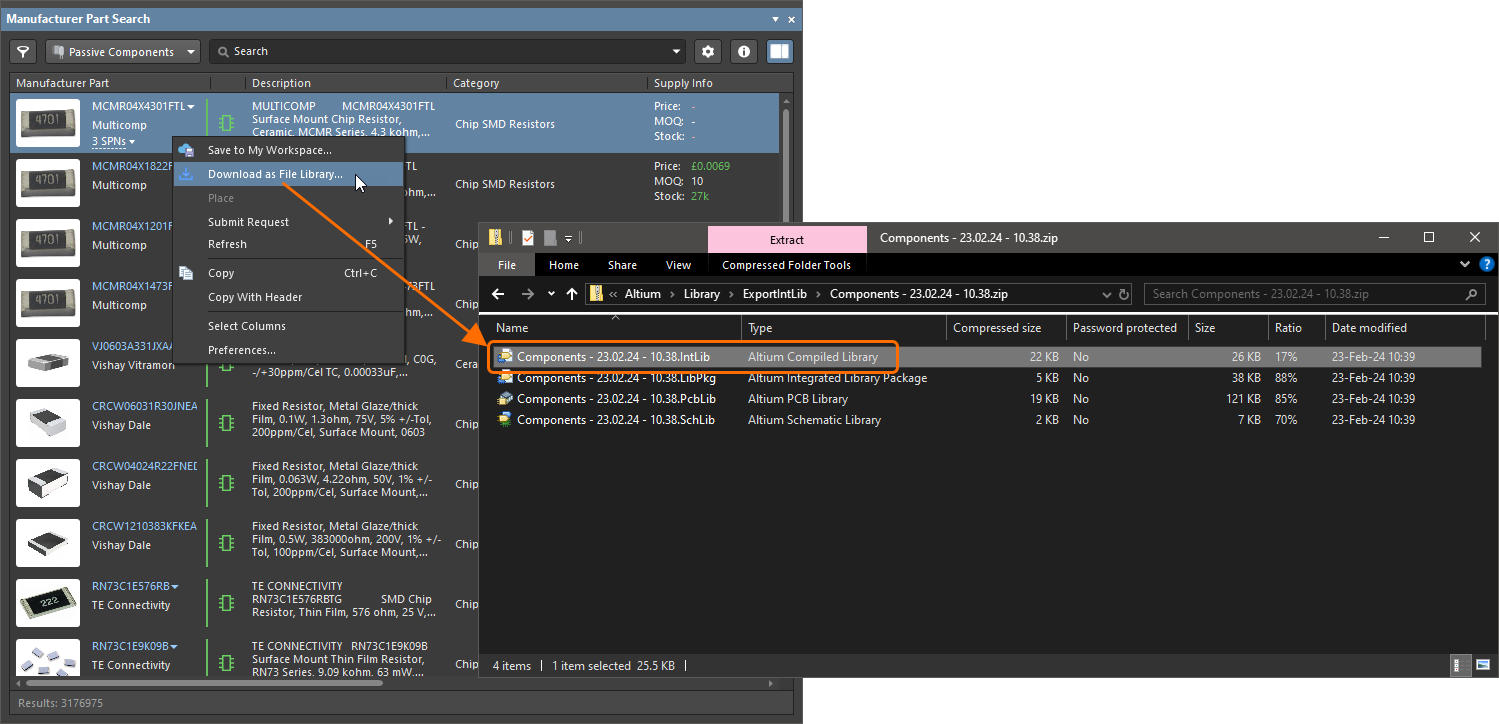

在下载的制造商部件压缩包中添加了已编译IntLib

现在,从Manufacturer Part Search面板下载元件作为文件库时,已编译集成库(*.IntLib)会包含在Zip文件中。

导入/导出改进

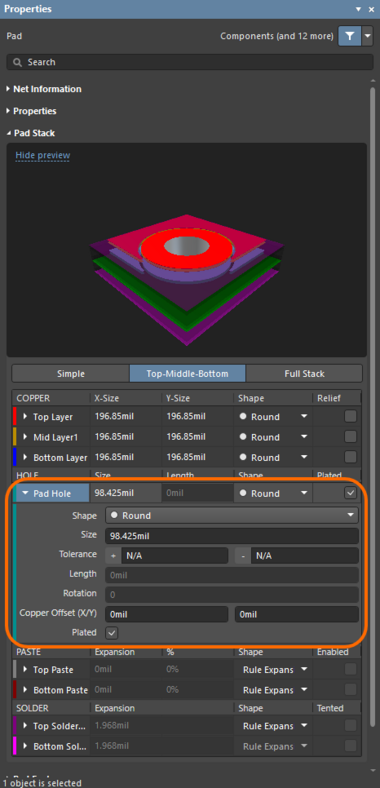

Xpedition库导入增强

本次发布在将Xpedition库导入Altium Designer方面作了以下改进。

- 在Xpedition库内添加了对在封装中定义的‘Round Donut’焊盘形状的支持。请注意,这一步实现了对此类封装焊盘的导入(作为自定义焊盘形状)。PCB/PCB Footprint编辑器中没有专门的‘Round Donut’焊盘形状。

- 现在,导入Xpedition库时,已定义焊盘孔公差将被包含在内。

- 在导入Xpedition库时,添加了对封装内复制文本字符串(即,安装孔‘A’)的支持。原始字符串、复制字符串,以及关联参数均会随之导入。

- 添加了对导入 Xpedition 库时为 Placement Outline 图层上的封装定义的零宽度线的支持。

电路仿真改进

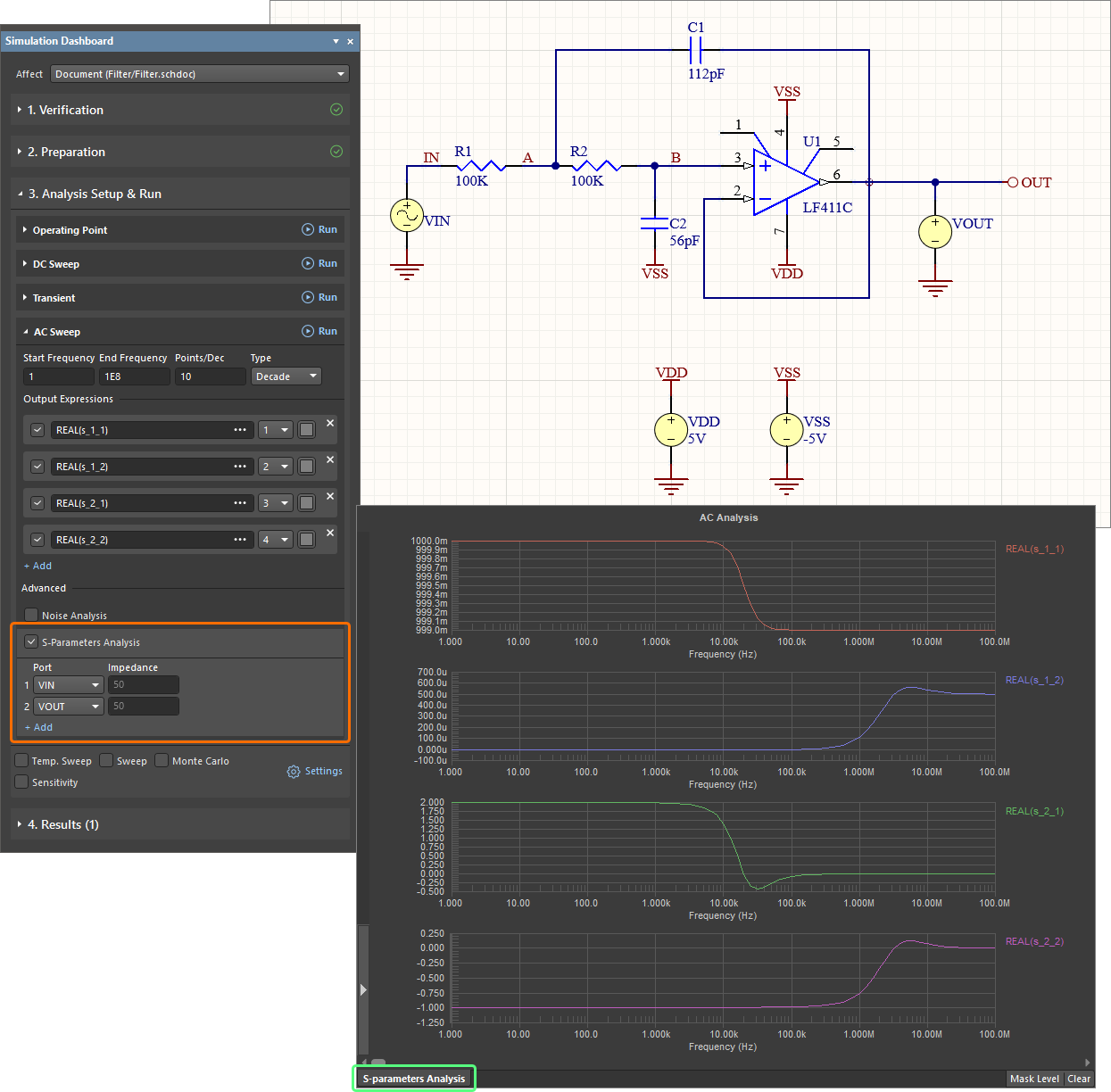

仿真S参数分析(公测版本)

本次发布添加了S参数(散射参数)分析功能。S参数有助于基于入射微波和反射微波的比值(就被测器件而言,从一个端口传递到另一个端口的功率值,以及被反射的功率值)描述网络。这些比值随后可以用于计算电路属性(包括输入阻抗、频率响应和隔离度)。虽然此类分析主要用于RF电路和元件,但它对带有至少两个电源(端口)的电路同样有效。

通过在Simulation Dashboard面板AC Sweep区域中启用S-Parameters Analysis选项,即可完成这一分析。定义所涉及的端口(电源),并为每个端口设定阻抗值(默认为50欧姆)。如果器件拥有两个以上端口,则您可以相应地添加并定义每个端口,而最终获得的“S矩阵”也将涉及更多的S参数。一旦运行AC扫描分析,即可在SDF文档的S-parameters Analysis图表中获得S参数数据。

该仿真引擎还会计算Y参数(导纳)和Z参数(阻抗)。您可以根据需要,将这两个参数添加到图表的曲线图上。

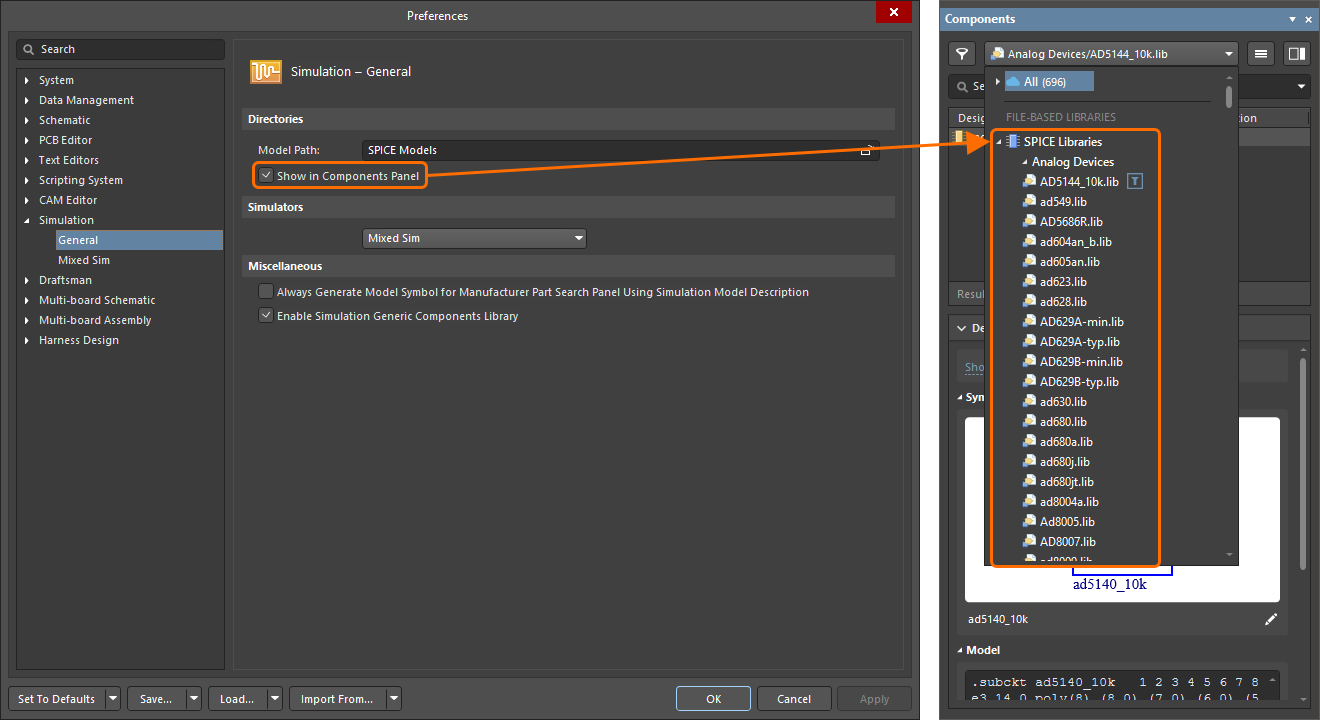

添加了在元件面板中显示SPICE模型的功能

本次发布在Preferences对话框Simulation – General页面中新增了Show in Components Panel选项。启用该选项后,Components面板中的SPICE Libraries类别将变为可用,并列出Preferences对话框Simulation – General页面上指定的Model Path文件夹中包含的库。类别结构反应了指定文件夹的结构。

在此过程中,Analog Devices的SPICE模型文件夹被添加到Mixed Simulation扩展的默认安装Library文件夹中(\ProgramData\Altium\Altium Designer <GUID>\Extensions\Mixed Simulation\Library\SPICE Models\Analog Devices)。

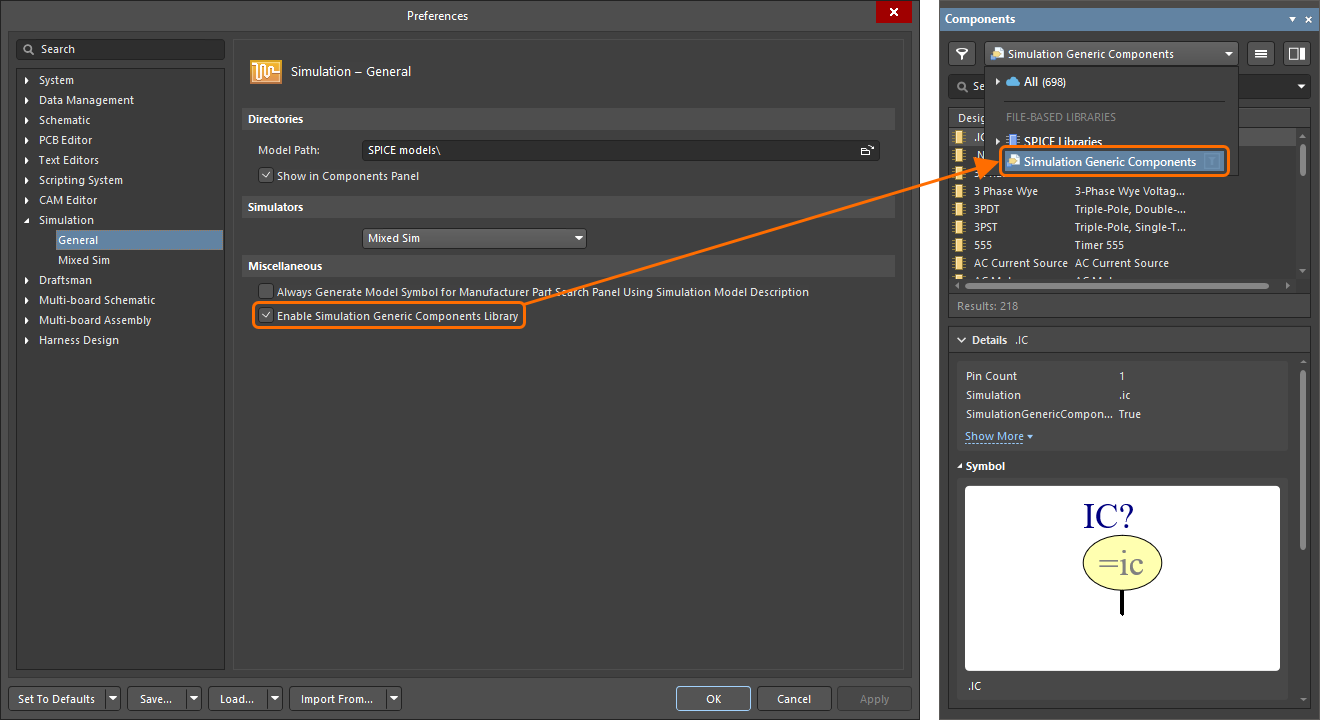

添加了启用仿真常规元件库选项

在Preferences对话框Simulation – General页面中新增了Enable Simulation Generic Components Library选项,以便您在Components面板中控制库的可视性。

此外,还将库从Libraries Preferences对话框的Installed选项卡中删除。

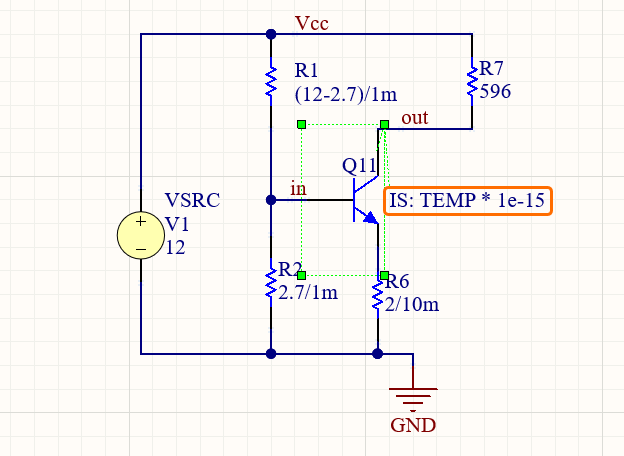

添加了对常量参数中‘TEMP’关键字的支持

就温度分析而言,现在可以在常量参数中使用关键词TEMP。

可以在常量参数中使用关键词TEMP。图片显示了使用TEMP关键词计算晶体管Q11的IS参数。

通过点击Simulation Dashboard面板Analysis Setup & Run区域中的Settings,即可在Advanced Analysis Settings对话框的Advanced选项卡上设置TEMP值(电路实际工作温度,单位为℃)。

添加了对LTspice‘AKO’模型关键词的支持

当基于另一个模型创建模型时,您现在可以使用 AKO model 关键字。

在下文所示列子中,除了更改BF并设置VA外,模型QP的其他参数与模型QP350相同。

.MODEL QP350 PNP(IS=1.4E-15 BF=70 CJE=.012P CJC=.06P RE=20 RB=350 RC=200)

.MODEL QP AKO:QP350 PNP(BF=150 VA=100)

Altium Designer 24.3中完全公开的功能

以下功能现已在此版本中正式对外公开:

- Print Not Fitted Components – 自22.3版开始提供

- Any Angle Retrace – 自23.10版开始提供

- Replication of PCB Layout – 自23.11版开始提供

- Automatic Tuning of Multiple Nets – 自23.11版开始提供

- Any Angle Diff Pair Router – 自24.0版开始提供

- Ability to Store TrueType Fonts – 自24.1版开始提供

Altium Designer 24.2

发布日期:2024年2月15日——版本24.2.2(Build 26)

PCB设计改进

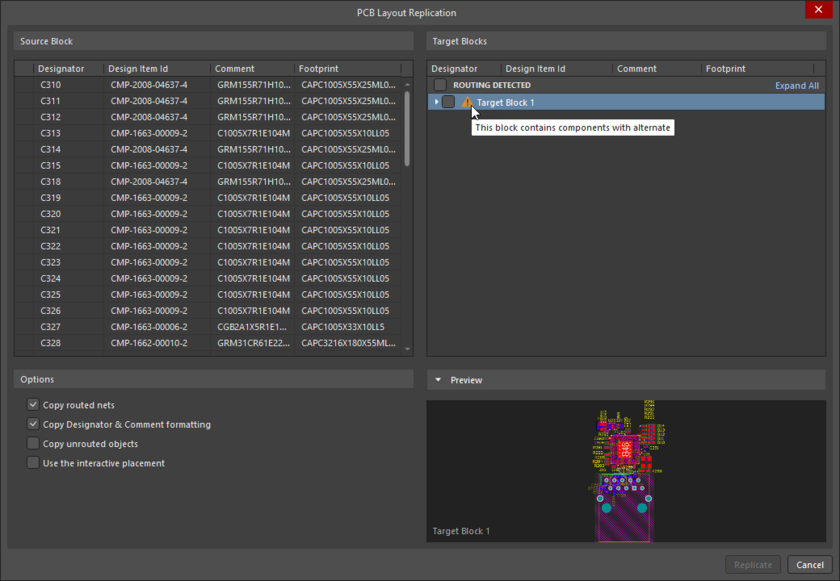

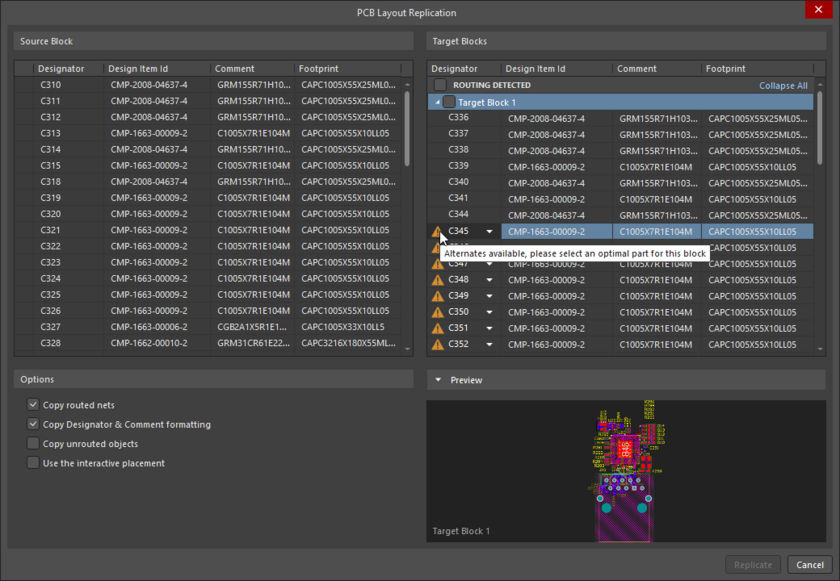

添加了复制时手动选择元件的功能

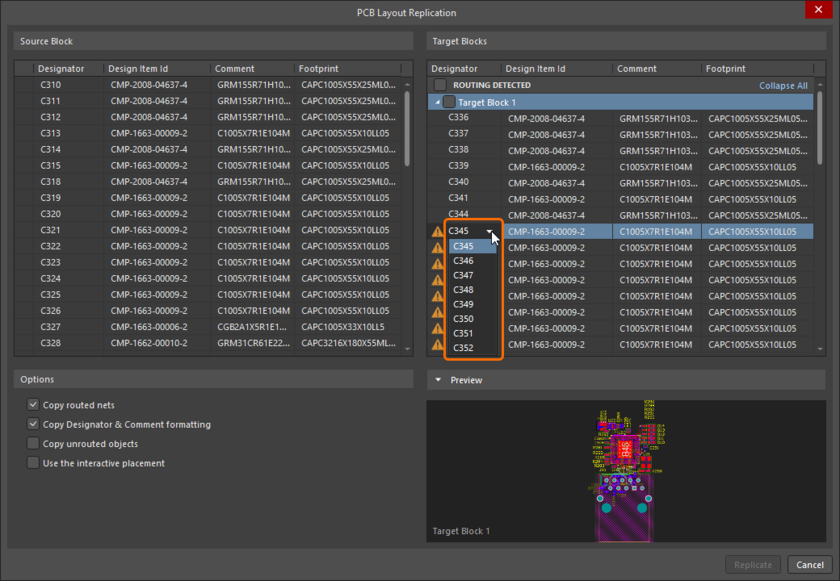

当前版本扩展了PCB Layout Replication工具的功能,支持用户在工具检测到多个元件具有类似连接的目标块中手动映射元件。该功能使您可以在不违反电路连接的前提下,手动选择可以相互替换的可用元件。

当工具检测到具有相似连接的多个元件时,PCB Layout Replication中相应的目标块将显示![]() 图标(当块折叠时),而具有可用替换元件的每个元件亦将显示

图标(当块折叠时),而具有可用替换元件的每个元件亦将显示![]() 图标(当块展开时)。使用已检测到替换元件的元件Designator字段中的下拉菜单选择所需元件。

图标(当块展开时)。使用已检测到替换元件的元件Designator字段中的下拉菜单选择所需元件。

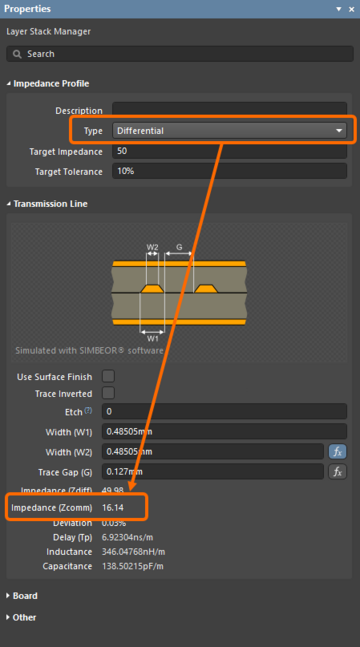

在层堆栈管理器中添加了差分对共模阻抗

在Properties面板中选择Differential作为Type以定义差分线对的Impedance Profile时,新增了一个显示所选Impedance Profile的共模阻抗的字段。该值(显示为Impedance(Zcomm))取自Simbeor计算得出的传输线数据。

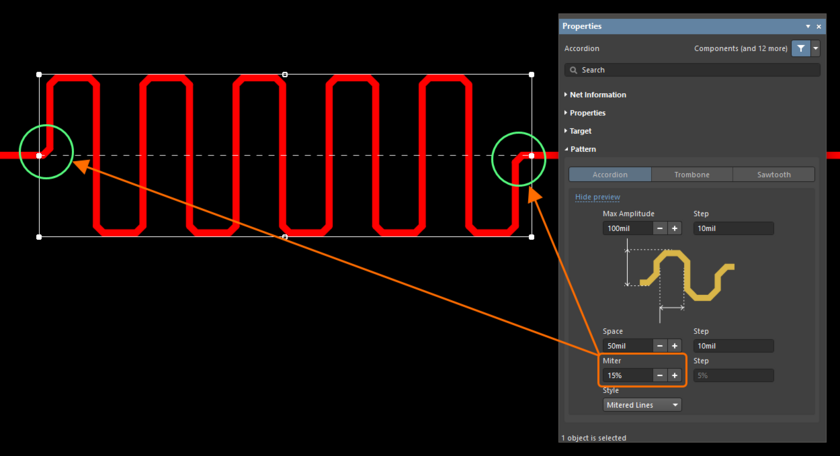

使用调节斜接参数将线路调整折叠段连接到布线

现在,通过添加折叠段进行交互式布线长度调整时,Properties面板中为折叠段定义的Miter参数亦被用于斜接连接折叠段和布线的导线,而这些导线之前使用的是为交互式布线定义的Miter Ratio参数。

现在,折叠段属性中的Miter值亦会被应用到连接折叠段和布线的导线上。

约束管理器改进

增强了从PCB到原理图的约束传输功能

在本次发布中,我们新增了在Constraint Manager的Physical视图和Electrical视图上传输已定义约束的功能。在PCB编辑器中,从主菜单中的<PCBProjectName>命令中选择Design » Update Schematics,然后使用打开的Engineering Change Order对话框探索、确认和执行约束变更。

多板设计改进

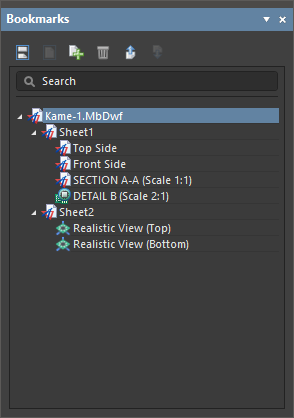

为多板Draftsman文档添加了书签面板

现在,您可以使用Draftsman中的Bookmarks面板处理用于制造的多板设计图纸(*.MbDwf)。该面板可在Draftsman文档上提供图纸的树状视图。每个图纸入口均可展开和折叠;展开图纸入口时,将显示每张图纸上的相关内容,具体如下图所示。

您可以使用该面板在设计区内轻松导航。当在面板或设计区内选中一个条目时,Properties面板(如果打开)将显示所选条目的属性和设置。另外,当您在Bookmarks面板中选中一个条目时,设计区将缩放至所选条目。

线束设计改进

为线缆、屏蔽和绞线对象删除了重复位号标识符违规

在Wiring Diagram上,当Cable/Shield/Twist对象使用相同位号标识符时,Duplicate Designator(WD)违规检查不会报告问题。现在,您可以使用相同位号标识符拆分对象并将其用于不用的位置。

高亮显示用于绞线和屏蔽的导线

如果绞线/屏蔽与Wiring Diagram上多个位置的导线相关联(使用相同位号标识符),则选择绞线/屏蔽实例将以荧光绿色高亮显示组中的所有关联导线。

|

两根具有相同位号标识符的绞线被放置在不同导线组上的Wiring Diagram示例。虽然仅选中了其中一根绞线,但被这些绞线所覆盖的所有导线均会高亮显示。 |

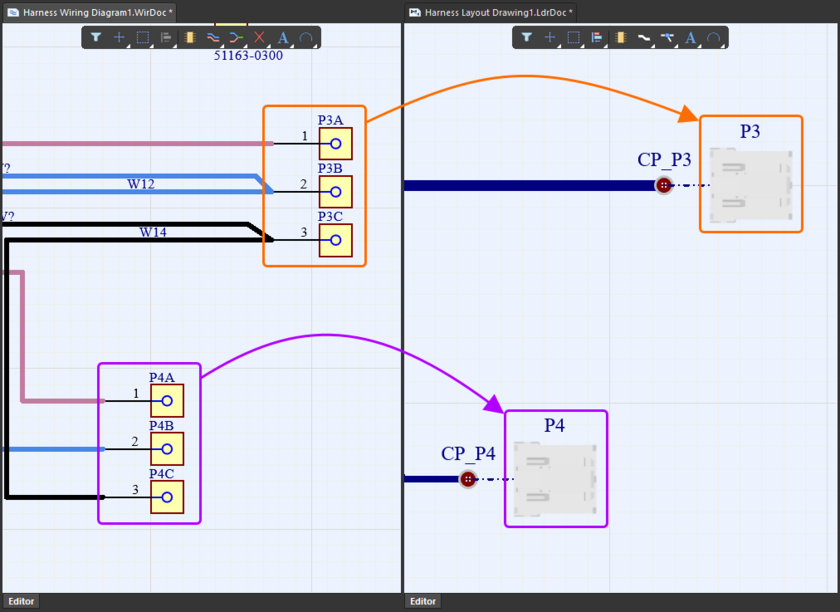

添加了对多部件元件的支持

添加了将多部件元件数据从Wiring Diagram传输到Layout Drawing的功能。当在Wiring Diagram上放置多部件元件时,软件会为Layout Drawing中的元件分配正确的位号标识符。若在Wiring Diagram上放置同一元件的多个部件,软件仅会在Layout Drawing中放置一个元件实例。

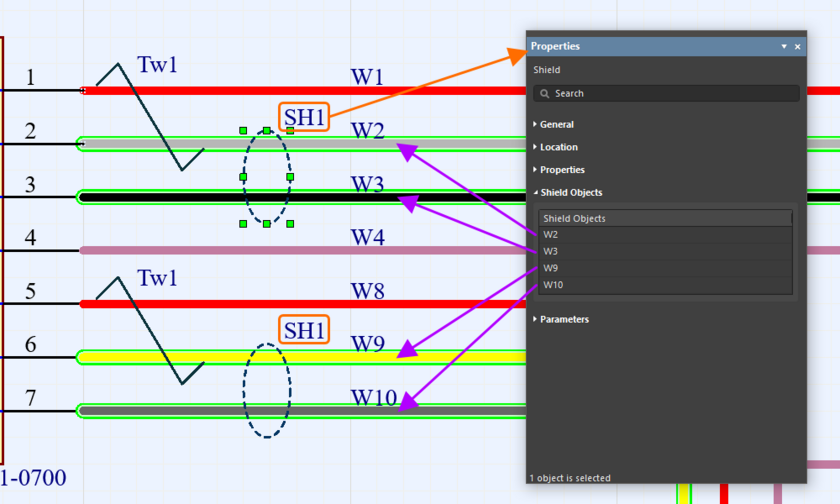

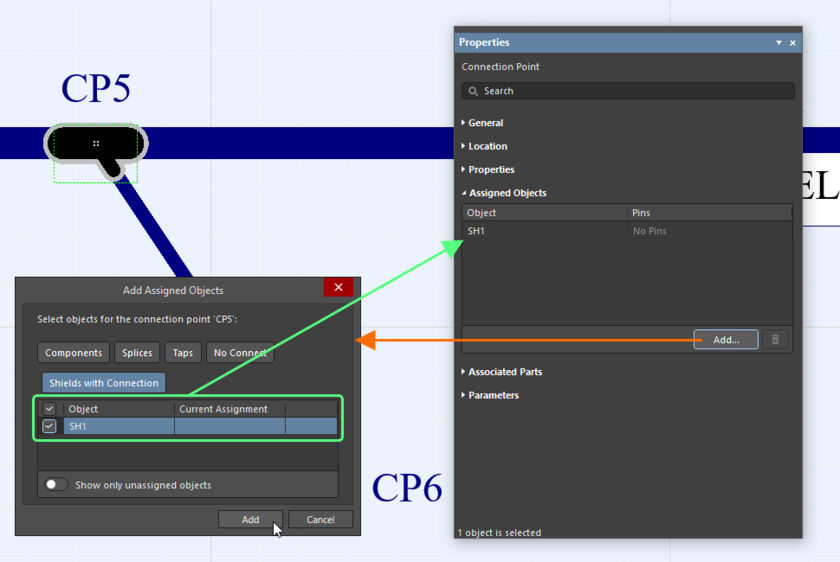

添加了对将屏蔽对象连接到连接点的支持

现在,可以将Wiring Diagram上定义的具有连接对象的屏蔽对象分配给Layout Drawing中的连接点。选中连接点时,使用Add Assigned Objects对话框(通过单击Properties面板的Assigned Objects区域中的Add按钮访问)选择带有将分配给该连接点的连接的屏蔽对象。

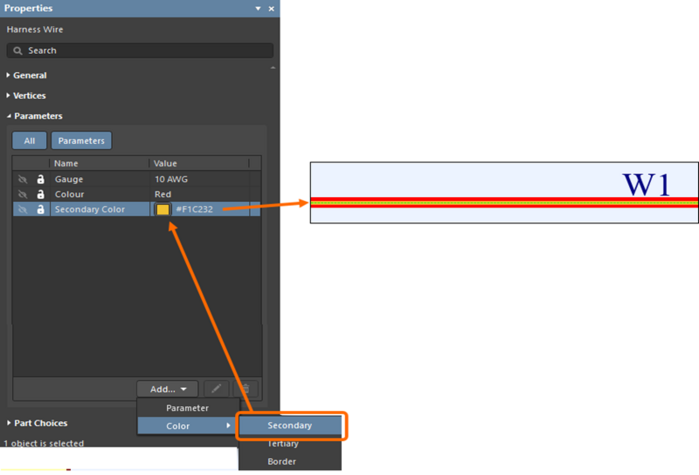

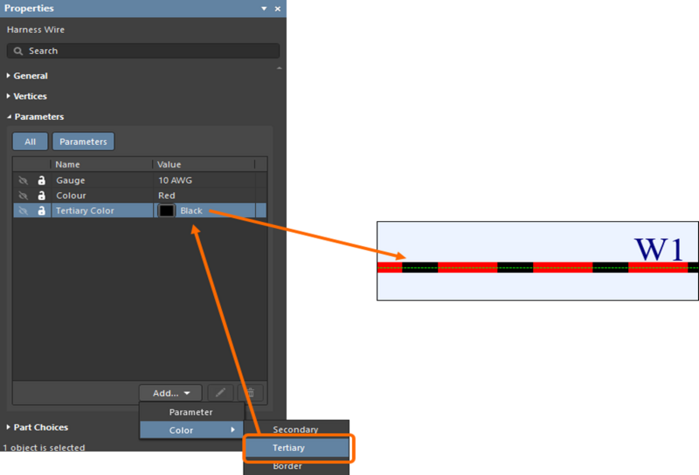

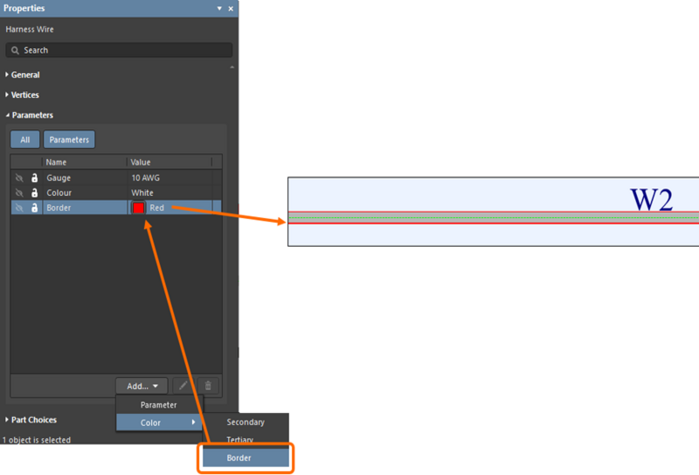

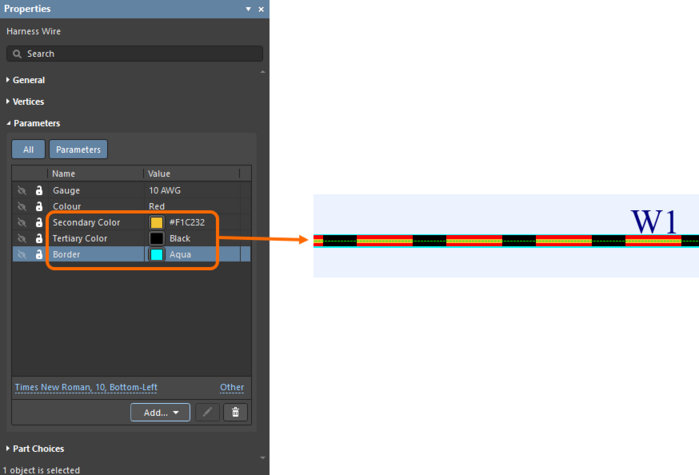

添加了对多色导线的支持

现在,您可以通过选择导线的二次色和三次色,在Wiring Diagram中使用多色导线。(原色是已放置导线的颜色。)在Properties面板中,单击Parameters区域底部的Add下拉菜单,然后选择Secondary和Tertiary来定义所需颜色;所选颜色的参数将出现在Parameters区域中。单击面板中的颜色图标可打开颜色选项;单击所需颜色。您还可以使用同一下拉菜单并选择Border,定义导线的边框颜色。点击下面的幻灯片查看示例。

|

为导线定义颜色 |

线束设计Draftsman文档(*.HarDwf)亦支持多色导线。软件可以在放置的表格中显示用于二次色、三次色和边框颜色的附加列,并将对应的Color单元格拆分,以显示分配给导线的二次色和三次色。

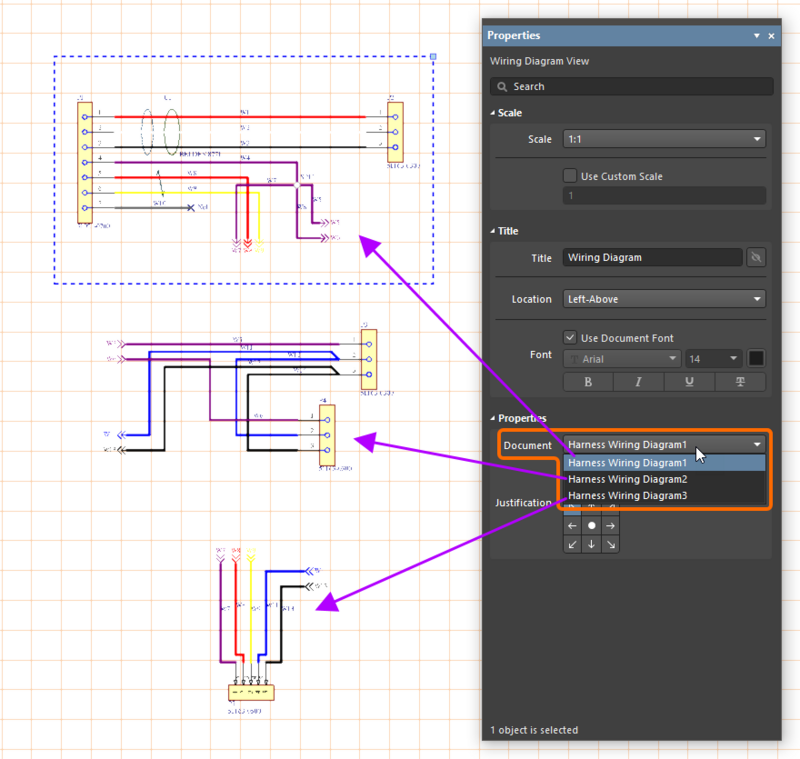

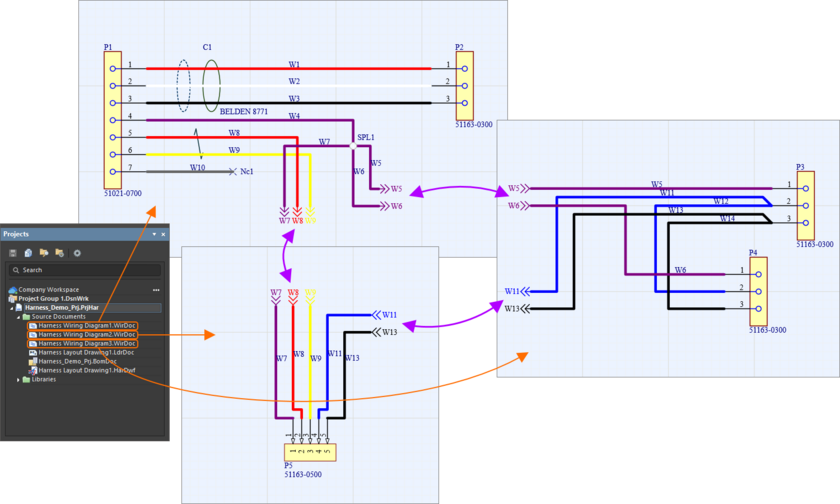

在Draftsman文档中支持多个接线图

现在,Harness Draftsman文档(*.HarDwf)支持同个项目中的多个Wiring Diagram文档(*.WirDoc)。借助该功能,您可以选择用于从中生成和更新已放置接线图视图的接线图文档。当选中接线图视图时,使用Properties面板的Properties区域中的Document下拉菜单,选择用于该视图的接线图文档。

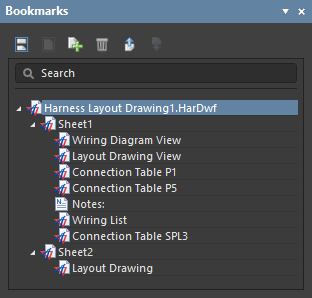

为线束Draftsman文档添加了书签面板

现在,您可以使用Draftsman中的Bookmarks面板处理用于制造的线束设计图纸(*.HarDwf)。该面板可在Draftsman文档上提供图纸的树状视图。每个图纸入口均可展开和折叠。展开图纸入口时,将显示每张图纸上的相关内容,具体如下图所示。

您可以使用该面板在设计区内轻松导航。当在面板或设计区内选中一个条目时,Properties面板(如果打开)将显示所选条目的属性和设置。另外,当您在Bookmarks面板中选中一个条目时,设计区将缩放至所选条目。

数据管理改进

SiliconExpert增强

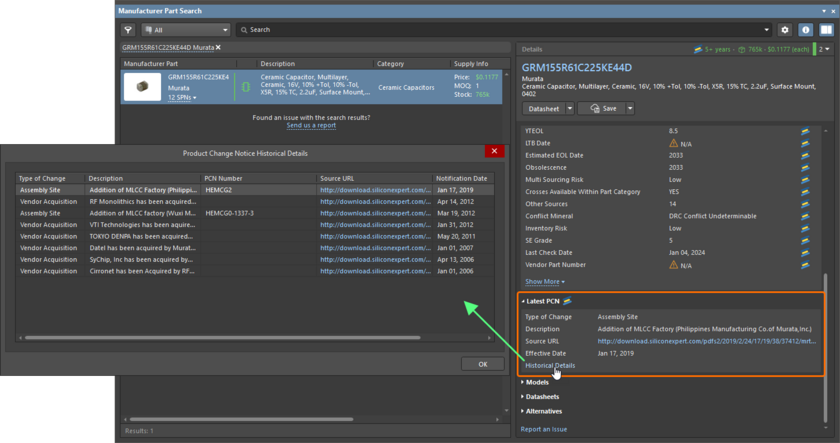

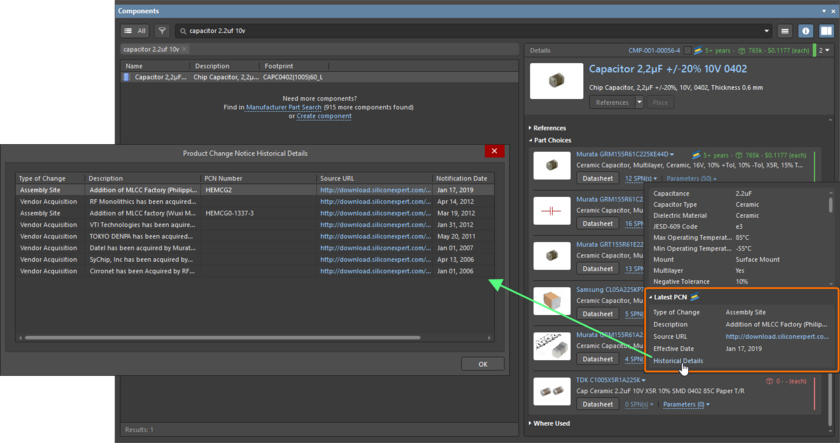

添加了SiliconExpert产品变更通知

在Manufacturer Part Search面板中以及可以访问部件选项的所有位置添加了SiliconExpert提供的Product Change Notice(PCN)。默认情况下,将显示最新的PCN数据。使用Historical Details控件打开Product Change Notice Historical Details对话框。您可以在该对话框中浏览有关先前使用的PCN的详细信息。

|

从Manufacturer Part Search面板访问最新和历史PCN。 |

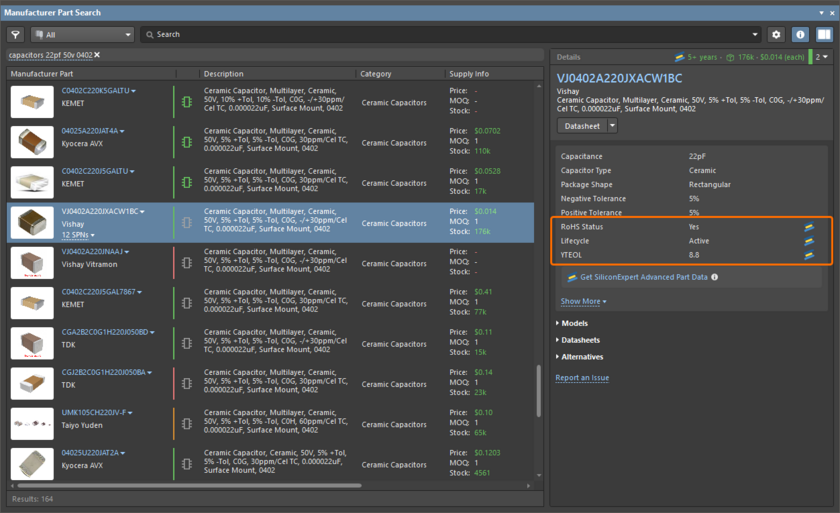

添加了SiliconExpert“Free”参数支持

现在,软件默认在Manufacturer Part Search面板以及展示部件选项的所有位置显示SiliconExpert提供的Lifecycle、YTEOL和RoHS Status参数。因此,您无需请求部件数据(进而使用您的SiliconExpert包中的配额),即可访问这些“Free”参数。

|

从Manufacturer Part Search面板访问SiliconExpert提供的“Free”参数。 |

此外,您还可以在不请求所有其他SiliconExpert参数的情况下,在ActiveBOM中使用这些SiliconExpert“Free”参数(通过将相应的列添加到ActiveBOM文档)。

添加了YTEOL参数显示

现在,将在下列位置显示YTEOL参数:

- 当在Manufacturer Part Search面板中选中制造商部件时,在Details窗格标题中显示。

- 当在Components面板中选中元件时,在Details窗格标题中显示。

- 在展示部件选项的所有其他位置显示。

- 当选中放置在原理图图纸上的元件时,在Properties面板中显示。

|

在Manufacturer Part Search面板中显示YTEOL参数。 |

在比较制造商部件时增加了对SiliconExpert参数的支持

现在,当比较两个选定部件时,Manufacturer Part Search面板的Selected Part Details窗格支持SiliconExpert参数。

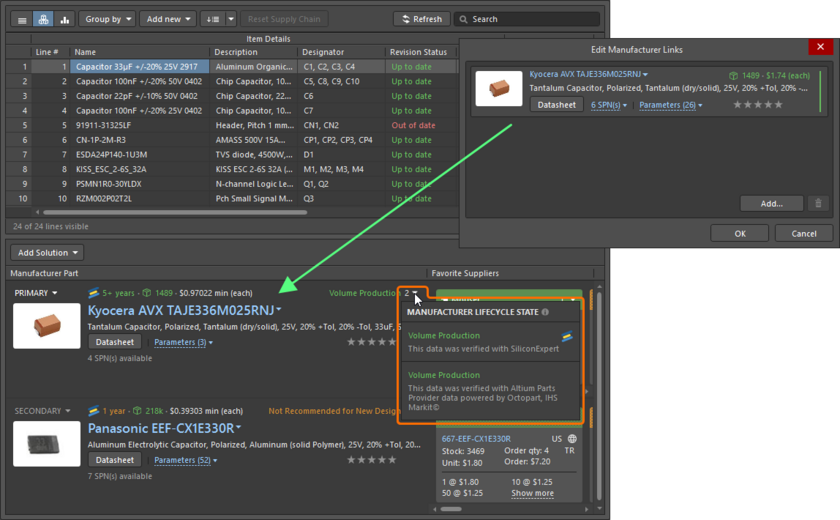

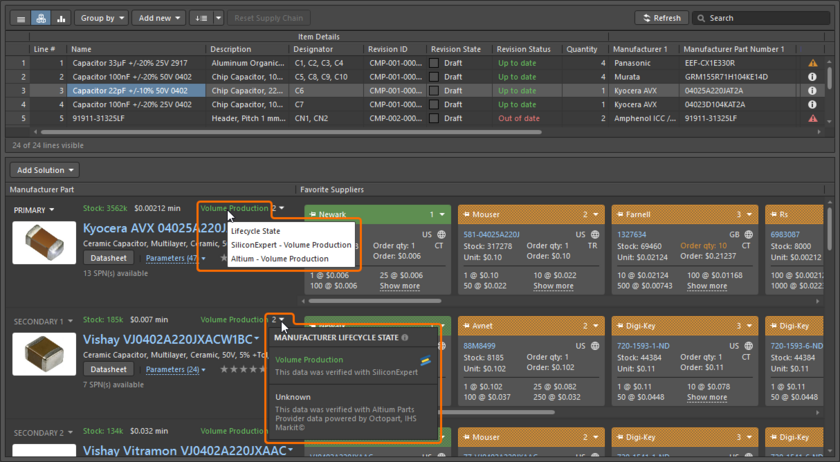

制造商链接增加了对汇总生命周期的支持

现在,当您探索以制造商链接形式添加到ActiveBOM文档的解决方案时,如果该制造商链接有多个生命周期数据来源(由Octopart或IHS Markit®和SiliconExpert提供支持的Altium Parts Provider),您将可以访问来自所有可用来源的该链接生命周期信息。将光标悬停在制造商生命周期状态上或使用下拉菜单,即可在工具提示/弹出窗口中查看来自所有来源的生命周期信息。

导入/导出改进

将封装导入到 Xpedition 的现有项目结构中

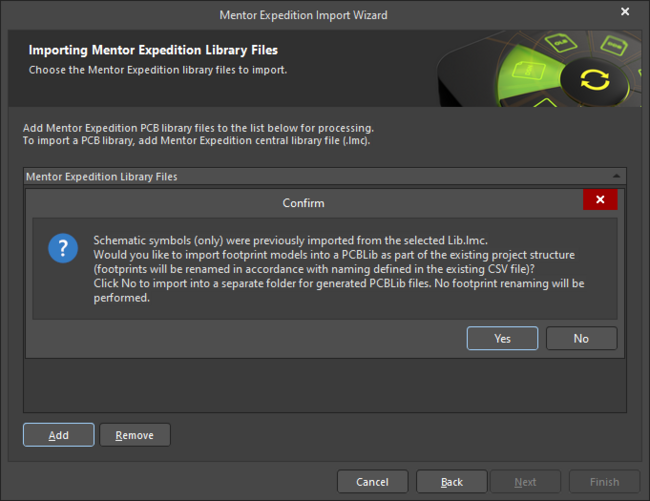

现在,对于之前使用xDX Designer Import Wizard导入原理图符号(仅限)并启用Import Symbols Only选项的Xpedition库(*.lmc),您可以选择将封装模型作为现有项目结构的一部分导入PCBLib。封装将根据在xDX Designer导入过程中生成的现有CSV文件中定义的命名进行重命名。

在Import Wizard的Importing Mentor Expedition Library Files页面上添加Xpedition库文件时,如果检测到之前导入的库,则会出现一个确认对话框,询问您是否按照上文所述导入封装。如果您单击No,则封装将被导入到用于生成的PCBLib文件的单独文件夹中,并且软件不会执行封装重命名操作。

Altium Designer 24.2中完全公开的功能

以下功能现已在此版本中正式转换为Public:

- PCB Section View - 自23.5版开始提供

Altium Designer 24.1

发布日期:2024年1月16日 – 版本24.1.2(build 44)

原理图输入改进

添加了线束连接器连接对象的违规检查

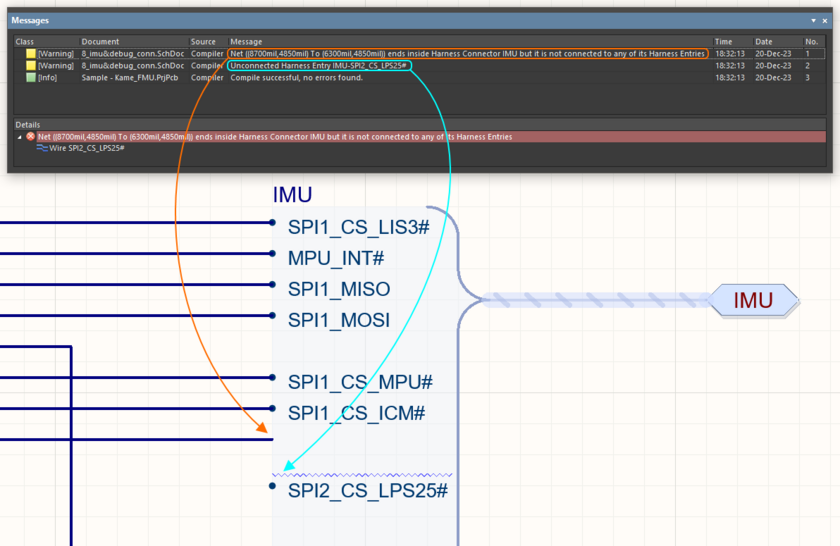

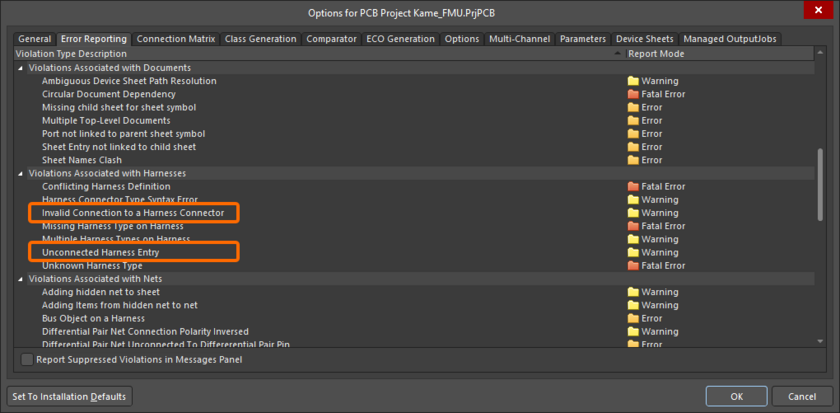

当前版本添加了新的违规检查,用于检测与PCB设计项目原理图中的信号线束相关的违规:

- Invalid Connection to a Harness Connector - 该违规检查检测的是导线、总线或信号线束在内部终止或与线束连接器边缘而不是与线束入口连接的情况。

- Unconnected Harness Entry - 该违规检查检测的是未连接的线束入口。

可以在Project Options对话框Error Reporting选项卡上的Violation Associated with Harnesses组中设置上述违规类型。

PCB设计改进

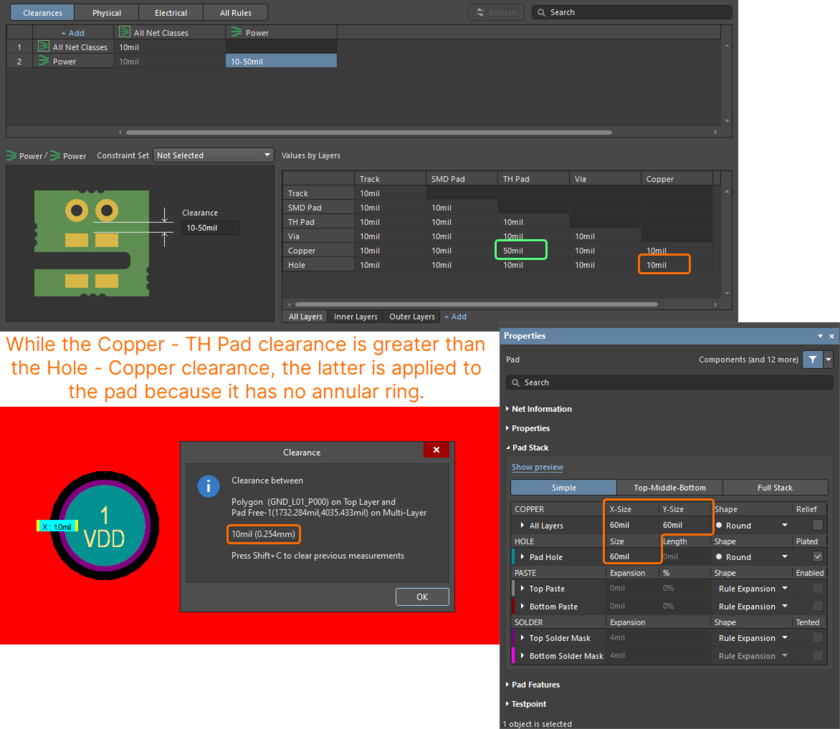

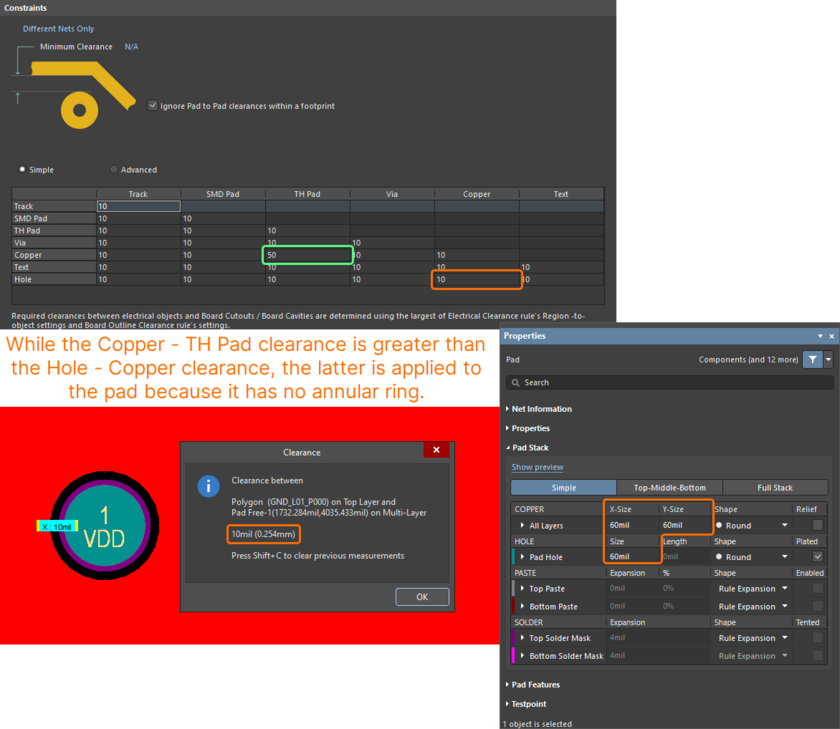

焊盘孔间隙检查改进(开放测试版)

当前版本改进了无孔环焊盘的间隙检测行为。

对于因孔径大于或等于焊盘尺寸而没有孔环的焊盘,由约束管理器中的相应约束或由间隙设计规则定义的孔的间隙值将被应用,而不是Hole和TH Pad间隙的最大值。

|

新焊盘孔间隙行为的示例。图中显示了在约束管理器中配置的间隙。 |

请注意:新创建的间隙约束和间隙设计规则中的孔间隙默认值已更新为10mil / 0.254mm。

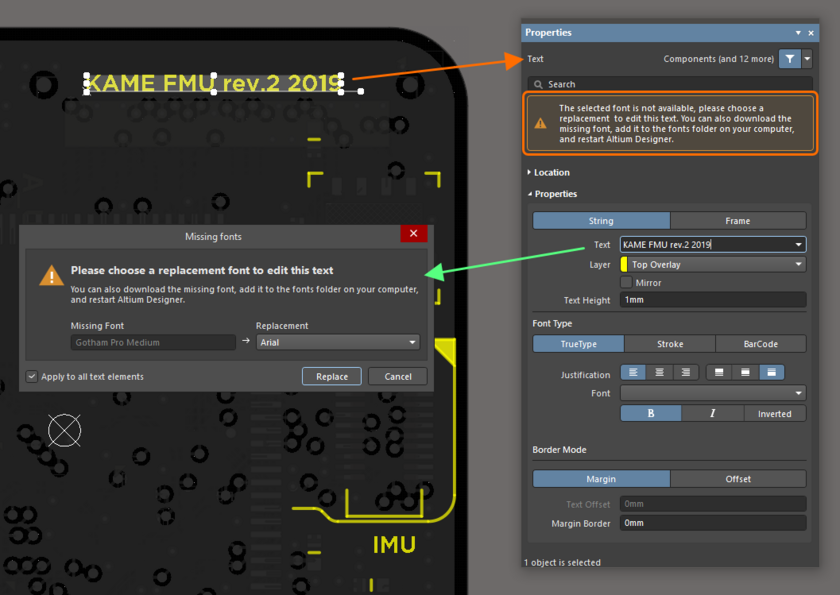

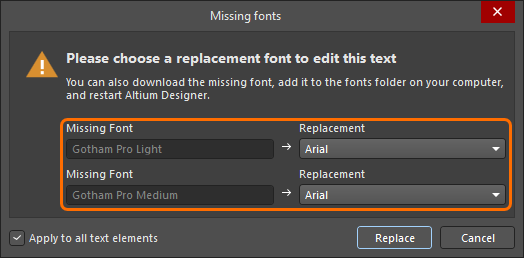

TrueType字体存储功能(开放测试版)

当前版本增加了在PCB文档中自动存储使用TrueType字体的文本对象几何图形的功能。当PCB文档中的对象(文本字符串/框架、尺寸、钻孔表和/或层堆栈表)使用TrueType字体时,如果PCB文档在另一台计算机上打开,那么即使未安装该TrueType字体,这些对象也将以相同的字体几何图形显示。

选择使用缺失字体的对象时,Properties面板顶部将出现一条警告消息。当影响文本的对象属性(例如,文本高度或文本本身)被更改时,Missing fonts对话框将打开,您可以从中选择替换字体。

从PCB List面板更改与文本相关的属性时,也会出现Missing fonts对话框。

尝试使用不同的缺失字体编辑多个对象时,您可以在Missing fonts对话框中为每个缺失字体选择替换字体。

增强焊盘属性面板的功能

Pad Properties面板上的Pad Stack区域经过增强,实现了更好的可用性。选择某个部分时,该部分的名称将以蓝色突出显示,并且整个部分的显示色度将与背景形成鲜明对比。

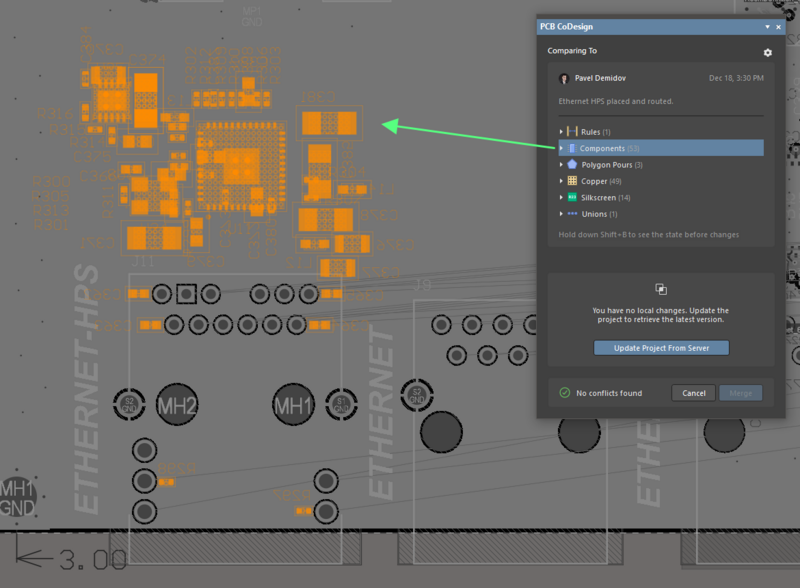

PCB CoDesign改进

类别更改突出显示功能

在PCB CoDesign面板中启用Show on PCB选项后,当在面板更改列表中选择特定类别时,可以突出显示该类别的所有更改。

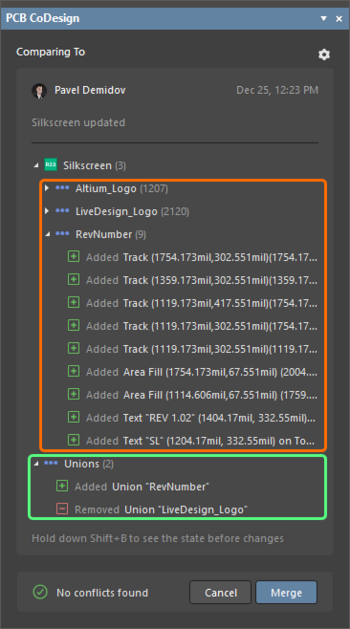

按照Union对变更进行分组

添加了对union(在PCB上定义的基元分组)比较和变更应用的支持。与union相关的变更显示在PCB CoDesign面板更改列表的Unions类别中。此外,如果对应对象属于任何union,则其他类别中的更改现在可以按照unions进行分组。

“Merged”状态更新

使用PCB CoDesign面板合并变更后,PCB文档将保持Merged状态(Projects面板上的图标),直至出现新的冲突。一旦在本地保存更改,则该状态将无法再更改为Modified。

另请注意:Merged状态的文档始终处于启用状态,以便能够在Save to Server对话框中保存到Workspace,并且无法禁用。

约束管理器改进

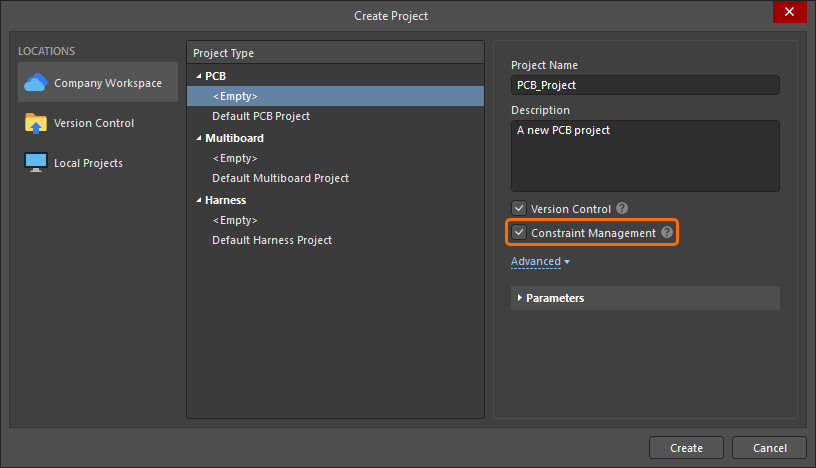

为新项目选择约束管理器的用法

现在,您在创建新的PCB项目时,可以控制选择约束管理器或旧的设计规则系统。在Create Project对话框(File » New » Project)中启用Constraint Management选项即可为所创建的项目使用约束管理器。

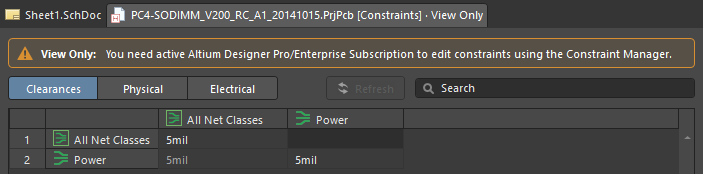

View Only模式

为PCB项目启用约束管理器后,如果没有订阅Altium Designer Pro/Enterprise Subscription的用户打开约束管理器,那么约束管理器将以View Only模式显示。在这种情况下,用户可以查看但不能修改已定义的约束。约束管理器的顶部将出现消息,告知您约束管理器处于View Only模式。

xSignal Creation更新

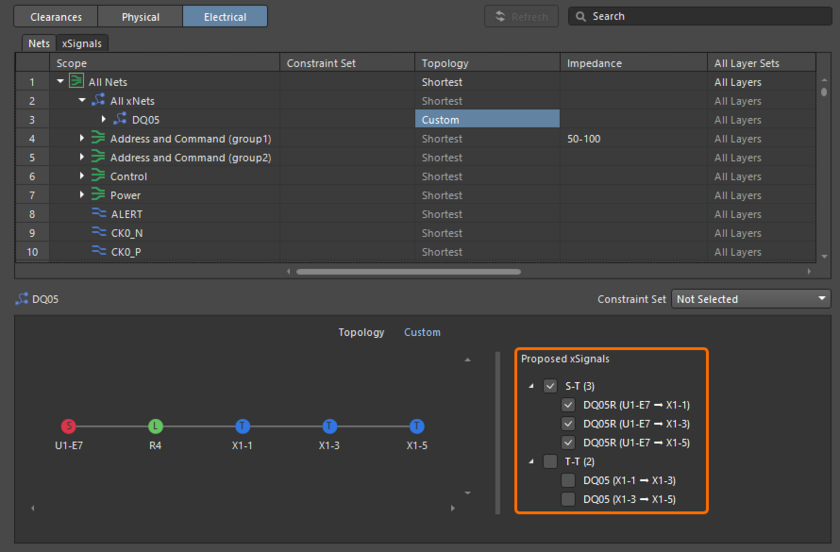

当前版本在使用约束管理器定义xSignals方面做出了一些更新:

- 现在,拟定xSignals列表将分为两组:从源点到目标点(S-T)的xSignals以及从一个目标点到另一个目标点 (T-T) 的 xSignals。在分组复选框中可以选择/取消选择相应分组中的所有xSignal。

- 现在,拟定xSignals列表包括从源点到每个目标点的xSignal(而不是仅仅从源点到最近目标点的xSignal)。

-

现在,为了更好地表示拟定xSignals,其在列表中的命名方案如下所示:

<SourceNetName> (<SourcePinDesignator> → <DestinationPinDesignator>)请注意:对于在约束管理器xSignals选项卡或PCB文档上可见的已创建xSignals的命名,将沿用之前的方案,即<SourceNetName>_<SourcePinDesignator>_<DestinationPinDesignator>。

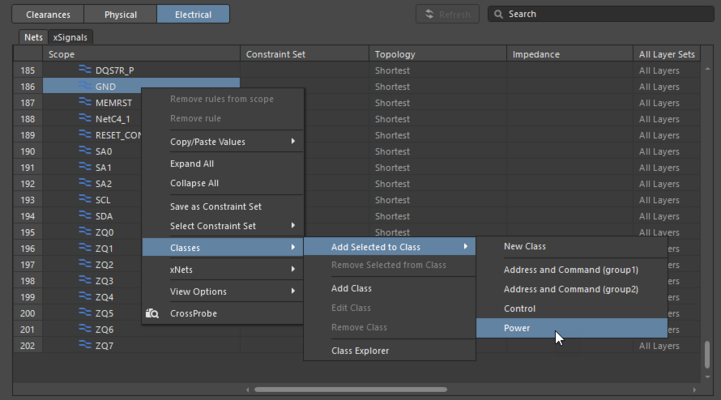

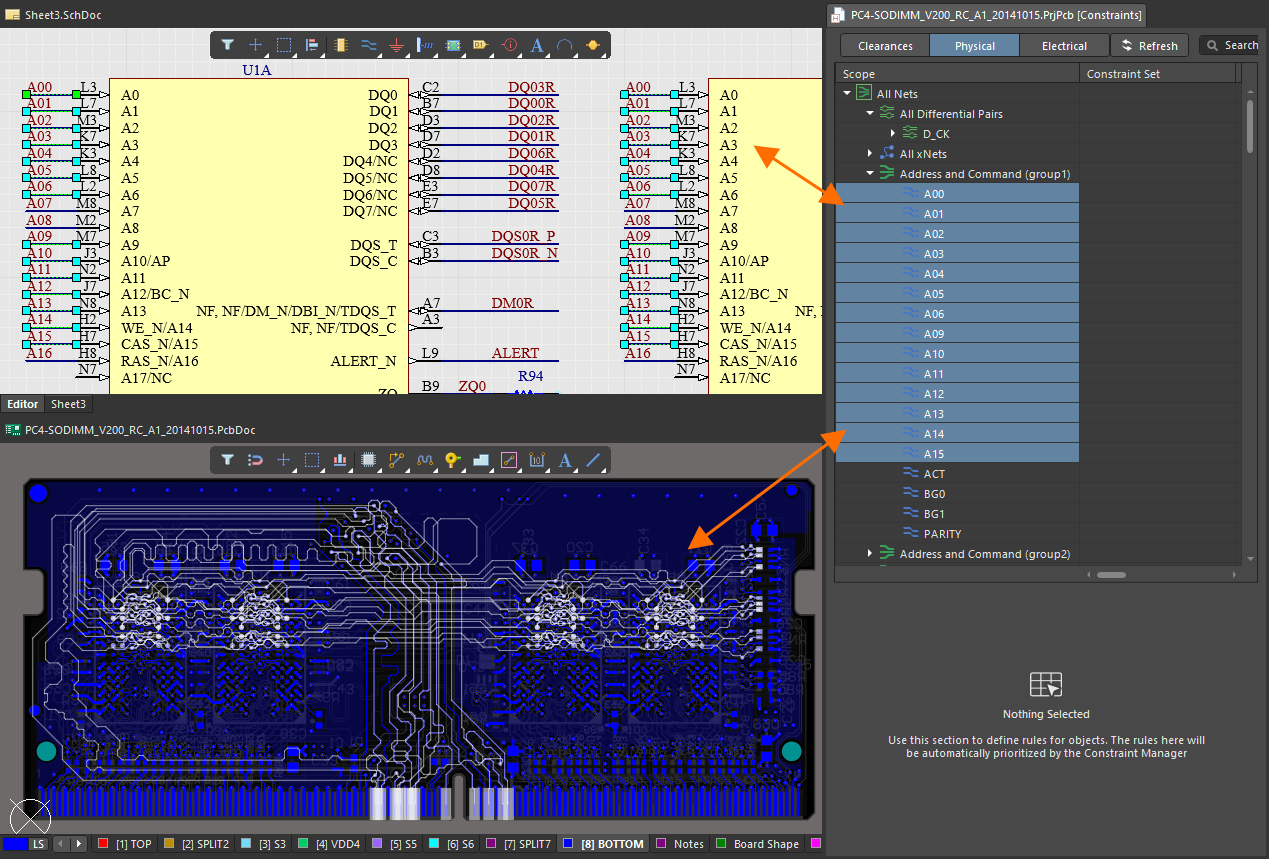

改进类选择

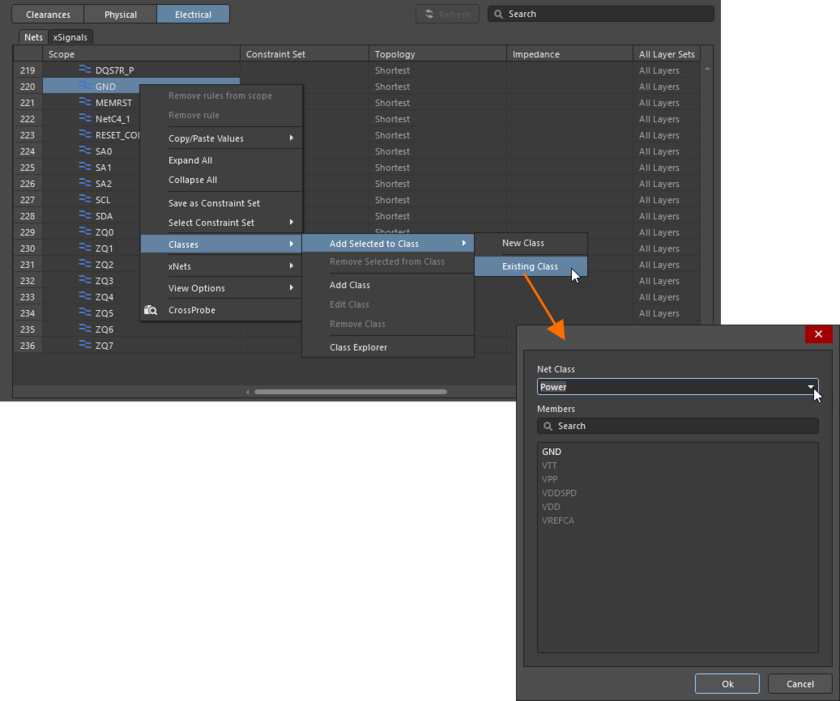

更新了Physical和Electrical视图中的条目的右键单击菜单,从而能够直接从菜单中快速将对象添加到现有类中。操作方法是右键单击一个或多个选定对象,然后从Classes » Add Selected to Class子菜单中选择现有类。

当现有类的数量超过30个时,Classes » Add Selected to Class » Existing Class命令在菜单中可用,而不是类列表可用。使用该命令访问对话框,并在对话框中选择选定对象将添加的现有类。

在栅格中添加了行号

行号已添加到约束管理器栅格中,帮助您更轻松地识别和区分列表中的项目。

多板设计改进

支持多板项目中的Draftsman文档(开放测试版)

现在,您可以添加Draftsman文档(*.MbDwf)到多板项目中,为项目中的多板装配创建制造图。

可以放置在多板项目Draftsman文档中的视图包括:

- 多板视图 – 构成多板装配的PCB轮廓和3D模型的自动图形组合。

- 剖视图 – 从指定“切割”点通过所放置的多板视图的剖面切片图或剖视图。

- 电路板详细视图 – 多板视图划定区域的浮动放大视图。

- 电路板真实视图 – 当前多板装配的可缩放3D渲染。

此外,还提供Draftsman注释、尺寸标注和图形工具,以及BOM和通用表格。

模块入口群组移动功能

添加了在多板原理图文档(*.MbsDoc)中移动一组选定模块入口的功能。这项新功能免除了单独移动每个模块入口的麻烦,加快了编辑过程。先在设计空间中选择多个模块入口,然后使用鼠标左键将该群组拖动到所需位置即可。当这些模块入口被拖动到新位置时,每个入口处将出现一个红点。松开鼠标按钮即可将整个群组放置在当前位置。

线束设计改进

将“Crimps”更改为“Cavities”

接线图和布局图用户界面上的“Crimps”已重命名为“Cavities”。

添加了用于屏蔽和扭转对象的位号标识符字段

在线束接线图的屏蔽和扭转属性中添加了位号标识符字段。

添加了多图Wire Break对象功能

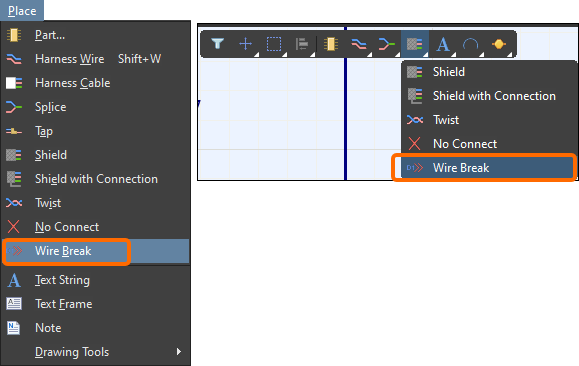

现在,可以在多张图纸上定义完整的接线图(采用“扁平化”设计方式),每张图纸都以原有的*.WirDoc文件表示,并能够使用新的Wire Break对象拆分导线。

使用Place菜单或从Active Bar放置Wire Break,如下所示。

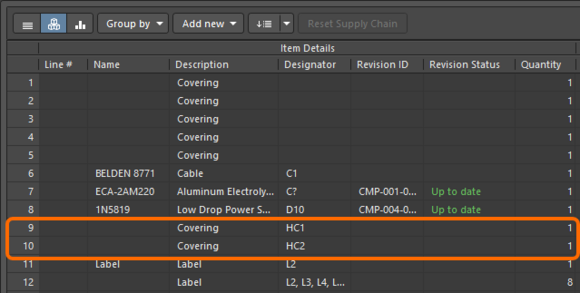

将覆盖物视为BOM中的元件

现在,Layout Drawing中的线束覆盖物被视为BOM中的元件,并支持部件选择和分组。

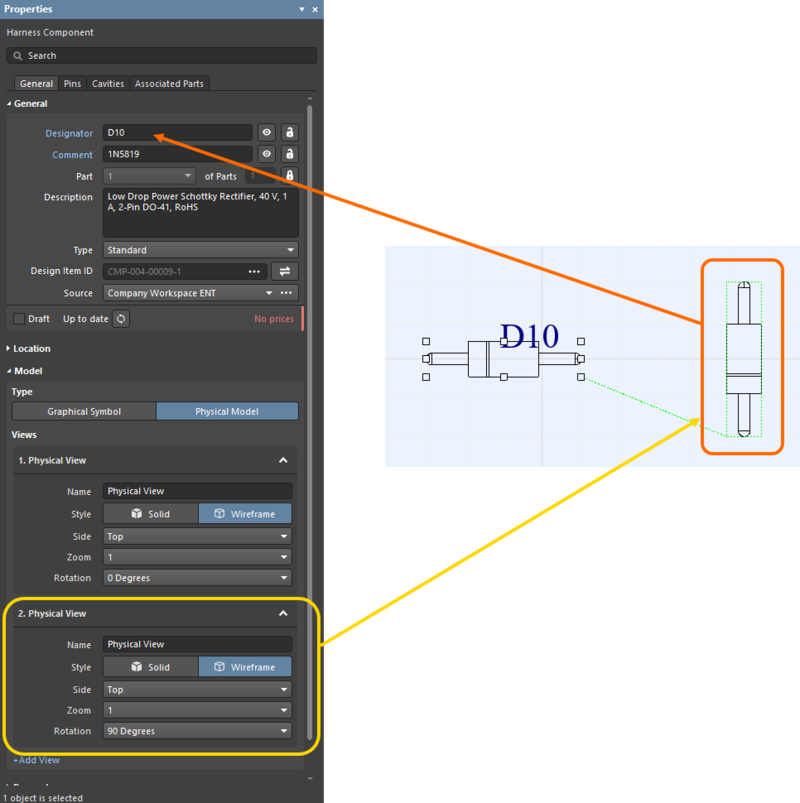

显示附加物理视图的元件属性

现在,在设计空间中选择线束元件的附加物理视图时,Properties面板将显示元件本身的特性,就像选择主(第一个)物理视图一样。在设计空间中选择第二个物理视图的结果如下图所示;Harness Component Properties面板显示的是原始(第一个)物理视图的属性。

改进了接线表

添加了“拆分”接线表功能

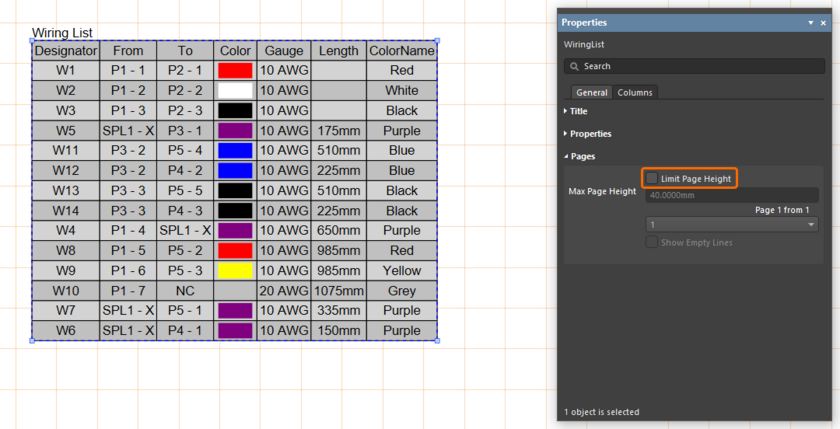

高级线束设计的接线表中可能包含大量条目,这些条目可能难以作为单个表格放入图纸文档中。现在,您无需借助字体和表格缩放功能、多个自定义表格条目或外部文档,即可在Harness Draftsman文档中“拆分”接线表,从而在多个“页面”上显示接线表。在已置入接线表的Properties面板中,启用Pages区域中的Limit Page Height选项即可使用这项新功能。这会将接线表的高度限制为额定高度条目(最大页面高度),从而限制表格中显示的行数。

编辑器检测到整个接线表未显示,如面板上的页面条目所示(例如,2页中的1页),并且关联的下拉菜单允许您指定所显示的页面。如需添加接线表的更多页面,请放置另一个接线表(Place » Wiring List),并在Properties面板的页面区域指定下一个页面。

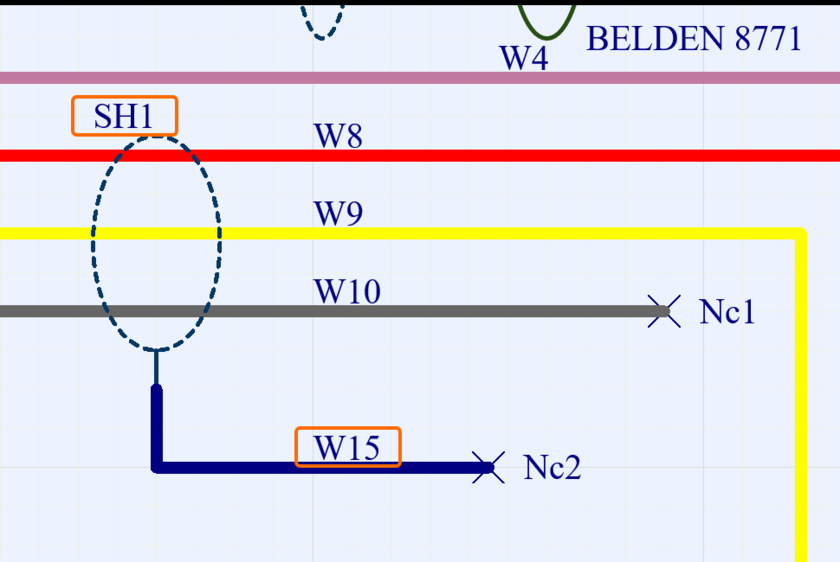

增强了“连接屏蔽”对象的接线表

现在,当导线与屏蔽层的连接器连接时,连接器屏蔽对象的位号标识符将显示在接线表中。

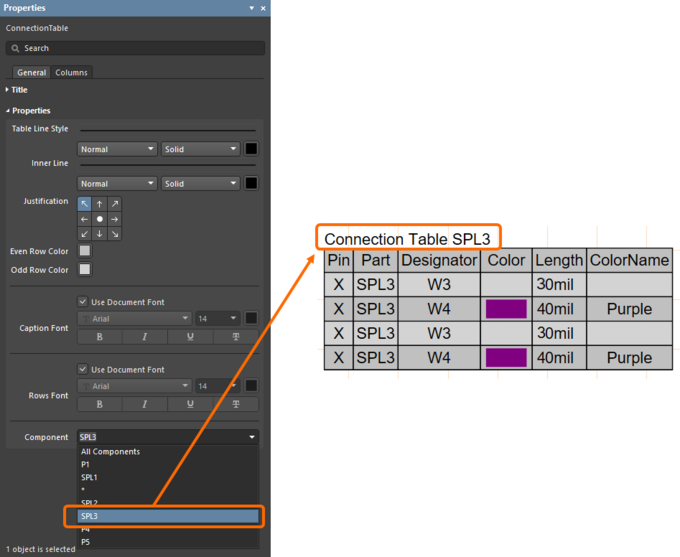

添加了显示接头连接表的功能

添加了显示单个接头的连接表的功能。之前仅显示元件和连接器的连接表。

为文本框和注释对象添加链接以进行交叉探测

现在,可以将对象位号标识符添加为文本框和注释中的活动链接。这些链接可以在接线图和布局图中发挥交叉探测功能。如需创建活动链接,请在接线图或布局图中放置文本框或注释对象。在Properties面板Properties区域的Text字段中输入“@”,此时将出现包含所有位号标识符的下拉列表。双击列表中的目标位号标识符即可在设计空间中的Text字段创建链接。单击设计空间中的链接,对关联文档(即,当前未处于活动状态的文档)中的相应对象进行交叉探测。以下视频将演示这一过程。

数据管理改进

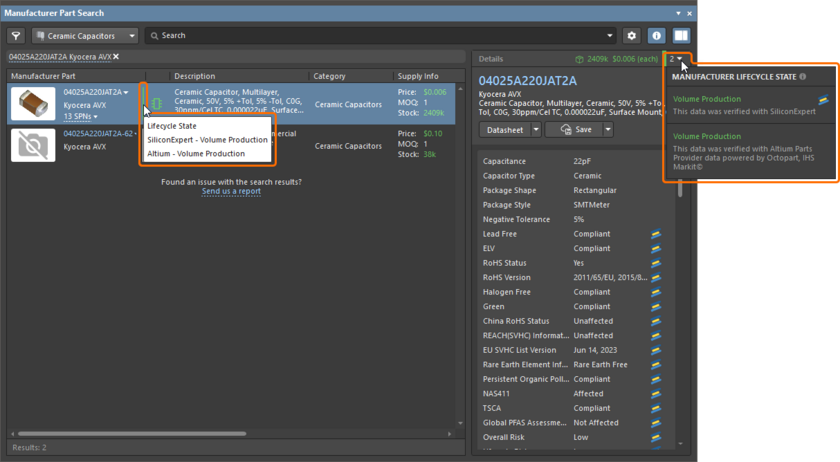

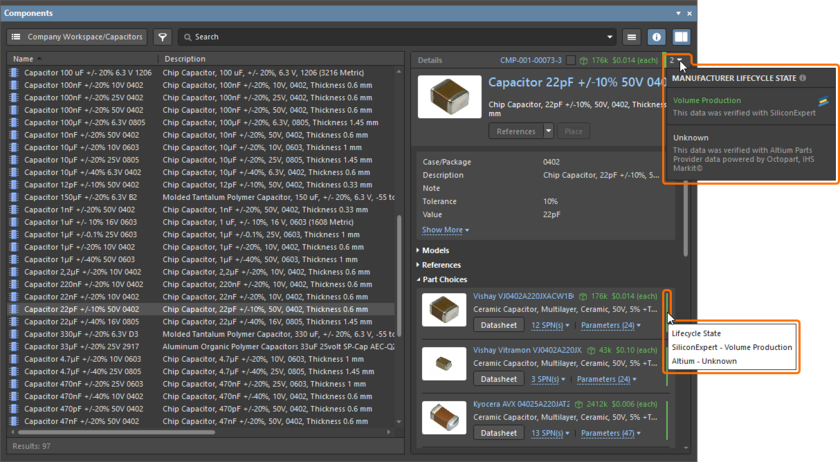

制造商生命周期状态消息增强

使用SiliconExpert集成功能时,可以从以下不同的来源获取制造商部件生命周期数据:Altium Parts Provider(由Octopart或IHS Markit®提供支持)和SiliconExpert。现在,为了改进不同来源的生命周期数据的可视化,可以访问所有可用来源的生命周期信息。

浏览制造商部件数据(例如,Manufacturer Part Search面板中的条目、Workspace库元件中的部件选择或AcitveBOM文档中的解决方案)时,将光标悬停在制造商生命周期状态/栏上或使用下拉列表即可查看工具提示中所有来源的生命周期信息。

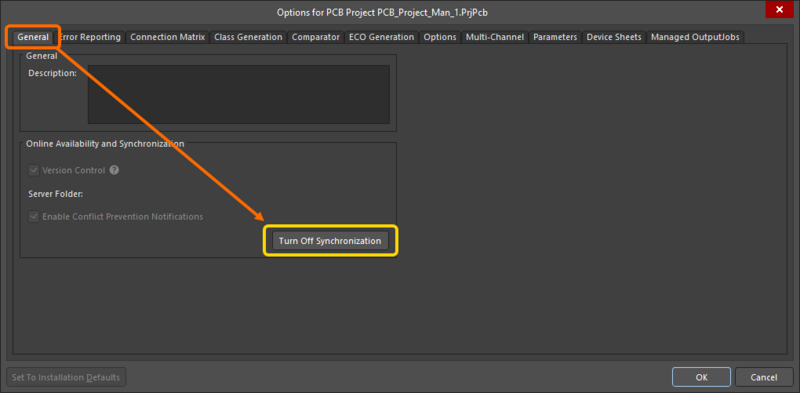

在脱机工作区项目的项目选项中添加了常规选项卡

在脱机工作区项目的Project Options对话框中添加了General选项卡。当您与工作区断开连接时,可使用这一功能来处理项目。该选项卡上唯一可访问的控件是Turn Off Synchronization按钮。单击该按钮可关闭同步功能。这样可以避免将本地副本与工作区内的副本链接。工作区内的项目保持不变。

删除了基于Git的项目的提交命令

对于基于Git的项目,删除了Projects面板和Project主菜单上项目条目右键菜单的History & Version Control子菜单中的Commit命令,以免在使用该命令时混淆数据提交位置(即,提交至本地存储库而不是远程存储库)。命令的可见性从Advanced Settings对话框中的VCS.AllowGitCommit选项(默认为关闭)进行控制。您可以一次性使用Save to Server命令将项目提交到本地存储库,然后将其推送到远程存储库。

导入/导出改进

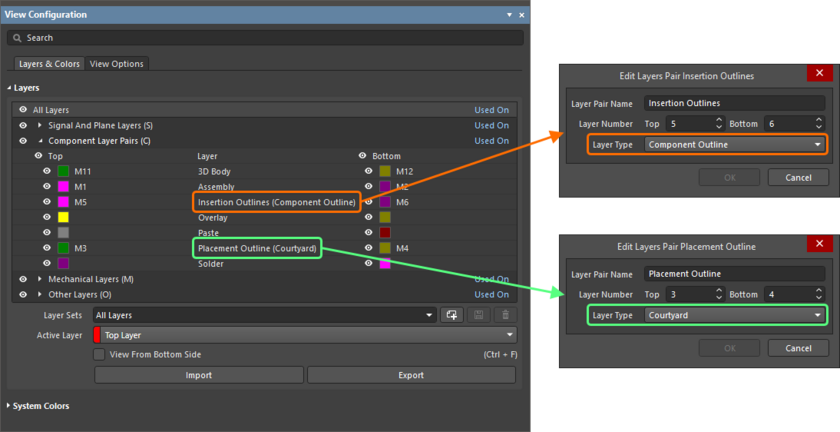

Mentor Xpedition Placement Outline和Insertion Ouline层映射

现在,导入Mentor Xpedition PCB和封装库文件时,Placement Outline层类型被映射为Courtyard层类型,而Insertion Outline层被映射到Altium Designer中的Component Outline层类型。

电路仿真改进

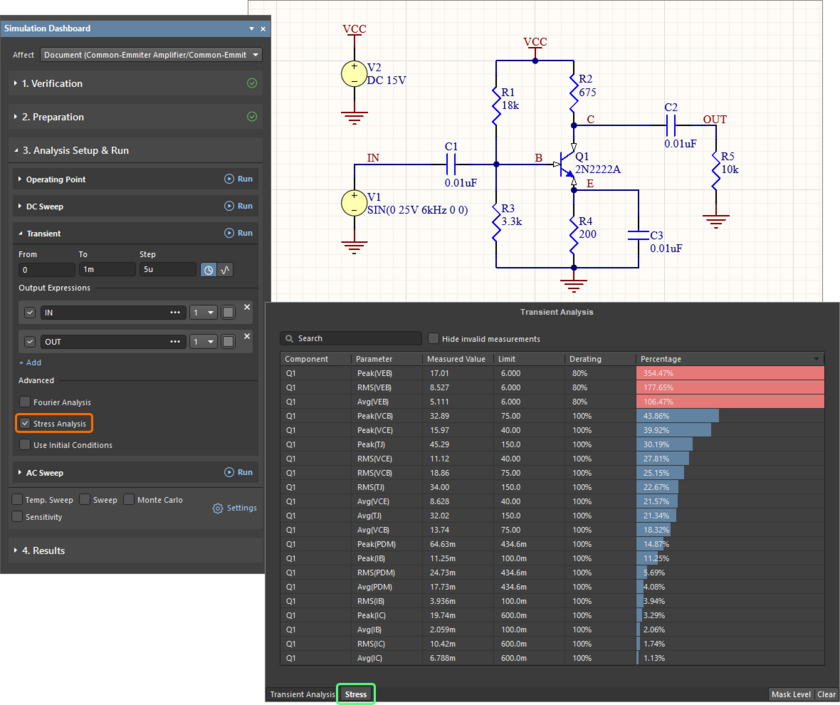

仿真应力分析(开放测试版)

应力分析用于计算每个元件的工作条件(例如,最大电压、电流和功耗),并根据元件应力模型中定义的限值进行检查。

当前版本在Simulation Dashboard的Transient区域添加了一个新的Stress Analysis选项。启用该选项并执行Transient分析后,应力分析结果将显示在仿真结果文档的附加应力图上。

使用新的应力分析根据定义的限值测试电路。

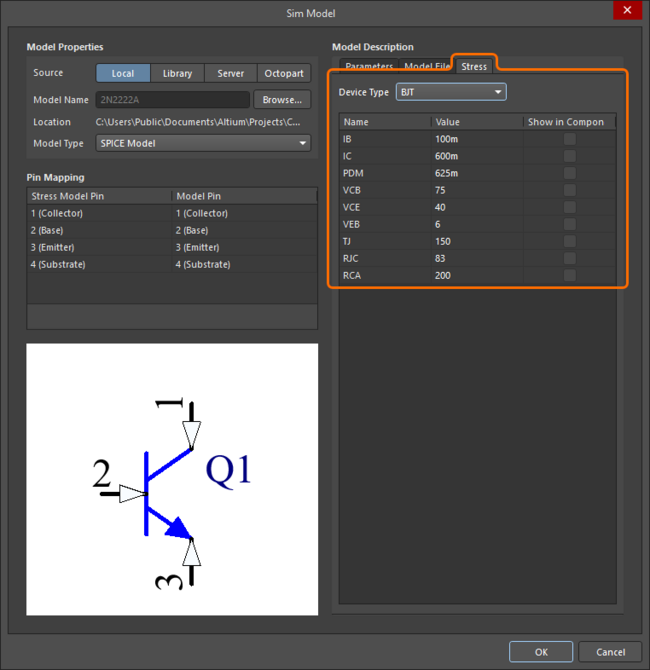

访问元件仿真模型时,可在Sim Model对话框的新增Stress选项卡上配置元件应力模型。您可以在该对话框上选择所需的设备类型并定义参数值。

元件的应力分析参数可以在Sim Model对话框的Stress选项卡上设置。

Altium Designer 24.1功能全面开放

本次发布正式开放当前版本的以下功能:

- 定制助焊层/阻焊层 – 从23.8版本开始提供

Altium Designer 24.0

发布日期:2023年12月13日——版本24.0.1(build 36)

PCB设计改进

任意角度差分对布线器(Open Beta版)

本次发布引入了对任意角度差分对布线的支持。当使用Interactive Differential Pair Routing工具(Route » Interactive Differential Pair Routing)对差分对进行布线时,现在可以在Properties面板中以Differential Pair Routing模式对布线属性进行配置,选定Any Angle转角样式(![]() )。

)。

- 任意角度差分对布线支持对称焊盘入口和间距变化。

- 当从天线开始进行差分对布线时,该工具将保持从左到右的网络顺序(即,左侧的延续性将仍位于左侧)并支持捕捉至原始方向。

- 使用Any Angle转角样式进行差分对布线时,按住Shift键即可使用切线圆弧进行差分对布线。

任意角度差分对布线演示。

请注意,当使用Route » Gloss Selected命令时,此功能还会启用更新后的角度差分对修线算法。

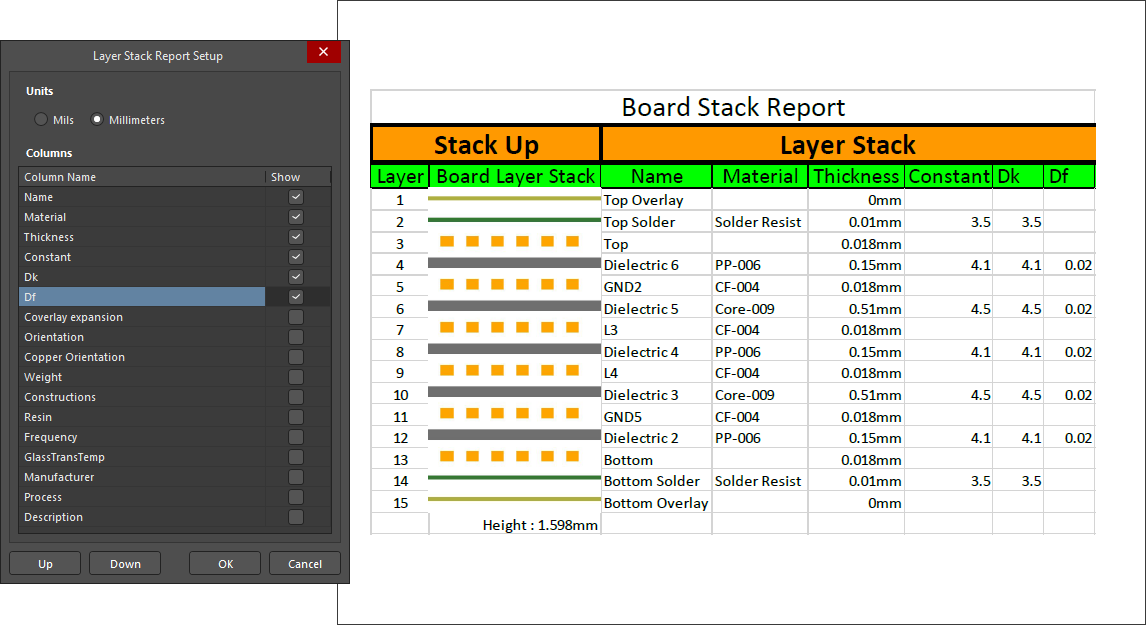

增强版Layer Stack Report Setup对话框(Open Beta版)

Layer Stack Report Setup对话框(File » Fabrication Outputs » Report Board Stack)功能已得到增强,现在包括Layer Stack中存在的所有列。可以使用该对话框选定想要在Layer Stack Report中显示的列。

PCB CoDesign改进

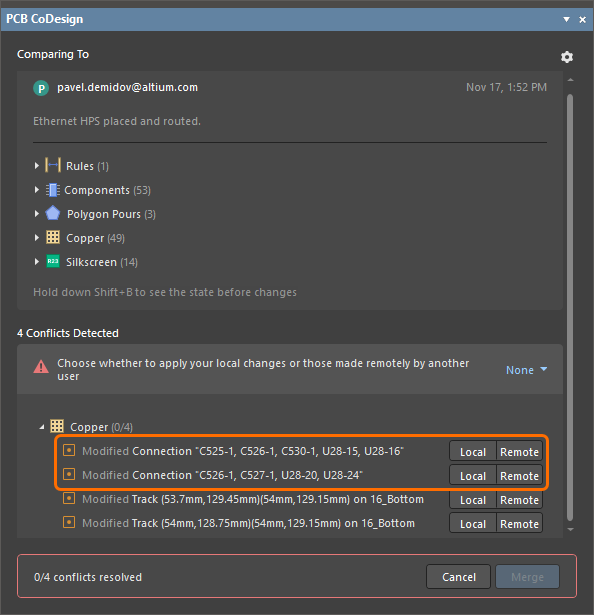

增强版铜皮冲突显示和解决

现在可根据具体情况,将铜皮对象冲突分为引脚间连接组,以便于探索和解决更改。

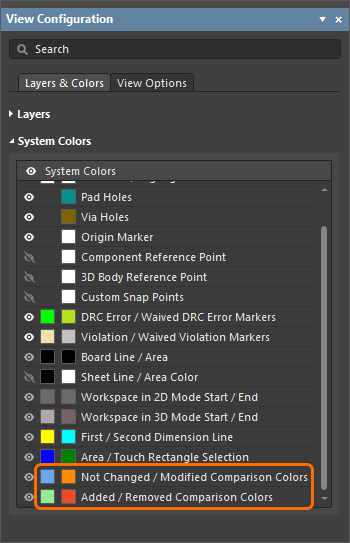

添加了颜色图例配置功能

您现在可以在View Configuration 面板中,为已添加、修改、删除和未更改的对象(在PCB CoDesign面板中选定引脚间连接时未更改的对象)选定颜色。

使用View Configuration面板,对比较颜色图例进行配置。

使用View Configuration面板,对比较颜色图例进行配置。

其他PCB CoDesign UI更改

- 显示正在进行比较的弹出窗口,现在将在运行比较后立即弹出。

- 添加了在更改列表中选定和取消选定入口的功能。当某个入口(通过单击该入口)已被选定时,再次单击即可取消选定该入口并将设计区内的对象高亮显示重置。

-

在使用PCB CoDesign面板将更改合并后显示的Project面板Merged图标(

)菜单中,添加了Save to Server命令 – 显示图像。

)菜单中,添加了Save to Server命令 – 显示图像。 - 合并更改后,单击PCB CoDesigner面板上的Save to Server按钮时,将在Save to Server对话框中默认仅选定合并后的PCB文档 - 显示图像。

- 运行合并更改时,现在将会出现一个新弹出窗口,提示正在进行合并 - 显示图像。

约束管理器改进

将差分对类别添加到间距矩阵中

自本次发布以后,您即可将网络类和差分对类添加到Clearances Matrix(Clearances视图)中。

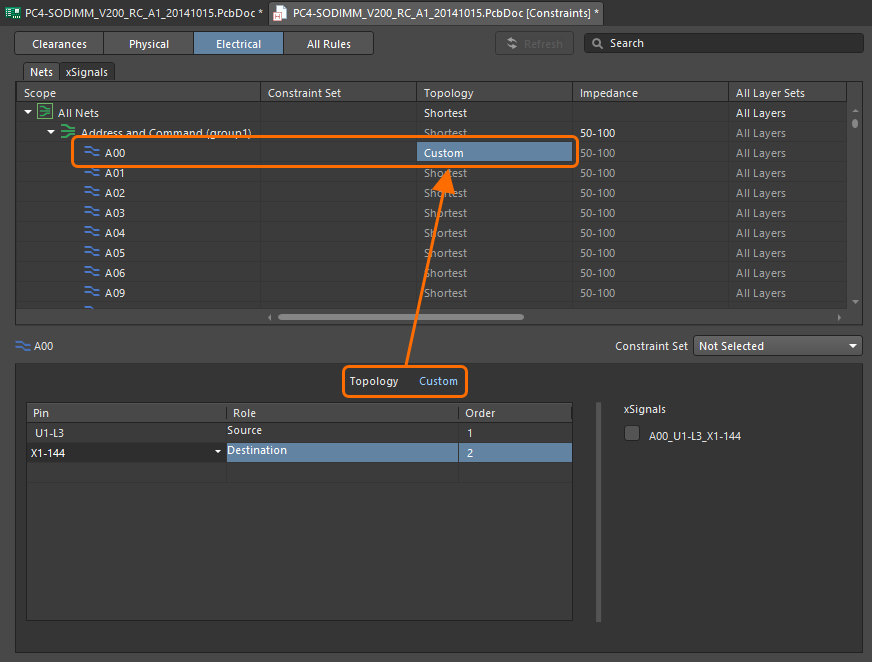

在PCB端对自定义拓扑结构进行编辑

现在可以将网络的拓扑结构定义为Custom,并在从PCB端访问网络时根据需要在Constraint Manager中对其进行编辑。

编辑约束集时传播拓扑结构更改

当对包含自定义拓扑结构的Constraint Set进行编辑时,对拓扑结构所做更改现在将传播到应用此Constraint Set的其他对象。

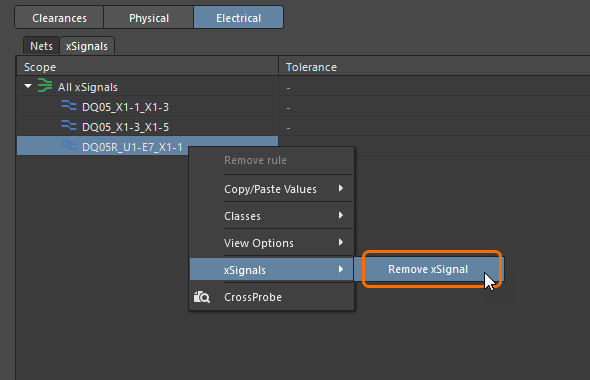

具备了删除xSignals的能力

现在可以从Electrical视图的xSignals选项卡中,删除xSignal。操作时,请右键单击xSignal,然后从上下文菜单中选定xSignals » Remove xSignal命令。

Constraint Manager交叉选定

在本次发布中,添加了从Constraint Manager中交叉选定对象的功能。(使用Constraint Manager、原理图或PCB编辑器Tools主菜单中的Cross Select Mode命令)启用交叉选定模式后,在Constraint Manager中选定的对象亦会在原理图和PCB文档中被选定,反之亦然。

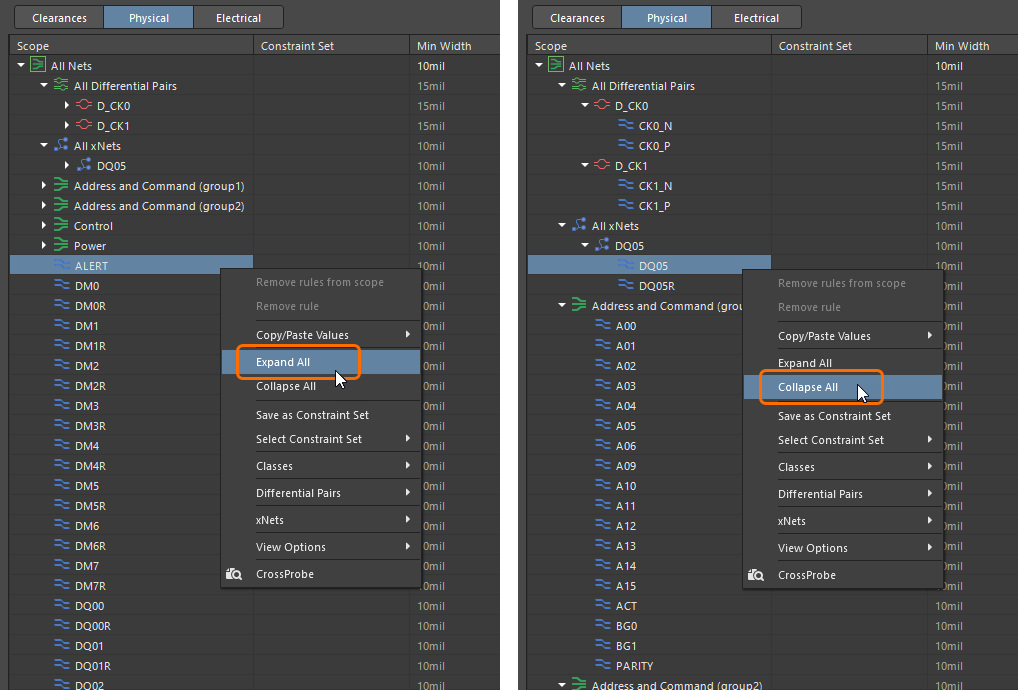

增强了展开/折叠状态

除预定义节点(例如,All Nets)以外,所有节点现在均默认在Physical和Electrical视图中折叠。您可以使用新Expand All和Collapse All右键单击菜单命令来控制网格节点。

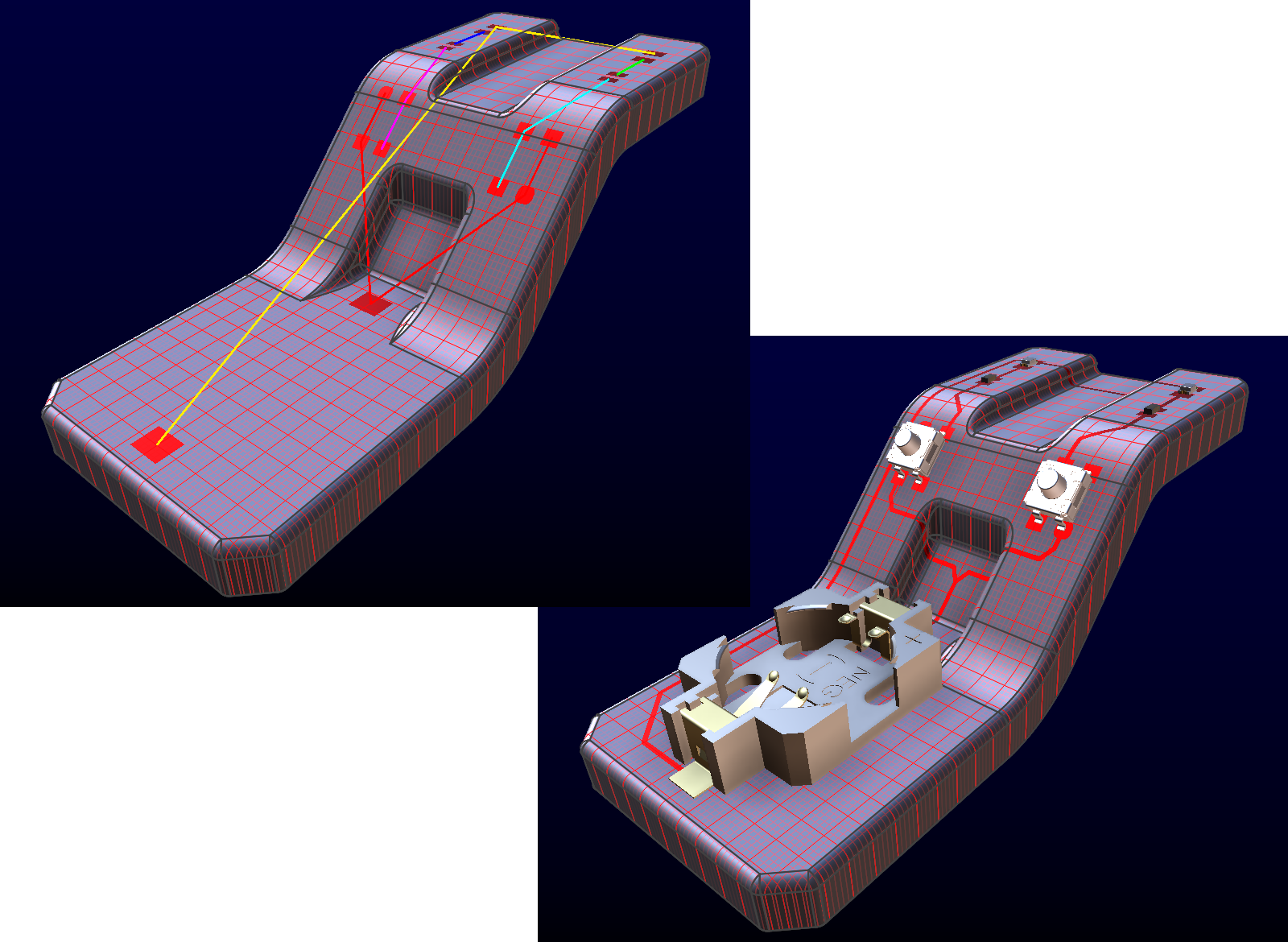

3D-MID设计(Open Beta版)

3D-MID技术将电路与三维机械部件相结合。此项功能融合给各种应用领域带来了无限可能。

一直以来,由于缺乏合适的ECAD工具,3D-MID设计人员通常仅限于使用MCAD封装。这种工作方式会存在许多固有问题,尤其是其无法通过电气智能来驱动电路布局,并且存在与将2D手动绘制草图投影到3D表面相关的困难。

Altium Designer中新3D-MID编辑器允许您将标准表贴元件放置在3D-MID文档内的3D形状上,并沿形状表面进行导线布线以完成布局。

然后,可以将完成的设计导出为Laser Direct Structuring(LDS)制造工艺所需的文件格式。

线束设计改进

将布局标签视为BOM中的元件

Layout Drawing中的布局标签现在被视为BOM中的元件,并支持部件选择和分组。

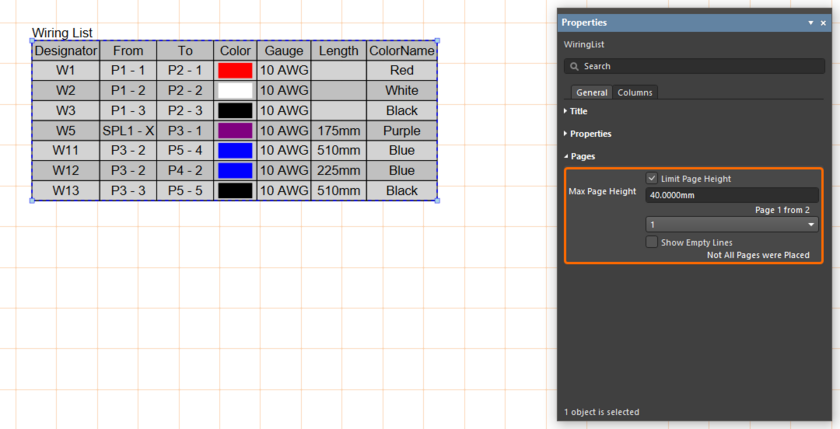

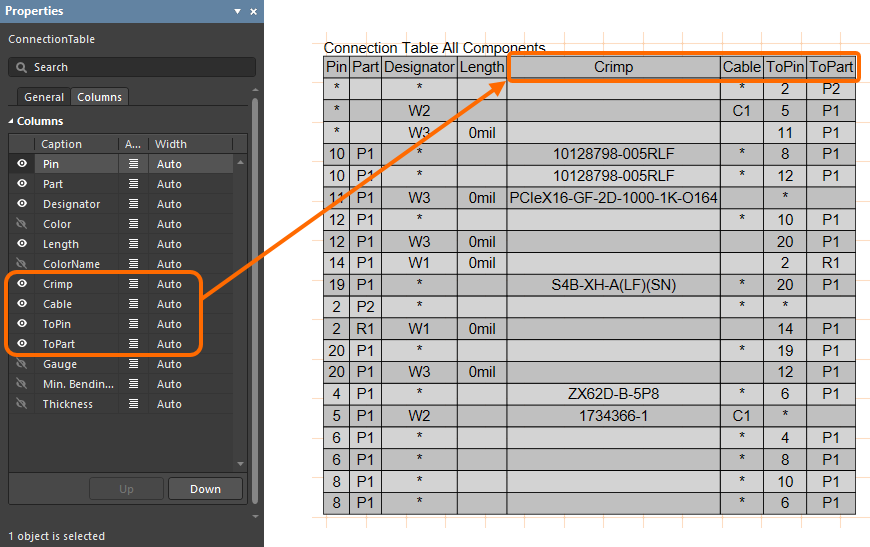

在连接表和接线列表中添加了列

在Manufacturing Drawing(*.HarDwf)的Connection Table和Wiring List中添加了其他列,以确保您可以轻松查看设计区内的附加信息。Crimp(部件编号)、Cable、ToPin和ToPart均已添加到Connection Table中;FromCrimp、ToCrimp和Cable均已添加到Wiring List中。在Properties面板中切换眼睛图标,以显示/隐藏连接表中的所需列。

平台改进

支持长路径名称(Open Beta版)

在本次发布中,实现了对长路径名称的支持。当文件名称的文件路径超过256个字符时,现在支持对文件执行以下操作:

- 从连接的Workspace打开项目。

- 使本地项目在Workspace中可用。

- 更改Outjob文件中的文件夹路径。

- 使用Outjob文件或Project Releaser生成输出。

- 将项目作为项目模板保存到Workspace中。

自Windows 10版本1607开始,已将MAX_PATH限制从常用Win32文件和目录函数中删除。但是,您必须通过更改Altium Designer所在计算机的注册表项来选择加入新功能。如需了解更多信息,请参阅Support for Long Path Names页面。执行此操作后,请务必重新启动计算机。

导入/导出改进

xDX Designer导入增强功能

本次发布中提供了许多与将xDX Designer设计文件导入Altium Designer相关的关键改进和修复。

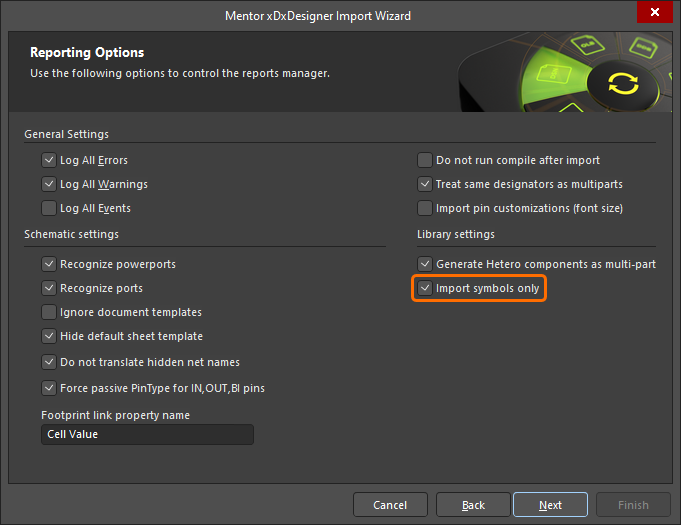

添加了仅导入符号功能

Mentor xDxDesigner Import Wizard的Reporting Options页面现在包括仅允许导入符号的Import symbols only选项。启用此选项后,即使原始元件库中多个元件使用该符号,元件库数据库中的相同符号亦将作为单个原理图符号导入,并且参数不会导入到Altium Designer中的符号内。

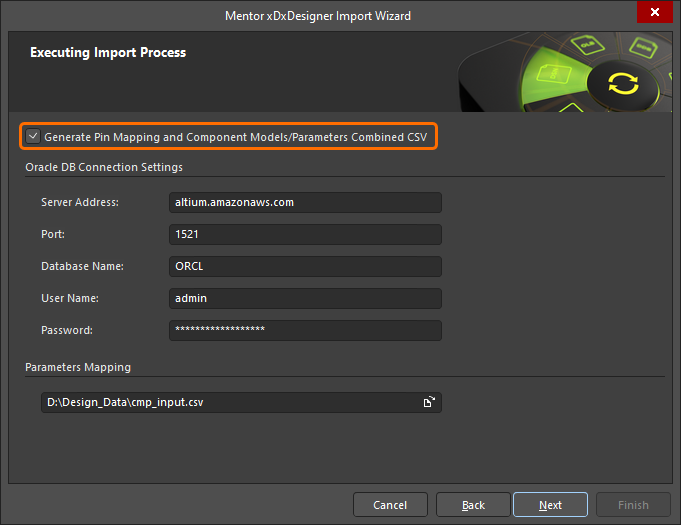

此外,启用此选项后,Wizard的下一页将建议通过启用Generate Pin Mapping and Component Models/Parameters Combined CSV选项,以CSV格式生成部件符号和引脚映射数据。启用此选项后,即可使用可用字段对Oracle DB连接参数和参数映射文件进行定义。

多部件符号导入改进

导入Altium Designer时,多部件符号会收到一个Design Item ID,以及在xDX Designer中定义的第一个和最后一个部件名称。此类组合型Design Item ID亦可用在生成的CSV文件中。

此外,将符号中部件导入Altium Designer的顺序现在与原始元件库中定义的顺序相同。

符号导入改进

其他导入改进包括:

- 现在可导入符号中的静态文本字符串。

- xDX Designer中用于否定的‘~’字符现在被转换为引脚名称中的‘\’字符,以确保可在Altium Designer中正确表示否定符号。

-

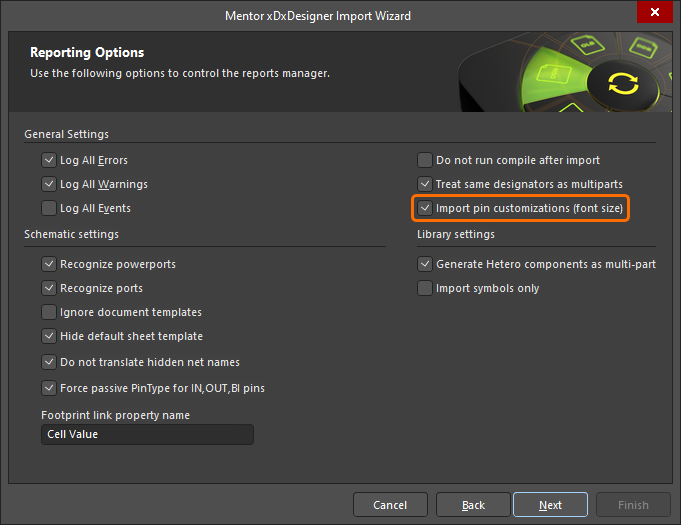

Mentor xDxDesigner Import Wizard的Reporting Options页面现在包括Import pin customizations(字体大小)选项。启用此选项后,引脚位号标识符和名称均将以与xDX Designer中的相同字体大小,被导入Altium Designer。

Mentor Expedition导入改进

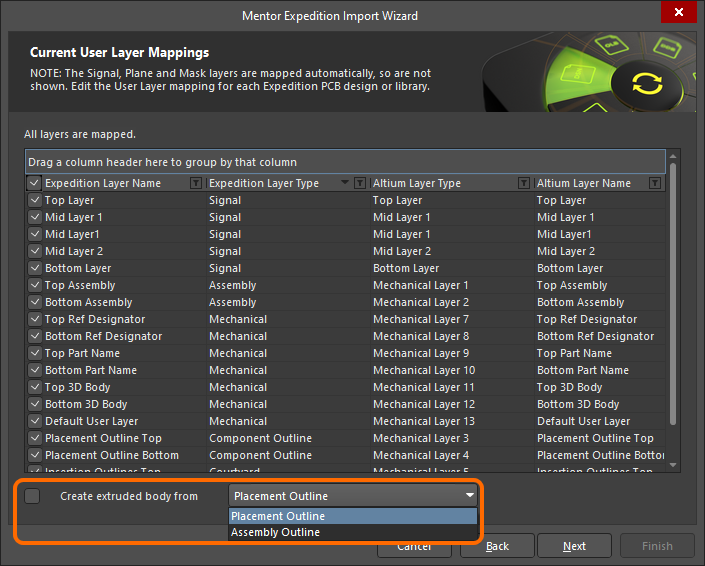

添加了选择挤压体层的功能

您现在可以在使用Import Wizard导入Mentor Expedition文件时,选定创建挤压体时需要的层。添加想要导入的Mentor PCB和Library文件后,使用Current User Layer Mappings页面上的Create extruded body from drop-down从Placement Outline或Assembly Outline中进行选择。启用该选项后,其将默认为Placement Outline。

Placement Outline改进

现在可以将Placement Outlines作为基元导入到Top/Bottom 3D Body组装层的Placement Outline上。

电路仿真改进

P-Channel晶体管的输出电流反相

P-Channel晶体管(BJT、JFET、MOSFET、MESFET)的输出电流现在将被视为流入电流,以确保其与N-Channel晶体管一致。

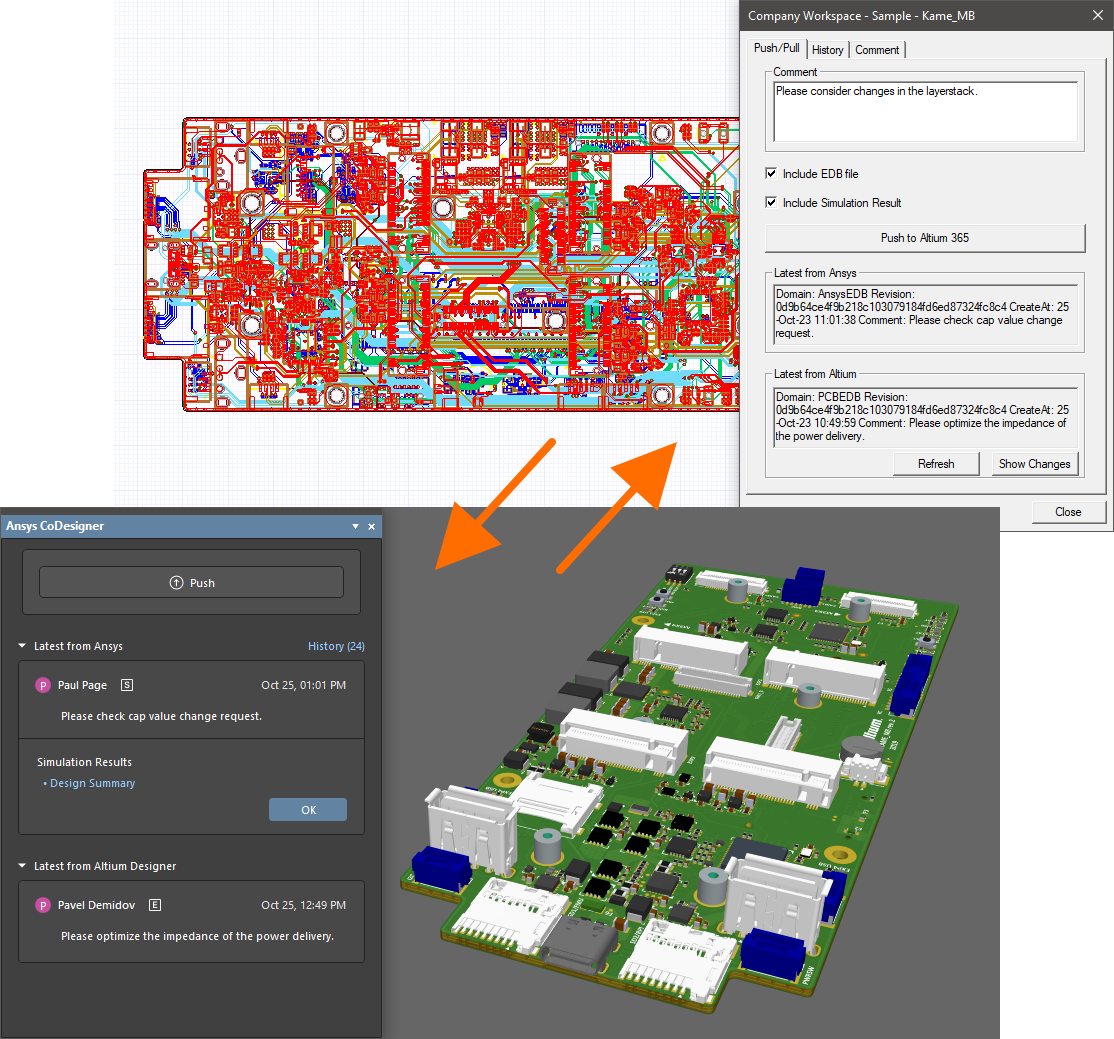

Ansys CoDesigner(Open Beta版)

本次发布介绍了在ECAD与Simulation域之间实现真正协作设计(CoDesign)的第一步。到目前为止,这两个孤立领域的工程师不得不依赖手动导出/导入文件流程,这些流程与设计修订以及变更和结果的沟通(通常通过电子邮件)只能在设计领域之间手动交互。

随着Ansys CoDesigner功能的推出,ECAD工程师(使用Altium Designer)现在可以与SIM工程师同事(使用Ansys Electronics Desktop(AEDT))进行无缝协作设计。Altium 365 Workspace将作为两个领域之间的桥梁,促进双方开展协作。本次首次发布包括对以下关键元素的支持:

- 两个领域之间可实现设计更改双向推/拉。在Altium Designer中,可以检测针对层堆栈以及材料、元件和基元所做的更改,并可在AEDT中进行应用。从AEDT中,可以通过EDB文件,推送针对层堆栈和材料的拟议更改,并在Altium Designer中进行检测/应用。

- 可将仿真结果从AEDT推送到Altium 365 Workspace,并与设计修订建立关联,以通过Workspace的浏览器界面对其进行查看,并在Altium Designer中进行预览。

- 使用注释系统进行双向通信,且每个注释线程均随附于设计中的特定元件。

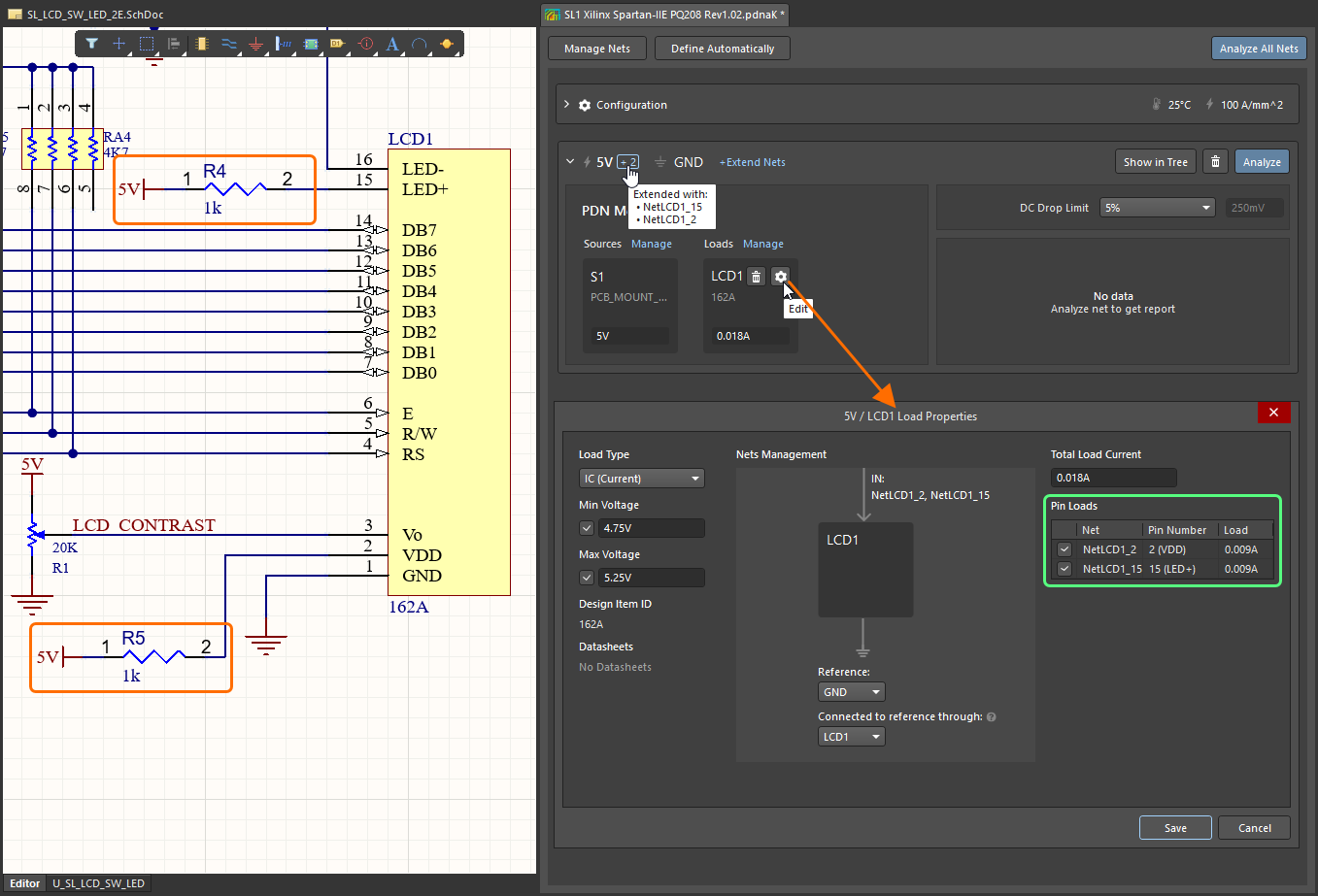

Power Analyzer by Keysight改进

添加了在同一元件上为多个网络分配电流的功能

在本次发布中,添加了在同一元件上为不同串行元素的多个网络分配电流的功能。

配置IC(Current)型负载时,您可以看到负载元件的所有引脚,这些引脚通过不同串行元件与源连接,并能够选定所需的引脚。

在以下示例中,5V电源网络通过R4和R5串行元件连接到LCD1元件的两个引脚。扩展电源网络并将LCD1作为负载添加后,可根据需要在Load Properties对话框中对两个引脚进行选定和配置。

Altium Designer 24.0中完全公开的功能

以下功能现已在本次发布中正式公开:

- 约束管理器 - 自23.11版开始提供

- PCB CoDesign - 自23.10版开始提供

- 线束设计 - 自23.0版开始提供

- 改进版最小孔环违规检测 - 自22.10版开始提供