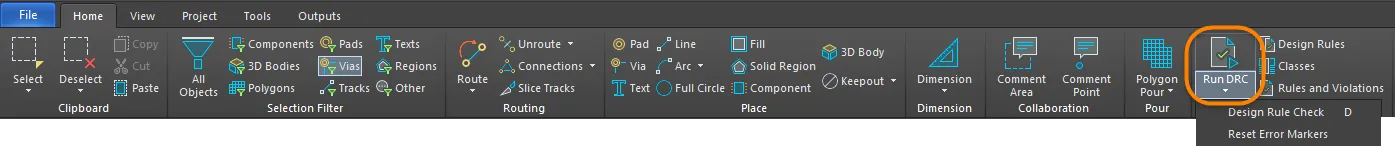

DRCを実行

- 設計ルールチェックを実行し、Design Rule Verification Report(設計ルール検証レポート)を作成します。

-

Design Rule Checker ダイアログを開きます。 - PCB内のエラーマーカーをリセットします。

これらのコマンドは、PCBエディタの

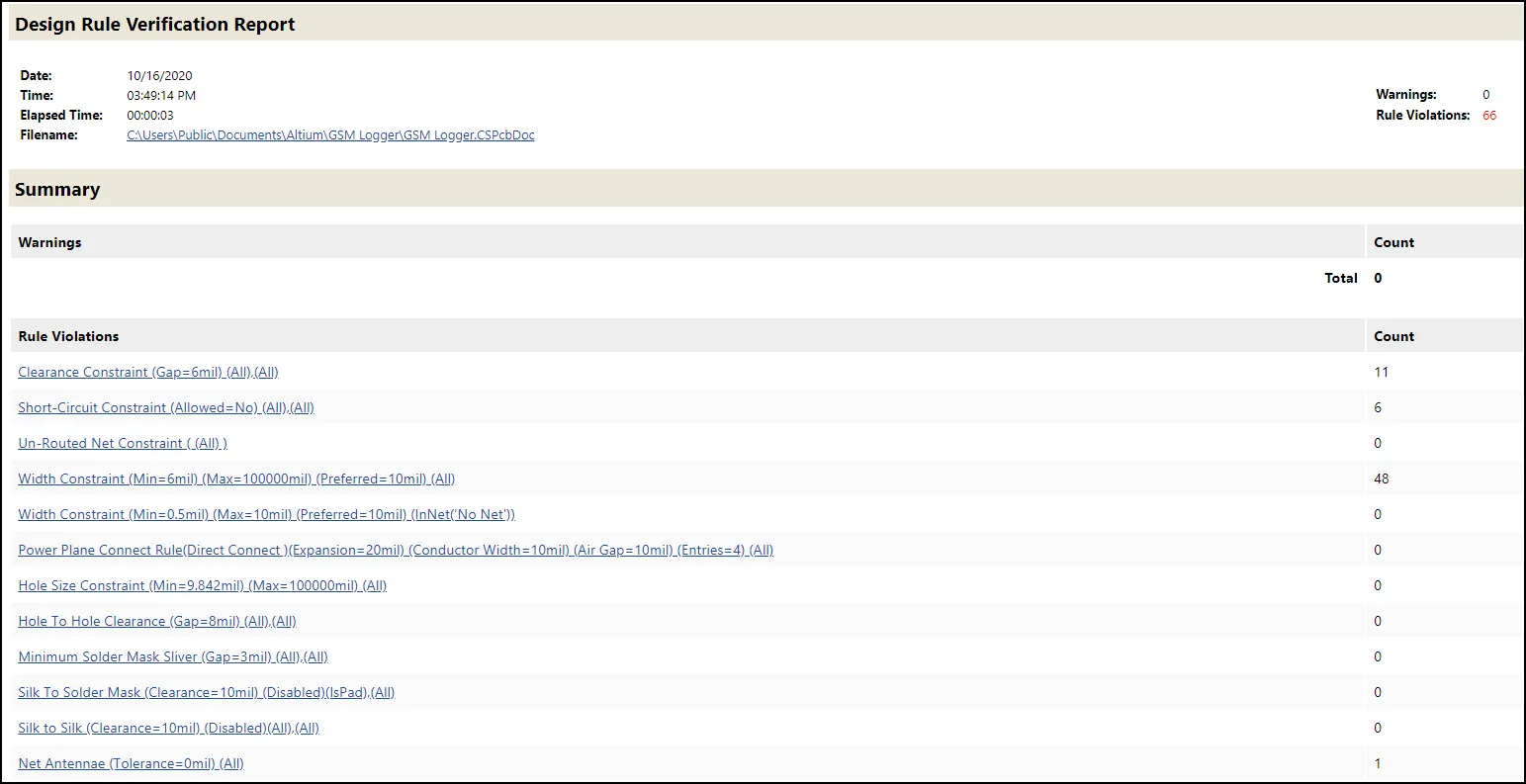

![]() をクリックすると、バッチチェック用に有効化されたルールおよびこのチェックタイプ用に定義された追加オプションに従って設計ルールチェックが実行され、その後 Design Rule Verification Report が開きます。設計ルールチェックは、設計の論理的および物理的な整合性をチェックする強力な自動機能です。以下にレポートの例を示します。

をクリックすると、バッチチェック用に有効化されたルールおよびこのチェックタイプ用に定義された追加オプションに従って設計ルールチェックが実行され、その後 Design Rule Verification Report が開きます。設計ルールチェックは、設計の論理的および物理的な整合性をチェックする強力な自動機能です。以下にレポートの例を示します。

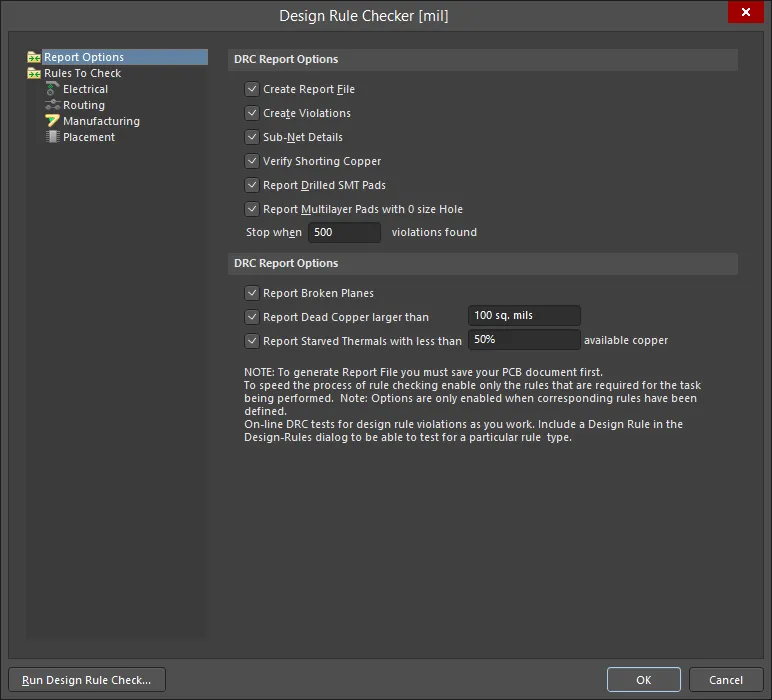

Design Rule Checker ダイアログ

このダイアログでは、基板の設計ルールチェックを設定できます。有効化された任意またはすべての設計ルールに対してチェックを行うことができ、オンライン、設計中、またはバッチ処理(オプションでレポート付き)として実行できます。この機能は、すべての配線済み基板で最小クリアランスルールが守られていること、他に設計違反がないことを確認するために使用すべきです。特に、最終アートワークを生成する前には必ずバッチモードの設計ルールチェックを実行することを推奨します。

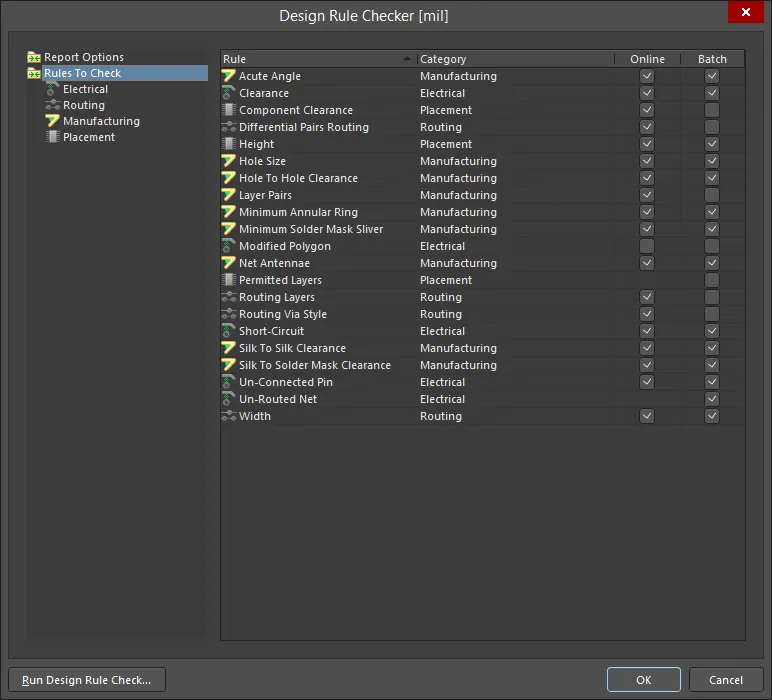

このダイアログの機能は2つの領域に分かれています。

- バッチDRCに関するオプションの設定。

- どのルールをチェックするか、およびそれらのルールをオンラインおよび/またはバッチDRCの一部としてチェックするかどうかの設定。

これらの領域は、左側ペインのフォルダのようなエントリで反映され、アクセスできます。

-

Run Design Rule Check - クリックすると、バッチチェック用に有効化されたルールおよびこのチェックタイプ用に定義された追加オプションに従ってバッチDRCを実行します。

レポートオプション

DRCレポートオプション

-

Create Report File - 有効にすると、基板のバッチDRC実行後にレポートが生成されます。

-

Create Violations - 有効にすると、定義された違反表示設定に従って設計空間内で違反がハイライト表示されます。このオプションは、違反がViolations 領域のPCB Rules And Violations パネルにリスト表示されるためにも必要です。

-

Sub-Net Details -Un-Routed Net ルールが定義されている場合、このオプションを有効にすると、DRCレポートにサブネットの詳細が含まれます。

-

Verify Shorting Copper - 設計で使用されているNet Tieコンポーネント内のショート銅箔の整合性を検証する場合に有効にします。このチェックは、コンポーネント内で他のパッドと正しくショートしていないパッドがある場合など、未接続の銅箔がないかを確認します。 -

Report Drilled SMT Pads - DRCレポートに誤ってドリル加工されたSMT(表面実装技術)パッドを含める場合に有効にします。

-

Report Multilayer Pads with 0 size Hole - 設計内で見つかった無効な多層パッドを含める場合に有効にします。無効な多層パッドとは、穴径がゼロであり、実質的にSMTパッドとなるものです。 -

Stop when n violations found - バッチDRCプロセスが停止するまでに検出できる違反の最大数を決定するために使用します(デフォルト =500 )。報告される違反数を制限することは、チェックプロセスを管理しやすくするための重要な戦略です。 -

Report Broken Planes - バッチルールチェックプロセスで、ブロークンプレーン(切断されたプレーン)を検出・報告する場合に有効にします。ブロークンプレーンは、ネットに接続されたプレーン領域が他のプレーン部分から電気的に切断された場合に発生します。例えば、分割プレーンをまたいでコネクタが配置されているが、プレーンに接続されていない場合などです。ピン周囲の空隙がつながってプレーン銅箔を完全に切断し、実質的に2つの部分に分かれます。

-

Report Dead Copper larger than - バッチルールチェックプロセスで、指定した面積より大きいデッドカッパー領域(ネットに接続されていない銅箔領域)を検出・報告する場合に有効にします。デッドカッパーとは、ネットに接続されておらず、元の親プレーンからも電気的に切断された銅箔部分を指します。例えば、プレーンに接続されていないコネクタのピン間隔が狭く、ピン周囲の空隙がつながってプレーン銅箔の一部が他の部分から孤立する場合などです。関連フィールドで、違反とみなす最小許容面積の値を指定します(デフォルト =100 sq. mils )。

-

Report Starved Thermals with less than n% available copper - バッチルールチェックプロセスで、指定したパーセンテージより大きいスターブドサーマル接続(熱的に孤立したサーマル接続)を検出・報告する場合に有効にします。サーマルとは、プレーンへの接続部に熱伝導を抑えるためのカットアウト(サーマルリリーフ)が設けられたものです。サーマルの銅スポークの表面積が空隙によって減少すると「スターブド(飢餓状態)」となります。このオプションでは、スポークだけでなくサーマル全体の表面積も空隙による減少分と比較してチェックします。関連フィールドで、違反とみなす最小許容接続銅パーセンテージの値を指定します(デフォルト =50% )。

チェックするルール

- バッチチェックプロセス中にテストされた各ルールが、生成されたデザインルール検証レポートに一覧表示されます。検出された各違反は、レイヤー、ネット名、コンポーネントデジグネータ、パッド番号などの参照情報や、オブジェクトの位置とともに詳細に記載されます。違反オブジェクトのエントリをクリックすると、デザイン空間内でそのオブジェクトにクロスプローブできます。

-

デザイン空間でルール違反を表示する際の柔軟性を高めるために、2種類の違反表示タイプ(違反詳細(カスタム違反グラフィック)と違反オーバーレイ)には、それぞれ個別のシステムカラーが割り当てられています。これにより、異なる明確な色で両者を区別できます。カラーの割り当ては

View Configuration パネルで行います。-

Violation Details –DRC Detail Markers システムカラーに割り当てられた色を使用します。 -

Violation Overlay –DRC Error Markers システムカラーに割り当てられた色を使用します。

-

-

バッチDRCを実行した後、

Messages パネル内の違反メッセージをダブルクリックすると、デザイン空間内でその違反を引き起こしているオブジェクトにクロスプローブできます。 -

オンラインまたはバッチDRCを実行すると、すべてのルール違反が

Violations 領域のPCB Rules And Violations パネルに一覧表示されます。 -

特定のデザインオブジェクトに関連する違反は、PCBデザイン空間内で直接調査できます。違反オブジェクトの上にカーソルを合わせて右クリックし、

Violations サブメニューからコマンドを選択してください。オブジェクトが関与している個別の違反を調査するか、Show All Violations コマンドを使って関与しているすべての違反を表示することができます。いずれの場合も、Violation Details ダイアログが開き、詳細な違反情報や、違反オブジェクトのハイライトやジャンプのためのコントロールが提供されます。

AI で翻訳

AI で翻訳