KB: 의도적으로 두 개의 다른 그물을 짧게 만듭니다

솔루션 세부 정보

1 넷 타이 컴포넌트 생성

2 신호 하네스 사용

3 0옴 저항 컴포넌트를 명시적으로 배치합니다

설계에서 서로 다른 두 개의 네트를 단락시키기 위한 기본 접근 방식은 네트 타이 컴포넌트를 생성하는 것입니다.

1 *.pcblib을 연 상태에서 두 개의 패드를 풋프린트에 배치합니다

2 중간에 구리 리전으로 단락시킵니다.

3 구리 리전이 패드 측면으로만 확장되고 패드 중앙의 스냅 지점까지 확장되지 않도록 합니다. 그렇지 않으면 연결 트랙과 폴리곤이 나중에 디자인에서 패드의 스냅 지점에 연결되지 않습니다.

반면에 넷 타이가 확인에 실패했다는 오류 메시지가 표시되는 경우: [...] DRC 검증 중에 구성 요소를 배치한 설계 후반부에 구리가 분리되어 있다면 두 패드 사이의 단락 구리가 너무 작기 때문일 수 있습니다. 또는 풋프린트에 단락 구리가 없는 다른 플로팅 패드/비아가 있을 수 있습니다.

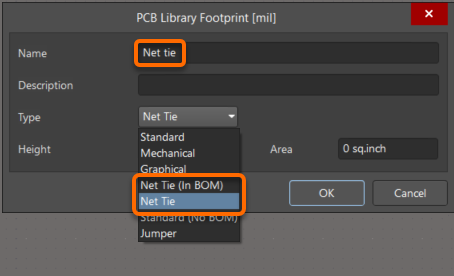

4 도구 " 풋프린트 속성에서 이름을 지정하고 풋프린트 유형을 넷 타이 옵션 중 하나로 설정합니다.

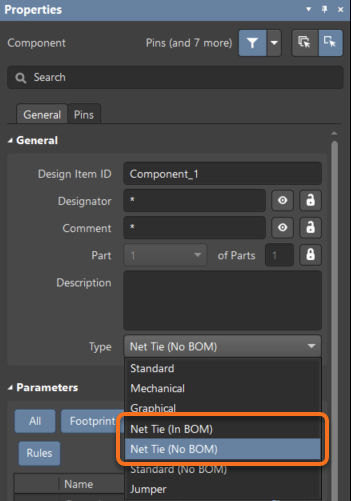

5 *.schlib 파일에 해당 회로도 기호를 생성하고 속성 패널을 사용하여 기호 유형을 Net Tie 옵션 중 하나로 설정합니다

6 1~4단계에서 생성한 풋프린트를 5단계: 회로도 라이브러리의 회로도 라이브러리 심볼에 추가합니다

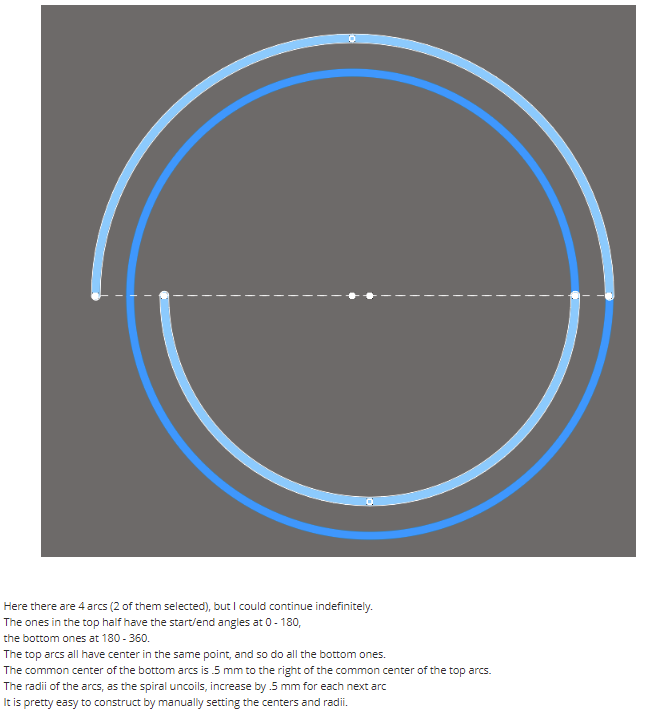

아래는 여러 개의 아크를 함께 배치하여 나선형 패턴을 형성하는 방법에 대한 시각적 예시입니다

넷 타이 컴포넌트에 대한 자세한 정보:

넷 타이를 사용하여 PCB 설계 요구 사항 충족하기

의도적으로 두 개의 네트 연결

네트 타이 컴포넌트로 두 개의 네트 연결하기

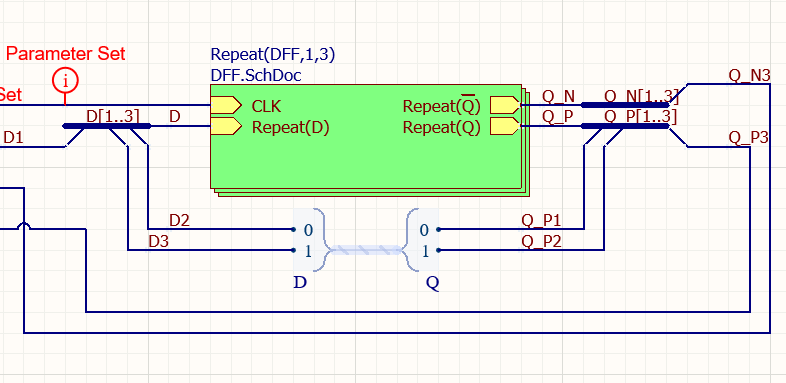

넷 타이 컴포넌트를 통해 추가 풋프린트를 도입/배치하고 싶지 않은 약간 다른 상황에서 두 개의 다른 넷을 단락시키는 또 다른 기술/핵은 신호 하네스를 사용하는 것인데, 이는 예를 들어 데이지 체인으로 반복되는 여러 다중 채널 블록에서 넷을 연결할 때 특히 유용하게 사용할 수 있습니다.

디버그 목적으로 네트 연결을 자주 끊어야 하는 경우에는 명시적으로 제로 옴 저항 컴포넌트를 채우는 것이 더 편리할 수 있습니다.

AI로 번역됨

AI로 번역됨