PDN Analyzer のサンプルガイド

PDN Analyzer のアプリケーションは、容易に使用でき、PI-DC シミュレーションのネット/デバイスパラメータを設定して、シミュレーションを実行します。そして、結果を確認します。シミュレーションは、いつでも再実行できます(電源経路の信頼性を改善するために PCB を変更して、結果をテストできます)。

PDN Analyzer で操作するためのこのガイドでは、Altium NEXUS のサンプルプロジェクト Spirit Level を使用します。このサンプルは、C:\Users\Public\Documents\Altium\ADxx\Examples\SpiritLevel-SL1 フォルダに保存されています(ADxx は、インストールした Altium NEXUS のバージョンを表します)。このガイドでは、PDN Analyzer が Altium NEXUS にインストールされていてライセンス認証済みであり、PI-DC (DC Power Integrity) の基本的な原理を理解していると仮定して説明します。

PDN Analyzer の拡張機能のインストール/ライセンス認証や、PI-DC シミュレーションの基礎に関する情報については、PDN Analyzer ページ をご覧ください。

PDN Analyzer 拡張機能のインターフェースは、Altium NEXUS のパネルとして表示されます(Altium NEXUS に結合したり、ワークスペース上に表示できます)。PDN Analyzer パネルを表示するには、回路図、または PCB ドキュメントを開き(この例では、Spirit Level プロジェクトから)、Tools メニューからアプリケーション (Tools » PDN Analyzer) を選択します。

パネル内では、source/load のオブジェクトと供給/リターンパスが、解析回路と同じように表示されます(オブジェクトのブロックにその情報が表示され、データを入力できます)。上図のように全てのオブジェクトが表示されない場合、パネルのサイズを調整する必要があるかもしれません。

パネルの注意点:

- 背景がダークグレーの電源、GND ネットオブジェクトは、編集できます。

- 背景が白の電源、GND ネットオブジェクトは、編集できません(編集できるようにするには、他のオブジェクトブロックを編集/供給する必要があります)。

- 背景がライトブルーの Source、または Load オブジェクトブロックは、編集できます、または編集しました。

- 背景がライトグレーの Source、または Load オブジェクトブロックは、編集できません(編集できるようにするには、他のオブジェクトブロックを編集/供給する必要があります)。

- Source、または Load オブジェクトにある

ボタンは、そのオブジェクトのパラメータをクリアします。

ボタンは、そのオブジェクトのパラメータをクリアします。 -

ボタンは、現在の PI-DC 設定を

ボタンは、現在の PI-DC 設定を *.pidc_configファイルとしてプロジェクトディレクトリに保存(または、再保存)できます。 -

ボタンは、以前に保存したPI-DC 設定をシミュレーション設定として読み込みできます。

ボタンは、以前に保存したPI-DC 設定をシミュレーション設定として読み込みできます。 -

ボタンは、現在アクティブな PI-DC 設定を

ボタンは、現在アクティブな PI-DC 設定を *.pidc_configファイルとしてプロジェクトディレクトリに保存できます。 -

ボタンは、パネルの現在の設定をクリアします。

ボタンは、パネルの現在の設定をクリアします。 -

ボタンは、電源と GND ネット間に Load オブジェクトを追加します。

ボタンは、電源と GND ネット間に Load オブジェクトを追加します。 - Metal Conductivity リンクは、Metal Conductivity dialog が表示されます(現在のネットの伝導率が表示され、基準となる金属の導電率や温度補償値を変更できます)。

-

ボタン(パネルの左下)は、PI-DC シミュレーションプロセスを開始します(必要なパラメータを設定したら有効となります)。

ボタン(パネルの左下)は、PI-DC シミュレーションプロセスを開始します(必要なパラメータを設定したら有効となります)。 - パネルには、Results モードもあります(PI-DC シミュレーションが成功した時、有効になります)。これは、パネルの下部にある PDN Analyzer Result タブから開きます。

以降(3 つの例)で、PDN Analyzer を使用する方法や、複数の負荷や電源ネットワークを対応する方法を説明します。これらの例を実行して、Altium NEXUS 内で PI-DC シミュレーションを設定、保存、実行、解析する方法を把握できます。

例 1

この例では、VCCINT (1.8V) と負荷である U1 のデバイス間の電源経路に関して、PI シミュレーションの設定を行います。そこで、VCCINT と GND ネットの銅箔に関する電圧降下、電流密度を表示、評価できます。

例 1 電源回路 – Spririt Level プロジェクトの SL_Power.SchDoc をご覧ください。

ステップ 1: Spirit Level プロジェクトの回路図、または PCB ドキュメントを開き、Tools メニューからPDN Analyzer の拡張機能を起動します。PDN Analyzer パネルが開きます。必要な場合、現在の設定を Reset し (  )、以前に使用した設定をクリアします。

)、以前に使用した設定をクリアします。

ステップ 2: パネルの <Source Power Net> オブジェクトボックスをクリックし、ポップアップダイアログから電源伝送ネットを選択します。ここでは、VCCINT を選択します。

デフォルトで、ダイアログのフィルタオプション(上部)は、電源ネットのみ表示するよう設定されています。これらは、以下のように設定されています:

- 全ての銅箔 (プレーンやポリゴンに接続された銅箔だけでなく)。

- 3 つ、またはそれ以上、接続されているネットのみ。

- ネット名に V のプリフィックスがあるネットのみ。

全てのフィルタオプションをクリアにすると、PCB デザインの全てのネットがダイアログにリスト表示されます。

Source Power Net で VCCINT を選択して OK をクリックした後、以下のようになります:

- <Source Power Net> オブジェクトには、選択したネットが表示されます。

- <Loads Power Net> は、白からグレーに変わります。これは、編集できることを示します。

- 電源オブジェクトは、ライトブルーに変わります。これは、編集できることを示します。

- シミュレーションボタン (

) のメッセージが変わります。

) のメッセージが変わります。

ステップ 3: <Ground Net> (パネル下部のオブジェクトボックス) で GND が選択されていることを確認します。このように設定されていない場合、上記の Source Power Net と同様の方法で選択できます。このダイアログのフィルタは、3 つ、またはそれ以上の接続があり、プレーンやポリゴンに接続されているネットのみ表示されるよう、設定されています。

ステップ 4: Source オブジェクト(<RefDes.Pin> として表示されています)を選択し、電源、パラメータを指定します(ここでは、U4 の1.8V の電圧レギュレータ)。電源デバイスとピン(任意)は、Source ダイアログで入力します。

ダイアログの PWR Component Pins ドロップダウンメニューを使用して、電源を選択します(ここでは、U4)。このデザインで、U4 は、直接、GND に接続されているピンがありません。そのため、GND Component ドロップダウンメニューから GND コンポーネントとして J1 を選択します(電源入力ソケット J1 の 2 番ピンと 3 番ピンは、GND ネットに接続されています)。

電源デバイスの適切な電圧レベルと電流特性を指定します。1.8V の電源供給性能を低下させるために 5%(または、0.1V)下げた1.7V の電圧と、その部品の最大電流として 5A を選択します。

ステップ 5: <Loads Power Net> オブジェクトボックスを選択します。Source Power Net(上記)と同様のダイアログが表示されます。デフォルトで、source power net (VCCINT) と同じネットが指定されます。そのため、すぐ OK ボタンで完了できます。

今、Load と Source power nets は同じです。そのため、パネルの Power Net ボックスは、VCCINT としてつながった状態になります。  ボタンのメッセージも変わります。

ボタンのメッセージも変わります。

ステップ 6: 最後に、Load オブジェクトボックス(<RefDes.Pin> として表示されています)をクリックし、Load Component、GND Component として U1 を指定します。そして、その load パラメータ(負荷電流と最小供給電圧)を入力します。この例では、U1 の全てのピンが同じパラメータであると仮定します。いくつかのピンが異なるパラメータの場合、同じパラメータのピンのみ選択され、パラメータが割り当てられます。それから、他のピンに別の U1 の負荷が追加され、適切なパラメータが割り当てられます。

最小供給電圧 1.6V (10%の電圧降下を想定; 1.8V – 10% = 1.6V)と負荷電流 0.5A を指定します。

ステップ 7: シミュレーションの設定が完了しました。パネルの全てのボックスに有効なパラメータデータが含まれています(入力したパラメータが正しいか、各オブジェクトボックスで確認できます)。  ボタン(今、青色になっています)のメッセージは、シミュレーションを実行できる表示になります。

ボタン(今、青色になっています)のメッセージは、シミュレーションを実行できる表示になります。

ステップ 8:  ボタンをクリックし、PI-DC シミュレーションを開始します。

ボタンをクリックし、PI-DC シミュレーションを開始します。

シミュレーションの進捗状況が、Messages パネルに表示されます(プロセスを完了できない場合、失敗した原因も表示されます)。シミュレーションが完了したら、  ボタンの右に '

ボタンの右に 'Simulation run successfully' と表示されます。

パネルの Source/Load オブジェクトには、source と load に関する電流と電圧結果が表示されることに注意してください。

source/load オブジェクトに、緑色 '成功' のチェックマークが表示されます。入力した(シミュレーションを設定する時)制限を超えていないため、違反はありません(最大Source 電流は、5A を超えていません (0.5A) 。そして、Load 電圧は、最小 1.6V 以上 (1.69V) となっています)。制限を超えた場合、失敗したことを表す赤色のアイコン: ![]() で表示されます。

で表示されます。

ステップ 9: シミュレーションの結果は、Altium NEXUS の PCB エディタでグラフィカルに表示されます。電圧(降下)の結果を見るには、パネルの PDN Analyzer Result タブを選択します。そして、Display Filter の項目内の Voltage オプションを有効にします。Net 欄で VCCINT を、Layer 欄で Top と Bottom Layer を指定して、電源ネットの経路を表示します。

PDN Analyzer Results パネルでの作業に関する詳細については、Result panel features(以下)をご覧ください。

analyzer 結果は、Altium NEXUS の PCB エディタに表示されます。表示は、PDN Analyzer Result パネルの  と

と  ボタンで 2D、または 3D フォーマットに切り換えできます。これらのボタンは、PCB エディタの Altium 2D PDN Analyzer や Altium 3D PDN Analyzer からの表示(下図のように)と同じです。一般的に、3D では、レイヤやビアが表示されますが、2D では、より簡易的(そのため、より見やすい)に表示されます。

ボタンで 2D、または 3D フォーマットに切り換えできます。これらのボタンは、PCB エディタの Altium 2D PDN Analyzer や Altium 3D PDN Analyzer からの表示(下図のように)と同じです。一般的に、3D では、レイヤやビアが表示されますが、2D では、より簡易的(そのため、より見やすい)に表示されます。

3D 表示オプションを選択すると、シミュレーション結果は、以下のように表示されます。

選択したネットの経路に関する電圧降下は(この例では、VCCINT)、カラーグラデーションで表示されます(画面下部に、電圧の段階が表示されます)。その段階は、デフォルトで、シミュレーションで実行された電圧レベルの範囲に自動で設定されます(パネルの Results ウィンドウの Scale Option をご覧ください)。

この例では、以下のように表示されることに注意してください:

- 段階に表示された最大電圧は、1.7V (

1.6995) です(source (U4) で表示されます)。 - U4 とデカップリングコンデンサ C3 間の重要な DC 電圧降下はありません(理想的なコンデンサを介した電流の流れではありません)。

- 最小電圧は、1.69V (

1.6871) です(load (U1) で表示されます)。 - 0.5A の負荷と仮定した時、VCCINT の電源の銅箔には、非常に小さい電圧降下(約12 mV)があります。

3D モードで表示します。U4 と U1 間の配線上の 3 つのビア(ビアのトップとボトム間で色が異なる)で、電圧降下があるのを確認できます。

ステップ 10: 電圧ネット (VCCINT) の電流密度の結果を表示します。パネルのResults ウィンドウで、Current Density オプションを選択します。そして、VCCINT ネット、Top と Bottom layer を指定します。

U4 と U1 間のトラックには、最も高い電流密度があることに注意してください。そして、デザインを改善する必要があるか確認できます。電流密度の段階の範囲は、シミュレーション結果(デフォルトのAuto Scale オプション)から自動で決定され、デフォルトで A/m2 (amps per square meter) で表示されます。

ステップ 11: GND ネットの電圧結果を表示します。パネルの Results ウィンドウで、Voltage オプションを選択します。そして、GND ネット、Top Layer を指定します。GND の大きい銅箔では、ほとんど電圧降下はありません(最大電圧は、わずか 1.37mV です)。

しかし、results モードを Current Density、GND ネット (Top layer) に切り換えた場合、問題を確認できます。GND の銅箔で、青色で示された島(電流が流れていません)があります。もちろん、これは、VCCINT の DC 電流の流れを示すだけですが、これらの GND の銅箔が使用されていないことを判断する前に、他の DC 電圧をチェックする必要があります。

削除する前に、GND の銅箔が、AC 電流を戻すために使用されていないことを(例えば、リターンパスに対する影響を見るために、コンデンサを 1K オーム抵抗に交換して)確認することも重要です。重要な場所の小さな接続(U1 の左下)でも、大きな GND の島に関する問題を減らすことができます。

実際に、これらの島は、AC、過渡電圧特性に関する問題を起こす場合があり、これを回避する必要があります。電源伝送の銅箔の接続点は、主要な部分で理想的である必要があります。

この画面でその他に気づく点は、左から右への電流の流れが(GND のリターンパスとして)、U1 の上下で細長く狭い領域に制限されていることです。このレイヤの全体の電流の流れが、重要である場合、狭い銅箔によって、GND の電圧降下が 1.37mV 以上になる可能性があります。

PDN Analyzer の電流密度を表示する機能を使用して、デザインのレイアウトを明確に解析できます。

例 2

この例では、VCCO (3.3V) と複数の負荷デバイス(抵抗負荷や U1 の別のピンの負荷を含む)間の電源経路に関する PI シミュレーションを設定します。Altium NEXUS をインストールした時に保存されている Spirit Level のサンプルファイルを使用します(例 1 で使用しました)。

例 2 power source 回路 – Spirit Level プロジェクト内の SL_Power.SchDoc をご覧ください。

PDN Analyzer パネルで、  (または、

(または、  ) ボタンを使用して、現在の設定を保存します。それから、

) ボタンを使用して、現在の設定を保存します。それから、  ボタンで設定をクリアします。

ボタンで設定をクリアします。

以下のように設定します。必要に応じて、パネルの ![]() ボタンを使用して、Load を追加します:

ボタンを使用して、Load を追加します:

- Power Net (Source と Loads):

VCCO - Ground Net:

GND - Source:

U3.2(Power Component),J1.2,3(GND Component)3.15V(3.3V – 5%) Source 電圧、5% の負荷軽減を仮定- source と全ての source ピンで最大

5A

- Loads:

R20.2(power),U6.3(ground): LED270Ω負荷抵抗3V最小電圧 (3.3V – 10%)

U5.18(power),U5.11(ground): JTAG VCCINT0.01A3V最小電圧 (3.3V – 10%)

U5.19(power),U5.11(ground): JTAG VCCO0.04A3V最小電圧 (3.3V – 10%)

U5.20(power),U5.11(ground): JTAG VCC0.05A3V最小電圧 (3.3V – 10%)

U1.*(power, 全てのピンを使用),U1.*(ground, 全てのピンを使用): FPGA 3.3V1.875A3V最小電圧 (3.3V – 10%)

R11.1(power),U2.3(ground): U2 電流0.005A3V最小電圧 (3.3V – 10%)

R16.1(power),S3.3,4(ground): Y1 電流0.012A3V最小電圧 (3.3V – 10%)

この例では、以下の内容を説明します:

- 複数の負荷を容易に追加してシミュレーションを行えます。

- シミュレーショントポロジーやデータをグラフィカルにパネルに表示します(パラメータを正確に入力できます)。

- 異なる電流値を、負荷デバイス(この例では、U5)の特定のピンへ割り当てる機能。

例 3

この例では、5V の電源 (PWR_IN) が、入力から介在するデバイス(や、U3 や U4 を含む複数の負荷デバイス)へ流れるまでの電源経路に関する PI シミュレーションを行います。この例でも、Altium NEXUS をインストールした時に保存されている Spirit Level のサンプルファイルを使用します。そして、例 1 と同様の方法で実行します。

例 3 電源回路 – Spririt Level プロジェクトの SL_Power.SchDoc をご覧ください。

ここでは、5V の電源(J1 のコネクタの PWR_IN のネットから供給された)について、source power net として PWR_IN を、load power net として 5V を選択して、解析できます(ダイアログのリストで PWR_IN ネットを表示するには、ネットフィルタを解除する必要があります)。PDN Analyzer は、中間ネット NetD1_2 (ツェナーダイオードD1 の上のピン) を含む、2 つのネット間の DC 経路を自動で構築します。

5V の電源経路は、J1 の入力 (PWR_IN) と 5V の電源間で正しく構築されています(Polyswitch (F1; 1 番ピンと 2 番ピン) と Power Switch (S1: 3 番ピンと 2 番ピン/1番ピン) の接続を含む)。

しかし、スイッチは、NetD1_2 と 5V 間で、Multi Passives (S1.3-S1.2, S1.3-S1.1) として表示されています。現在の経路に合わせるには、S1.3 と S1.2 間のみにします。オブジェクトボックス('Multi Passives' と表示されている)をクリックして、S1 のピン設定を変更します(S1 の 3 番ピンから 1 番ピン間のチェックを外します)。

変更を完了したら、S1 のオブジェクトは、'Multi Passives' ではなく、1 つのピン間設定 (S1.3 から S1.2 間) として表示されます。passive コンポーネント(ここでは、F1 と S1)で表現された抵抗は、デフォルトで 0.001Ω ですが、パラメータダイアログで変更できます。

PWR_IN から 5V までのサンプルシミュレーションでは、source と loads で別のネットを使用する方法を説明します(この経路では、passive コンポーネントを介します)。これらのコンポーネントは、抵抗のみで形成できます。しかし、アクティブコンポーネントを介す経路では、個々に形成した入出力経路が必要です。source と load net の経路が自動で反映された場合、その経路は、必要に応じて、変更する必要があります(以下をご覧ください)。

指定した Source と Load ネット間に多くの DC 経路が存在する状況で、PDN Analyzer は、望ましくない Source から Load までの経路(主要でない、想定していた大電流が流れる経路)を選択する場合があります。

Analyzer が自動で選択する経路は、回路のネットトポロジー(分類されたネットやその他の要素)に依存します。そのプロセスでは、例えば、アクティブデバイスのピンは識別されません。または、最も大きい電流経路は予測されません。

source から load までの経路を正しいネットに設定するために、PDN Analyzerのインターフェースでは、個々のネットをその経路から削除できます。そのため、強制的に別のネット経路を選択できます。望ましくないネットは、インターフェースのグラフィカル表示画面から削除されます。

例えば、Source net (VCC) と Load net (VSS) 間で、3 つ、または 4 つの DC 経路がある簡単な電源回路で考えてみます。

PDN Analyzer で、Source Power Net を VCC、Load net を VSS として指定してシミュレーションを設定した時、それらのネット間の 3 つの経路のいずれかが選択されます。1 つは、直接、U1 のレギュレータを経由する望ましい経路です(以下の経路 C として指定)。

しかし、この例では、自動で経路 A が選択されました(D2 と Q1 を経由する経路)。PDN analyzer のユーザインターフェースでは、source から load までの経路がグラフィカルに表示されます。

PDN Anayzer は、source から load までの経路として、自動で経路 A を選択しました(Analyzer の GUI で表示)。

この場合のネットは以下です:

NetD2_1– R6 と D2 の接合点NetD2_2– D2 と Q1 の接合点NetQ1_2– Q1 と R7の接合点

現在の経路を目的の経路 (C) へ変更するため、望ましくないネットを削除します(たまたま、目的の経路のネットは含まれていません)。

これにより、その経路は除外され、他の経路を選択できます。この例では、経路 By(上図をご覧ください)を選択しました(目的のネット経路でない)。

source から load までの経路で、あるネットを削除すると、別の経路を選択できます。この例では、経路 By(望まれていないネット; NetC3_1 を含む)に変更しました。

この経路では、以下のネットが含まれています:

NetC2_1–R1とC2の接合点 (これは、経路 C にも含まれ、望ましいネットです)NetC3_1–C3とU1の GND ピンの接合点

この時点で、経路 C にするために NetC3_1 のネットを除外する必要があるのは明確です。これを削除すると、source から load までの経路が、目的の経路になるよう望ましいネット; NetC2_1 のみ含めることができます。

そのため、その経路は、経路 C のように表示されます(R1、NetC2_1、U1 のみが含まれます)。

間違ったネットを削除して、目的のシミュレーション経路 C に定義。

金属の導電率

PDN Analyzer パネルの Metal Conductivity リンクをクリックすると、Metal Conductivity ダイアログが表示されます。そこに、デザインで使用した金属の導電率の値(抵抗の逆数; 1/R)に関する詳細や設定が表示されます。

シミュレーションで使用するデフォルトの金属は、純銅 です(一般的に、25°C で 5.88e7S/m の導電率、0.4%/°C の導電率温度係数であると仮定されています)。この正温度係数は、ダイアログの Temp. Compensation 設定で、例えば、25°C から 125°C (100°C delta) まで上げることで、シミュレーションでの導電率が 3.53e7S/m まで(40%)下がることを意味します。

PCB Copper 設定では、PCB electro-deposited (ED) 銅の一般的なものとして、産業文献でレポートされた導電率が反映されます(25°C で 4.7e7S/m の導電率、0.4%/°C の温度係数

基本の伝導率(または、抵抗率)、温度係数、温度は、ダイアログで変更して、デザインの金属属性として反映できます。Sim Conductivity は、全てのパラメータを考慮した、最終的な導電率の値を示します。

ビア内側の厚さ

シミュレーション解析で、ビア内側の銅箔厚を指定するには、PDN Analyzer パネルの Via Wall Thickness リンクを選択します。

ビア内側の材料の厚さは、デフォルトで 18µm (0.7mm) で、シミュレーションを行うための最小の厚さは 1µm です(Wall Thickness で、それ以下の値を設定した場合、1µm の設定が使用されます)。その設定は、ビア内側の銅箔が薄い(スルーホール)場合、抵抗になるため、電源ネットワーク DC の損失に影響を及ぼします。しかし、十分なサイズ/厚さであれば、ビアは、デザインの DC 性能に影響を与えず、電源配線と同じ電流密度になります。そして、その接続点間で重要な電圧損失はありません。ビアを介した DC 解析の例は、上図で説明しています。

ビアサイズと、内側の銅箔厚によって、シミュレーションでどれぐらいの導電性か(抵抗/導電率)を効果的に定義できます。シミュレーションでは、ビアの直径は、finished hole size と、内側の銅箔厚を足した部分と仮定します。そのため、: Finished Hole Diameter + (2 x Wall_Thickness) = Drill Diameter です。

Result panel の機能

PDN Analyzer Result パネルには、Altium NEXUS の PCB エディタで、シミュレーション結果をどのように表現するか(電圧/電流、ネットやレイヤ)など、シミュレーション結果を管理するための設定があります。

パネルの Display filter 欄では、シミュレーション結果を表示する領域を手動で定義できます。

- 特定の電圧、または電流密度の範囲を設定するには、Scale option の項目で Manual モードを選択します。最小、最大値を入力して

ボタンをクリックすると、PCB エディタの段階表示(カラーグラデーション)が変わります。

ボタンをクリックすると、PCB エディタの段階表示(カラーグラデーション)が変わります。 - 電流密度の結果は、デフォルトで

A/m2(amps per square meter) の単位で表示されます。Current density ドロップダウンメニューから別の単位を選択できます。

パネルの Results 欄には、シミュレーションデータで作業するためのボタンがあります。これらは以下です:

-

: このボタンは、PCB エディタでシミュレーションデータの情報を表示します。選択した時、エディタのカーソルは、プローブモードに変わります(3D の場合、紫のカーソル、2D の場合、十字)。シミュレーションデータは、Altium NEXUS の Heads Up Display に表示されます。特定の場所の電圧、または電流密度の情報を表示するには、基板内をクリックします。

: このボタンは、PCB エディタでシミュレーションデータの情報を表示します。選択した時、エディタのカーソルは、プローブモードに変わります(3D の場合、紫のカーソル、2D の場合、十字)。シミュレーションデータは、Altium NEXUS の Heads Up Display に表示されます。特定の場所の電圧、または電流密度の情報を表示するには、基板内をクリックします。

-

: PCB エディタで表示されているシミュレーション結果を削除するには、このボタンをクリックします – 元に戻すには、

: PCB エディタで表示されているシミュレーション結果を削除するには、このボタンをクリックします – 元に戻すには、  をクリックします。

をクリックします。 -

: 最後に使用した画面(例えば、Altium Standard 2D)に戻すには、このボタンをクリックします。PI-DC シミュレーション結果は、PCB エディタで重なった状態で表示され、

: 最後に使用した画面(例えば、Altium Standard 2D)に戻すには、このボタンをクリックします。PI-DC シミュレーション結果は、PCB エディタで重なった状態で表示され、  ボタンで削除できます。

ボタンで削除できます。  と

と  : PCB エディタでの表示タイプを選択します。PDN Analyzer の結果は、2D、または 3D で表示できます。これは、PCBエディタで直接、Altium 2D PDN Analyzer、または Altium 3D PDN Analyzer 表示オプションを選択するのと同じです。

: PCB エディタでの表示タイプを選択します。PDN Analyzer の結果は、2D、または 3D で表示できます。これは、PCBエディタで直接、Altium 2D PDN Analyzer、または Altium 3D PDN Analyzer 表示オプションを選択するのと同じです。-

: PDN Analyzer の出力ディレクトリが表示されます。ここには、現在のシミュレーションデータが含まれています(

: PDN Analyzer の出力ディレクトリが表示されます。ここには、現在のシミュレーションデータが含まれています(*.jsonや*.csvの結果ファイルが保存されている\Resultsサブディレクトリを含む)。 -

: JSON フォーマット (属性値ペア) のデータファイルを読み込みます。例えば、analyzer の

: JSON フォーマット (属性値ペア) のデータファイルを読み込みます。例えば、analyzer の fields.json結果ファイル(\Resultsサブディレクトリにある)には、シミュレーションを行ったレイヤやネットに関する電圧/電流データの結果が含まれています。このようなファイルを読み込んで、現在の基板レイアウトの銅箔に関するシミュレーションデータを定義できます。 -

: 一般的な(セミコロンで区切った)CSV データファイルを読み込みます。

: 一般的な(セミコロンで区切った)CSV データファイルを読み込みます。\Resultsサブディレクトリ内にあるvolt_curr.csvファイルには、シミュレーションに関するパラメータや電圧降下の情報が含まれています。

電流制限

PDN Analyzer の拡張機能に関して、できるだけ効率的にツールを使用できるように機能やインターフェースを追加していく予定です。現在、実行できる解析に制限がありますが、改善していく予定です。

現在の機能制限は、以下です:

- 統合された回路図/PCB 編集。 ネット名とコンポーネントは、直接、回路図、または PCB 画面から入力できません。

- 複数の source。 現在、1 つの正電圧 source のみ、対応しています。複数の source や/または負電圧 source(または、負電流負荷)は対応していません。

- Source から load までの GND 経路。 1 つの GND ネット経路のみ、source と load 間で利用できます(電源ネットの複数のネット経路を定義する機能と異なります)。

- コンポーネント名のスペース。 現在、デジグネータにスペースがあるコンポーネントが PCB デザインに含まれている場合、シミュレーションは失敗します。これは、次のバージョンで修正する予定です。

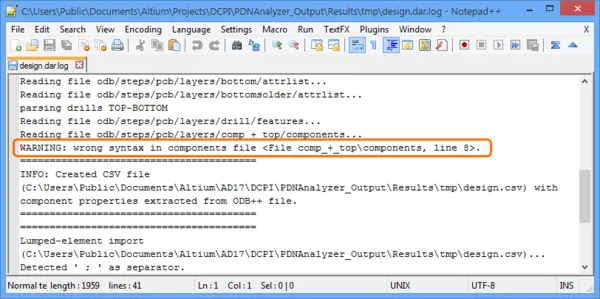

\PDNAnalyzer_Output\Results\tmp ディレクトリにあるdesign.dar.log ファイルを確認します。これには、シミュレーションエンジンが生成した components ファイルの行数を示す構文の警告、またはエラーメッセージが表示されます。

components\PDNAnalyzer_Output ディレクトリにある tar アーカイブファイル [project_name].tgz を開く/抽出する必要があります。これは、互換性のあるアーカイブ管理ツール(例えば、7-Zip、または 類似のツール)で実行できます。\odb\steps\pcb\layers\comp_+_top (または、構文エラーによる comp_+_bot) から components ファイルを確認するには、そのツールを使用します。その問題を引き起こしているコンポーネント名を見つけるには、design.dar.log ファイル内の警告/エラーで示された行数を参照します。この例では、デザインの Voltage Regulator コンポーネント (8 行目) のデジグネータに、スペースが含まれていることを示します: U 1。このエラーは、PCB デザインで修正して解決できます。