Working with the Slope - Falling Edge Design Rule on a PCB in Altium NEXUS

Created: 三月 23, 2017 | Updated: 九月 26, 2019

| Applies to versions: 1.0, 1.1, 2.0, 2.1, 3.0, 3.1 and 3.2

您正在阅读的是 3.1. 版本。关于最新版本,请前往 Working with the Slope - Falling Edge Design Rule on a PCB in Altium NEXUS 阅读 4 版本

Rule category: Signal Integrity

Rule classification: Unary

Summary

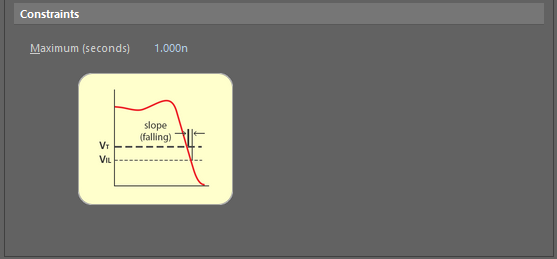

This rule specifies the maximum allowable slope time on the falling edge of the signal. Falling edge slope is the time it takes for a signal to fall from the threshold voltage (VT), to a valid low (VIL). Constraints.

Constraints

Default constraints for the Slope - Falling Edge rule.

Default constraints for the Slope - Falling Edge rule.

- Maximum (seconds) - the value for the maximum permissible falling edge slope time.

How Duplicate Rule Contentions are Resolved

All rules are resolved by the priority setting. The system goes through the rules from highest to lowest priority and picks the first one whose scope expression matches the object(s) being checked.

Rule Application

Batch DRC and during Signal Integrity analysis.