Проверка правил проектирования

Проверка правил проектирования (Design Rule Checking, DRC) – это мощная автоматизированная функциональная возможность, которая проверяет логическую и физическую целостность проекта. Проверки выполняются для некоторых или всех включенных правил проектирования (Design Rules), и она может выполняться онлайн, т.е. в режиме реального времени при проектировании, либо как пакетный процесс, с отображением результатов в панели Messages системы и, опционально, в сформированном отчете.

Эту функциональность следует использовать для всех разведенных плат для подтверждения соблюдения правил минимального зазора и отсутствия прочих конструктивных нарушений. Особенно рекомендуется всегда выполнять проверку правил проектирования в пакетном режиме перед созданием финальных чертежей для фотошаблонов.

Настройка DRC

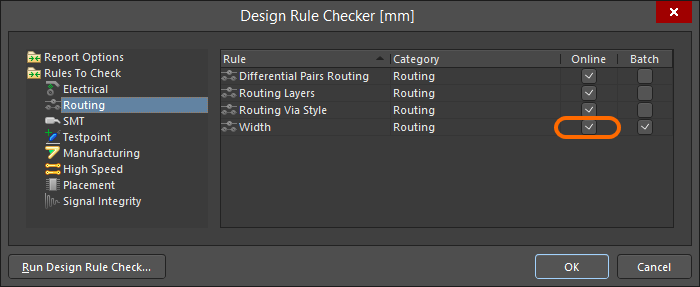

Настройка проверки правил проектирования выполняется в диалоговом окне Design Rule Checker, доступ к которому осуществляется с помощью команды Tools » Design Rule Check из документа платы.

Диалоговое окно Design Rule Checker, в котором показаны настройки по умолчанию, где некоторые онлайн-проверки DRC отключены для улучшения производительности редактора плат. Используйте соответствующие опции, чтобы включить тип правил проектирования в онлайн и/или пакетную проверку DRC.

Диалоговое окно Design Rule Checker, в котором показаны настройки по умолчанию, где некоторые онлайн-проверки DRC отключены для улучшения производительности редактора плат. Используйте соответствующие опции, чтобы включить тип правил проектирования в онлайн и/или пакетную проверку DRC.

В области дерева папок в левой части диалогового окна, в папке Rules To Check приводится список категорий правил проектирования, типы правил которых доступны для проверки. Щелкните ЛКМ по папке верхнего уровня, чтобы отобразить список всех доступных для проверки типов правил в правой части диалогового окна. Либо щелкните ЛКМ по определенной категории, чтобы отобразить список только тех типов правил, которые относятся к этой категории. Используйте диалоговое окно для включения/отключения онлайн (где это доступно) и/или пакетного режима проверки типов правил, которые нужно проверять.

Использование онлайн DRC

Онлайн-проверка правил проектирования работает в режиме реального времени в фоне, помечая и/или автоматически предотвращая нарушения правил проектирования. Это особенно полезно при интерактивной трассировке платы для мгновенной подсветки нарушений зазора, ширины и параллельных сегментов. Чтобы для правила работала онлайн DRC, должны быть соблюдены следующие условия:

-

Правило должно быть включено. Это осуществляется в диалоговом окне PCB Rules and Constraints Editor путем включения опции Enabled для правила или в панели PCB Rules and Violations путем включения опции On для правила.

Убедитесь, что правила проектирования, которые вы хотите отслеживать с помощью онлайн DRC, включены для использования в проекте.

Убедитесь, что правила проектирования, которые вы хотите отслеживать с помощью онлайн DRC, включены для использования в проекте. -

Тип правил должен быть включен для онлайн-проверки в диалоговом окне Design Rule Checker.

-

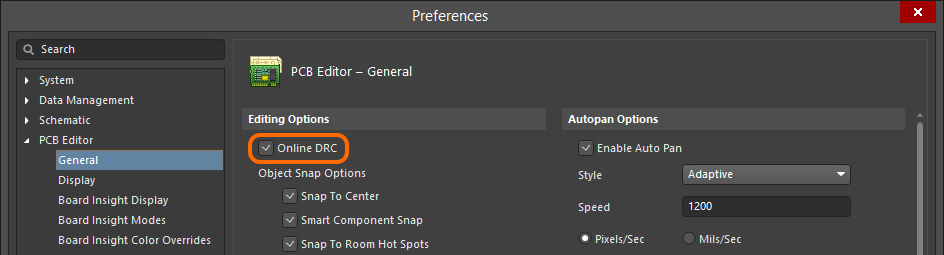

Функциональная возможность онлайн DRC должна быть включена. Для этого включите опцию Online DRC на странице PCB Editor - General диалогового окна Preferences.

Убедитесь, что функциональная возможность онлайн DRC включена.

Убедитесь, что функциональная возможность онлайн DRC включена.

Если для каких-либо объектов будет обнаружено нарушение применяемого правила проектирования, которое включено для онлайн-проверки, эти объекты будут подсвечены в главной проектной области в соответствии с заданными опциями отображения нарушений.

Использование пакетной DRC

В то время как онлайн DRC обнаруживает только новые нарушения, т.е. нарушения, появившиеся после включения этой функциональной возможности, пакетная DRC позволяет вручную запустить проверку в любой момент во время процесса конструирования платы. Опытные проектировщики понимают ценность онлайн DRC, но они также знают, что конструирование платы должно начинаться и заканчиваться пакетной DRC.

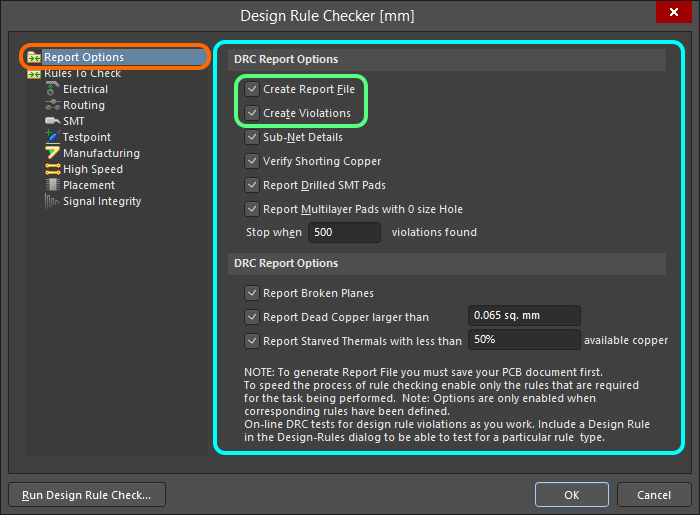

Включите нужные типы правил для пакетной проверки в диалоговом окне Design Rule Checker (см. раздел Настройка DRC выше). При запуске пакетной DRC доступны различные дополнительные опции, в том числе возможность формирования файла отчета. Чтобы получить доступ к этим опциям, щелкните ЛКМ по папке Report Options в дереве папок диалогового окна. Двумя ключевыми опциями (выделены на изображении ниже) являются:

- Create Report File – включите эту опцию, чтобы сформировать отчет о DRC.

- Create Violations – включите эту опцию, чтобы подсветить нарушения в проектной области в соответствии с заданными опциями отображения нарушений. Включение этой опции также необходимо, чтобы список нарушений был приведен в разделе Violations панели PCB Rules And Violations.

Доступ к опциям, применимых к запуску пакетной DRC и формированию отчета о DRC.

Доступ к опциям, применимых к запуску пакетной DRC и формированию отчета о DRC.

Запуск DRC в пакетном режиме осуществляется нажатием кнопки Run Design Rule Check в нижней левой части диалогового окна. По завершении проверки все нарушения будут приведены в виде сообщений в панели Messages. Если вы включили формирование отчета о DRC, он будет создан и автоматически открыт (если это было настроено) в качестве активного документа в главном проектном окне. В отчете будет приведен список всех правил, которые проверялись, в соответствии с настройками в диалоговом окне Design Rule Checker. Правила, которые не присутствуют в плате, не проверяются.

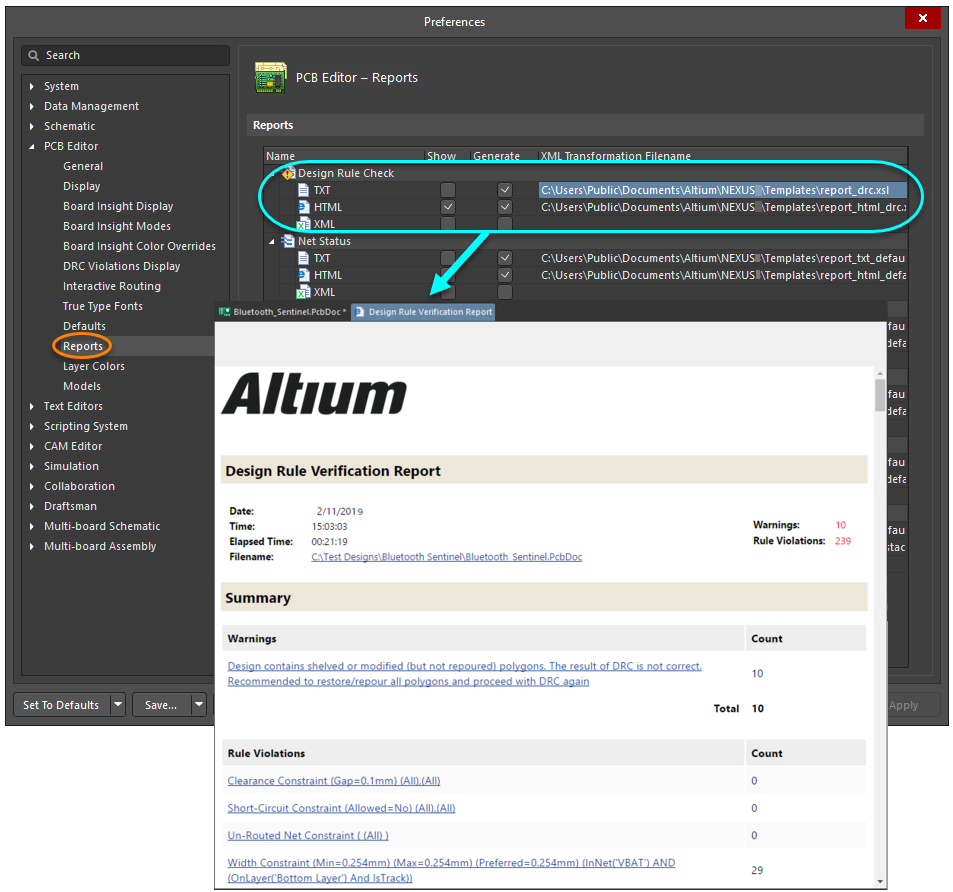

Отчеты о DRC

Если в диалоговом окне Design Rule Checker включена опция Create Report File, после выполнении пакетной DRC будет сформирован отчет о DRC. Опции, доступные на странице PCB Editor - Reports диалогового окна Preferences, позволяют указать формат отчета и то, будет ли отчет автоматически открыт после формирования.

Формирование отчета о DRC в рамках процесса пакетной DRC.

Поддерживаемые форматы:

- TXT – формирует файл

Design Rule Check - <НазваниеДокументаПлаты>.drc. - HTML – формирует файл

Design Rule Check - <НазваниеДокументаПлаты>.html. - XML – формирует файл

<НазваниеДокументаПлаты>.xml.

В отчете приводится список всех правил, которые были проверены в процессе пакетной проверки в соответствии с настройками в диалоговом окне Design Rule Checker. Будут приведены все найденные нарушения с подробной информацией, такой как слои, имена цепей, позиционные обозначения компонентов, номера контактных площадок, а также координаты объектов.

Опции отображения нарушений

Проверять конструкцию на соответствие заданным правилам проектирования – это одно, но что происходит при нарушении одного или нескольких из этих правил? При работе онлайн DRC в процессе проектирования или при запуске пакетной DRC вручную необходима некоторая визуальная индикация мест, где происходят нарушения этих правил. Редактор плат включает в себя эффективные опции отображения нарушений для ясного визуального обозначения этих нарушений.

Собственная графика нарушений

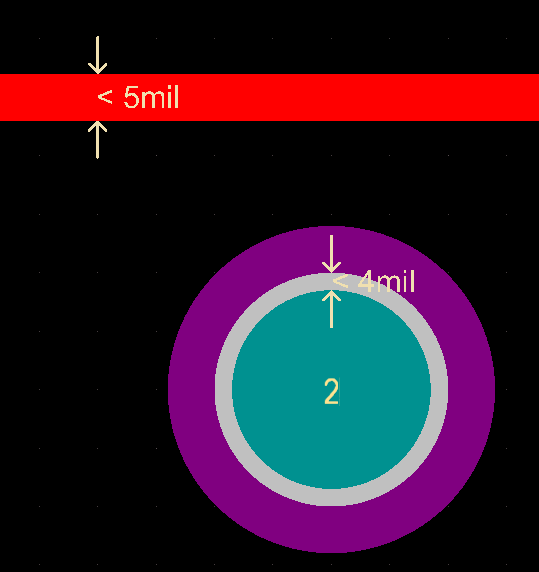

У большинства правил проектирования, которые доступны для онлайн и/или пакетной DRC, есть соответствующая графика нарушений, которая отображается в проектной области при нарушении определенного правила. Эта графика обеспечивает визуально более ясное представление DRC. При нарушении определенного правила соответствующая собственная графика нарушения будет изображена только на слое (или слоях, в зависимости от конкретного случая), к которым это нарушение относится.

В некоторых случаях, графика отображает не только место, где произошло нарушение, но и его причину, т.е. значение ограничения, которое определено для правила, и обозначение, что примитивы, вызывающие нарушения, выходят за рамки этого значения.

Пример, показывающий использование собственной графики для нарушений правил ширины и минимального пояска.

Пример, показывающий использование собственной графики для нарушений правил ширины и минимального пояска.

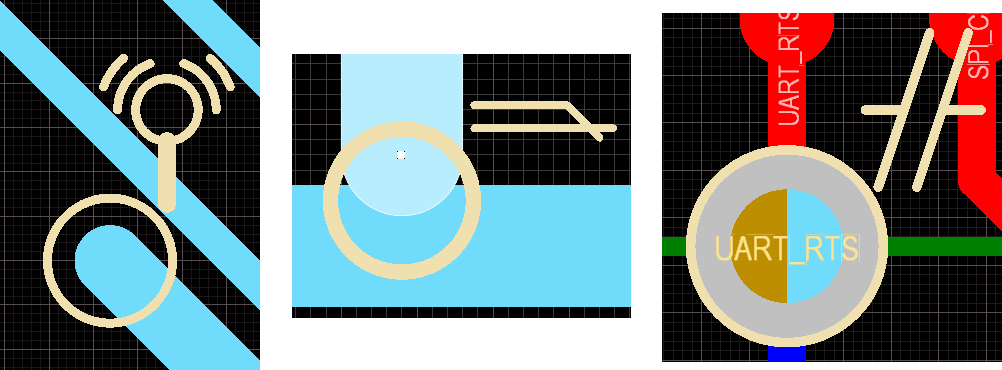

Для других нарушений, таких как нарушения правил антенны цепи, короткого замыкания, нерастрассированной цепи, определения комнаты, пары слоев и переходов под SMD, есть собственная графика, но для них не отображается определяемое значение ограничения.

Дополнительные примеры собственной графики нарушений. Слева направо: нарушение антенны цепи; нарушение короткого замыкания; нарушение нерастрассированной цепи.

Дополнительные примеры собственной графики нарушений. Слева направо: нарушение антенны цепи; нарушение короткого замыкания; нарушение нерастрассированной цепи.

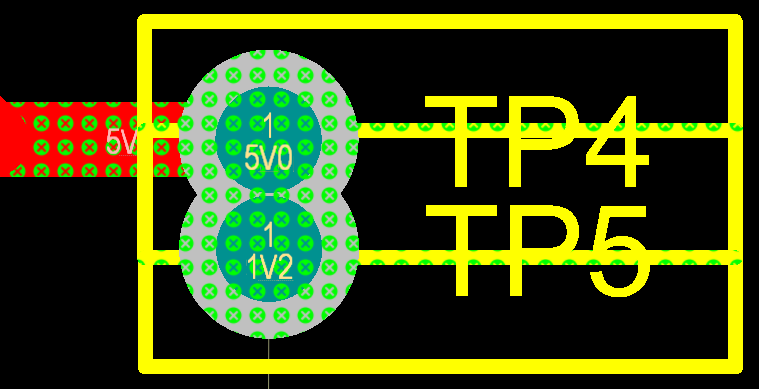

Оверлей нарушений

Помимо собственной графики нарушений, для настройки и использования доступен оверлей нарушений, который отображается поверх проектных примитивов. Вы можете выбрать один из доступных стилей рисунка, который будет отображаться на примитивах.

Используйте оверлей нарушений в качестве альтернативы собственной графике при отображении нарушений DRC.

Используйте оверлей нарушений в качестве альтернативы собственной графике при отображении нарушений DRC.

Комбинирование двух типов отображения нарушений может оказаться полезным с точки зрения "грубой" и "точной" индикации нарушений. При отдалении вида оверлей нарушения может указывать на наличие нарушения, а при приближении вида вы сможете увидеть подробную информацию, представленную соответствующей собственной графикой нарушения.

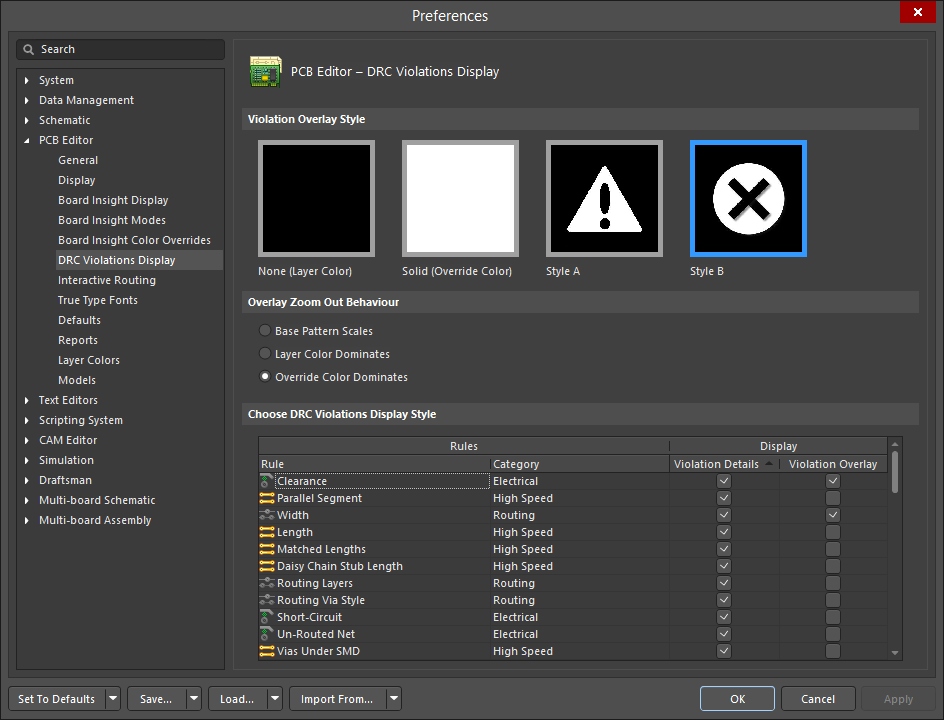

Настройка отображения нарушений

Управление отображением нарушений DRC, с помощью собственной графики нарушений и/или определенного оверлея нарушений, осуществляется на странице PCB Editor - DRC Violations Display диалогового окна Preferences.

Задайте настройки отображения нарушений DRC в проектной области, с помощью собственной графики нарушений и/или определенного оверлея нарушений, в настройках системы.

Доступные опции позволяют:

- Выбрать используемый стиль оверлея нарушения.

- Определить поведение отображения оверлея нарушения при отдалении вида.

- Выбрать используемый стиль нарушения для каждого типа правила. Включите опцию Violation Details, чтобы для отображения нарушений DRC правил этого типа использовалась собственная графика нарушений. Включите опцию Violation Overlay, чтобы отображать нарушения с использованием оверлея заданного стиля.

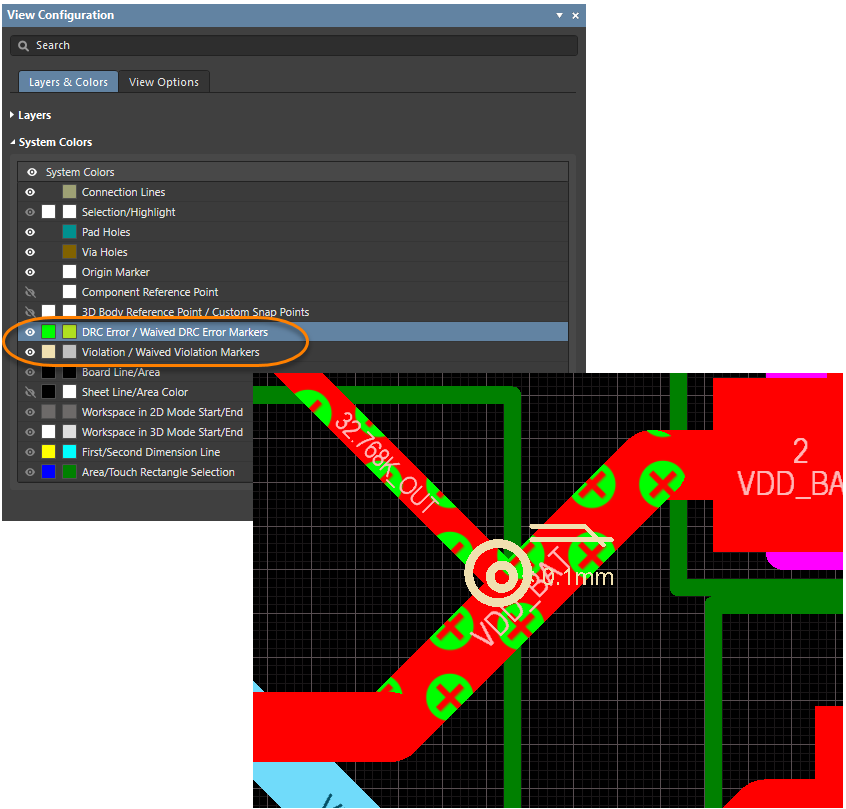

Определение цвета нарушений

Для обеспечения еще большей гибкости при отображении нарушений в проектной области, с двумя типами отображения нарушений (информация о нарушении, или собственная графика нарушений, и оверлей нарушения) связаны отдельные системные цвета, что позволяет различать эти типы отображения с помощью разных цветов. Назначение цвета осуществляется в разделе System Colors на вкладке Layers & Colors панели View Configuration:

- Violation Details – используйте системный цвет Violation Markers (для отклоненных нарушений, использующих этот стиль, используется системный цвет Waived Violation Markers).

- Violation Overlay – используйте системный цвет DRC Error Markers (для отклоненных нарушений, использующих этот стиль, используется системный цвет Waived DRC Error Markers).

Укажите различные цвета для двух типов отображения нарушений и включите/отключите их отображение нужным образом.

Укажите различные цвета для двух типов отображения нарушений и включите/отключите их отображение нужным образом.

Исследование и устранение конструктивных нарушений

При внимательной и поэтапной проверке правил в процессе проектирования, в результате финального запуска пакетной DRC для завершенной, полностью растрассированной платы может произойти только несколько нарушений, либо их может не быть совсем. Однако может быть отмечено и достаточно большое количество нарушений, и тогда задача сводится к устранению этих нарушений.

Отчеты о DRC, формируемые пакетной DRC, могут показаться довольно пугающими для начинающих конструкторов. Для управляемого процесса необходимо определить стратегию. Одна из стратегий – ограничить количество сообщаемых нарушений. При задании опций отчета в диалоговом окне Design Rule Checker укажите меньшее значение для Stop When Found. Другой стратегией является проведение DRC в несколько этапов. Если конструкция содержит большое количество нарушений, начните с включения правил по одному за раз. В дальнейшем вы выработаете предпочтительный подход к проверке различных правил проектирования.

Для устранения нарушения сначала необходимо определить его положение. Редактор плат предлагает различные методы для исследования нарушений, которые описаны в следующих разделах.

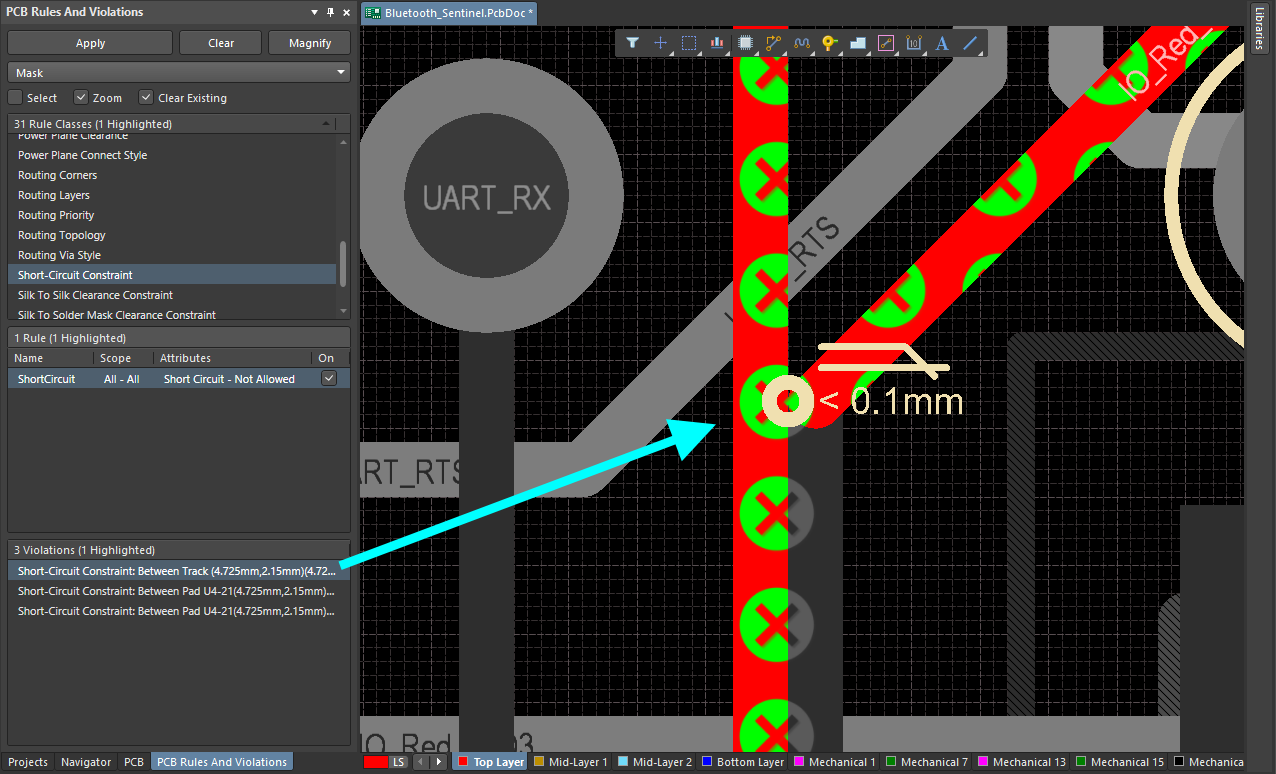

Из панели PCB Rules And Violations

При проведении онлайн или пакетной DRC все нарушения правил будут приведены в разделе Violations панели PCB Rules And Violations. Вы можете увидеть нарушения, связанные с определенным классом правил или с отдельным правилом в классе, либо все нарушения, выбрав класс [All Rules].

Щелкните ЛКМ по строке нарушения, чтобы применить фильтр, областью действия которого будут объекты с нарушениями. Итоговое представление в главном окне проектирования будет зависеть от включенных опций подсветки (Mask/Dim/Normal, Select, Zoom) в верхней части панели.

Исследование нарушений правил с помощью панели PCB Rules And Violations.

Исследование нарушений правил с помощью панели PCB Rules And Violations.

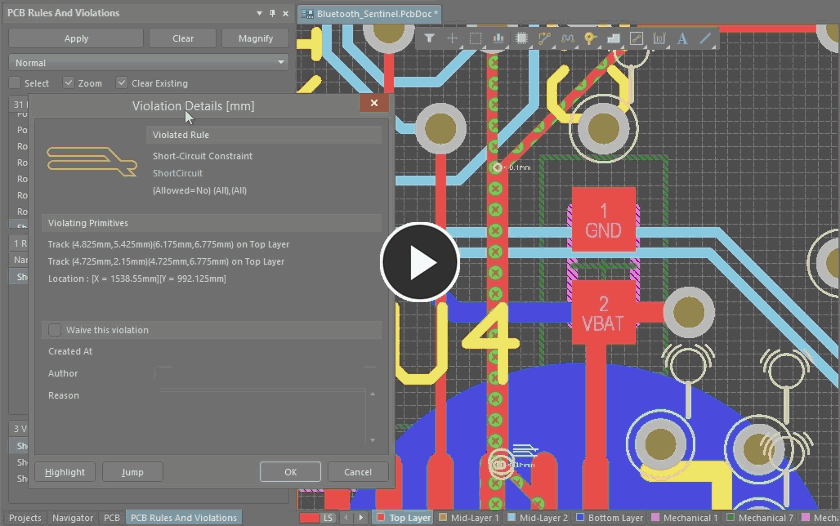

Дважды щелкните ЛКМ по строке нарушения (или щелкните ПКМ по ней и выберите Properties), чтобы открыть диалоговое окно Violation Details, где представлена информация о нарушенном правиле и ответственных за это примитивах. Из этого диалогового окна можно подсветить объекты с нарушением (они будут временно подсвечены в проектной области) или перейти к ним, т.е. приблизить и центрировать их.

С помощью диалогового окна Violation Details вы можете подсвечивать примитивы, которые вызывают нарушение правила проектирования, и переходить к ним.

С помощью диалогового окна Violation Details вы можете подсвечивать примитивы, которые вызывают нарушение правила проектирования, и переходить к ним.

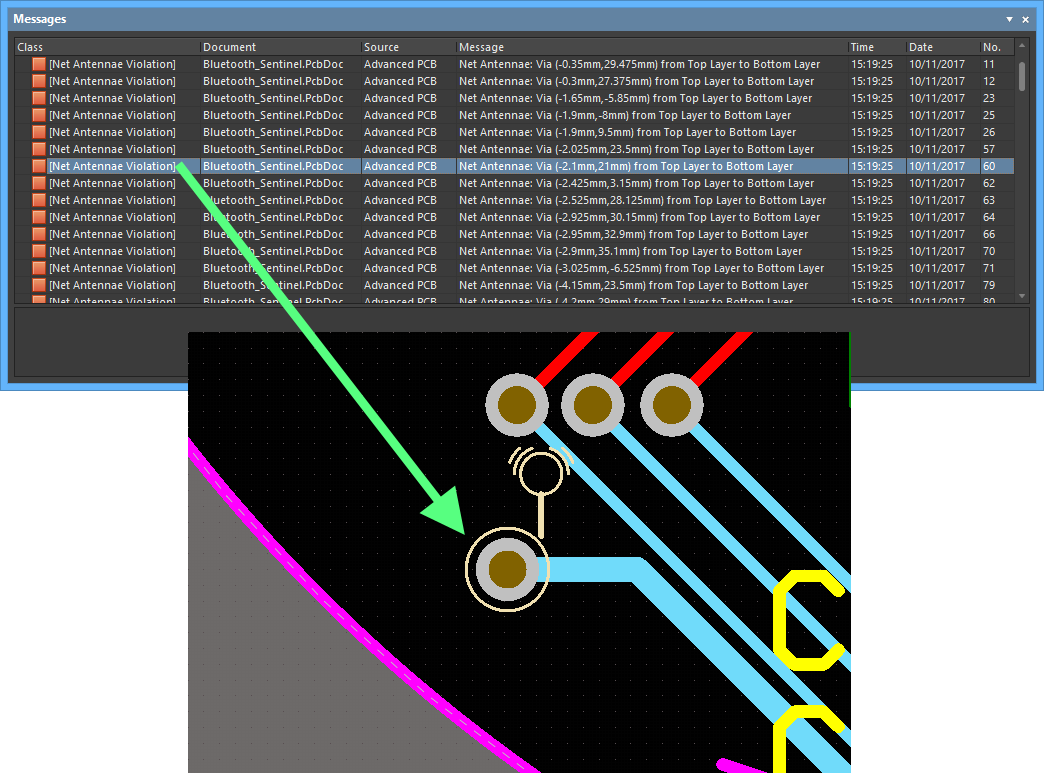

Из панели Messages

После проведения пакетной DRC дважды щелкните ЛКМ по сообщению о нарушении в панели Messages, чтобы перейти к объектам, вызывающим нарушение, в проектной области.

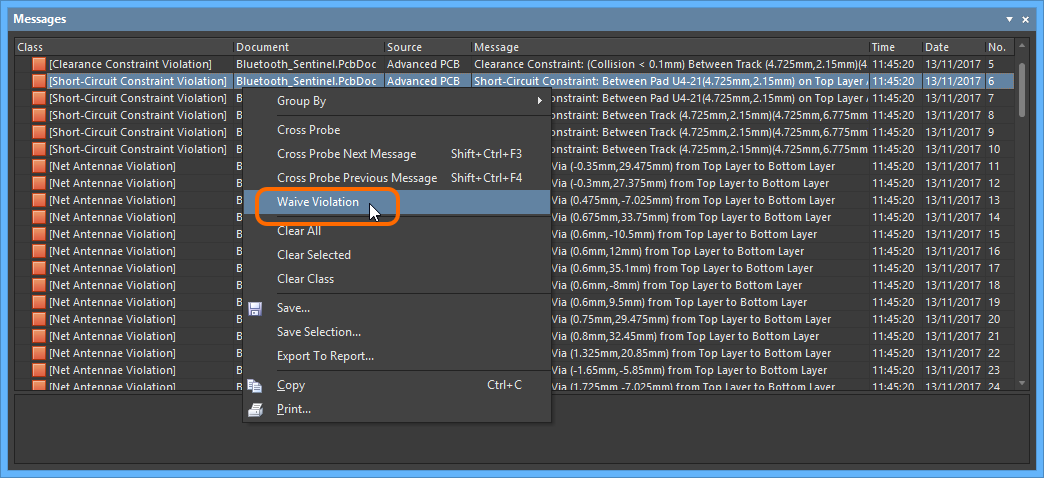

Перекрестный переход к нарушению из панели Messages.

Перекрестный переход к нарушению из панели Messages.

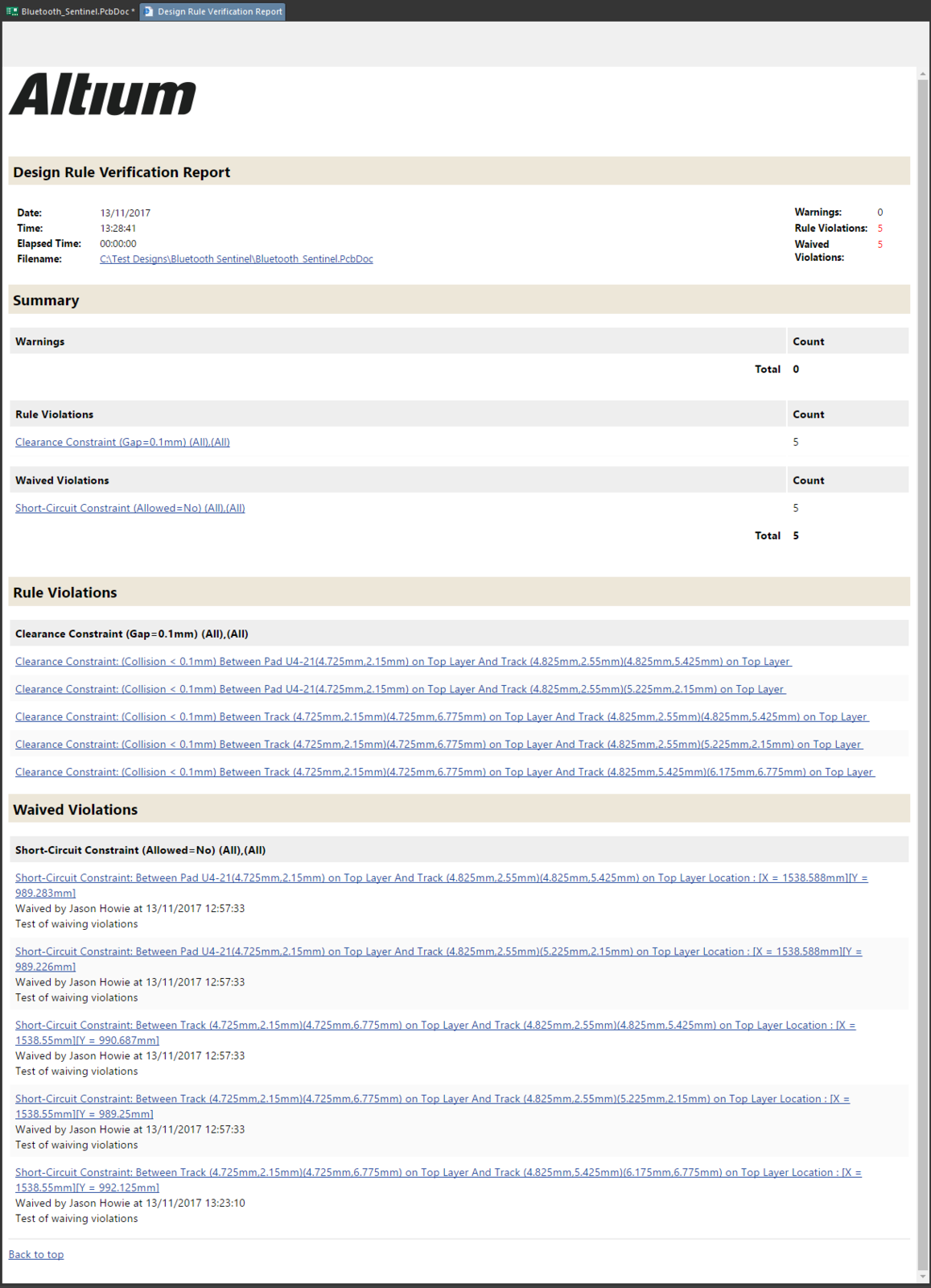

Из сформированного отчета о DRC

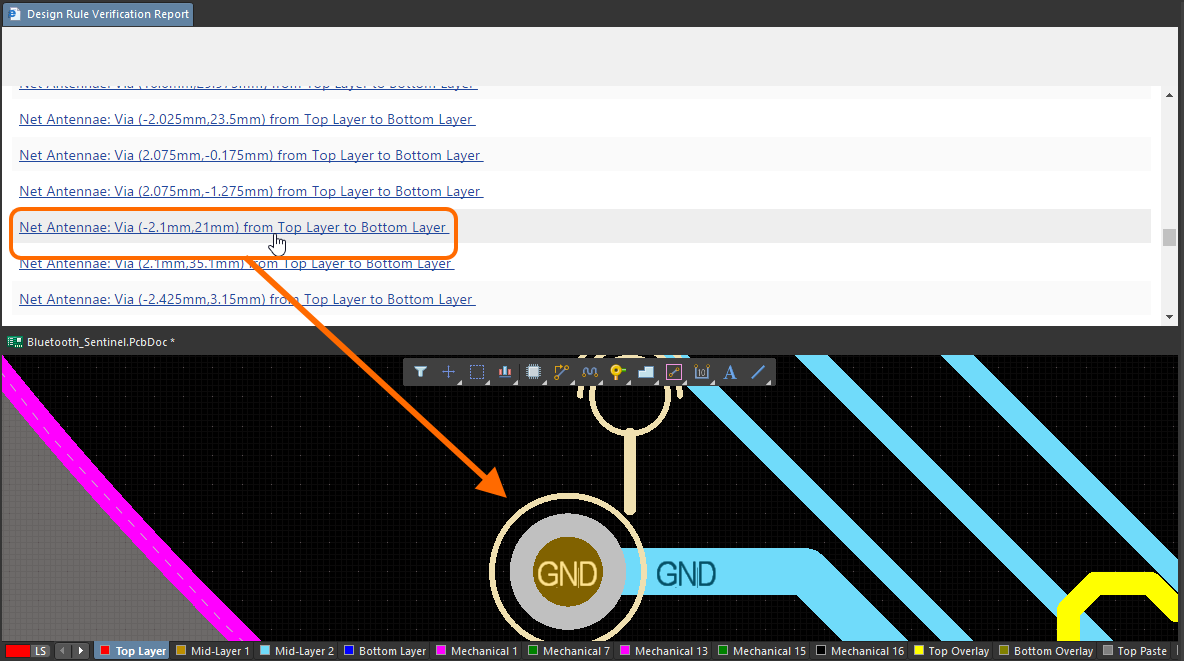

Если в диалоговом окне Design Rule Checker включена опция Create Report File, все обнаруженные в ходе пакетной DRC нарушения будут представлены в списке в сформированном отчете Design Rule Verification Report. Щелкните ЛКМ по гиперссылке объекта, вызывающего нарушение, чтобы перейти к нему в проектной области.

Перекрестный переход к вызывающему нарушение объекту из сформированного отчета о DRC.

Перекрестный переход к вызывающему нарушение объекту из сформированного отчета о DRC.

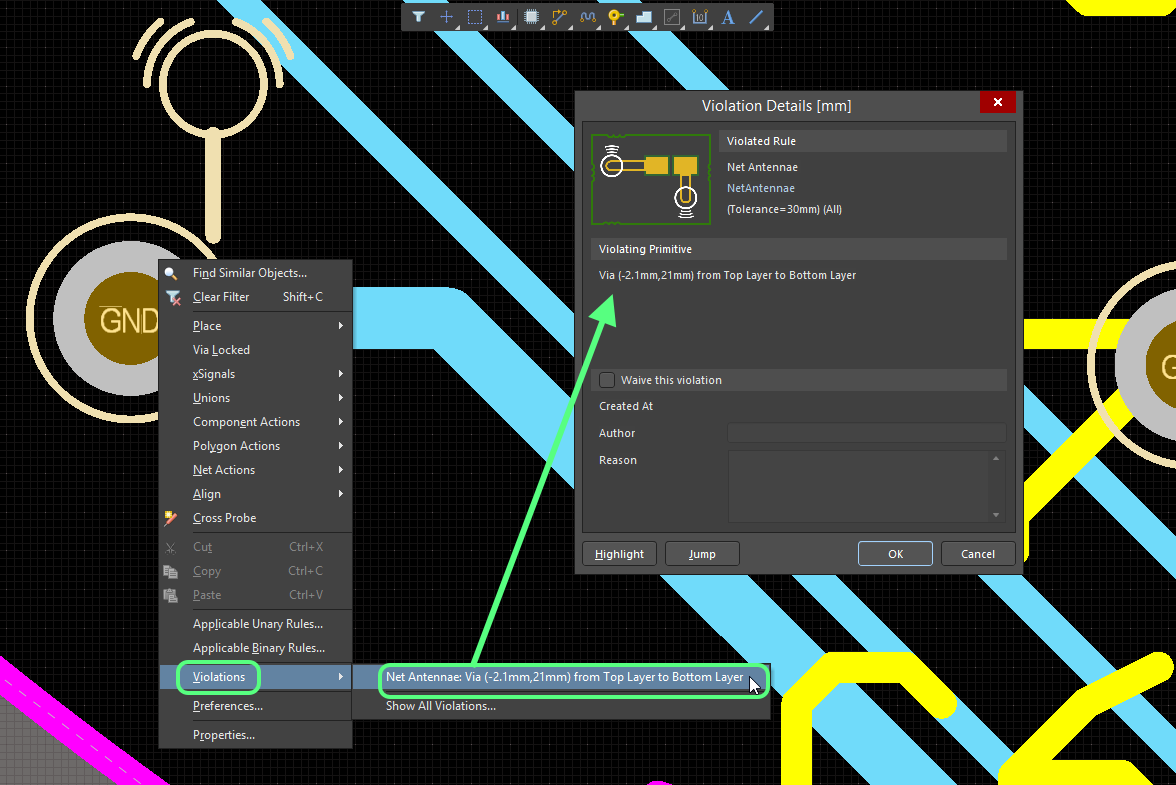

Непосредственно в проектной области

Нарушения, связанные с определенным проектным объектом, можно исследовать непосредственно в проектной области платы. Наведите курсор мыши на вызывающий нарушение объект, щелкните ПКМ и выберите команду из подменю Violations. Вы можете выбрать для исследования отдельное нарушение, в котором участвует объект, или все нарушения, в которых он участвует, с помощью команды Show All Violations. В любом случае, будет открыто диалоговое окно Violation Details с подробностями о нарушении и элементами управления для подсветки объектов, вызывающих нарушение, и перехода к ним.

Исследование нарушений, в которых участвует определенный объект, непосредственно в проектной области.

Исследование нарушений, в которых участвует определенный объект, непосредственно в проектной области.

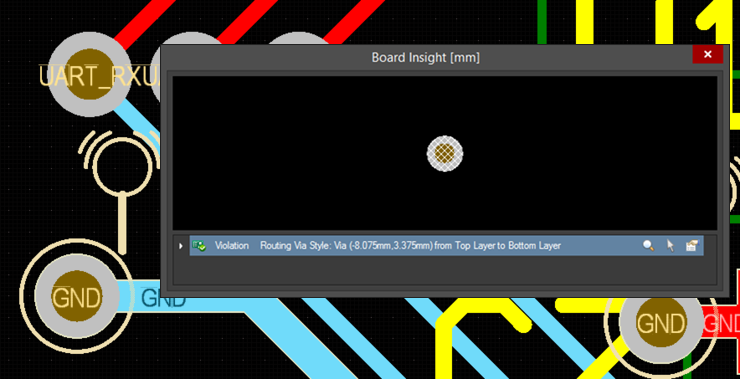

Нарушения также можно просмотреть непосредственно в проектной области с помощью всплывающего окна Board Insight. Наведите курсор мыши на объект с нарушением и включите отображение этого всплывающего окна с помощью сочетания клавиш Shift+V. Щелкните ЛКМ по строке нарушения, чтобы открыть меню команд, в том числе Properties, которая открывает диалоговое окно Violation Details. Разверните строку, чтобы увидеть список примитивов, которые участвуют в нарушении.

Исследование нарушения с помощью всплывающего окна Board Insight.

Выборочное отклонение нарушений DRC

Система поддерживает возможность выборочного отклонения нарушений DRC. Это позволяет фактически "подавить" нарушение, которое не считается проблемой, без необходимости в создании отдельного (возможно, довольно сложного) правила проектирования, которое учитывало бы определенную ситуацию в конструкции.

Отклонение нарушения DRC

Отклонить нарушение DRC можно следующими способами:

-

Выберите нарушение (или нарушения) в панели Messages, щелкните ПКМ и выберите команду Waive Violation из контекстного меню.

-

Выберите нарушение (или нарушения) в разделе Violations панели PCB Rules and Violations, щелкните ПКМ и выберите команду Waive Selected Violations из контекстного меню.

-

Включите опцию Waive this violation в диалоговом окне Violations Details. Чтобы открыть это диалоговое окно, дважды щелкните ЛКМ по нарушению в панели PCB Rules and Violations или используйте его исследование из рабочей области, как описано выше.

Для каждого отклоненного нарушения система записывает три составляющих. При отклонении нарушения из панели Messages или панели PCB Rules And Violations эти составляющие вводятся в диалоговом окне Waived Violation Info. В диалоговом окне Violation Details поля для ввода этой информации доступны, когда включена опция Waive this violation.

Ввод информации, которая хранится с отклоненным нарушением, вводится в диалоговом окне Waived Violation Info или в диалоговом окне Violation Details.

Ввод информации, которая хранится с отклоненным нарушением, вводится в диалоговом окне Waived Violation Info или в диалоговом окне Violation Details.

Информация, которая хранится с отклоненным нарушением:

- Created At – дата и время, когда нарушение было отклонено.

- Author – если вы подключены к серверу управляемых данных, это поле автоматически будет заполнено именем и фамилией подключенного пользователя, и это значение будет недоступно для редактирования. Если вы не подключены к серверу управляемых данных, это поле будет заполнено именем и фамилией из профиля подключенного пользователя, который в данный момент использует систему, и в этом случае поле будет доступно для редактирования.

- Reason – используйте это поле для опционального ввода причины, по которой нарушение было отклонено.

Обратите внимание, что эти изменения будут применены ко всем отклоняемым нарушениям, которые были выбраны.

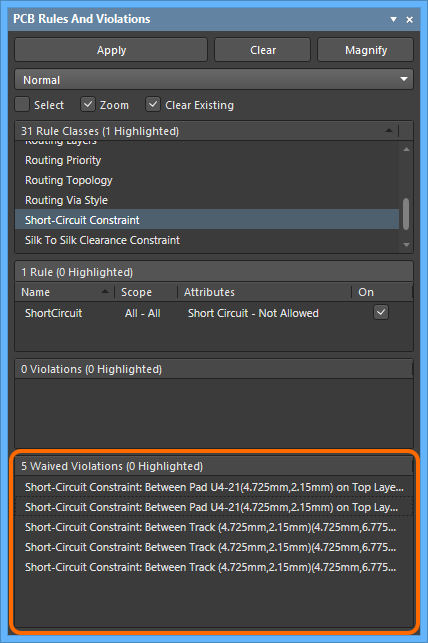

Работа с отклоненными нарушениями

Список отклоненных нарушений приводится в нижнем разделе панели PCB Rules and Violations, как показано на изображении ниже. Обратите внимание, что этот раздел отображается только в том случае, если в конструкции есть отклоненные нарушения.

Нарушения, которые были отклонены, перечислены в панели PCB Rules And Violations.

Нарушения, которые были отклонены, перечислены в панели PCB Rules And Violations.

Щелкните ЛКМ по строке отклоненного нарушения, чтобы перейти к нему в проектной области (если в верхней части панели включена опция Zoom). Дважды щелкните ЛКМ, чтобы перейти к нарушению (если включена опция Zoom) и открыть диалоговое окно Violation Details, где будет представлено это нарушение.

Отклоненное состояние нарушения можно отменить в любой момент одним из следующих способов:

- Щелкните ПКМ по нарушению в разделе Waived Violations панели PCB Rules And Violations и выберите команду Unwaive Selected Violations из контекстного меню.

- Откройте диалоговое окно Violation Details для отклоненного нарушения и отключите опцию Waive this violation.

Нарушение, отклоненное состояние которого было отменено, будет удалено из раздела Waived Violations панели PCB Rules And Violations, и оно появится в разделе Violations.

Документирование отклоненных нарушений

Отклоненные нарушения также приводятся в сформированном отчете о DRC, который создается, если в диалоговом окне Design Rule Checker была включена опция Create Report File.

Вся информация об отклоненных нарушениях приводится в отчете о DRC.

Вся информация об отклоненных нарушениях приводится в отчете о DRC.

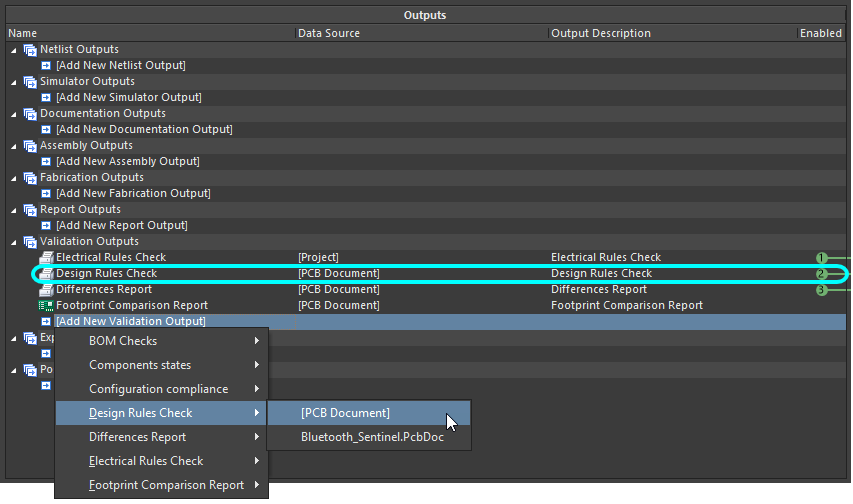

Валидация DRC в файле Output Job

Altium NEXUS позволяет настраивать и запускать создание валидационного отчета о DRC в файле Output Job (*.OutJob). Когда файл OutJob открыт в качестве активного документа, этот отчет доступен из группы выходных документов Validation Outputs. Чтобы добавить отчет, нажмите [Add New Validation Output] и выберите Design Rules Check и документ платы, который будет использоваться в качестве источника.

Добавление валидационного отчета о DRC в файл Output Job.

Добавление валидационного отчета о DRC в файл Output Job.

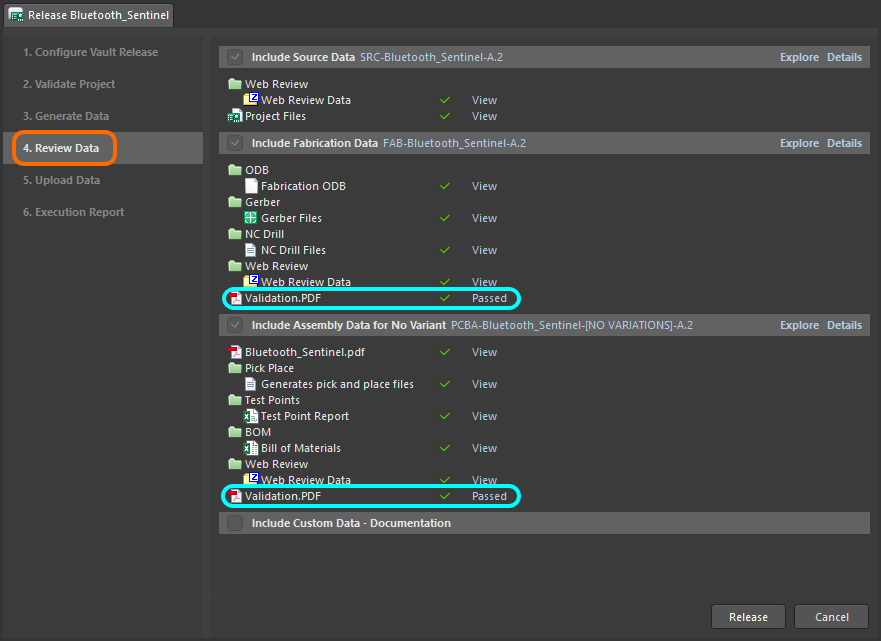

Валидация в рамках выпуска проекта платы

Если в назначенном файле Output Job определены валидационные отчеты, система позволит провести валидацию проекта как неотъемлемую часть процесса выпуска проекта. Эти валидационные проверки проводятся при каждом выпуске, и если какая-либо из валидационных проверок не пройдет успешно, выпуск завершится неудачей. Валидация проводится на этапе Validate Project в представлении Release, и ее результаты станут доступны на этапе Review Data.

Пример успешного проведения валидации для наборов производственных данных в представлении Release.

Пример успешного проведения валидации для наборов производственных данных в представлении Release.

), иначе соответствующая информация о нарушении или оверлей нарушения не будет отображаться.

), иначе соответствующая информация о нарушении или оверлей нарушения не будет отображаться.