Нарушение

Parent page: Объекты PCB

Нарушения правил проектирования четко отмечаются объектами нарушений.

Нарушения правил проектирования четко отмечаются объектами нарушений.

Сводка

Объект нарушения отмечает место, где один или несколько объектов проекта нарушают правило проектирования. Объекты нарушений также известны как маркеры ошибок DRC (Design Rule Check). Они добавляются в проект, когда нарушение обнаруживается функцией онлайн- или пакетной проверки правил проектирования (DRC).

Доступность и размещение

Объекты нарушений автоматически размещаются функцией Design Rule Check; это не объекты, которые можно размещать или редактировать вручную. Когда выполняется онлайн DRC или запускается пакетный DRC, каждый объект проекта, нарушающий правило проектирования, помечается объектом нарушения. Правила, которые в данный момент проверяются, настраиваются в диалоговом окне Design Rule Checker. Откройте это диалоговое окно, щелкнув Home | Design Rules | ![]()

, затем настройте правила, которые должны проверяться онлайн и/или в пакетном режиме.

И онлайн-, и пакетная проверка правил настраиваются в диалоговом окне Design Rule Checker. Каждый объект проекта, нарушающий правило, помечается

И онлайн-, и пакетная проверка правил настраиваются в диалоговом окне Design Rule Checker. Каждый объект проекта, нарушающий правило, помечается

объектом нарушения.

Отображение объектов нарушений

Существует два типа объектов нарушений: DRC Error Markers и DRC Detail Markers.

- DRC Error Markers — это маркеры, применяемые ко всему объекту, который находится в состоянии нарушения, независимо от места самого нарушения. Эти объекты позволяют быстро увидеть, где находится нарушающий объект, независимо от уровня масштабирования.

- DRC Detail Markers — детальные маркеры показывают место и причину нарушения правила проектирования. Эти маркеры дают мгновенную обратную связь о нарушаемом условии и размещаются в точке нарушения.

На изображениях ниже показано, как два типа маркеров работают вместе: изображение слева — при уменьшенном масштабе, изображение справа — при увеличенном масштабе тех же нарушений. На левом изображении показаны нарушения зазоров, отмеченные маркером ошибки DRC (красным); на правом изображении показаны и красный маркер ошибки, и белый детальный маркер, указывающий, что зазор меньше 0,6 мм, заданных в применимом правиле проектирования Electrical Clearance.

Нарушения зазоров: при уменьшении видны маркеры ошибок, при увеличении становятся видны детальные маркеры.

Нарушения зазоров: при уменьшении видны маркеры ошибок, при увеличении становятся видны детальные маркеры.

Отображение объектов нарушений можно настроить следующими способами.

Цвета маркеров DRC

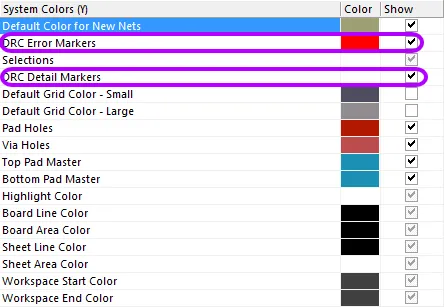

Цвет обоих типов маркеров настраивается на вкладке Board Layers and Colors диалогового окна View Configurations. Раздел System Colors этой вкладки показан ниже:

Настройте цвет Error и Detail Markers в диалоговом окне View Configurations.

Настройте цвет Error и Detail Markers в диалоговом окне View Configurations.

Стиль маркера ошибки и поведение при масштабировании

На изображениях выше маркеры ошибок DRC показаны как сплошные красные при уменьшенном масштабе и как красные точки с крестом при увеличенном. Поведение отображения этих маркеров можно настроить на странице PCB Editor — DRC Violations Display диалогового окна Preferences. Можно настроить два аспекта (см. изображение ниже):

-

Violation Overlay Style — маркеры ошибок могут отображаться одним из четырех следующих способов. Щелкните, чтобы выбрать предпочтительный стиль:

- None (Layer Color) — маркеры ошибок отображаются цветом слоя, поэтому не видны.

- Solid (Override Color) — маркеры ошибок отображаются цветом слоя Error Marker.

- Style A — маркеры ошибок отображаются в виде предупреждающего треугольника.

- Style B — маркеры ошибок отображаются в виде точки с крестом внутри.

-

Overlay Zoom Out Behavior — при уменьшении масштаба маркеры ошибок ведут себя следующим образом:

- Base Pattern Scales - маркеры ошибок масштабируются независимо от уровня масштабирования (тип маркера определяется выбранным выше параметром Violation Overlay Style).

- Layer Color Dominates - при уменьшении масштаба маркеры ошибок превращаются в сплошную область цвета слоя.

- Override Color Dominates - при уменьшении масштаба маркеры ошибок превращаются в сплошную область цвета слоя Error Marker.

Точка, начиная с которой при масштабировании отображаются детальные маркеры нарушений, задается ползунком Show Violation Detail.

Настройте стиль наложения (в этом примере — Style B) и то, как маркеры ошибок отображаются при разных уровнях масштабирования.

Настройте стиль наложения (в этом примере — Style B) и то, как маркеры ошибок отображаются при разных уровнях масштабирования.

Когда нарушения помечаются

Включенные правила проектирования определяют, какие правила проверяются и когда они проверяются (онлайн и/или пакетно). То, как затем помечаются обнаруженные нарушения, определяется параметрами DRC Violation Display Style на странице PCB Editor - DRC Violations Display диалогового окна Preferences.

Можно настроить отображение так, чтобы показывались только детали нарушений (Detail Markers), или наложение нарушений (Error Markers), или оба варианта. Включайте флажки по необходимости либо щелкните правой кнопкой мыши в диалоговом окне, чтобы включить/выключить сразу несколько параметров.

Выберите, какие нарушения будут отображаться как детали, с наложением или в обоих вариантах.

Выберите, какие нарушения будут отображаться как детали, с наложением или в обоих вариантах.

Понимание нарушений

Существует несколько способов отображения информации о нарушениях в программе. Маркеры нарушений (и наложения, и детальные) дают четкие подсказки о месте и характере нарушения. Например, на изображении ниже переходное отверстие слева имеет детальный маркер, показывающий, что диаметр via меньше 1 мм, значит он должен быть меньше допустимого размера в применимом правиле проектирования Routing Via Style. Также от via к расположенному рядом пэду проведена линия, и эта линия прерывается двойным слэшем. Это означает, что цепь между via и пэдом не разведена (разорвана). Используйте детальные маркеры, чтобы интерпретировать состояние ошибки.

Детальные маркеры, показывающие via с недостаточным размером и неразведенную цепь.

Детальные маркеры, показывающие via с недостаточным размером и неразведенную цепь.

Помимо маркеров, все обнаруженные нарушения подробно перечислены на панели PCB Rules and Violations (Home | Design Rules | ![]()

). На изображении ниже показан фрагмент панели с выбранным ограничением Clearance Constraint; ниже показано, что выбрано одно правило; еще ниже — что есть два нарушения этого правила.

Используйте панель PCB Rules and Violations, чтобы быстро находить нарушения правил проектирования.

Используйте панель PCB Rules and Violations, чтобы быстро находить нарушения правил проектирования.

Щелкните по нарушению один раз, чтобы приблизить рабочую область к месту нарушения; дважды щелкните по нему, чтобы открыть диалоговое окно Violation Details, в котором подробно описаны и Violated Rule, и Violating Primitives.

Диалоговое окно Violation Details показывает и правило, и примитивы, участвующие в состоянии ошибки.

Диалоговое окно Violation Details показывает и правило, и примитивы, участвующие в состоянии ошибки.

Очистка объектов нарушений

Объекты нарушений можно удалить, выполнив команду Reset Error Markers . Нажмите Home | Design Rules | ![]()

» Reset Error Markers. Обратите внимание: это удаляет только маркеры ошибок; сами нарушения правил проектирования все равно необходимо проанализировать и устранить.

Локализовано с помощью ИИ

Локализовано с помощью ИИ