违规

Parent page: PCB 对象

概述

违规对象用于标记一个或多个设计对象违反设计规则的位置。违规对象也称为 DRC(Design Rule Check,设计规则检查)错误标记。它们会在在线或批量 Design Rule Check (DRC) 功能检测到违规时添加到设计中。

可用性与放置

违规对象由 Design Rule Check 功能自动放置;它们不是可以手动放置或编辑的对象。当在线 DRC 正在运行或执行批量 DRC 时,每个违反设计规则的设计对象都会被一个违规对象标记。当前正在检查的规则在 Design Rule Checker 对话框中配置。通过单击 Home | Design Rules | ![]()

访问该对话框,然后配置需要进行在线和/或批量检查的规则。

在线与批量规则检查都在 Design Rule Checker 对话框中配置。每个违反规则的设计对象都会被

在线与批量规则检查都在 Design Rule Checker 对话框中配置。每个违反规则的设计对象都会被

通过一个违规对象标记。

违规对象的显示方式

违规对象有两种类型:DRC Error Markers 和 DRC Detail Markers。

- DRC Error Markers - 这类标记会应用到整个违规对象上,而不管违规发生在对象的哪个位置。无论缩放级别如何,这些对象都便于快速看出哪里存在违规对象。

- DRC Detail Markers - 细节标记会显示设计规则违规的位置和原因。这些标记能对被违反的条件提供即时反馈,并放置在违规位置。

下图展示了两种标记如何配合工作——左图为缩小视图,右图为对同一处违规的放大视图。左图显示用 DRC 错误标记(红色)标出的间距违规;右图同时显示红色错误标记和白色细节标记,表明间距小于适用的 Electrical Clearance 设计规则中规定的 0.6 mm。

违规对象的显示方式可通过以下方式进行配置。

DRC 标记颜色

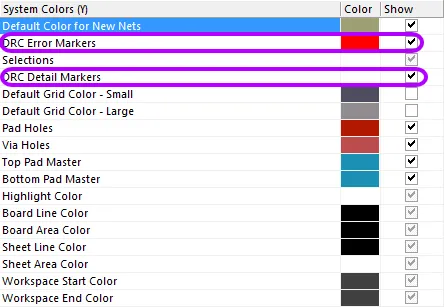

两种标记的颜色都在 Board Layers and Colors 选项卡的 View Configurations 对话框中配置。该选项卡中的 System Colors 区域如下所示:

在 View Configurations 对话框中配置 Error 和 Detail Markers 的颜色。

在 View Configurations 对话框中配置 Error 和 Detail Markers 的颜色。

错误标记样式与缩放行为

在上面的图中,DRC 错误标记在缩小时显示为实心红色,在放大时显示为带十字的红点。这些标记的显示行为可在 PCB Editor — DRC Violations Display 页面的 Preferences 对话框中配置。可配置两个方面(参见下图):

-

Violation Overlay Style - 错误标记可通过以下四种方式之一显示。单击选择你偏好的样式:

- None (Layer Color) - 错误标记以层颜色显示,因此不可见。

- Solid (Override Color) - 错误标记以错误标记层颜色显示。

- Style A - 错误标记显示为警告三角形。

- Style B - 错误标记显示为内部带十字的点。

-

Overlay Zoom Out Behavior - 当你缩小时,错误标记将执行以下行为:

- Base Pattern Scales - 无论缩放级别如何,错误标记都会按比例缩放(标记类型由上方选择的 Violation Overlay Style 决定)。

- Layer Color Dominates - 随着缩小,错误标记会变为层颜色的实心色块。

- Override Color Dominates - 随着缩小,错误标记会变为错误标记层颜色的实心色块。

缩放时显示违规细节标记的阈值由 Show Violation Detail 滑块控制。

配置叠加样式(本例为样式 B)以及错误标记在不同缩放级别下的显示方式。

配置叠加样式(本例为样式 B)以及错误标记在不同缩放级别下的显示方式。

何时标记违规

启用的设计规则决定检查哪些规则以及何时检查(在线和/或批量)。检测到的违规随后如何被标记,则由 Preferences 对话框的 PCB Editor - DRC Violations Display 页面上的 DRC Violation Display Style 设置决定。

你可以配置显示为仅显示违规细节(细节标记),或显示违规叠加(错误标记),或两者同时显示。按需启用复选框,或在对话框中右键以切换多个选项的开/关。

理解违规信息

软件中有多种方式显示违规信息。违规标记(叠加与细节)能为违规的位置与性质提供强有力的线索。例如,在下图中,左侧的过孔带有一个细节标记,显示过孔直径小于 1mm,因此它必然小于适用的 Routing Via Style 设计规则允许的尺寸。还可以看到从该过孔到附近焊盘画出了一条线,并且这条线被双斜杠打断。这表示该网络在过孔与焊盘之间未布线(断开)。使用细节标记来帮助解读错误状态。

除了标记之外,所有检测到的违规都会在 PCB Rules and Violations 面板(Home | Design Rules | ![]()

)中详细列出。下图显示了面板的一部分:选中了 Clearance Constraint;其下显示选中了一个 Rule;再下显示该规则有两处 Violations。

使用 PCB Rules and Violations 面板快速定位设计规则违规。

使用 PCB Rules and Violations 面板快速定位设计规则违规。

单击一次某个违规可在工作区缩放定位到该违规,双击可打开 Violation Details 对话框,其中会详细列出 Violated Rule 以及 Violating Primitives。

Violation Details 对话框会显示规则以及与错误状态相关的图元。

Violation Details 对话框会显示规则以及与错误状态相关的图元。

清除违规对象

可通过运行 Reset Error Markers command 来移除违规对象。单击 Home | Design Rules | ![]()

» Reset Error Markers。注意,这只会移除错误标记;底层的设计规则违规仍需要分析并解决。

AI 翻译

AI 翻译