PDN Analyzer(PDNA)アプリケーションは比較的使いやすく、基本的にはPI-DCシミュレーションのネット・パラメータを設定し、シミュレーションを実行して結果を解釈する、という流れになります。PDN Analyzerの電源ネット・シミュレーションで使用されるデータは、現在読み込まれているPCB設計プロジェクトから直接取得されます。これにより、電源供給パスのパワーインテグリティを改善するために設計を反復的に編集し、その都度PDNシミュレーションを再実行して結果を検証できます。

PDN Analyzerの操作を示すこのデモガイドでは、Altiumから入手できる2つのリファレンスデザインを使用します。

さらに、PDN Analyzerのインストールには、複数の解析設定ファイル例を含むSpiritLevel PCBプロジェクトが同梱されています。PDNAのFile » Explore Samplesメニューオプションからプロジェクトとサンプルにアクセスし、解凍してください。

このガイドは、使用中のAltium DesignerにPDN Analyzerが利用可能であり、またPI-DC(DC Power Integrity)の原理について基本的な理解があることを前提としています。

PDN Analyzer機能へのアクセス方法、およびPI-DCシミュレーションの基礎については、PDN Analyzer pageを参照してください。

PDN Analyzer Interface

PDN Analyzer拡張のインターフェースは、Altium Designerの非モーダルウィンドウとして起動され、ワークスペース内の任意の場所、または利用可能であれば別画面にも配置できます。メインのPDN Analyzerウィンドウを開くには、プロジェクトの回路図またはPCBドキュメントを開き、Toolsメニュー(Tools » PDN Analyzer)からアプリケーションを選択します。

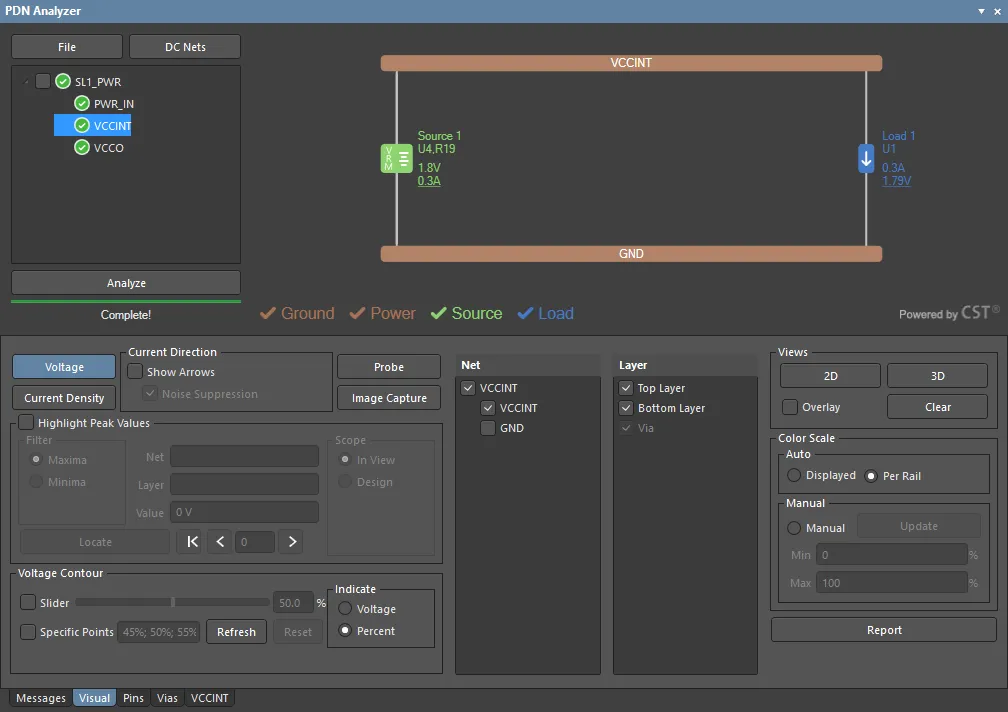

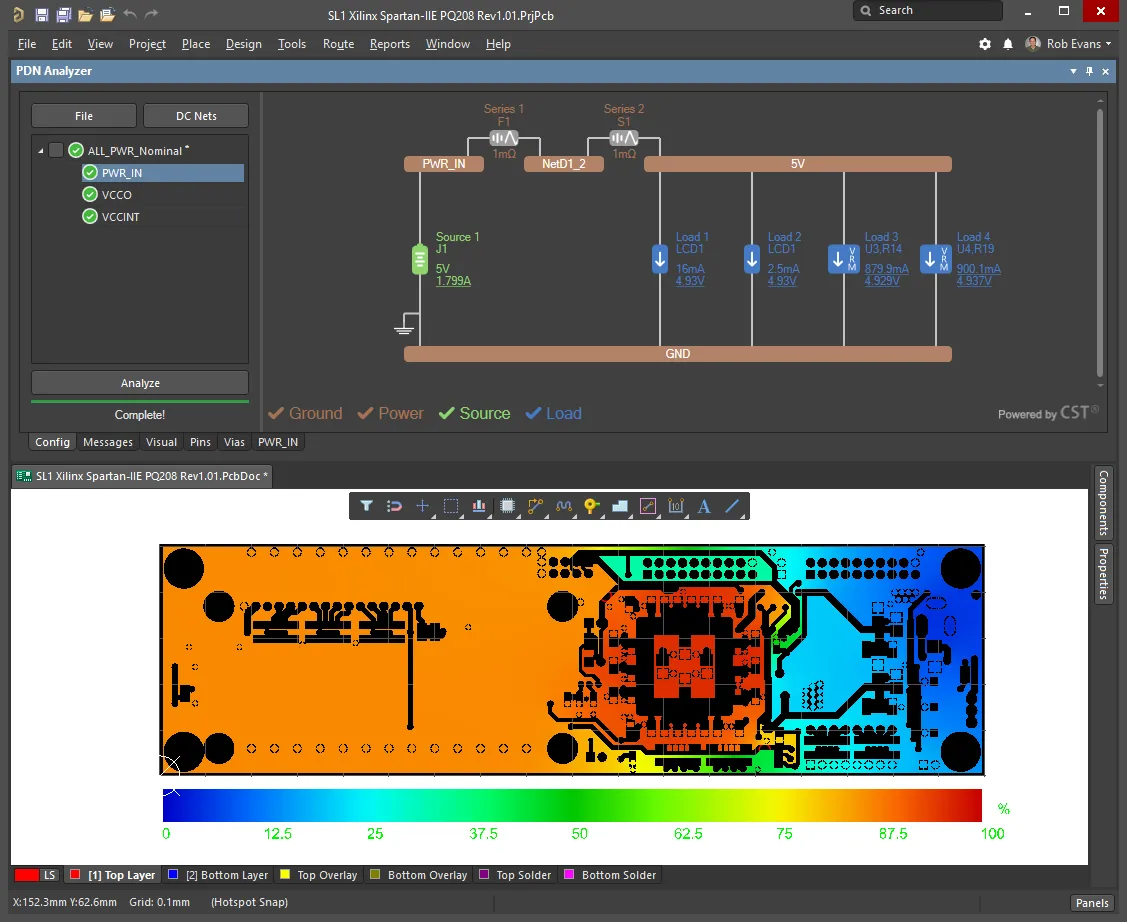

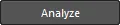

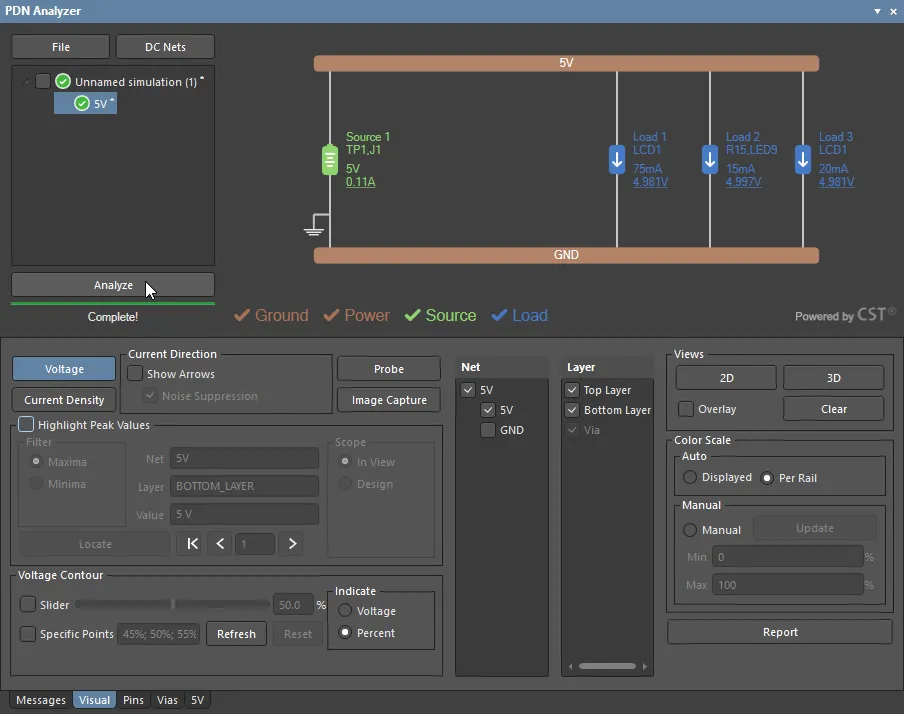

単一の電源ネットワークを選択したPDN Analyzer GUI。表示および結果の設定は下部パネルで行えます。

単一の電源ネットワークを選択したPDN Analyzer GUI。表示および結果の設定は下部パネルで行えます。

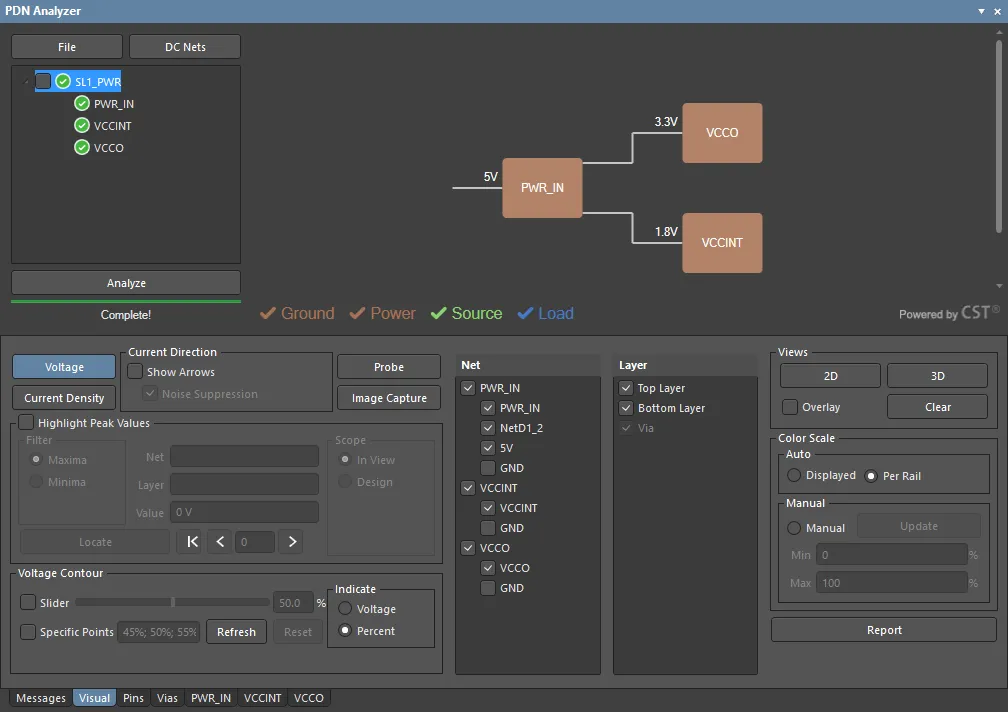

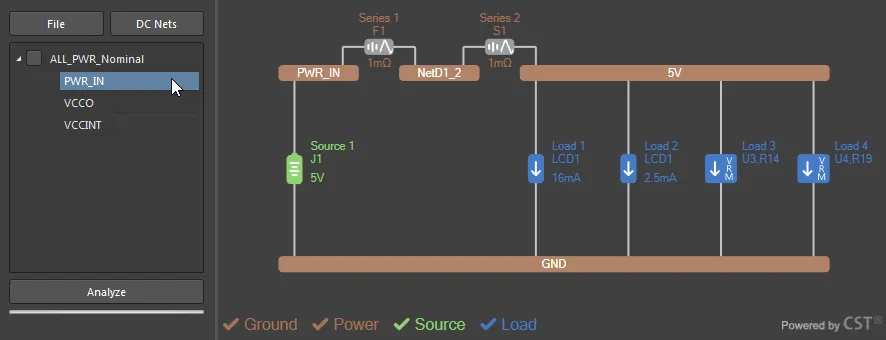

PDNAウィンドウGUIは、上部がファイル/ネット制御と、現在選択されている電源ネットワークのインタラクティブ表示に割り当てられ、下部パネルでは解析オプション、表示設定、結果データにアクセスできます。PDNAバージョン2では、複数の相互接続されたネットに対応しており、PCB設計全体のDCパワーインテグリティを階層構造として、または個別の電源ネットとして解析できます。

電源ネット階層全体を選択したPDN Analyzer GUI。含まれるネットワークとレイヤの表示は下部パネルで制御します。

電源ネット階層全体を選択したPDN Analyzer GUI。含まれるネットワークとレイヤの表示は下部パネルで制御します。

PDNインターフェースには、下部パネルを含まないコンパクト画面モード(File » Compact Layout)も用意されており、Altium Designerのメイン画面での水平/垂直ドッキングに最適です。コンパクトまたは標準画面モードで画面ドッキングを有効にするには、PDNAインターフェースのタイトルバーを右クリックし、コンテキストメニューからAllow Dockを選択して、HorizontallyまたはVerticallyオプションを選びます。

以下の折りたたみセクションでは、PDN Analyzerパネルのユーザーインターフェースの詳細を説明します。

PDN Analyzer Panel

Layout Modes

ドッキング可能なPDN Analyzerパネルは、ソフトウェアのPCB Editorと併用するのが最適です。これにより、解析実行の視覚的な結果を設計の銅箔レイアウト上で即座に確認できます。フローティング(未ドッキング)モードでは、PCB Editorの視認性を保つためにパネルを第2モニタへ移動できます。また、メイン設計画面に対して垂直/水平にドッキングし、PCB Editorと画面領域を共有することも可能です。

後者の場合、パネルにはコンパクトなインターフェースモードが用意されており、メインの設定ペインを別タブ(Config)へ移動します。このモードに切り替えるには、設定ペイン/タブ内のパネル ボタンのドロップダウンメニューからCompact Layoutオプションを選択します。

ボタンのドロップダウンメニューからCompact Layoutオプションを選択します。

Compact Layoutモードでは、Configurationペインがタブアクセスに切り替わり、PCB Editorのための画面スペースを確保できます。

Compact Layoutモードでは、Configurationペインがタブアクセスに切り替わり、PCB Editorのための画面スペースを確保できます。

Configuration

Configurationペイン(またはConfigタブ)は、シミュレーションネットワークの制御に割り当てられており、現在選択されている電源ネットワークのインタラクティブなグラフィック表現を表示します。

Simulation and network management

Configurationペイン/タブの左側セクションは、シミュレーションファイル管理に使用され、読み込まれた電源ネットワークを階層表示します。ネットワーク構造全体、または個別の電源ネットワークを選択できます。このセクションのオプションには次が含まれます。

-

ドロップダウンメニュー。

ドロップダウンメニュー。

-

New Simulation – 単一の電源/グラウンドネットワークに基づいて、新しいPDNシミュレーションを開始します。

-

Open – 以前に保存した、またはサンプルのシミュレーション設定ファイル(

*.pdna)を開きます。

-

Save – アクティブなシミュレーション設定を、現在の名前でディスクに保存します。

-

Save As – アクティブなシミュレーション設定を、指定した名前でディスクに保存します。

-

Explore – アクティブなシミュレーションの場所をWindowsのファイルブラウザで開きます。

-

Explore Samples – インストールに含まれるサンプルプロジェクト(zipアーカイブとして保存)をWindowsのファイルブラウザで開きます。プロジェクトを任意の場所に解凍してください。なお、このプロジェクトにはPDN Analyzer設定ファイルの例も含まれており、それぞれ銅箔温度が25°C(公称)、100°C、175°Cに設定されています。

-

Compact layout – 上で説明した代替画面モードです。

-

Right click options – 最上位のシミュレーション名を右クリックしてアクセスします。

-

Import (1.x) – 以前の

1.xxバージョンのPDN Analyzer(*.pidc_config)で保存したシミュレーション設定を読み込みます。

-

New Network – 現在のシミュレーション設定内に、新しいベースレベルのネットワークを作成します。

-

Remove – 選択したシミュレーションをアンロードします。

-

Delete – 選択したネットワークをシミュレーションから削除します(個別ネットワーク名の右クリックオプションとして利用可能)。

-

Clear Results – 電源ネットワーク解析結果をリセットします(前回のシミュレーション実行からキャッシュされた結果を含む)。

-

Revert – 直前のシミュレーション解析結果と、それに対応する設定を復元します。

-

Save – アクティブなシミュレーション設定を、現在の名前(

*.pdna)でディスクに保存します。

-

Save As – アクティブなシミュレーション設定を、指定した名前でディスクに保存します。

-

Copy – 選択したネットワークシミュレーションを複製します。

-

Explore – 現在のシミュレーションの

/PDNAnalyzer_OutputフォルダをWindowsのファイルブラウザで開きます。ここには、直近に実行したシミュレーションの詳細なイベントログファイル(PDNAnalyzer.log)も含まれます。

-

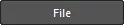

Settings – 現在のシミュレーション設定のSettings dialogを開きます。設定はエクスポート/インポート(

*.pdna.settings)でき、デフォルトにリセットすることも可能です。

このダイアログには次が含まれます。

-

Simulationタブ – 実基板の銅箔の金属導電率設定、およびレイヤ接続ビアの重量(壁厚)を指定します。

-

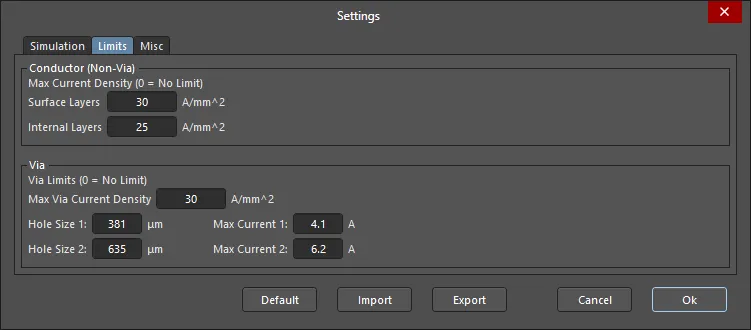

Limitsタブ – 銅箔レイヤと2種類のサイズのビアについて、シミュレーションで検出される最大電流密度の制限を指定します。

-

Miscタブ – 印加電流密度の単位、データ平滑化(Noise Filtering)、および設計のゼロ電圧基準を確立するための電圧オフセット方式など、シミュレーションパラメータを設定します。

-

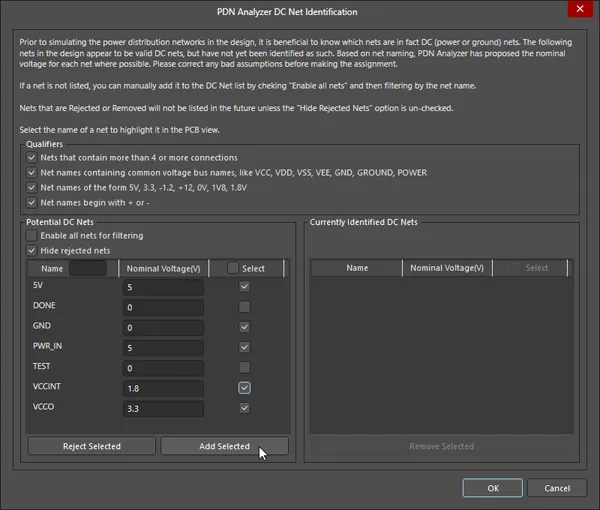

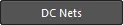

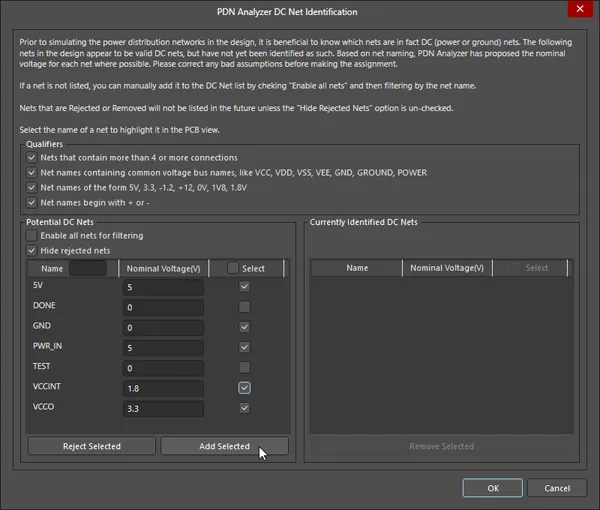

ボタン。PDN Analyzer DC Net Identificationダイアログを開きます(PDN Analyzerを最初に起動したときにも表示されます)。システムは、現在のPCB設計内から適切なDC電源ネットを自動検出しようとします。

ボタン。PDN Analyzer DC Net Identificationダイアログを開きます(PDN Analyzerを最初に起動したときにも表示されます)。システムは、現在のPCB設計内から適切なDC電源ネットを自動検出しようとします。

ダイアログのオプションを使用して、DCネットとその公称電圧レベルを正しく識別できるようにします。

-

Qualifiers – 必要に応じて、識別用フィルタを解除し、設計のDCネットを正しく特定します。フィルタは接続数と一般的な電源ネット命名規則に基づいています。

-

Potential DC Nets – 設計内で識別された電源ネットの表形式リストです。DC電源解析に必要に応じて、Enable allおよび/またはHide rejectedオプションを使用してリストを作成します。

-

Name – 基板設計のネットデータから抽出されたネット名です。関連する検索フィールドを使用して、入力したキーワードで一覧をフィルタできます。

-

Nominal Voltage – 解析の基本ソースデータとして、電源ネットに適切な電圧を入力します。

-

Select – チェックボックスを使用して、PDNシミュレーションに登録(識別)させたいネットを指定します。

-

Reject/Add Selected –

および

および ボタンを使用して、Currently Identified DC Nets一覧に反映するネットを管理します。

ボタンを使用して、Currently Identified DC Nets一覧に反映するネットを管理します。

-

Currently Identified DC Nets – Potential DC Nets一覧から反映された、PDNシミュレーションで利用可能な電源ネットの表形式リストです。

-

Select –

ボタンにより削除(識別済みネット一覧から候補ネット一覧へ戻す)されるネットを、チェックボックスで選択します。

ボタンにより削除(識別済みネット一覧から候補ネット一覧へ戻す)されるネットを、チェックボックスで選択します。

ネットのエントリをクリックすると、PCB Editorでそのネットへクロスプローブします。

-

ボタン。電源ネットワークのシミュレーションおよび解析ルーチンを実行します。このボタンは、電源ネットワークと関連データが完全に設定されると有効になります。これは、電源ネットワーク図のGround、Power、Source、Loadラベルに関連付けられたチェックアイコンで示されます。

ボタン。電源ネットワークのシミュレーションおよび解析ルーチンを実行します。このボタンは、電源ネットワークと関連データが完全に設定されると有効になります。これは、電源ネットワーク図のGround、Power、Source、Loadラベルに関連付けられたチェックアイコンで示されます。

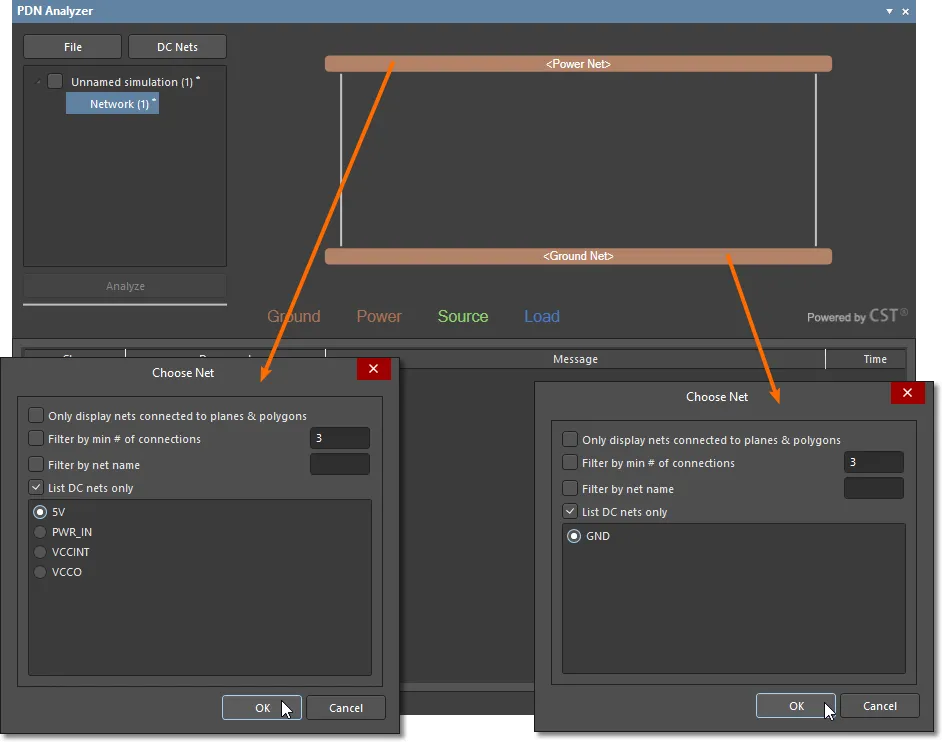

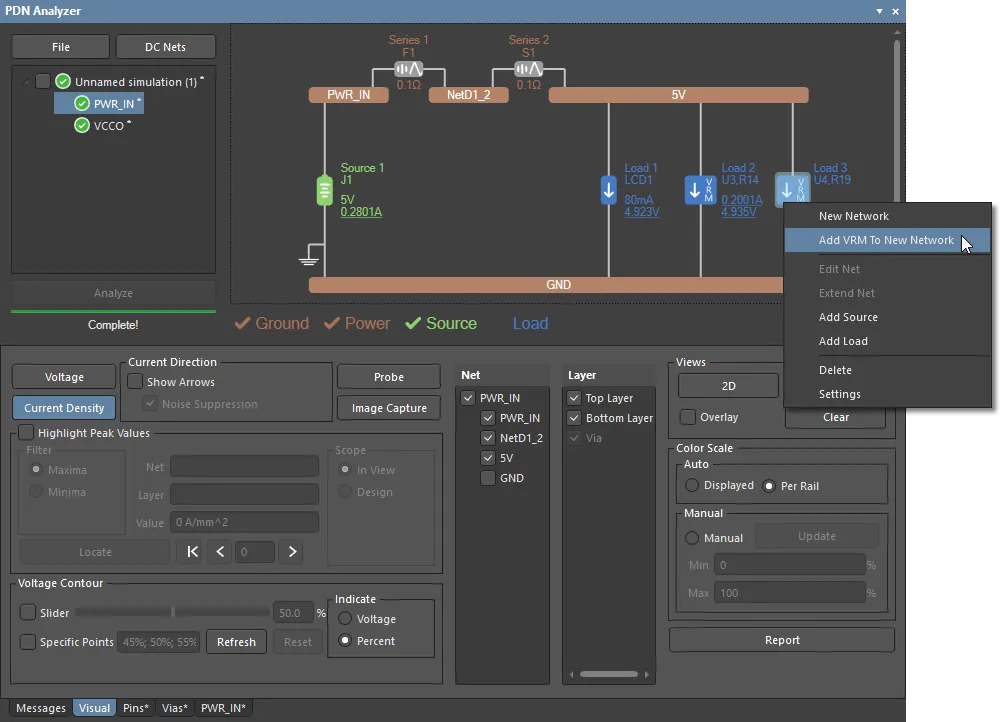

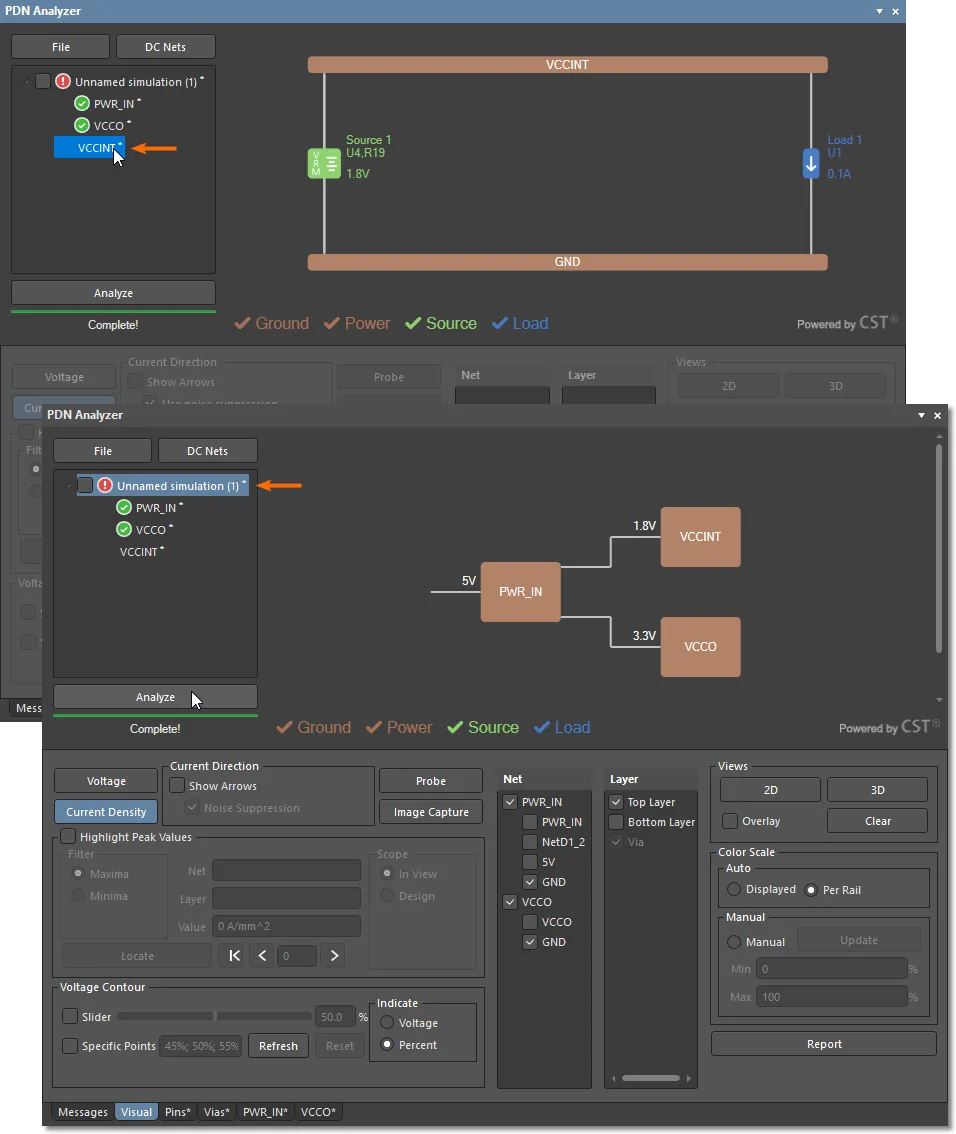

Power Network Graphic

Configurationペインの主領域には、(左側の)シミュレーションのネットワークツリーで選択された電源ネットワーク構造の、インタラクティブなグラフィック表現が表示されます。最上位のシミュレーション名を選択すると、グラフィックにはサブ電源ネットワークの全体的な接続関係が表示されます。サブネットワークのグラフィック要素をダブルクリックすると、そのサブネットワークを開きます。このインタラクティブグラフィックは、右クリックオプションを使用するか、グラフィック要素をダブルクリックすることで、PCB設計のネットデータと接続性に基づいて電源ネットワークを構築する用途にも使用されます。

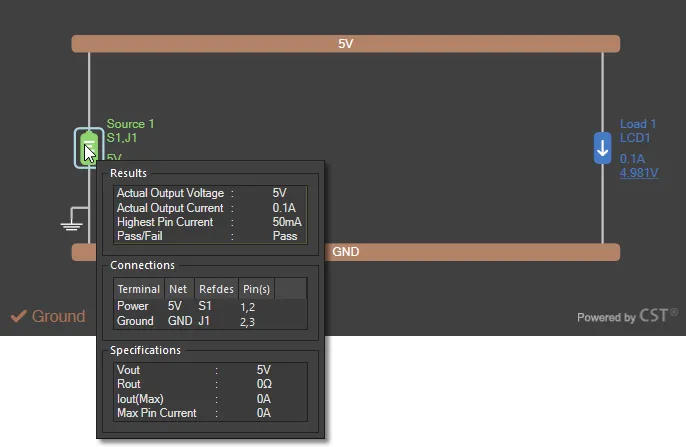

アクティブな要素(Source、Load、直列デバイスなど)にカーソルを合わせると、そのプロパティ、接続性、該当する場合は解析結果の概要が表示されます。

► 各種タイプの電源ネットワーク作成の詳細は、以下のExample 1、Example 2、Example 3を参照してください。

設定グラフィックまたはその要素のいずれかを右クリックすると、次のオプションにアクセスできます。

-

New Network– 現在のシミュレーション内に、新しいベースレベルのネットワーク(電源ネットおよびグランドネット)を作成します。

-

Edit Net – Choose Net ダイアログで電源ネットワークの設定を指定します(ネットワーク要素をダブルクリックしても開けます)。このダイアログには、シミュレーションで使用可能なネットの選択リスト(PDN Analyzer Net Identification ダイアログで定義。

ボタンから開く)と、リスト表示を絞り込むための複数のフィルターオプションが含まれます。

ボタンから開く)と、リスト表示を絞り込むための複数のフィルターオプションが含まれます。

-

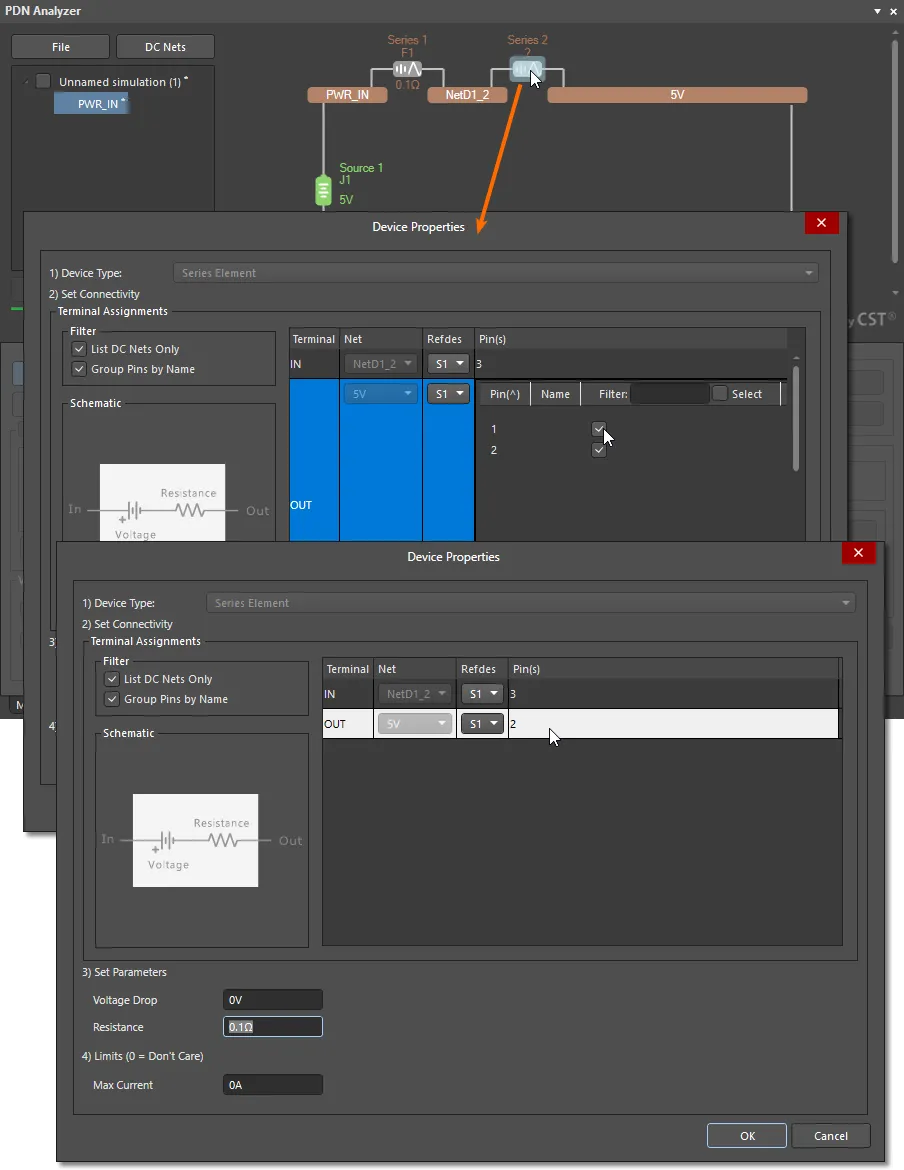

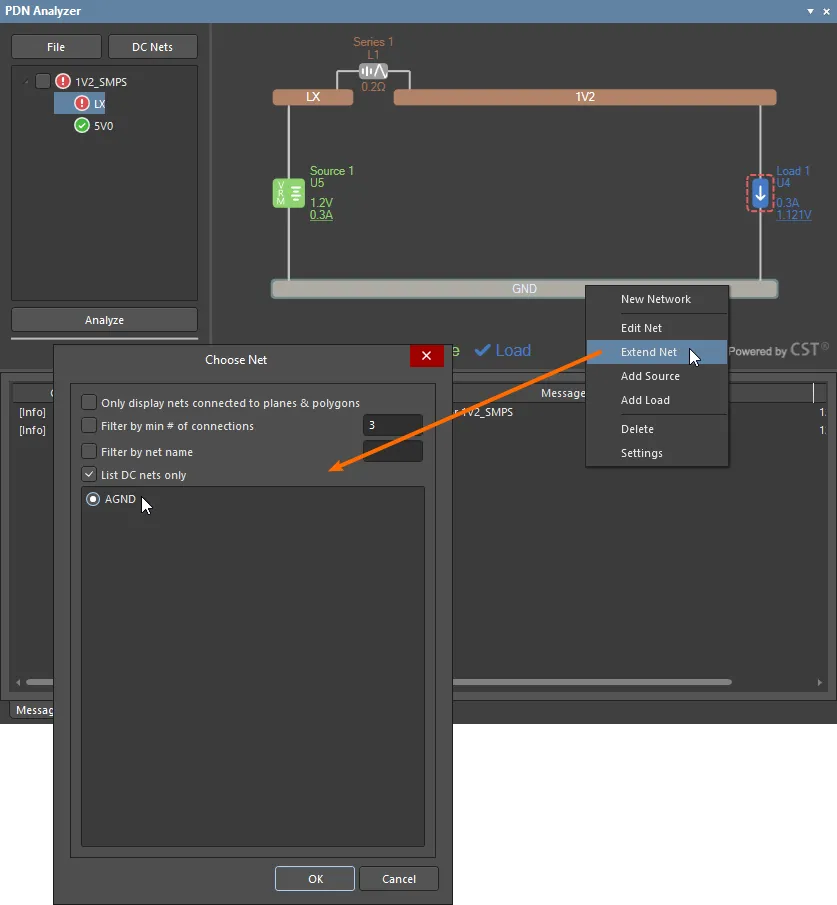

Extend Net – 直列要素を介して、選択したネットに別のネットを追加するために使用します。直列要素は自動的に挿入されます。追加するネットは Choose Net ダイアログで選択し、挿入された直列デバイスは、その要素をダブルクリックして Device Properties ダイアログにアクセスし設定します。詳細は Extending Networks Through Series Elements を参照してください。

-

Add Source – Device Properties ダイアログを使用して、指定した電源/グランドのネットペア間に Voltage または Voltage Regulator Model (VRM) のソースデバイスを追加します。このダイアログは既存の Source 要素をダブルクリックしても利用できます。VRM の扱いについての詳細は Including Voltage Regulator Models を参照してください。

-

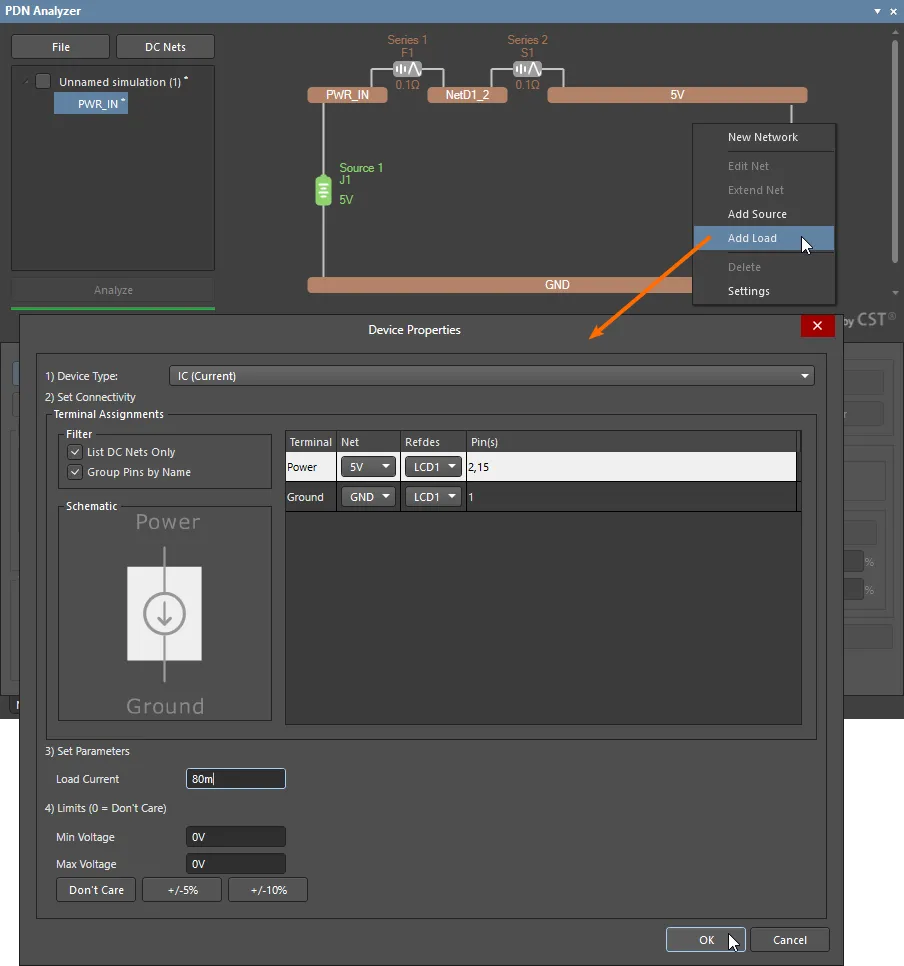

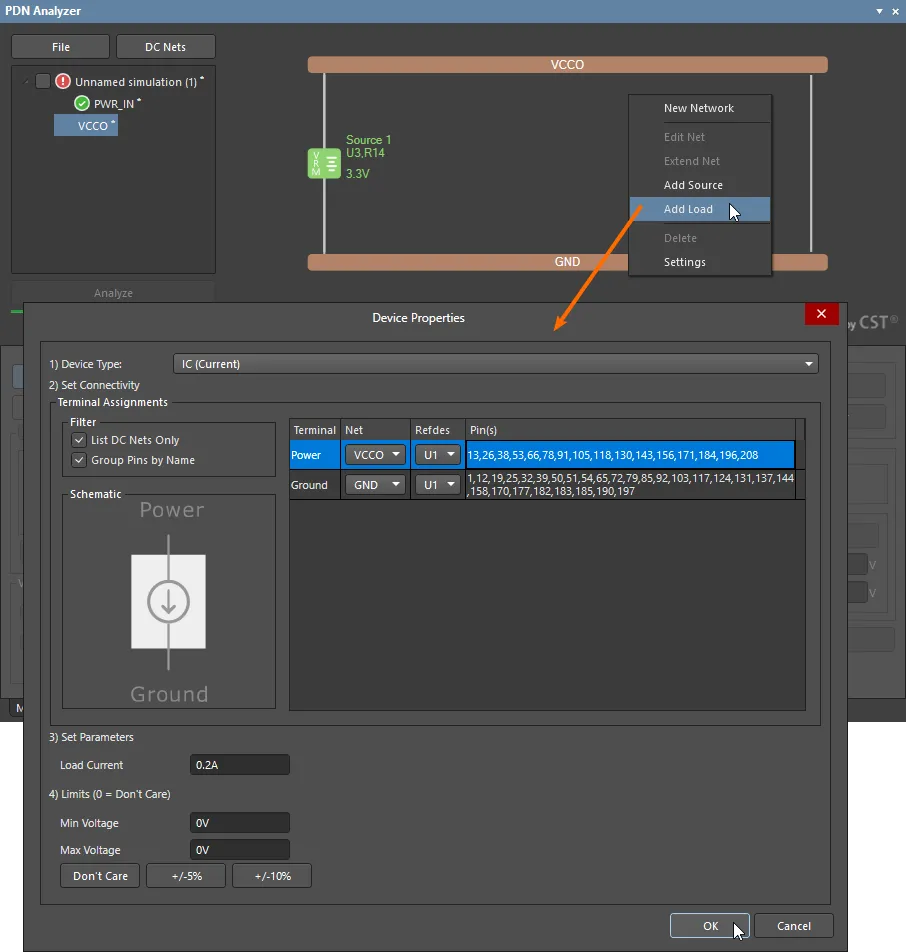

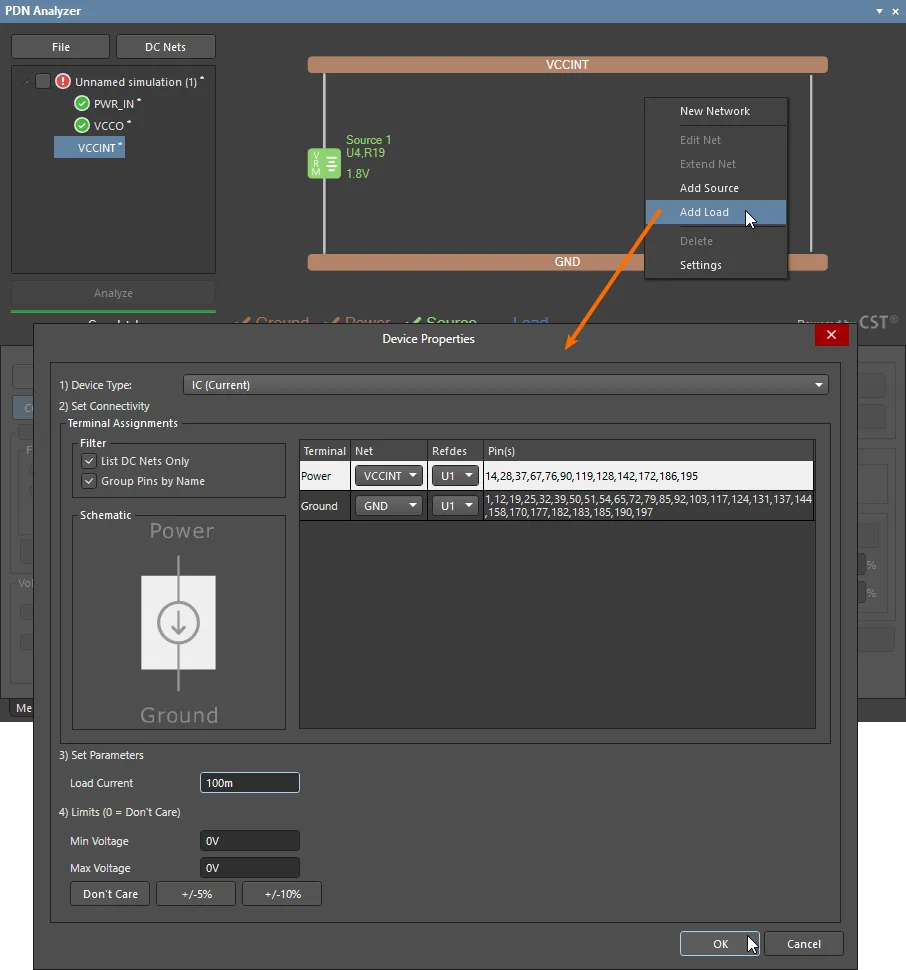

Add Load – Device Properties ダイアログを使用して、指定した電源/グランドのネットペア間に Resistor、電流シンク、または Voltage Regulator Model (VRM) の負荷デバイスを追加します。このダイアログは既存の Load 要素をダブルクリックしても利用できます。

-

Delete – シミュレーションから電源ネットを削除します。ネットワークには最低限、電源ネット1つとグランドネット1つが必要である点に注意してください。

-

Settings – 上記で説明した Settings ダイアログを開きます。

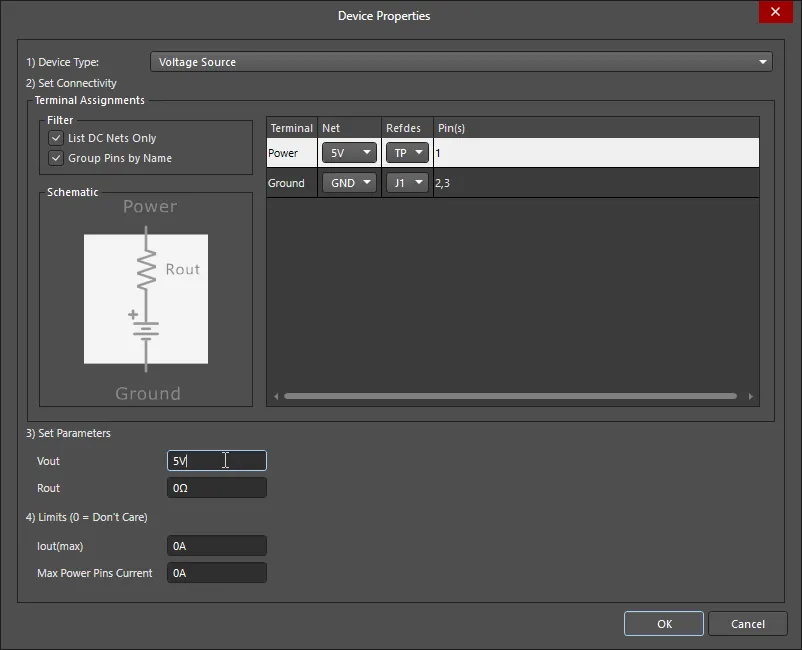

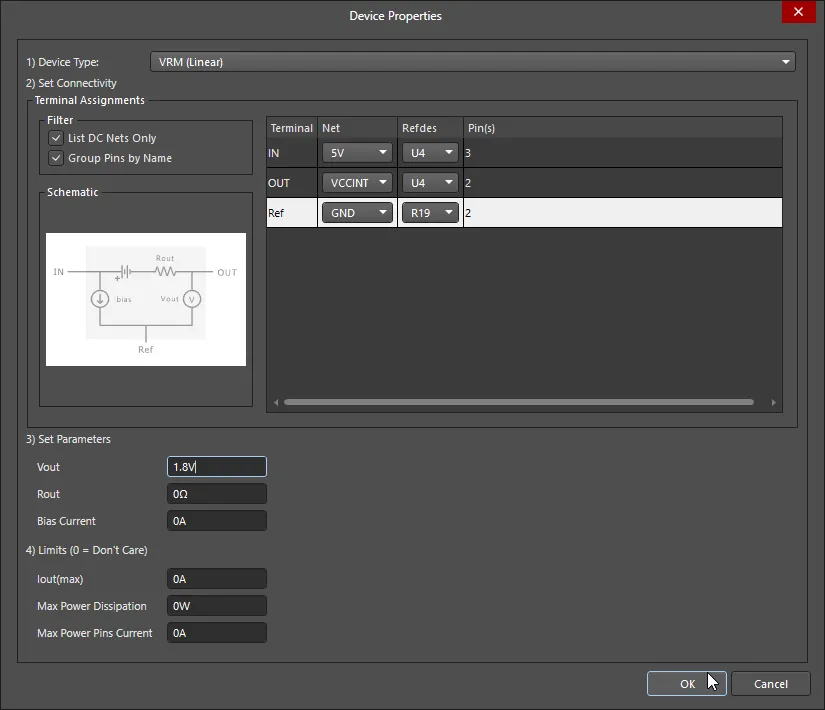

既存のデバイス要素(Load、Source など)を追加または編集する際に使用する Device Properties ダイアログでは、デバイスタイプ、接続性、パラメータを指定するための設定が提供されます。

ダイアログで利用可能な設定オプションは、配置/編集するデバイス要素の機能に依存しますが、一般的には次のとおりです。

-

Device Type – ドロップダウンメニューを使用してデバイスの種類を選択します。利用可能な選択肢は要素タイプ(Source、Load など)によって決まります。

-

Set Connectivity – リストの Net および Refdes のドロップダウンオプションを使用して、利用可能なネットおよびノードからデバイスの Terminal 接続を選択します。端子は Schematic シミュレーションモデルのグラフィックに示されているとおりです。ネット接続 Pins は、指定したノードのネット接続性に基づいて自動的に割り当てられます。

-

Filter – List DC Nets Only オプションを使用して利用可能な Net オプションを制限し、Group Pins by Name オプションを使用して相互接続されたデバイスピンを結合します。後者を無効にすると、Pins フィールドをクリックして表示される Select チェックボックスを使い、必要に応じて個々のピンを選択/選択解除できます。詳細は Working with Loads の LCD 例を参照してください。

-

Set Parameters – 利用可能なパラメータオプションは配置(または編集)するデバイスの種類に依存しますが、一般的には、Voltage Source の出力電圧と内部抵抗、Current sink の負荷電流、Resistor load の抵抗値など、基本特性を定義します。

-

Limits – シミュレーション実行時に Violation をトリガーする、デバイスの Voltage/Current/Power の制限値です。Violation は、該当要素のグラフィックの周囲に赤い破線の枠として表示され、ネットワーク名に関連付けられた赤いアイコンでも示されます。例として Current Density Limit Violations または Other Violations を参照してください。

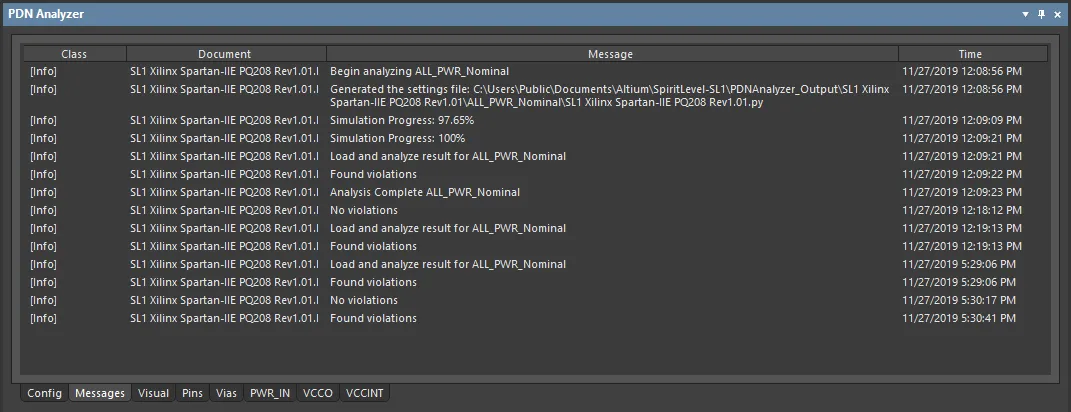

Messages タブ

Messages タブには、直近に実行した PDN 解析のシミュレーションイベントが時系列で一覧表示され、発生した Violation も含まれます。シミュレーション実行が失敗した場合は、問題を要約したイベントエントリがリストに含まれます。シミュレーション実行の詳細については、設定の Explore オプションから利用できる PDN_Analyser.log ファイルを参照してください。

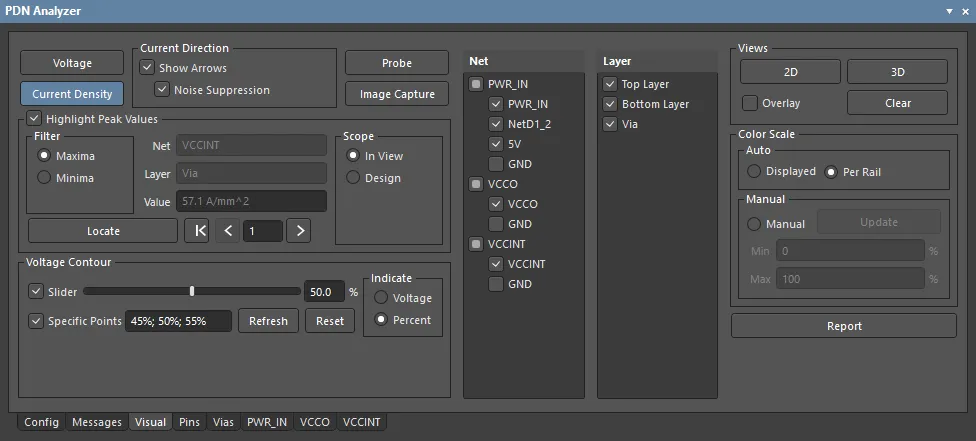

Visual タブ

PDN Analyzer インターフェースの Visual タブでは、電源ネットワーク解析データを PCB Editor でどのように表示するかを高いレベルで制御できます。PCB レイアウトのレンダリングに含める情報の種類、結果データのスケーリング、注目点をどのように(または表示するかどうか)強調表示するか、そしてエクスポートする情報を指定できます。PCB Editor でレンダリングされるレイアウトは、PDN Analyzer の Configuration ネットワーク階層で現在選択されている電源ネットワークに適用されます。

PCB レイアウト表示の設定を行う際は、Visual タブのデフォルト設定を出発点として使用してください。デフォルトでは、2D モードで全電源レールネットにわたる色分けされた電圧プロファイルを表示するよう設定されています。純粋な解析結果を表示するには Overlay オプションの選択を解除します。Visual タブで行った設定変更は、即座に PCB のレンダリングに反映されます。

Visual タブのオプションには次が含まれます。

-

Voltage –

ボタンを選択して、有効なすべてのネットにわたる電圧プロファイルを表示します。スケールはボルト単位、または全体のパーセンテージ範囲(Color Scale 参照)です。

ボタンを選択して、有効なすべてのネットにわたる電圧プロファイルを表示します。スケールはボルト単位、または全体のパーセンテージ範囲(Color Scale 参照)です。

-

Current Density –

ボタンを選択して、有効なすべてのネットにわたる電流密度プロファイルを表示します。スケールは面積あたりのアンペア、または全体のパーセンテージ範囲(Color Scale 参照)です。

ボタンを選択して、有効なすべてのネットにわたる電流密度プロファイルを表示します。スケールは面積あたりのアンペア、または全体のパーセンテージ範囲(Color Scale 参照)です。

-

Current Direction – Show Arrows オプションをチェックして、レンダリングされた PCB レイアウト上に電流方向/分布を示す矢印を重ねて表示します。Noise Suppression オプションを選択すると、データ平滑化が適用され、より見やすい表示になります。

-

Probe –

ボタンを選択して Probe ダイアログを開きます。ここでは、レンダリングされたレイアウト内の2つのデータ位置を対話的に選択し、数値を比較できます。詳細は Data Probe を参照してください。

ボタンを選択して Probe ダイアログを開きます。ここでは、レンダリングされたレイアウト内の2つのデータ位置を対話的に選択し、数値を比較できます。詳細は Data Probe を参照してください。

-

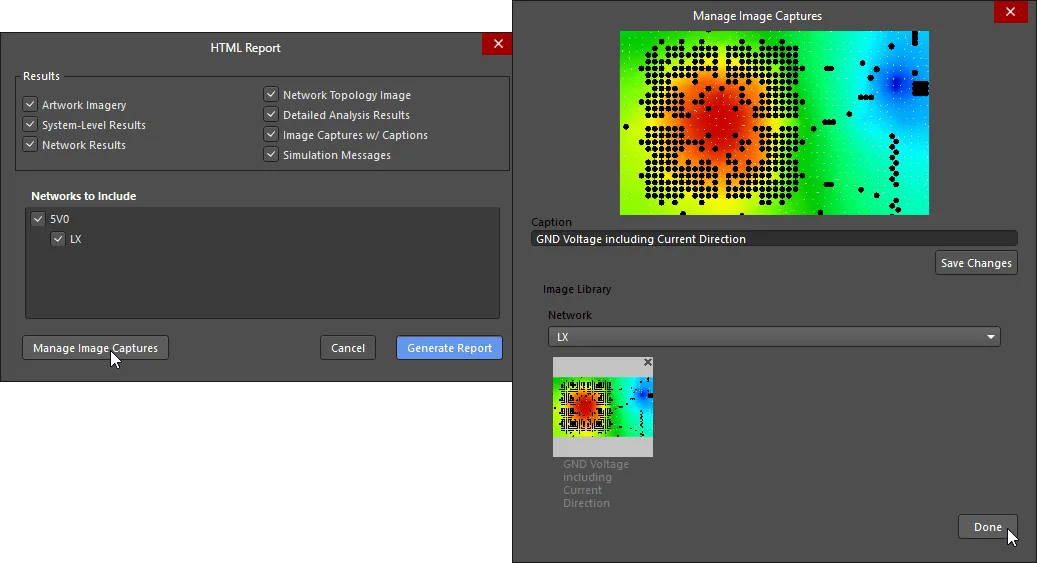

Image Capture –

ボタンを選択して Manage Image Capture ダイアログを開きます。ここで現在の PCB レンダリングをキャプチャして保存できます。画像は、後で Report に含められるよう、プロジェクトシミュレーションの

ボタンを選択して Manage Image Capture ダイアログを開きます。ここで現在の PCB レンダリングをキャプチャして保存できます。画像は、後で Report に含められるよう、プロジェクトシミュレーションの /HTMLReport/ImagesCache フォルダに保存されます。詳細は Analysis Report を参照してください。

-

Peak Values – Highlight Peak Values オプションを選択して、現在選択されているネットおよびレイヤー内の最大値または最小値(Filter オプションに従う)Value を視覚的にマーキングして強調表示します。Scope オプションで検出範囲を指定し、Locate ボタンでピーク値ポイントを視覚的に強調表示し、データポイント矢印(

)で隣接する値のシーケンスを順に移動できます。例は Locating Power Integrity issues を参照してください。

)で隣接する値のシーケンスを順に移動できます。例は Locating Power Integrity issues を参照してください。

-

Voltage Contour – Slider オプションを選択して、等高線上の電圧レベルを表す破線オーバーレイを有効にします。検出レベルはスライダー位置で設定され、関連する Indicate オプションにより電圧値またはパーセント値として決まります。Specific Points オプションを選択すると、示されたパーセンテージポイントそれぞれに電圧等高線を有効化します。

をクリックして Specific Point 値をデフォルトに戻し、

をクリックして Specific Point 値をデフォルトに戻し、 ボタンで有効な電圧等高線をすべて更新/強調表示します。詳細は Voltage Contour を参照してください。

ボタンで有効な電圧等高線をすべて更新/強調表示します。詳細は Voltage Contour を参照してください。

-

Net – レンダリングされた PCB 解析結果に表示したい Nets を選択します。ネットは利用可能な電源ネットワークごとにグループ化されています。

-

Layer – レンダリングされた PCB 解析結果に表示したい基板 Layers を選択します。3D 表示モードでは Vias も選択可能である点に注意してください。

-

Views –

および

および  ボタンを使用して、レンダリング表示を PCB Editor の 2D/3D モード間で切り替えます。Overlay オプションでエディタ標準の PCB 表示ビューを有効/無効にし、

ボタンを使用して、レンダリング表示を PCB Editor の 2D/3D モード間で切り替えます。Overlay オプションでエディタ標準の PCB 表示ビューを有効/無効にし、 ボタンでレンダリング表示を標準ビューに戻します。詳細は Display Control and Options を参照してください。

ボタンでレンダリング表示を標準ビューに戻します。詳細は Display Control and Options を参照してください。

-

Color Scale – Auto オプションを設定して、レンダリングされるカラーグラデーションを全体のパーセンテージ範囲(Per Rail)として表示するか、電圧スパンデータ全体に対応するグラデーション(Displayed)として表示するかを指定します。後者は単一ネットを表示する場合に最適です。Manual モードを選択すると、Min および Max フィールドに入力した電圧値に表示範囲を上書きします。詳細は Visual Rendering in the PCB Editor を参照してください。

-

Report –

ボタンをクリックして HTML Report ダイアログを開き、HTML ベースの PDN Analysis レポートを設定・生成します。詳細は Analysis Report を参照してください。

ボタンをクリックして HTML Report ダイアログを開き、HTML ベースの PDN Analysis レポートを設定・生成します。詳細は Analysis Report を参照してください。

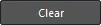

Pins タブ

Pins タブには、設定済みの電源ネットワークに接続されている設計内の全コンポーネントピンのリストが表示されます。各コンポーネントピンのエントリには、ピン番号、接続ネット、そして前回のシミュレーション実行による関連 Voltage および Current の結果値が含まれます。列ヘッダーをクリックするとその名前でリストを並べ替えでき、もう一度クリックすると順序が反転します。

エントリをダブルクリックすると、PCB Editor でそのピンへクロスプローブします。レンダリングビューでピン(パッド)接続が見えない場合は、接続先の Layer および電源 Net が Configuration ペイン/タブで有効になっていることを確認してください。

Pins タブのリスト(Component reference で並べ替え)と、— 画像上にカーソルを置くと — ピン Current で並べ替え。

Pins タブのリスト(Component reference で並べ替え)と、— 画像上にカーソルを置くと — ピン Current で並べ替え。

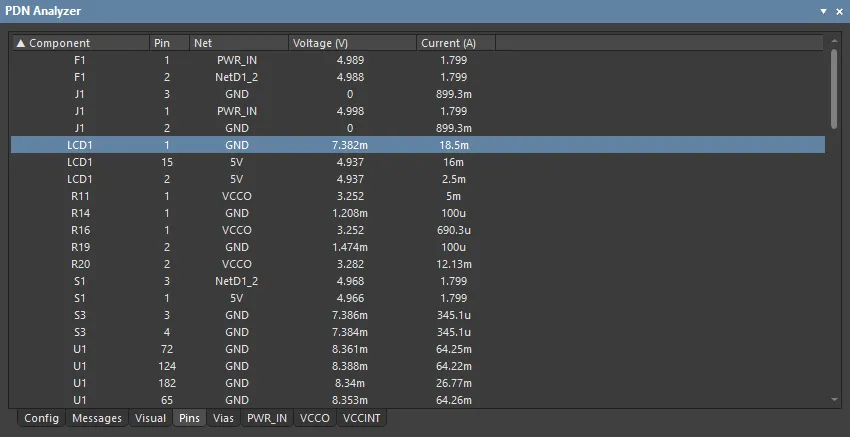

Vias タブ

Vias タブには、設定済みの電源ネットワークに接続されている設計内の全 PCB ビアのリストが表示されます。各ビアのエントリには、接続ネット、位置座標、レイヤーペア、そして前回のシミュレーション実行による端点間の関連 Voltage, Current および Current Density の結果値が含まれます。列ヘッダーをクリックするとその名前でリストを並べ替えでき、もう一度クリックすると順序が反転します。

エントリをダブルクリックすると、PCB Editor でそのビアへクロスプローブします。レンダリングビューでビアが見えない場合は、(3D ビューで利用可能な)Layer リストで Via がチェックされていること、また接続先の電源 Net が Configuration ペイン/タブで有効になっていることを確認してください。

Vias タブのリスト(Net connection で並べ替え)と、— 画像上にカーソルを置くと — Current Density で並べ替え。

Vias タブのリスト(Net connection で並べ替え)と、— 画像上にカーソルを置くと — Current Density で並べ替え。

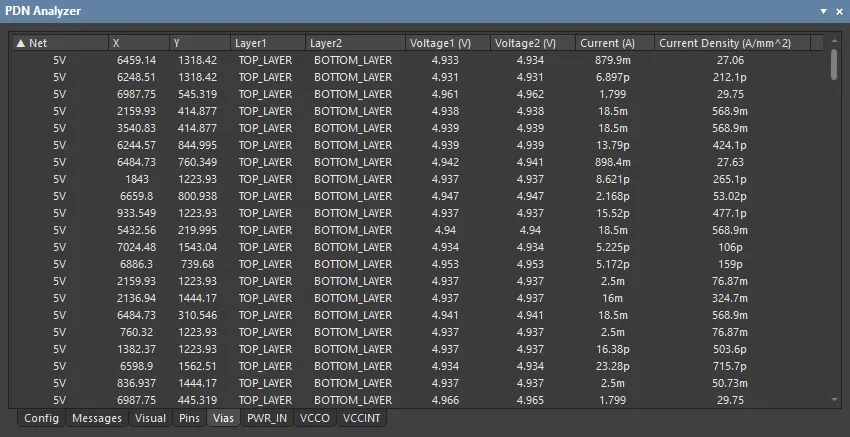

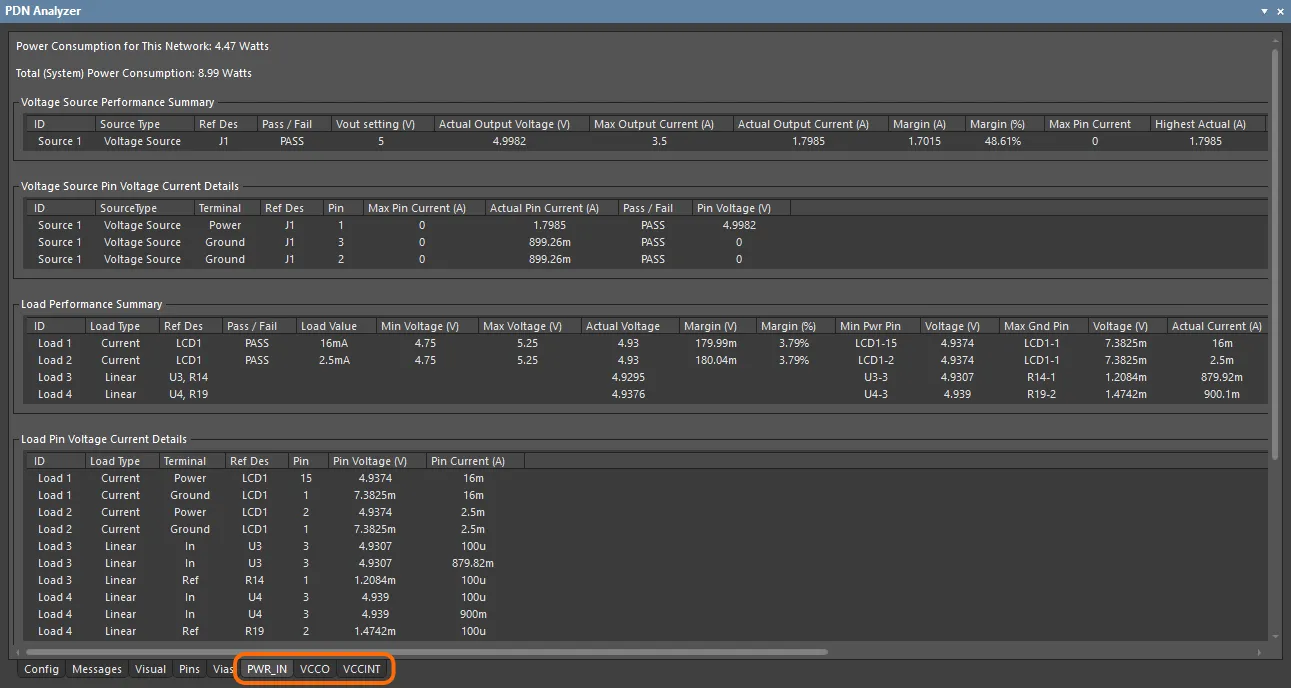

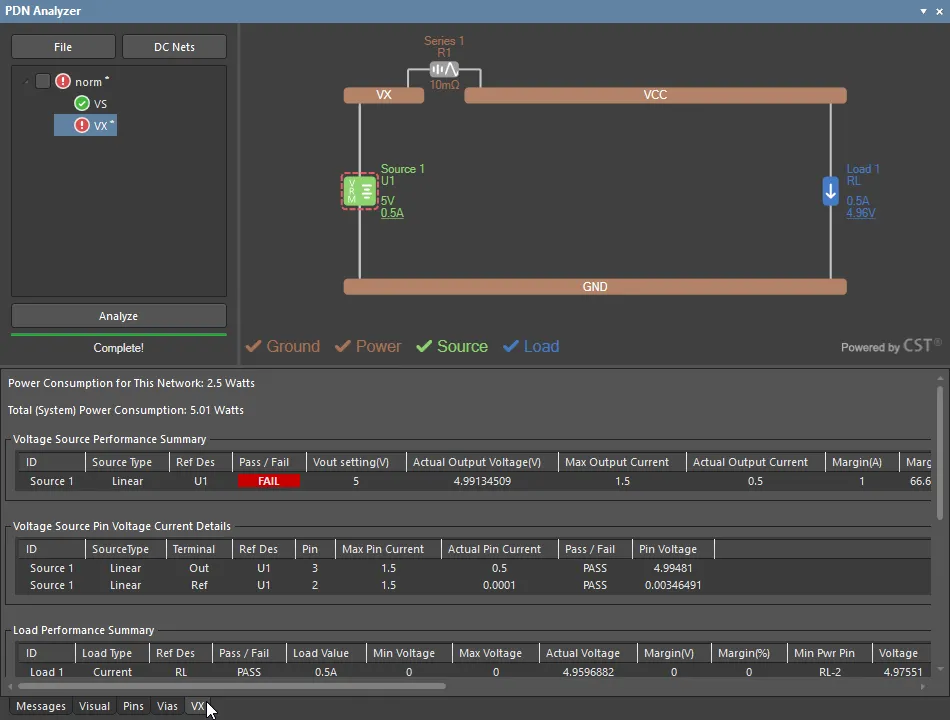

Power Network タブ

タブ表示は、シミュレーション構成内で利用可能な各電源ネットワークごとに用意されています。表示されるネットワークタブは、Configuration ペイン/タブでの電源ネットワーク選択によって決まります。ネットワーク名が付いた電源ネットワークタブには、その電源ネットワークに適用される、グループ化されたシミュレーション結果と算出データの包括的な一覧が表示されます。ネットワークの消費電力サマリーも含まれます。

一覧内のデータグループは、電源ネットワーク内のデバイス(ソース、負荷、直列要素)に適用され、各デバイスについて Performance Summary と Pin Voltage/Current Details のデータエントリが含まれます。デバイスの詳細に加えて、データグループには主要な電圧・電流値が示され、Performance summary の場合は、Device Properties ダイアログで指定されたデバイス限界に関連する算出済み安全マージンも提示されます。

DC Net Identification

PDN Analyzer をPCB設計で最初に開くと、一般的な電源ネットワークの命名規則に基づき、設計のネットデータからすべてのDC電源ネットワークを識別しようとします。 すべての候補電源ネットが識別されていない場合は、適切な Qualifiers フィルターオプションの選択を解除するか、すべてのネットを表示するには Enable all nets for filtering オプションを選択してください。

Select チェックボックスを使用して、PDNA analyzer で利用可能にする電源ネットを選択し、対応する Nominal Voltage フィールドに適切な電圧レベルを入力します。Add Selected ボタンをクリックして Currently Identified DC Nets リストを生成し、これらのネットを識別済み電源ネットワークとして確定します。

ダイアログ内のリストされたネットエントリをダブルクリックすると、PCBレイアウト上のそのネットへクロスプローブされる点に注意してください。

追加のネットは、アナライザーGUIで DC Nets ボタンを選択することで、PDN解析セットアップ中に識別して適用できます。

以下の解析例は、PDN Analyzer の主要な機能と特長を示すために含まれています。各例は、関心の焦点に応じてネットワークの電源インテグリティを異なる観点で評価するために使用できる、多数のパラメータ構成のうちの1つのみを示しています。正常に完了した解析は、PDNA構成ファイル(*.pdna)として保存し、いつでも再読み込みできます。— File » Save As および File » Open(デフォルトではプロジェクトの PDNAnalyzer_Config フォルダー内)

Example 1

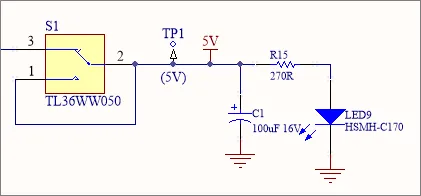

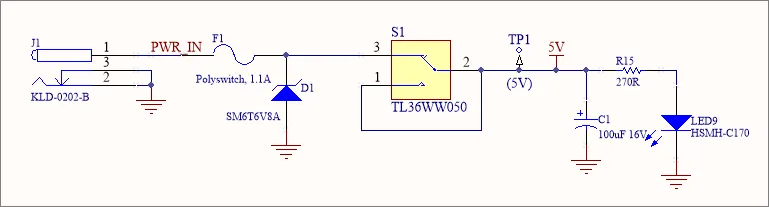

この例では、単純な電源ネットとその電流負荷を用いて、電源インテグリティ・シミュレーションをセットアップする基本を示します。SpiritLevel-SL1 参照プロジェクトにおいて、設計のLCDディスプレイを負荷として接続した状態で、5V電源レールの分配とそのGNDリターンパスを評価するように構成されています。このケースでは、5V 電源レールは単純な電圧源として扱われ、(スイッチ S1 経由などの)接続ネットワークは含めません。

このPDNシミュレーション例の事前条件は次のとおりです。

-

Spirit Level PCBプロジェクトが Altium Designer で開かれている

-

PDN Analyzer アプリケーションがアクティブである(Tools » PDN Analyzer)

-

PCB設計のDC Netsが PDN Analyzer DC Net Identification ダイアログで識別済みである(outlined above)。

電源ネットとGNDネットを指定して解析プロセスを開始します。GUIのネットワークグラフィック内にある <Power Net> と <Ground Net> 要素をダブルクリックして Choose Net ダイアログを開くと、識別済みの電源ネットから選択できます。

必要に応じて、ダイアログの修飾子/フィルターオプションでリスト表示されるネットを絞り込む/拡張するか、メイン画面に戻って  ボタンを選択し、DC power nets を再識別します。

ボタンを選択し、DC power nets を再識別します。

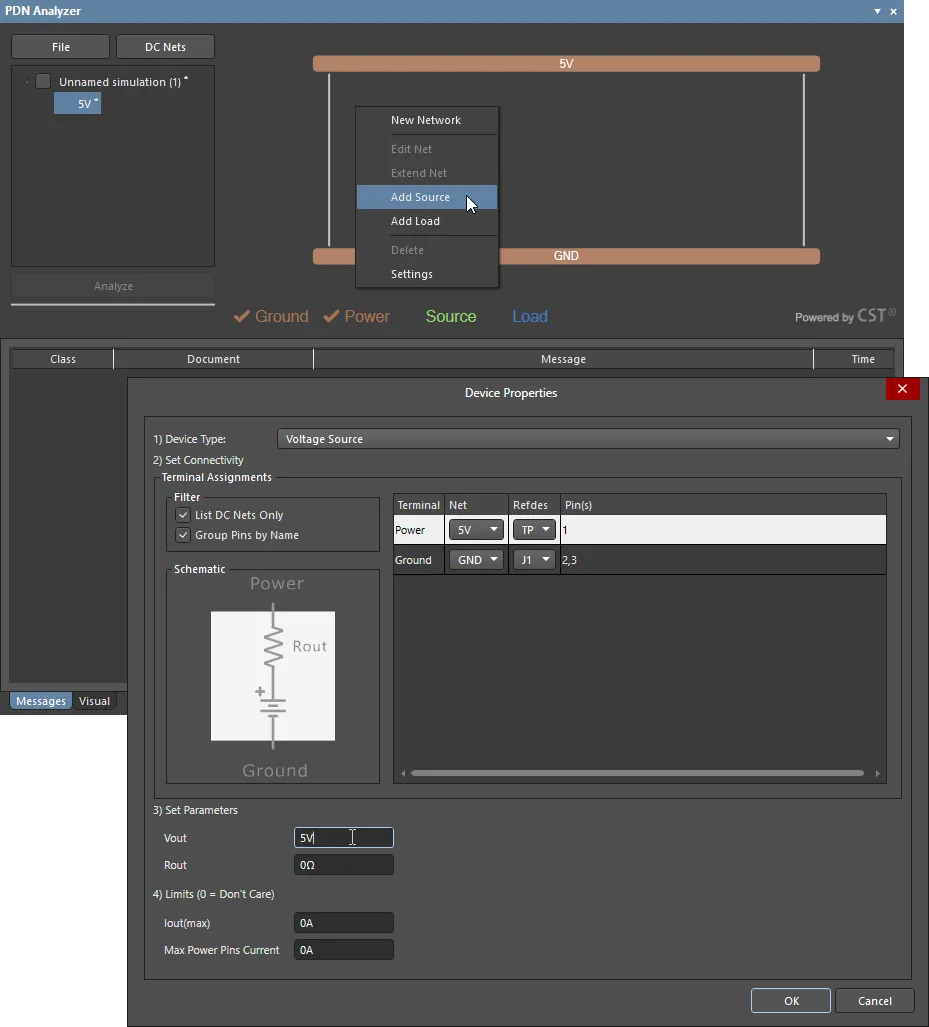

これで、指定した電源ネットワークとGNDネットワークの間に Source または Load 要素を追加できます。— Ground と Power のステータスインジケータがチェック状態(✔)に変わる点に注意してください。ネットワークグラフィックの作業領域で右クリックし、コンテキストメニューから Add Source(または Add Load)を選択して Device Properties ダイアログを開きます。ダイアログに示される手順は次のとおりです。

-

ネットワークに電源 Source(この場合は単純な電圧源)を追加するには、ダイアログの Device Type ドロップダウンメニューから Voltage Source オプションを選択します。

-

ソース接続の一覧では、PDNA が電源ネットワークパラメータに基づいて正しいネット接続オプション(

5V と GND ネット間)を選択しようとします。Refdes ドロップダウンメニューのオプションを使用して、ソース電圧のコンポーネント接続点を指定します。この例では、ソース電圧点を TP1、GNDリターンを設計のDC入力ソケット J1(ピン 2 と 3)として指定します。

-

ダイアログ下部では、ソースパラメータで電圧源シミュレーションモデルの属性を指定します。ここではソース電圧(Vout)を

5V に設定し、モデルの内部抵抗(Rout)はデフォルトの 0Ω 設定のままにします。

-

最後に、最大ソース電流およびピン電流(複数出力ピンを持つソースの場合)はデフォルト設定(

0A: Don't Care)のままにします。Limits を特定の電流値に設定すると、シミュレーション結果がその値を超えた場合にPDN解析が Violation をフラグします。

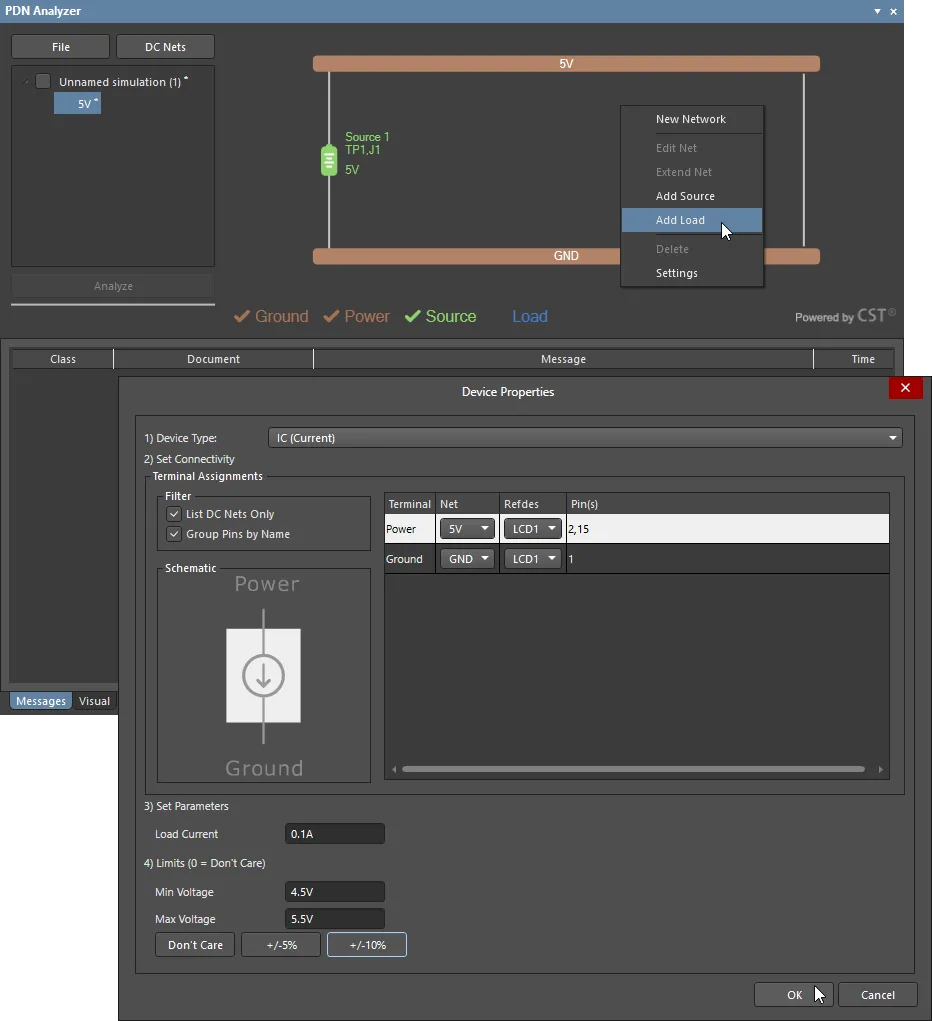

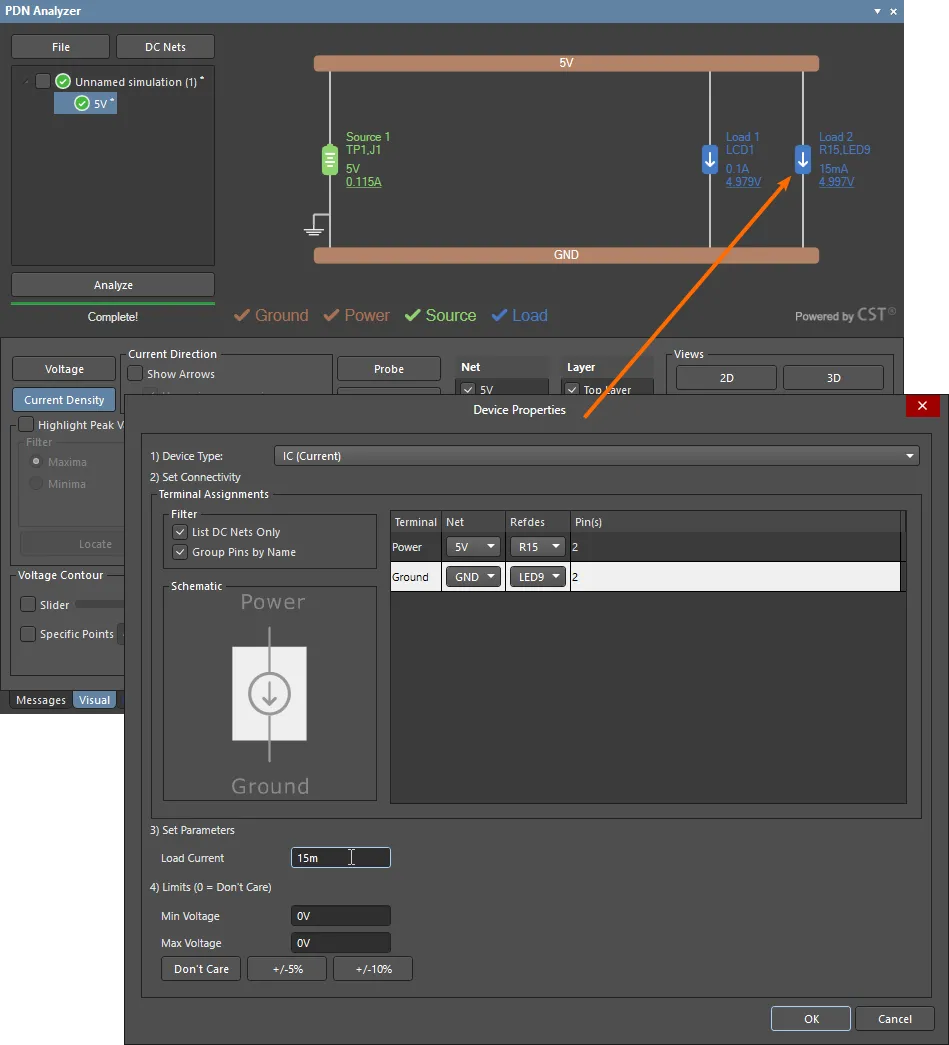

ネットワークに Source を追加したときと同じ手順で Load を追加し、Device Properties ダイアログでそのパラメータを指定します。

この例では、設計のLCDコンポーネントが5Vレールから引き込む電流を表すため、電流シンク負荷(Device Type: IC (Current))を追加します。なお、Device Type として Resistor を選択することで、純抵抗負荷オプションも利用できます。

負荷の接続先を LCD1 に設定し、5V電源から引き込む Load Current を指定します。— 単位の接頭辞(例:500m で 0.5A を表すなど)がサポートされている点に注意してください。電圧 Limits 設定は任意ですが、ここでは(関連ボタンを使用して) +/-10% に設定しています。これにより、負荷自身の電圧が4.5V未満(または5.5V超)に低下した場合、シミュレーション違反がトリガーされます。

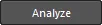

電源ネットワークが定義され、すべてのパラメータが指定されると(すべてのネットワーク要素が ✔ ステータスを持つ)、  ボタンを選択してPDN解析を実行できます。シミュレーションの進行状況は Messages タブのイベントストリームとして表示され、処理が完了できない場合はシミュレーション失敗の原因も示されます。

ボタンを選択してPDN解析を実行できます。シミュレーションの進行状況は Messages タブのイベントストリームとして表示され、処理が完了できない場合はシミュレーション失敗の原因も示されます。

解析を実行すると、現在のシミュレーション構成(指定したネット、ソース/負荷など、および関連パラメータ)が、解析結果データ(File » Explore; PDNAnalyzer_Ouput フォルダー参照)とともに保存されます。この構成セットアップは、シミュレーション名を右クリックしてコンテキストメニューから Revert を選択することで、現在のシミュレーションに対していつでも復元できます。

PDN解析の即時結果はネットワークグラフィックで確認でき、(該当する場合)算出された負荷/ソースの電圧・電流レベル、およびパラメータ Violation を引き起こしたネットワーク区間のハイライトが含まれます。Visual タブがフォーカスされアクティブになっている点に注意してください。

ネットワーク内の任意の要素(Load、Source、または Series Element)にカーソルを合わせると、指定パラメータや解析結果などの追加情報を確認できます。

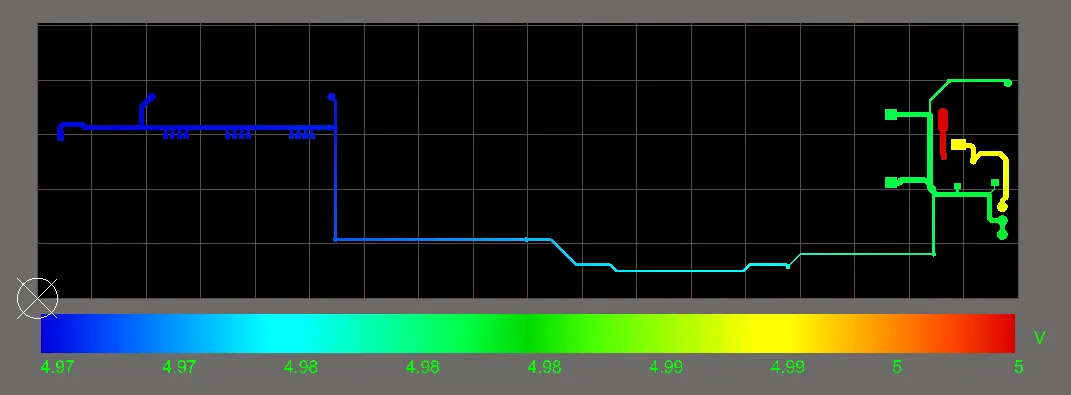

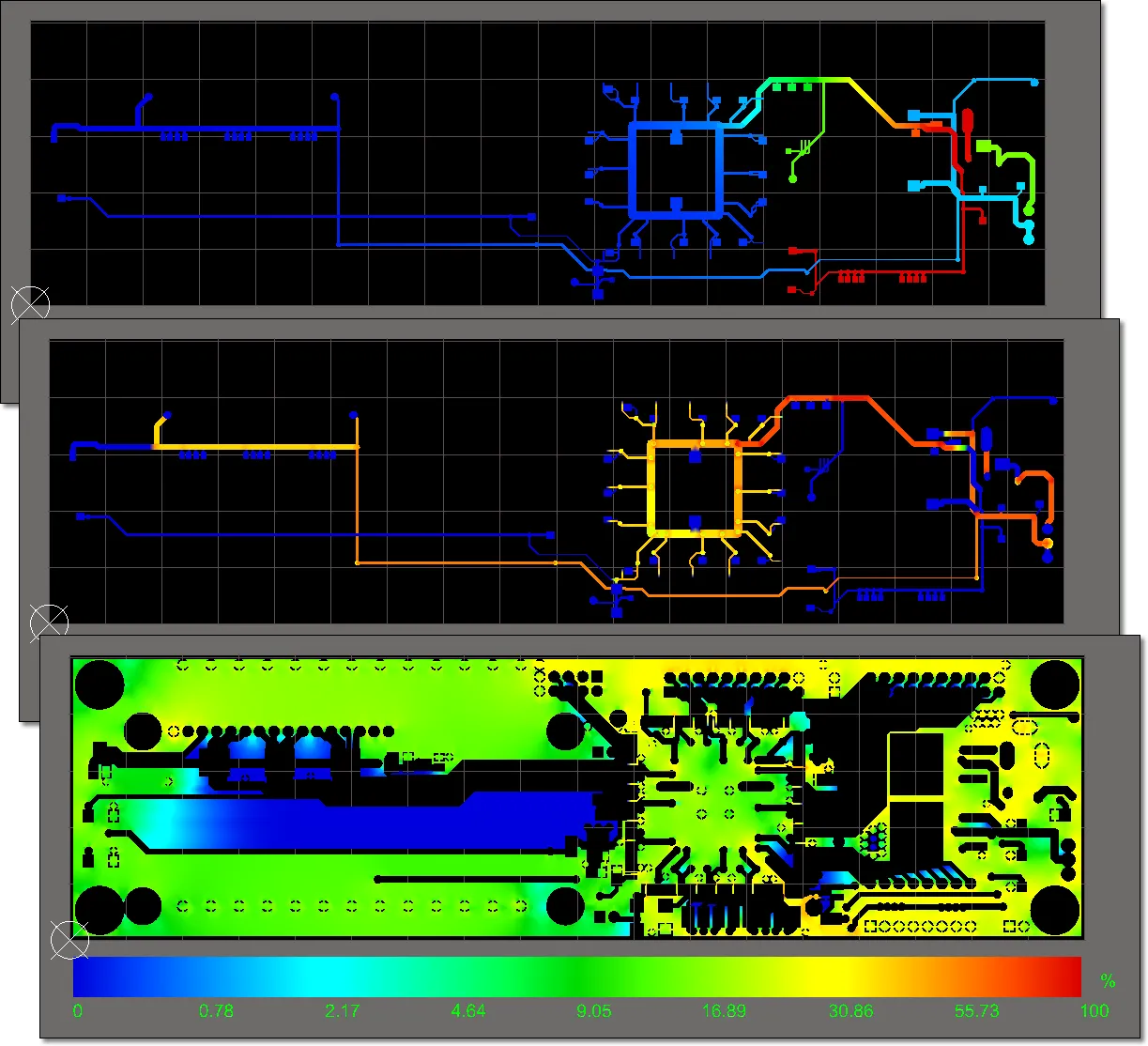

Visual Rendering in the PCB Editor

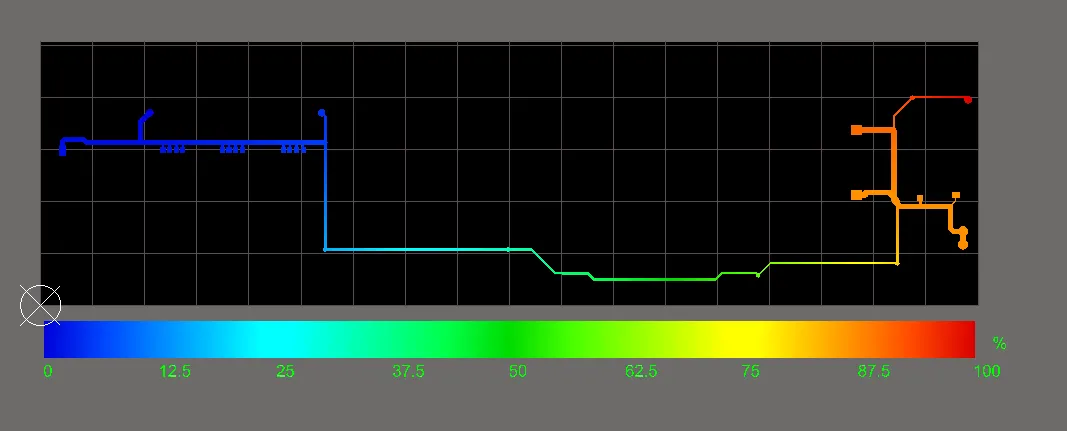

シミュレーション結果は、PDNA の Visual タブで利用可能な設定により制御され、Altium Designer PCBエディタ上でグラフィカルに表示できるようになります。 表示オプションを設定し、5V Net の Layers(Top と Bottom)の両方について Voltage を表示するようにします。— これは初期のデフォルト表示設定です。アナライザー結果はPCBエディタにレンダリングされ、既存のPCBグラフィックスオーバーレイを置き換えます。

選択したネットパスの電圧降下(この例では TP1 の5Vソースから LCD1 コンポーネントまで)は、ビュー下部に表示される電圧スケールに対応したカラーグラデーションでレンダリングされます。これは電圧パーセンテージ(Color Scale 配下の Per Rail オプション)として、または実際の電圧幅(Displayed オプション)として表示されます。

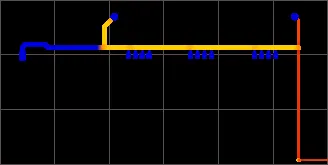

以下の画像では、基板上のネットワークパスに沿った色の遷移が全体の電圧降下を表しています。IR損失による最小レベル(0%: 青)は LCD1 コンポーネント側にあり、最大レベル(100%: 赤)は指定した電圧源ポイント(TP1)にあります。

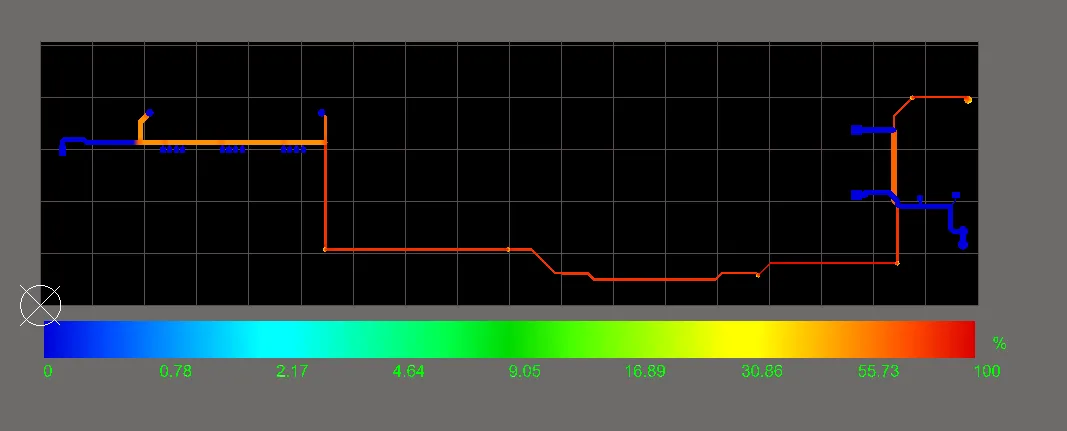

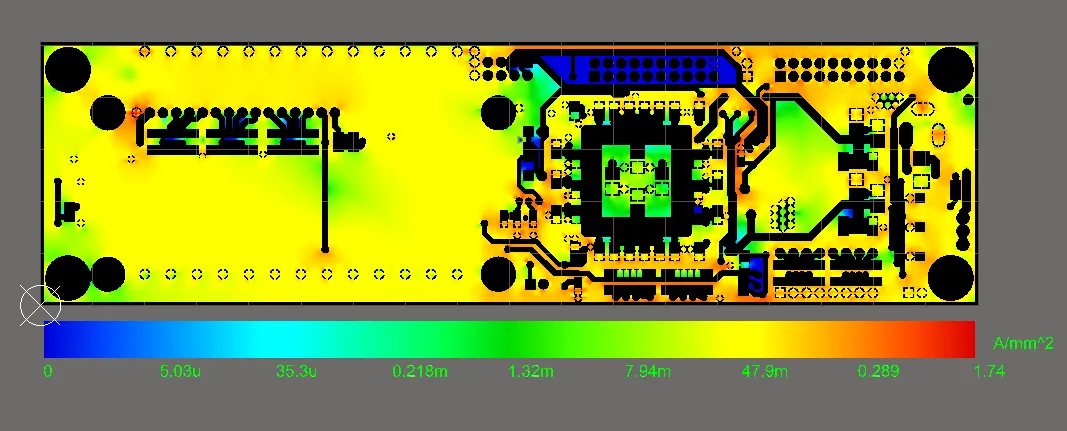

ネットワークの対応する電流解析を表示するには、Visual タブの Current Density オプションを選択します。ここでは、基板上のネットワークパスの色レベルが電流密度変動の割合に対応し、100%(赤)がネットワークパスレイアウトで算出された最大電流密度、0%(青)が最小(おそらく 0A/mm2)を示します。

なお、代替の電圧/電流スケールオプション(Displayed)は単一ネットワークの表示には直感的なスケール形式ですが、複数の電圧ネットワークを同時に表示する場合(この例の 5V and GND など、または設計内の複数電源ネットワークを解析した場合)には、有用な情報が限定されます。

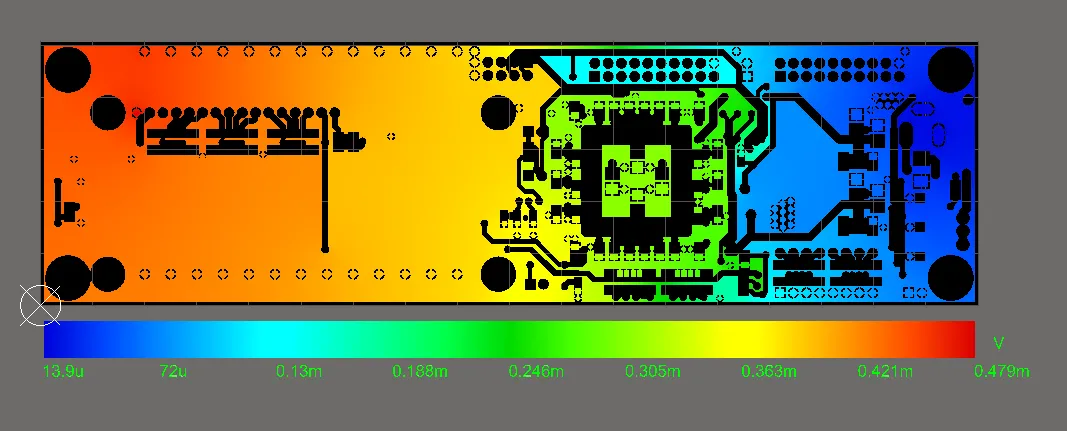

例のGNDリターンパスにおける電源インテグリティ結果を表示・解析するには、PDNA の Visual タブ配下の Net リストで5Vネットワークオプションの選択を解除し、次にGNDネットワークを選択します。GNDリターンパスは設計のTop層とBottom層の両方を経由しており、PDNA の Layer リストで各エントリを選択することで、PCBエディタ上で個別に表示できます。

以下の画像は、GNDネットのボトム層における電圧表示を示しており、Color ScaleスケールはDisplayedに設定されています。電圧降下が最も大きい箇所(赤:約0.5mV)はLCDのGNDピンにあり、電圧降下が最も小さい箇所(青:約0V)は電圧源のリターンポイント(J1)です。

PDNAのCurrent Densityオプションに切り替えると、最大電流の「ホットスポット」が赤で表示されます。最大電流密度レベル自体(1.74 A/mm2)は非常に低く、許容範囲内に十分収まっています。

表示の制御とオプション

PDN Analyzerには、解析結果をAltium DesignerのPCBエディタ上でどのようにグラフィカル表示するかを決定する、複数の対話的な表示オプションがあります。表示Color Scaleのオプションに加えて、グラフィックスは2Dと3Dのレンダリングを切り替えられ、後者はビアや層間を通した解析結果の把握に有用な洞察を提供します。

また、エディタ表示から解析結果をClearするオプションも用意されており、これによりグラフィック表示は自動的に標準の基板レイアウトへ戻ります。対照的に、ビューのOverlayオプションを有効にすると、基板レイアウト表示が有効になり、現在表示中の解析結果とともに基板レイアウトもレンダリングされます。このオプションは、解析結果で注目しているポイントが基板レイアウト上のどこに位置するかを確認するのに特に便利です。

負荷の扱い

必要に応じてネットワークに追加の負荷を加え、電源解析を再実行して結果を評価できます。たとえば設計の電源LEDに起因する小さな負荷電流(例:15mA)を追加するには、直列抵抗(R15)を5Vレール接続として選択し、LEDピンをGND接続として選択します。

PDN Analyzerでは、負荷に対するデバイスのピン接続を指定することもでき、これにより、異なるピンから異なる電流を消費する単一コンポーネントに対して複数の負荷モデルを作成できます。

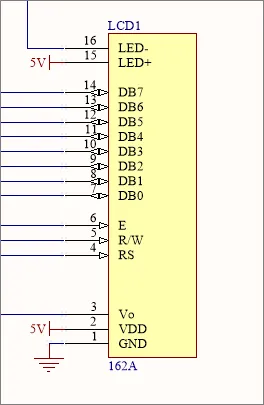

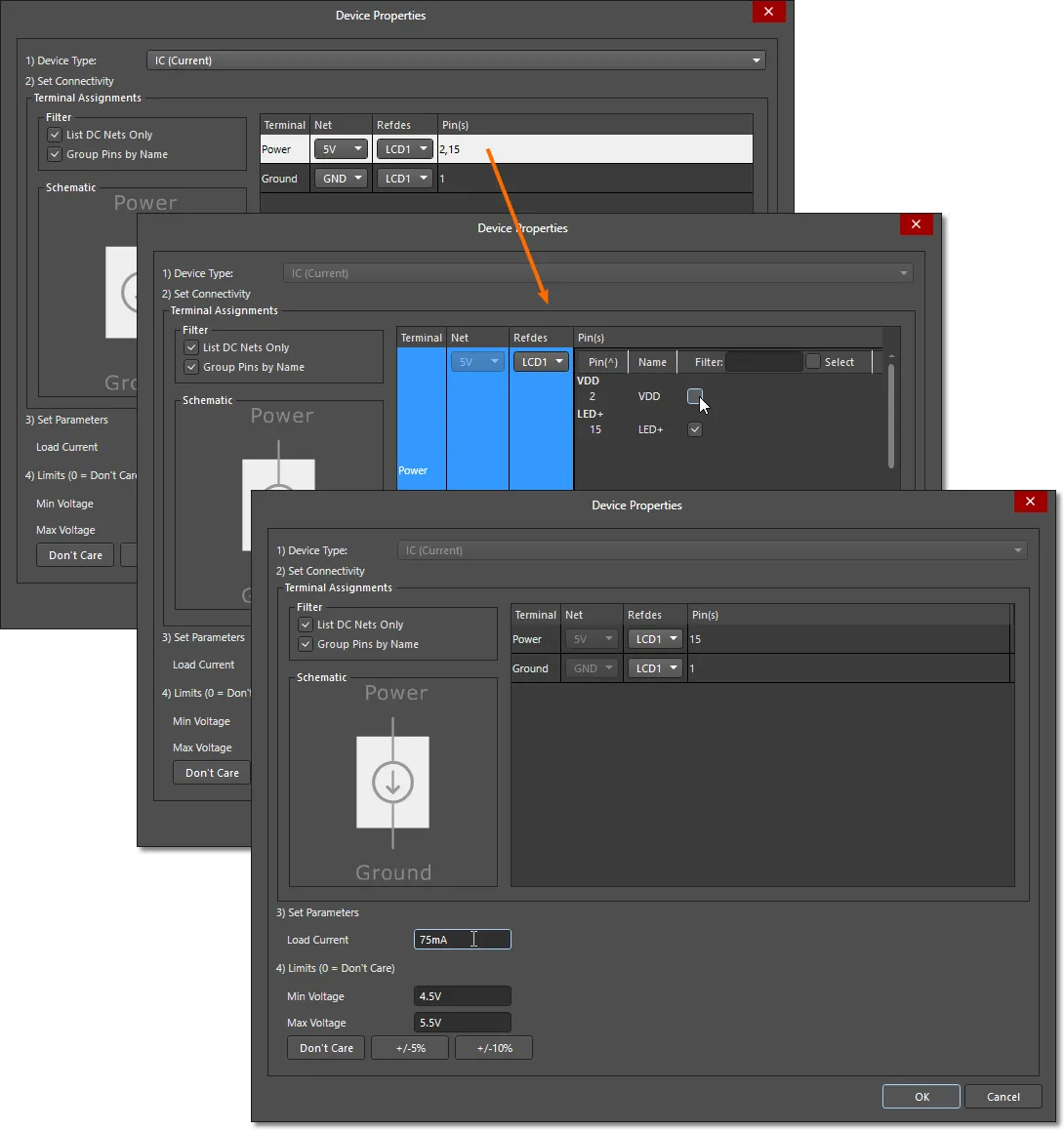

例のプロジェクトにあるLCDデバイスはこの状況を示しており、ピン15の5V接続(LED+)は表示バックライトに給電し、ピン2の5V接続(VDD)は内部ロジックに給電します。実際には、ピン15はピン2よりも大幅に大きな電流を消費します。

以前に追加した単一のPDNA負荷モデルとしては、LCD1の両ピンが(デフォルトで)5V負荷接続として指定され、PDN解析ではLCD1の負荷電流がこれらのピンに均等に分配されました。電源解析の精度を高めるため、LCD1コンポーネントはtwo個の負荷モデル(各5Vピンとそれに対応する負荷電流ごとに1つ)として表現できます。この変更は、既存のLCD1負荷モデルのピンパラメータを編集し、その後、分離したピン用に別の負荷を追加することで行えます。

ネットワークグラフィック内のアイコンをダブルクリックして既存のLCD1負荷モデルを開き、Device Propertiesダイアログを表示します。次に、5V電源ネットのエントリにあるPins(s)フィールドをダブルクリックします。表示されるピン編集モードでは、その負荷に対して個別のデバイスピンを選択できます。ピン2の選択を解除して、負荷をピン15のみ(LED+)に再構成し、LCDバックライト電流を表すようにLoad Currentパラメータを(例:75mAに)調整します。

次に、LCD1に対して別の5Vネットワーク負荷を作成し、ピン2を有効(ピン15は無効)に設定して、VDD負荷を表します。これは適切に低いLoad Currentに設定でき、たとえば20mAです。

その後、5V電源ネットワークを再解析することで、ネットワーク経路を通るLCD1負荷のより正確な表現を得られます。

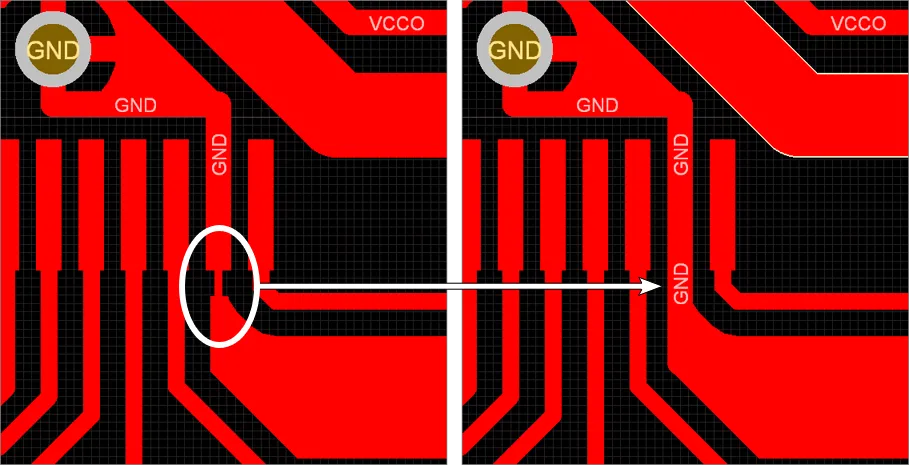

負荷電流分布の違いは、元の負荷構成と更新後の負荷構成でLCD1電源ネットワーク配線の電流密度を比較すると確認できます。以下の電流密度解析画像は、左が元の単一負荷LCD1モデルの結果、右が更新後の複数負荷の結果を示しています。

ピン2(左側寄りのLCDパッド)およびピン15へ供給する配線の電流密度に注目してください。更新後のバージョンでは、LCD電流の大部分がピン15(右側寄りのLCDパッド)へ流れることが正しく示され、左画像のように2つのピンへ均等に分配されることはありません。

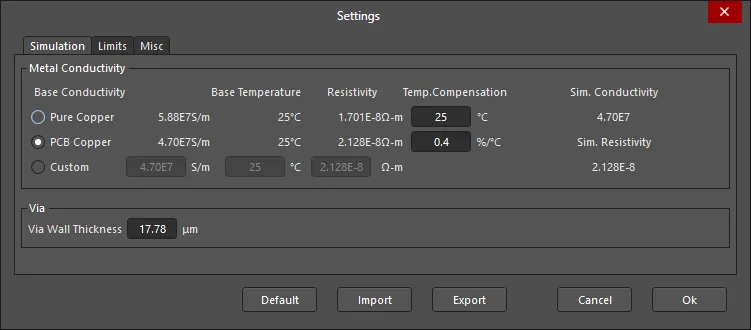

シミュレーション設定

解析結果、特に基板形状におけるIR損失の度合いは、基板銅の導電率およびビア壁厚の仕様にも依存します。これらの設定を表示・編集するには、SettingsダイアログのSimulationタブを選択します。ダイアログにアクセスするには、現在の解析名を右クリックし、コンテキストメニューからSettingsを選択します。

金属の導電率

ダイアログのMetal Conductivityセクションでは、設計で使用される金属の導電率(抵抗率の逆数;1/R)の詳細と設定が提供されます。ベース導電率(または抵抗率)、温度係数、温度をダイアログで選択または変更し、設計の基板構造特性を反映できます。

-

Pure Copper – 銅は通常、

25°Cにおいて導電率5.88e7S/m、導電率の温度係数 0.4%/°Cであると仮定されます。この正の温度係数は、ダイアログのTemp. Compensation設定を25°Cから125°Cへ(差分100°C)上げると、シミュレーション導電率が40%低下し、たとえば3.53e7S/mになることを意味します。

-

PCB Copper – これはシミュレーションのデフォルト設定で、業界文献で報告されている、PCBの電解銅(ED)に代表的な導電率値を反映しています。これは

25°Cで4.7e7S/mと測定され、温度係数は0.4%/°Cです。

-

Custom – このオプションを選択して、シミュレーション用に特定の導電率または抵抗率の値を入力します。

表示されるSim Conductivityの数値は、すべてのパラメータを考慮した後の最終的な導電率値を表します。Sim Resistivityはその逆数です。

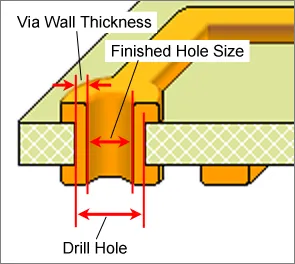

ビア

ダイアログのVia Wall Thickness値を設定して、設計シミュレーション解析におけるすべてのビアのビア壁金属の重量を指定します。

この設定は、薄い壁(めっき)のビアが持つ固有抵抗により、電源ネットワークのDC損失に顕著な影響を与える場合があります。しかし十分なサイズ/重量がある場合、ビアは設計のDC性能を阻害せず、接続する電源配線と同等の電流密度を示し、接続点間で有意な電圧損失も発生しません。ビアによる損失のDC解析例は、以下のセクションに示されています。

シミュレーションの観点では、ビア径と壁厚が、ビアとして表現される導電材料量を実質的に定義し、したがって抵抗/導電率を決定します。シミュレーションでは、ビア径は仕上がり穴径を表し、ビア壁厚によってビア径が増加すると仮定します。したがって:Finished Hole Diameter + (2 x Wall_Thickness) = Drill Diameter。

例2

この例では、相互接続する直列要素のパラメータを考慮しつつ、接続された一連のネットワークを全体として解析できるように実装する方法を示します。また、ネットワーク間の相互接続としても機能するVoltage Regulator Model (VRM)ソースの追加方法と、設計の電源ネットワークの完全な階層がどのように構築されるかの概要も示します。

この例は、SpiritLevel-SL1リファレンスプロジェクトのPWR_INから5Vへのネットワークをモデル化し、3.3V(VCCO)および1.8V(VCCINT)の両VRMを含めて、完全な電源ネットワーク構造を作成します。

このPDNシミュレーション例の事前条件は次のとおりです。

-

Spirit Level PCBプロジェクトがAltium Designerで開かれている

-

PDN Analyzerアプリケーションがアクティブである(Tools » PDN Analyzer)

-

PCB設計のDC NetsがPDN Analyzer DC Net Identificationダイアログで識別されている(上記で概説したとおり)。

新しいシミュレーションで入力電源ネット(PWR_IN)を指定して、例の電源ネットワーク構築を開始します(必要に応じてFile » New Simulationを選択)。プロジェクトの回路図に示されているとおり、PDNの<Power Net>パラメータはPWR_IN、<Ground Net>はGND、SourceはJ1です。

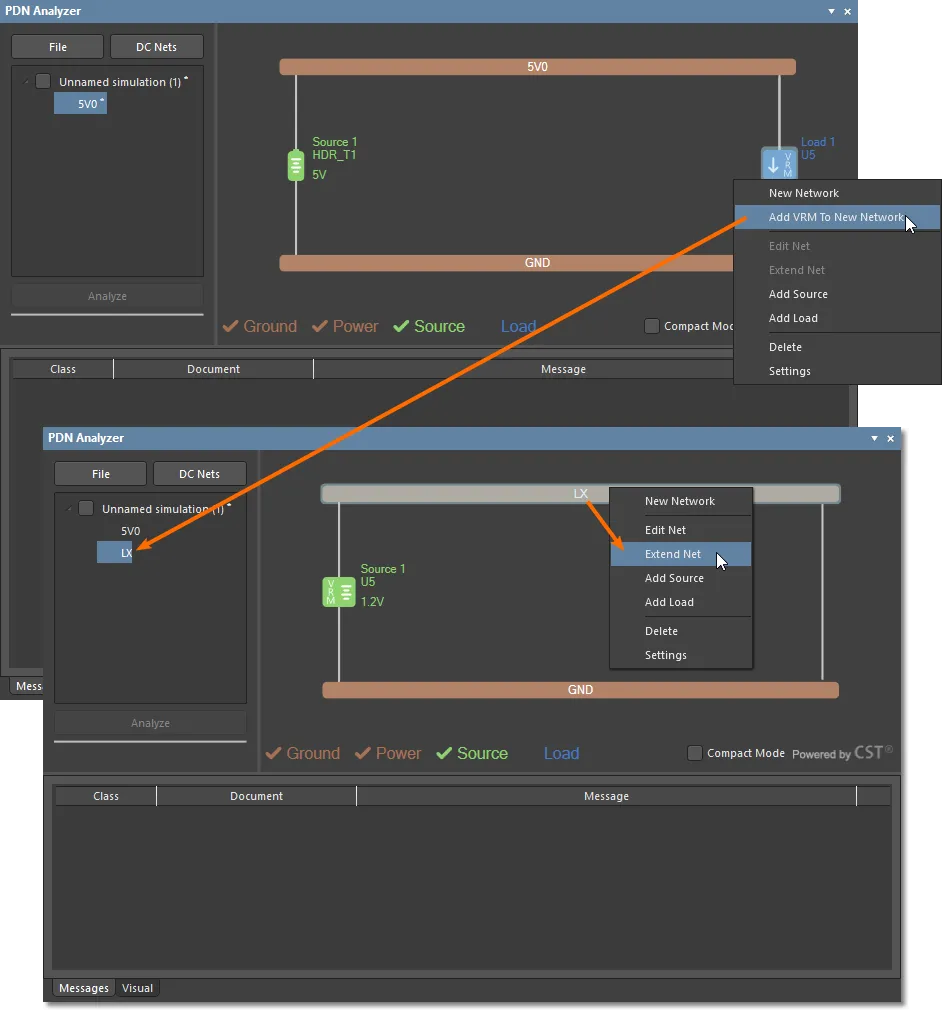

直列要素を介したネットワークの拡張

PWR_INネットワークから5Vネットワークまでの完全な電源経路をモデル化するには、直列のヒューズ(F1)およびスイッチ(S1)コンポーネントと、それらの間のネットを追加する必要があります。PDNAインターフェースでは、電源ネットワークを順次拡張することでこれらを追加します。各ネットの「拡張」は、汎用の直列要素モデルで接続されます。

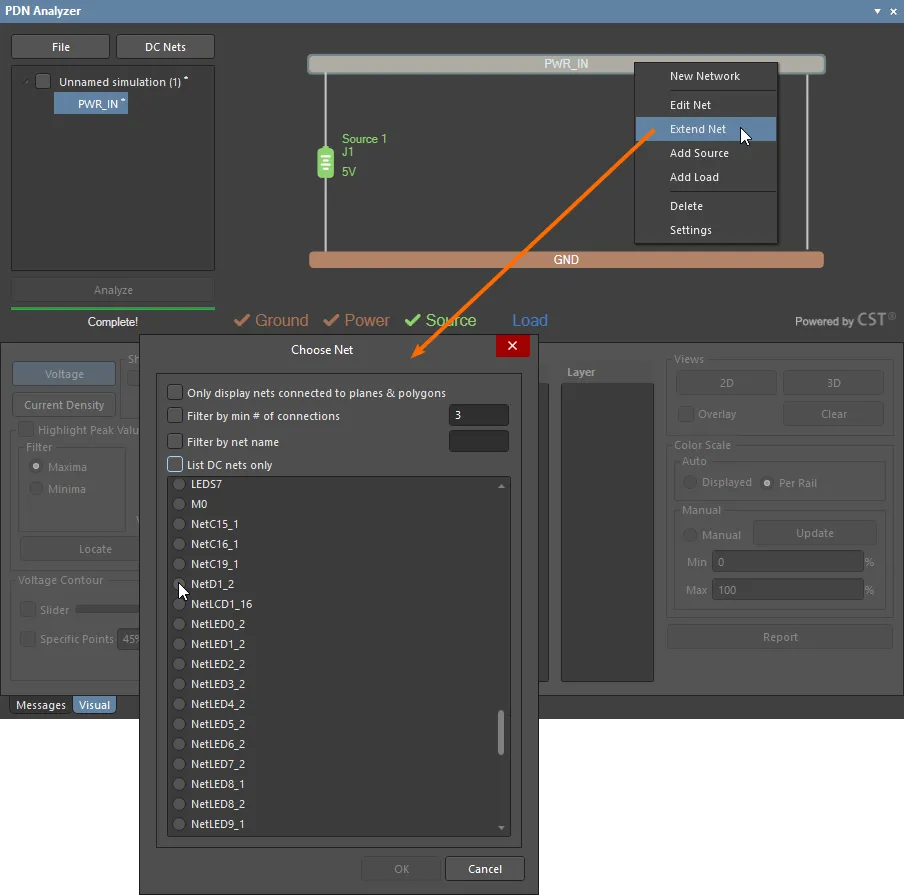

ネットを拡張するには、まず追加先のネットワーク内で右クリックし、コンテキストメニューからExtend Networkオプションを選択します。Choose Netダイアログで、PWR_INに直列要素で接続されているネットワークを選択します。この場合はNetD1_2で、F1とS1のピン3をブリッジするネットワークであり、ダイオードD1のピン2として識別されます。

このネットワークは初期のDC Net Identification段階で登録されていない可能性が高いため、Choose NetダイアログでList DC nets onlyオプションの選択を解除し、そのネットを選択可能にします。

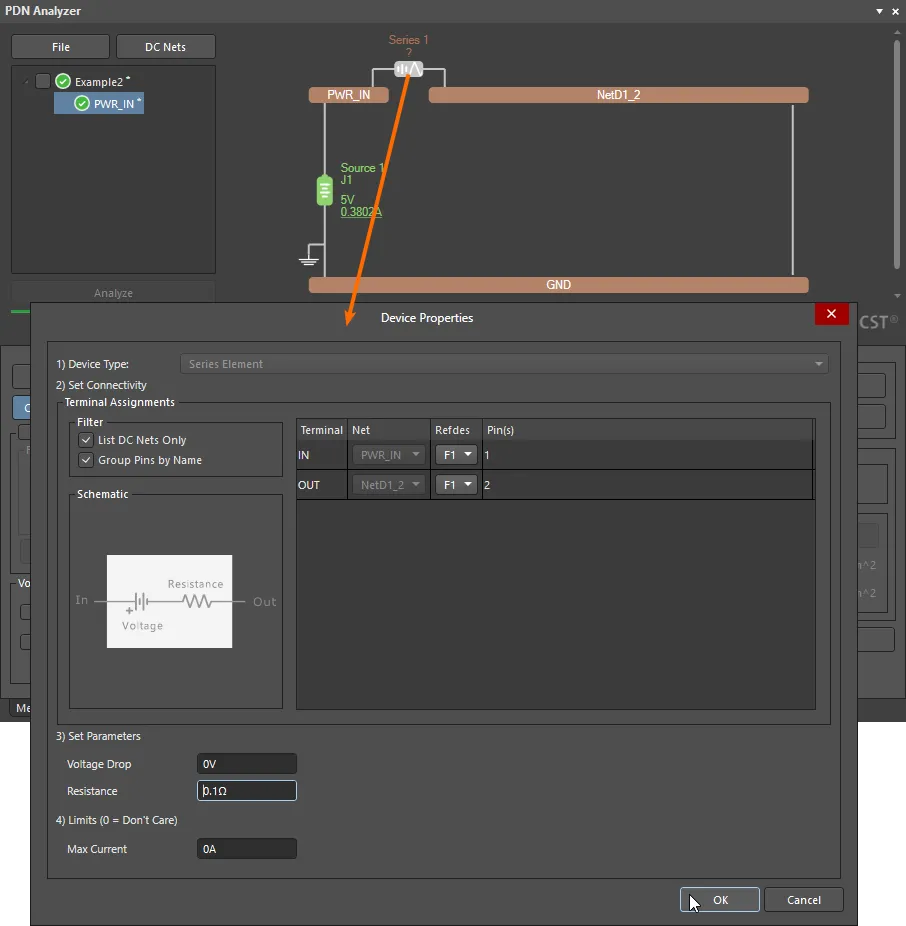

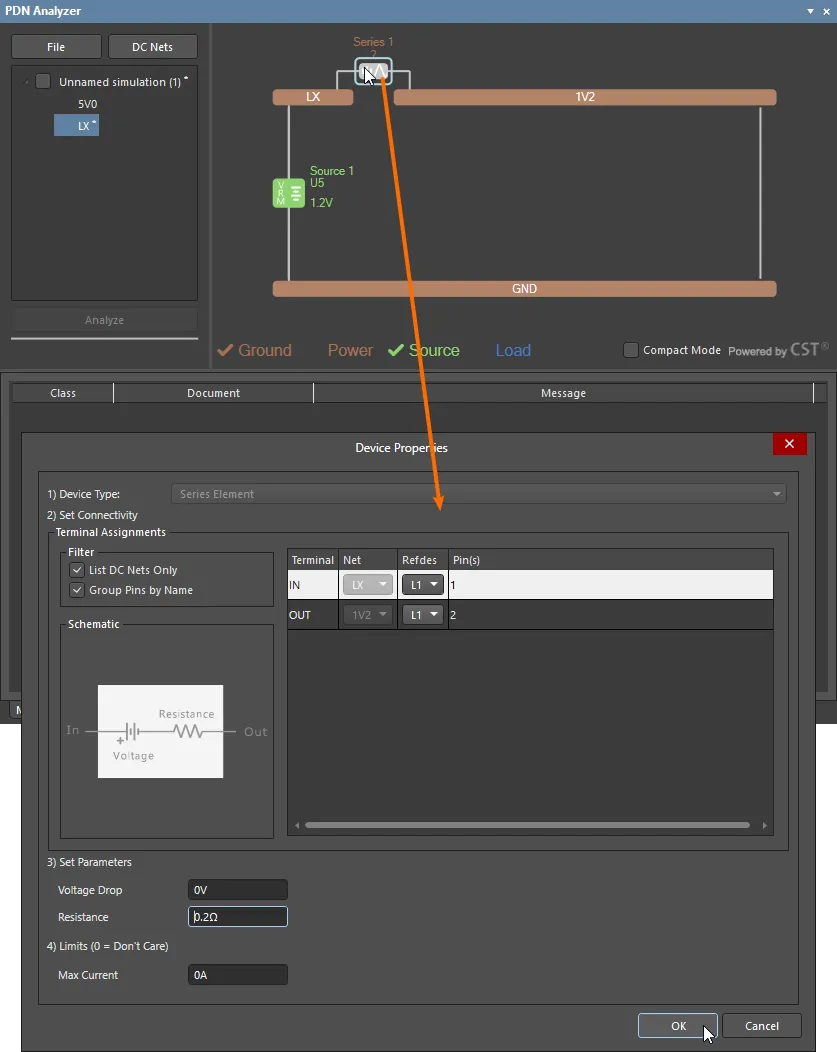

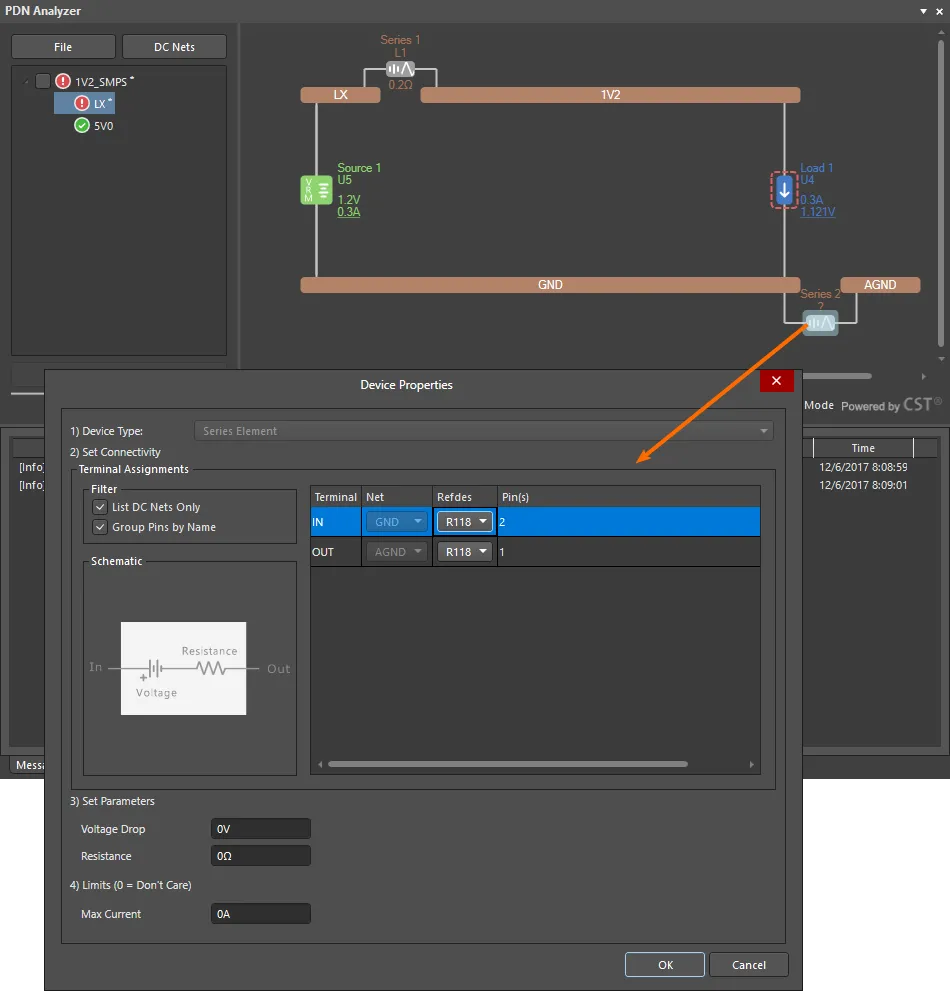

ネット拡張プロセスにより、2つのネット間にSeries Elementが自動的に追加されます。この要素をダブルクリックして、Device Propertiesダイアログで接続関係とパラメータを指定します。Series Elementモデルは、電圧源と抵抗の直列で構成され、抵抗、インダクタ、ダイオード、スイッチなどのコンポーネントを基本的にモデル化できます。

このケースではSeries Elementはヒューズ部品F1であり、接続RefDesオプションとして選択し、公称の内部Resistanceを0.1Ωとして与えます。Series Elementがダイオードなどの半導体デバイスである場合は、Voltage Dropパラメータをデバイスの内部Resistance値とともに指定します。

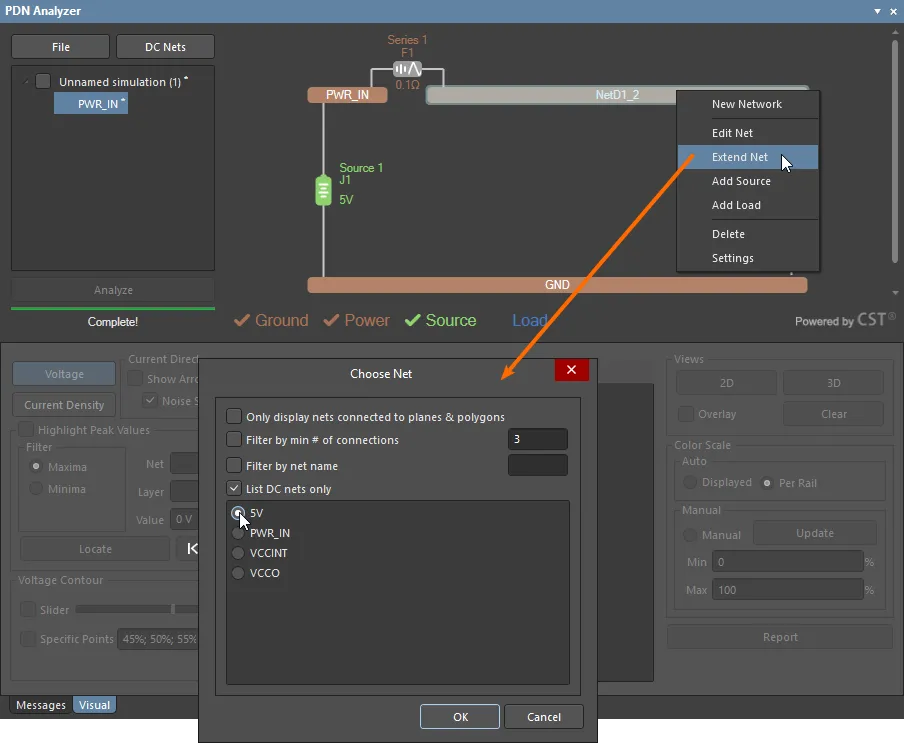

回路図に沿って作業を進めると、次のステップは、スイッチ部品 S1 を介してネット D1_2 を 5V 電源ネットへ拡張することです。前述と同様に、右クリックのコンテキストメニューから Extend Net を選択し、Choose Net ダイアログで拡張先のネットを選びます。

この場合に追加される直列要素(Series Element)は S1 で、ピン3からピン2を介して D1_2 ネットを 5V 出力ネットワークへ接続します(schematic を参照)。S1 の予備入力スイッチ(ピン1)は出力接続(ピン2)に結線されており、負荷電流を流さないため、例として Device Properties ダイアログの pin selection options を使ってネットワーク解析からピン1を除外できます。OUT端子エントリの Pin(s) フィールドをダブルクリックしてください。

これで、接続された電源ネットワークの5Vセクションに負荷を追加できます。この場合は表示モジュール LCD1 の負荷です。

解析を再実行すると、PCB Editor のデータおよびグラフィック表示の両方に、接続された3つすべての電源ネットワークが含まれ、相互接続する直列要素を通る計算済み電流と電圧降下が表示されます。

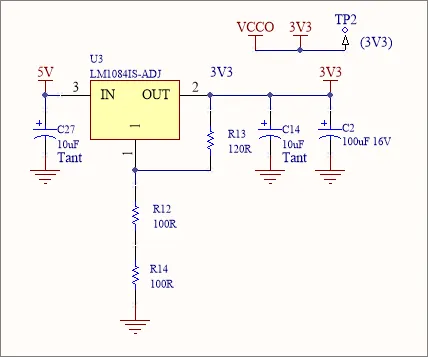

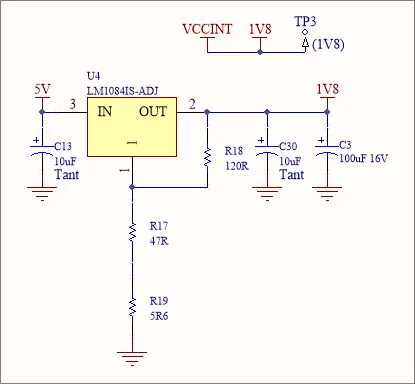

電圧レギュレータモデルを含める

PDN Analyzer には、電圧入力ネットワークと出力ネットワークの間に挿入できるアクティブな Voltage Regulator Models(VRM)が用意されています。PDNA の電源ネットワークに追加すると、電圧入力ネットワーク側では負荷(Load)として、電圧出力ネットワーク側ではソース(Source)として現れます。VRMモデルのオプションには、リニア、スイッチング、およびリモートセンシング対応スイッチング電圧レギュレータがあります。

SpiritLevel-SL1 参照プロジェクトでは、リニア電圧レギュレータを使用して 3.3V(VCCO)および 1.8V(VCCINT)の電源レールを生成します。VCCO レギュレータ(U3)を PDNA シミュレーションネットワークに追加すると、5V入力ネットワークの負荷として、また 3.3V ネットワークのソースとして提示されます。

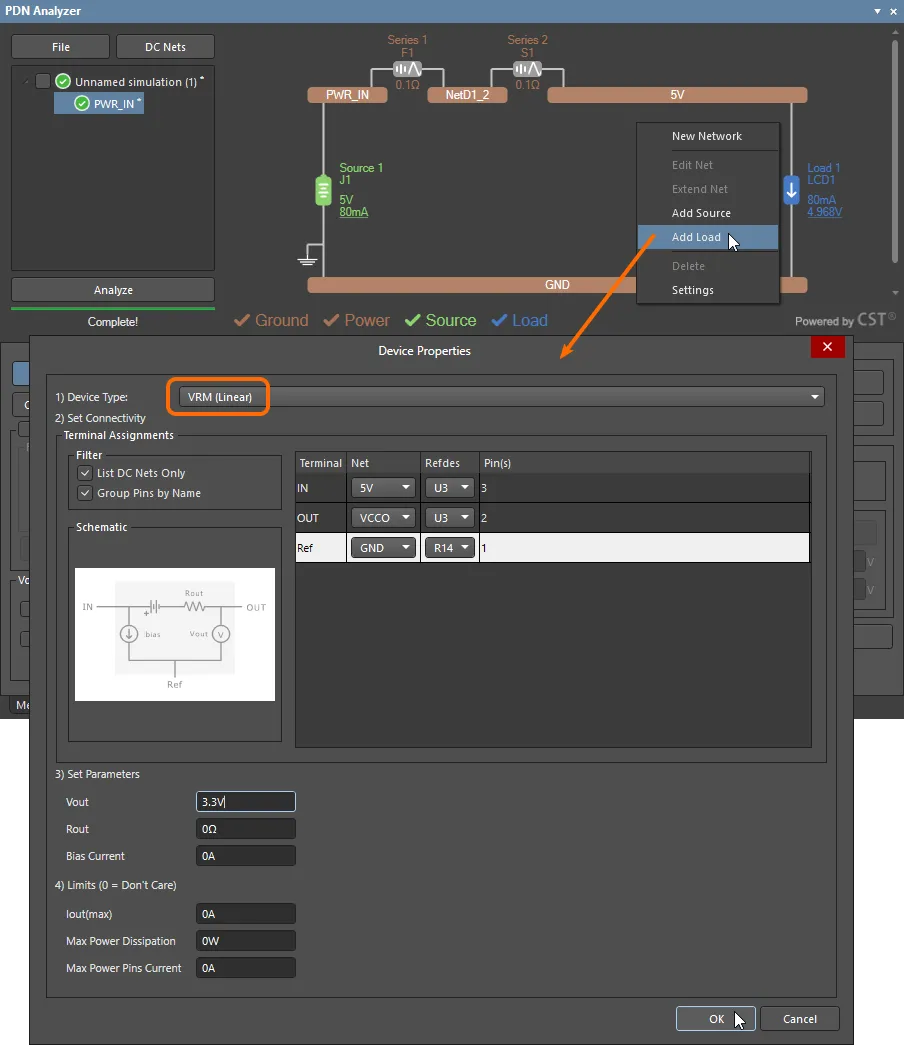

リニアレギュレータ U3 を5Vネットワークの負荷として配置するには(上記手順で実装したのと同様に)、5Vネットワークに Load を追加し、Device Properties ダイアログで Device Type として VRM (Linear) オプションを選択します。回路図に示されているとおりにモデルの接続を設定し、R14 のGND接続として Ref ピンを指定します。この基準点は、GNDネットワークのレイアウトに応じて、PCBの近傍で別の、より適切な位置にすることも可能です。

VRMを確定するには、出力電圧パラメータ(Vout: 3.3V)を設定し、必要に応じて出力(内部)抵抗、定常バイアス電流、解析中に検出させたい Limits を指定します。

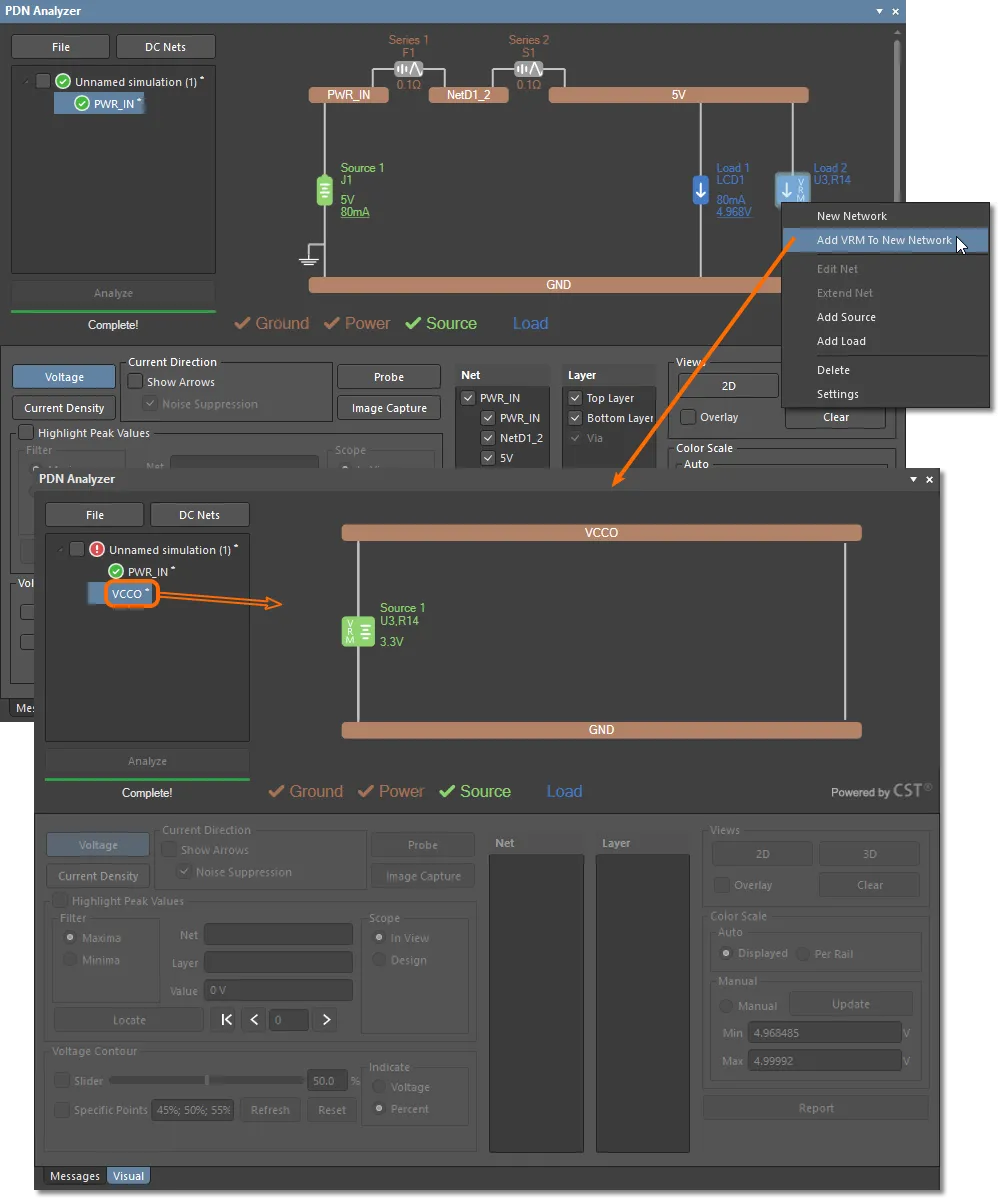

PDNA には、VRMの出力側モデルをターゲットの出力電圧ネットへソースとして自動追加し、必要であればそのネットワークを作成する手段があります。

この例では、作成したばかりのVRM負荷モデル(Load2: U3)を右クリックし、Add VRM To New Network オプションを選択します。これにより、VRM(Source 1: U3)の出力側モデルが電圧ソース(3.3V)として設定されたVCCOネットワークが自動的に作成されます。

3.3V VRMの2つの現れ方、すなわち5Vネット上の負荷としての入力モデルと、3.3Vネットのソースとしての出力モデルは相互に連動しており、実質的に同一モデルです。そのため、PDNAインターフェースではどちらのネットワークからでもVRMにアクセスして編集できます。

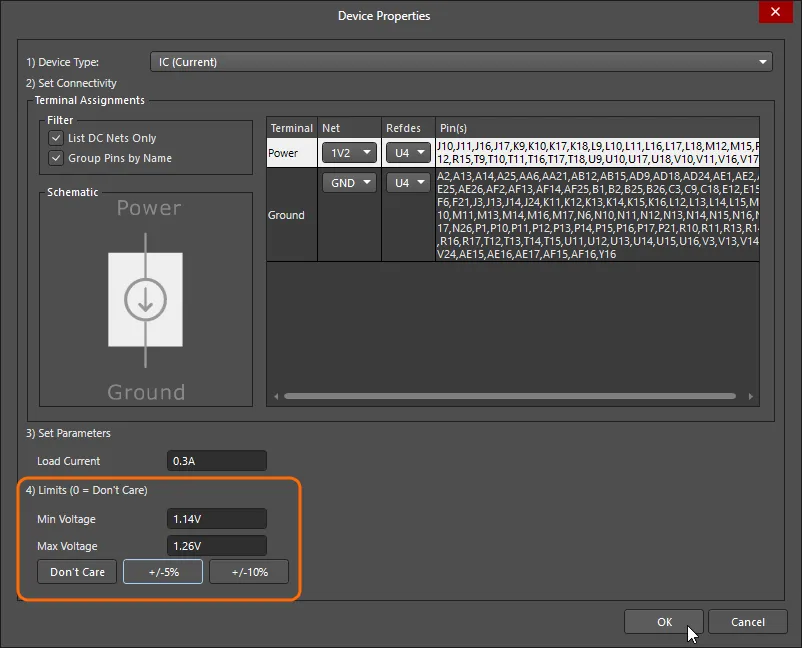

新しいVCCOネットワークを選択し、適切な負荷を追加できます。この例では、部品 U1 の複数ピンによって消費される0.2Aの負荷電流です。

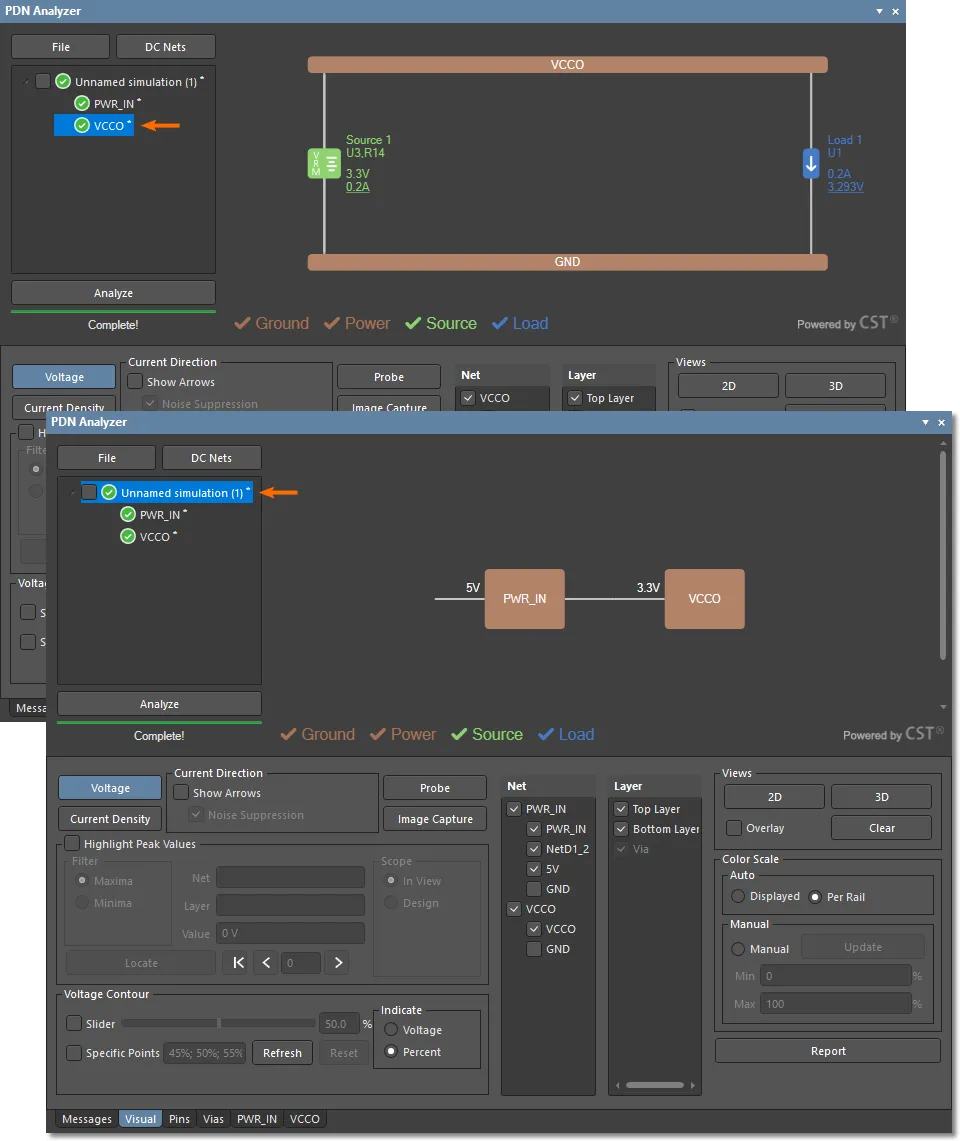

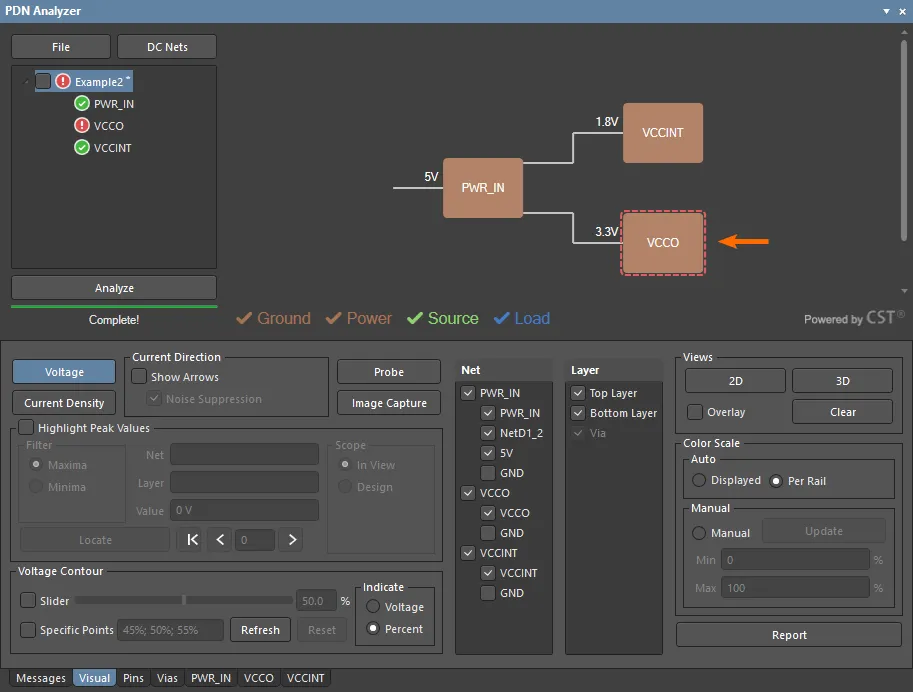

完成した電源ネットワーク構成には、3.3Vのリニア型VRMによって接続された2つのネットワーク(PWR_IN と VCCO)が含まれます。現在のPDNAファイル構造でネットワーク階層の最上位を選択すると、ネットワークグラフィックにより電源ネットの相互接続がブロック形式で概観表示されます。

この例では、VRMを5V(入力電圧)ネットワークに負荷として追加し、その後VRMをソースとして用いて 3.3V(VCCO)の電圧出力ネットワークを自動作成しました。逆の手順も可能で、場合によってはこちらの方が便利です。その場合、VRMを出力電圧ネットワークにソースとして追加し、そのモデルを「入力」電圧ネットワークに負荷として追加します(Add VRM To New Network または Add VRM To Existing Network)。

PDN解析では、VRMを含む複合ネットワークの結果が得られます。グラフィック表示としては、PDNAインターフェースでネットワーク階層の最上位を選択すると、PCB Editor にすべてのネットワークが表示されます。リストから個別ネットワークを選択すると、レンダリングされるグラフィックをそのネットワークに限定でき、さらに下部パネルの Net および Layer オプションを切り替えて表示を制御できます。

なお、この例のGNDネットワーク経路には、PWR_IN ネットワークと VCCO ネットワークの両方からのリターン電流の寄与が含まれるようになります。

例のプロジェクトの電源分配ネットワークは、残りのVRM(U4)と、その1.8V電源出力ネットワーク(VCCINT)を追加することで完成します。

前述のとおり5VネットワークにリニアVRMを追加し、Vout パラメータを 1.8V に設定します。

VRM(ここでは Load 3)を新しいネットワークに追加して、1.8V(VCCINT)電源ネットワークを作成します。

VCCINTネットワークに適切な負荷を追加します。ここでは部品 U1 の1.8V電源ピンです。

PDNAインターフェースのネットワーク階層には、相互接続された3つのネットワークがすべて表示されるようになります。

PDN解析では、VRMを含む複合ネットワークの結果が得られます。

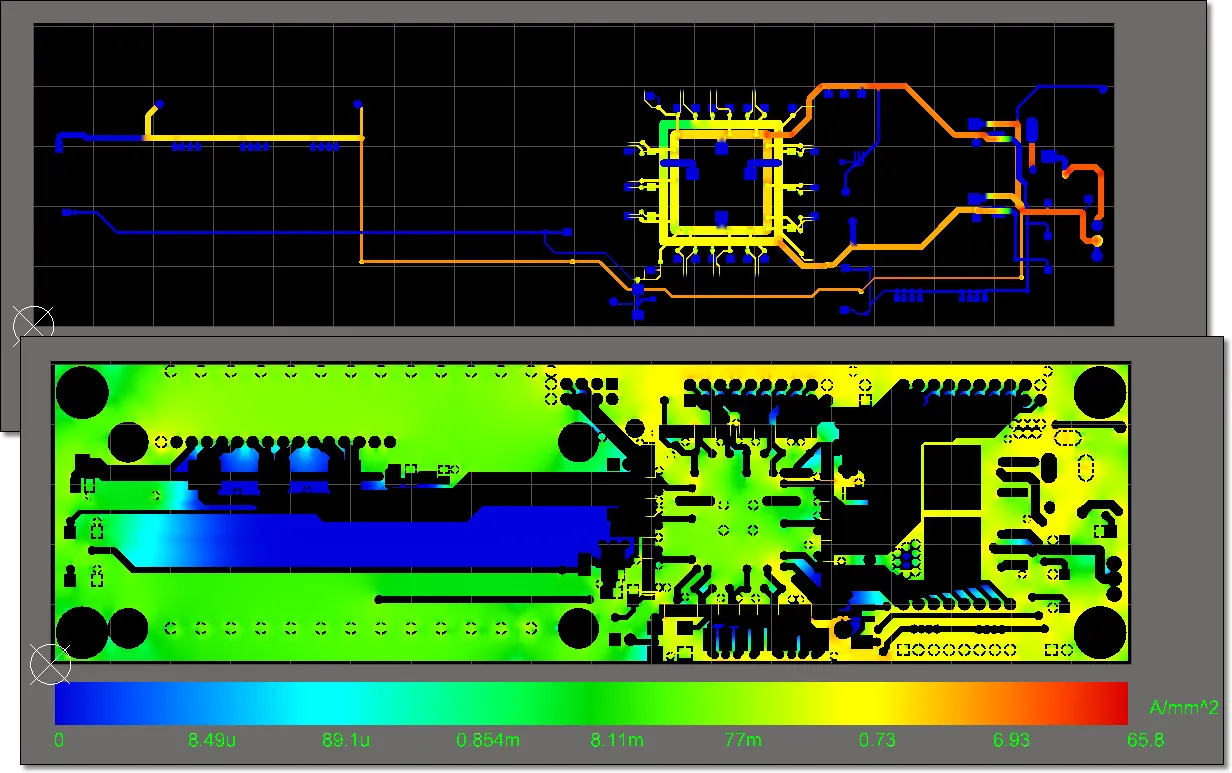

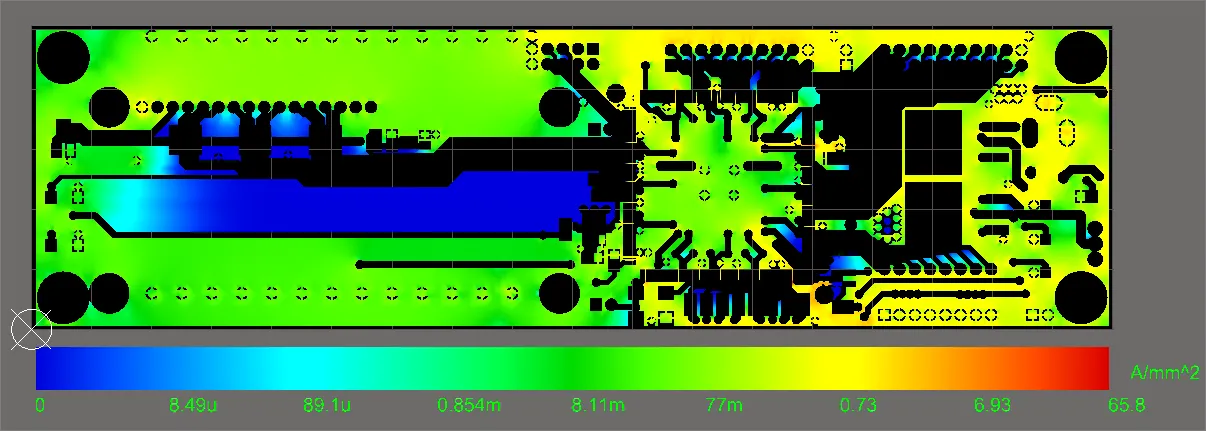

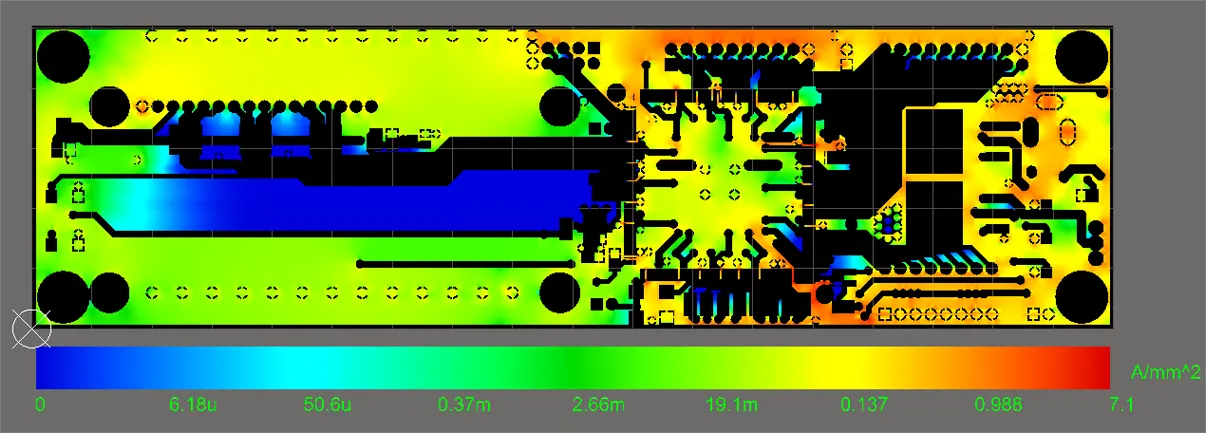

繰り返しになりますが、GNDネットワークには、共通のGNDレイヤーシェイプを使用する3つすべてのネットワークのリターン電流が含まれるようになります。その最大電流密度レベル(65.8 A/mm2)は高く、許容限界を超える可能性が高い状態です。

電源インテグリティ問題の特定

PDN Analyzer は、解析済みPCB設計の電源インテグリティを評価し、トラブルシュートするために使用できる、包括的なグラフィックおよびデータ情報を提供します。

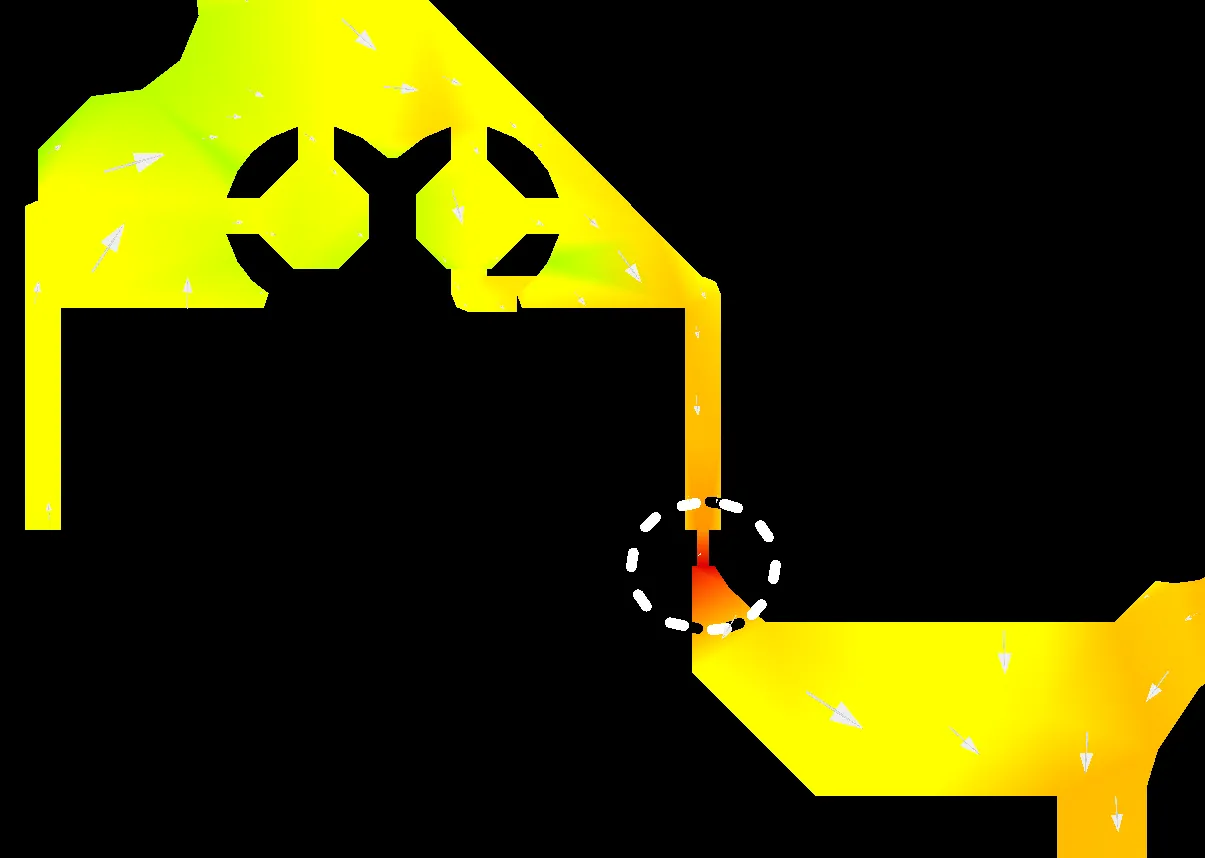

上記の例では、Top Layer GNDネットワーク経路の解析により、65.8A/mm2 の最大スケール値が示すとおり、許容できないほど高い電流密度が存在することが分かります。問題箇所はすぐには明確ではありませんが、PDNA の Highlight Peak Values 機能を使うことで特定できます。

これを選択し、Filter オプションを Maxima に設定すると、電流密度のピーク領域がハイライトされ、PCB Editor の解析グラフィック上にマークされます。

ボタンをクリックしてグラフィックのハイライトを繰り返すか、関連ボタン(

ボタンをクリックしてグラフィックのハイライトを繰り返すか、関連ボタン( )を使用して、最も高いピークの読み値/位置を順にたどります。Scope オプションを設定して、現在表示されているPCB領域内のピークをハイライトする(In View))か、レイアウト全体のすべてのピークを対象にする(Design)かを選びます。後者では、ステップ移動に合わせて各位置へパン/ズームします。

)を使用して、最も高いピークの読み値/位置を順にたどります。Scope オプションを設定して、現在表示されているPCB領域内のピークをハイライトする(In View))か、レイアウト全体のすべてのピークを対象にする(Design)かを選びます。後者では、ステップ移動に合わせて各位置へパン/ズームします。

懸念箇所の追加情報は、PDNA の Show Arrows 機能を有効にすることで推定できます。これは、電流方向(矢印の角度)と相対的な大きさ(矢印のサイズ)を示す複数の矢印グラフィックを重ねて表示します。この例では、高密度領域がU1(上側)から基板下側外周のGND領域へ戻る電流のリターンパスであることを確認できます。

この問題を解決する方法の1つは、懸念箇所の配線幅を広げることです。

PDN Analyzer を有効にしたままPCB編集を行えるため、レイアウト改善を反復的に実施して再解析できます。PCB Editor でPDNA結果を無効化し、必要なPCB編集を進めるには、Views 領域の Clear ボタンをクリックします。

その後、PDN解析を再度実行( をクリック)して電源インテグリティ結果を確認できます。以下の2つの画像は、重要箇所で配線幅を増やしたことによってGNDネットワーク(

をクリック)して電源インテグリティ結果を確認できます。以下の2つの画像は、重要箇所で配線幅を増やしたことによってGNDネットワーク(Top Layer 上)の電流密度がどのように変化したかを示しています。上の画像が初期の電流密度結果、下の画像がPCB修正後の電流密度グラフィックです。

この「修正前(上)」と「修正後(下)」の比較における注目点は次のとおりです。

-

GNDレイヤーの最大電流密度レベルが、以前の値のおよそ10分の1という許容レベルまで低下しました(

65.8A/mm2 から 7.1A/mm2 へ)。

-

最大電流領域は、値が大幅に低下したうえで、1つの問題箇所に集中するのではなく、GNDリターンパス全体により均等に分散しています。

-

より直接的にグラフィック比較するには、電流密度スケールを以前の値に手動設定します。Manual スケールオプションを選択し、Max フィールドに

65.8 を入力して  ボタンをクリックし、表示を更新します。

ボタンをクリックし、表示を更新します。

電流密度制限違反

PCB設計の電流経路における電源インテグリティ問題を、より客観的に特定して解決する方法は、特定の電流密度制限を定義し、超過時に違反として検出させることです。他の種類の違反 については以下を参照してください。

表層/内部層およびビアの電流密度制限は、Settings ダイアログの Limits タブで指定します。このダイアログは、現在のPDNシミュレーション名を右クリックし、コンテキストメニューから Settings を選択して開きます。設定した制限は、基板設計内のすべての表層/内部層およびビアに適用されます。

指定した電流密度制限は、現在の解析結果に適用され、シミュレーションを再実行しなくても変更して再評価できます。制限検出は解析後処理です。違反を含むネットワークは赤い破線のアウトラインで表示されます。

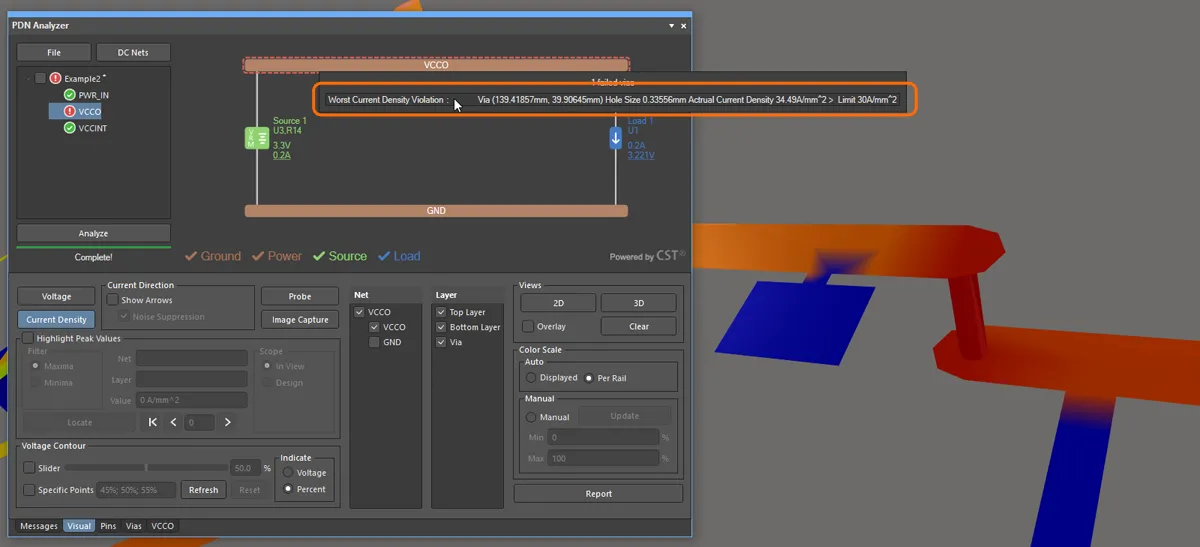

ここに示す例では、VCCO電源ネットワークに電流密度違反が含まれています。VCCOネットワーク自体を選択すると、VCCO電源経路がハイライトされたアウトラインによって違反状態であることが示されます。違反しているネットワーク上にカーソルを合わせると、現在の違反内容とそれに関連する詳細を示すポップアップリストが表示されます。この場合の単一エントリは、ビア内の電流密度(約 34.5A/mm2)が、定義された上限(30A/mm2)を超過していることを示しています。

違反エントリをダブルクリックすると、その位置へクロスプローブ(パンおよびズーム)します。下の画像では、PDNA のグラフィックスビューが 3D モードに設定されており、問題となっているビアと、その Top/Bottom レイヤ接続がより明確に表示されています。

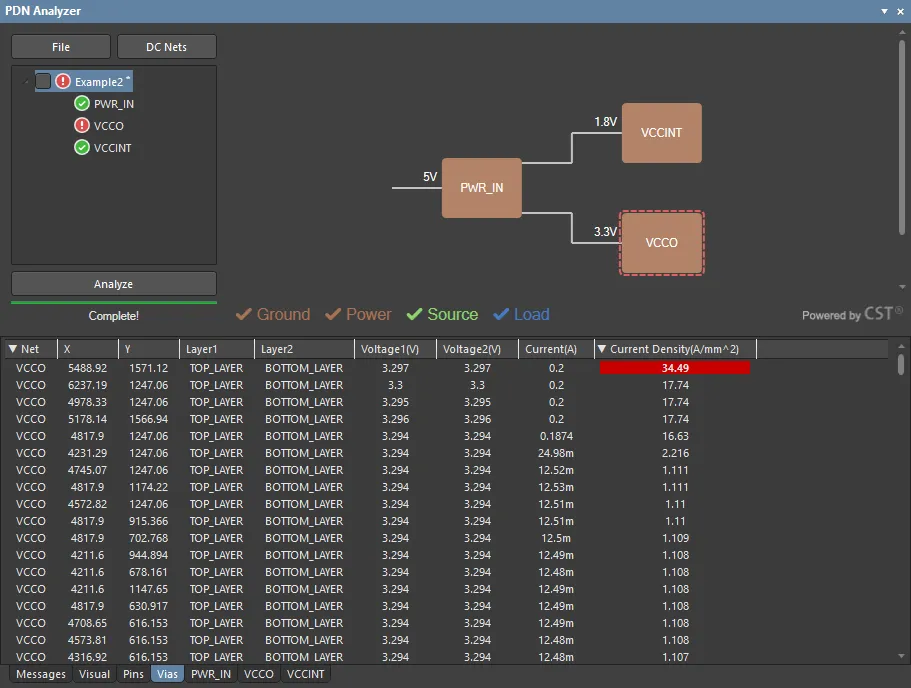

このビアに関する関連データ(電流密度違反の表示を含む)は、PDNA インターフェースの Via タブで確認できます。

ビア情報の一覧は、現在の設計に含まれるすべてのネットワークに適用されます。Net および Current Density の列見出しを切り替えて並べ替えると、VCCO ネットワークのビアを電流密度順に表示できます。定義された制限を超える電流密度値は赤でハイライト表示されます。

ビア一覧の任意のエントリをダブルクリックすると、PDNA の基板グラフィックス上の位置へクロスプローブできます。

その他の違反

指定した電流密度上限の検出に加えて、PDN Analyzer は、Load、Source、または Series Element を追加する際にシミュレーション設定で指定された Limit パラメータなど、対象ネットワークの性能違反も検出します。

これらのシミュレーション Limit パラメータには、次が含まれます。

-

Load における許容電圧範囲

-

Source からの最大出力電流

-

リニアレギュレータ Source における許容電力損失、および最大出力電流

-

スイッチングレギュレータ Source からの最大出力電流

-

Series Element を流れる最大電流

Source 電圧や Load 電流設定などのネットワーク要素のシミュレーションパラメータは解析実行中に処理されますが、Limit パラメータ違反(例:Load の最小電圧指定)の検出は解析後の処理です。つまり、Limit パラメータ値を変更すると、シミュレーション解析を再実行しなくても直ちに検出されます。

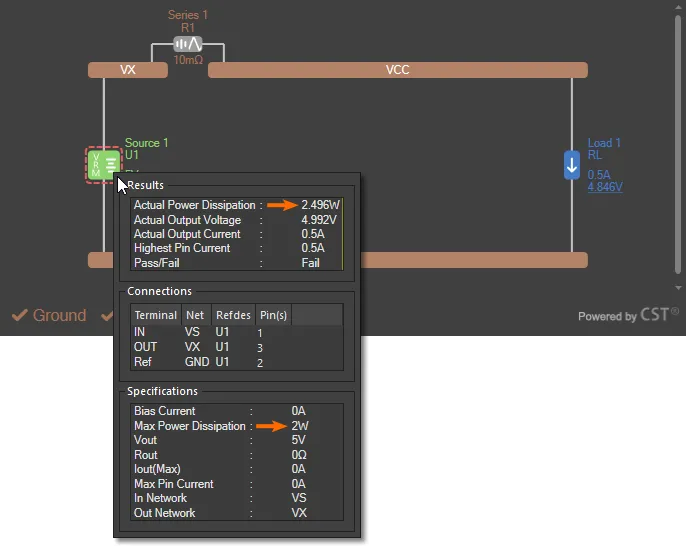

Limit パラメータが指定されている(ゼロ以外の値を持つ)場合、そのパラメータに違反すると、該当するネットワーク要素が PDNA インターフェースのネットワークグラフィック上でハイライト表示されます。要素にカーソルを合わせると、パラメータと解析結果を確認できます。

以下の例では、Source 1(電圧レギュレータ U1)で算出された電力損失が、定義された最大 Power Dissipation パラメータ 2W を超過しています。

電源ネットワークの性能に関するより詳細な情報は、そのネットワークタブで確認できます。ここでは解析結果データの表形式ビューが表示され、算出されたネットワーク消費電力値も含まれます。

例 3

この例では、PDN Analyzer のスイッチング電源(SMPS)シミュレーションモデル(VRM)を電源ネットワークに適用し、更新されたネットワークモデルによってより正確な電源解析結果が得られることを示します。また、PDNA の Voltage Probe および Contour 機能を使用して、基板レイアウト形状内の特定ポイントまたは領域の電圧データを表示する概要も示します。

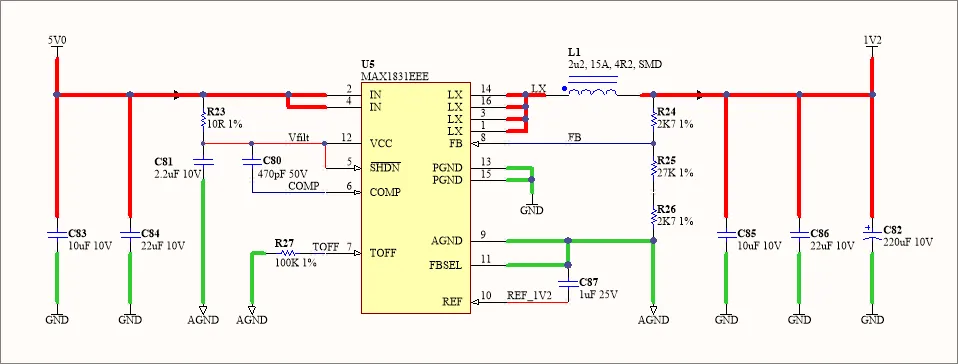

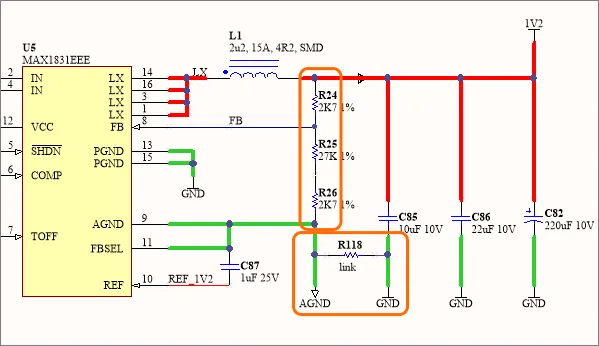

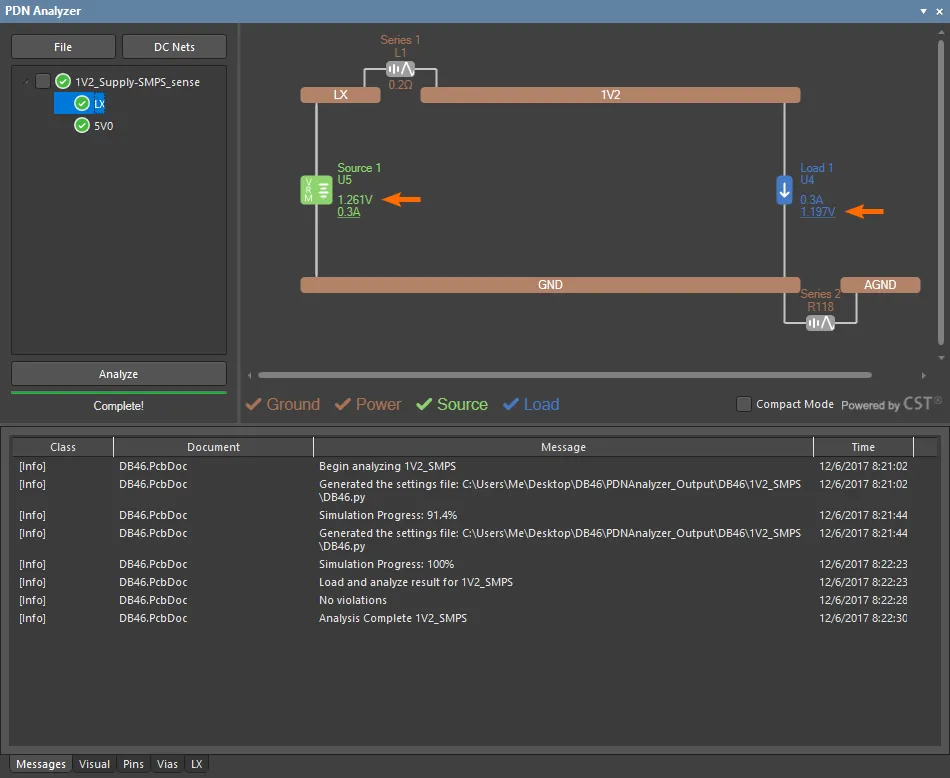

この例は Altium の DB46 Xilinx Daughter Board リファレンスプロジェクトに基づき、設計の 1.2V 電源ネットワーク(1V2)に使用される SMPS セクション(U5)に焦点を当てます。

この PDN シミュレーション例の前提条件は次のとおりです。

-

DB46 Xilinx Daughter Board プロジェクトが Altium Designer で開かれている

-

PDN Analyzer アプリケーションがアクティブである(Tools » PDN Analyzer)

-

PCB 設計の DC Nets が PDN Analyzer DC Net Identification ダイアログで識別されており、上記のとおりであること。なお、この例ではネットワーク

LX と AGND も必要です。

新しいシミュレーションで入力電源ネットを指定して、例の電源ネットワーク構築を開始します(必要に応じて File » New Simulation を選択)。上の回路図が示すとおり、PDN <Power Net> は 5V で、<Ground Net> は GND です。5V ネットワークの Source はコネクタヘッダ HDR_T1 または HDR_B1 です。

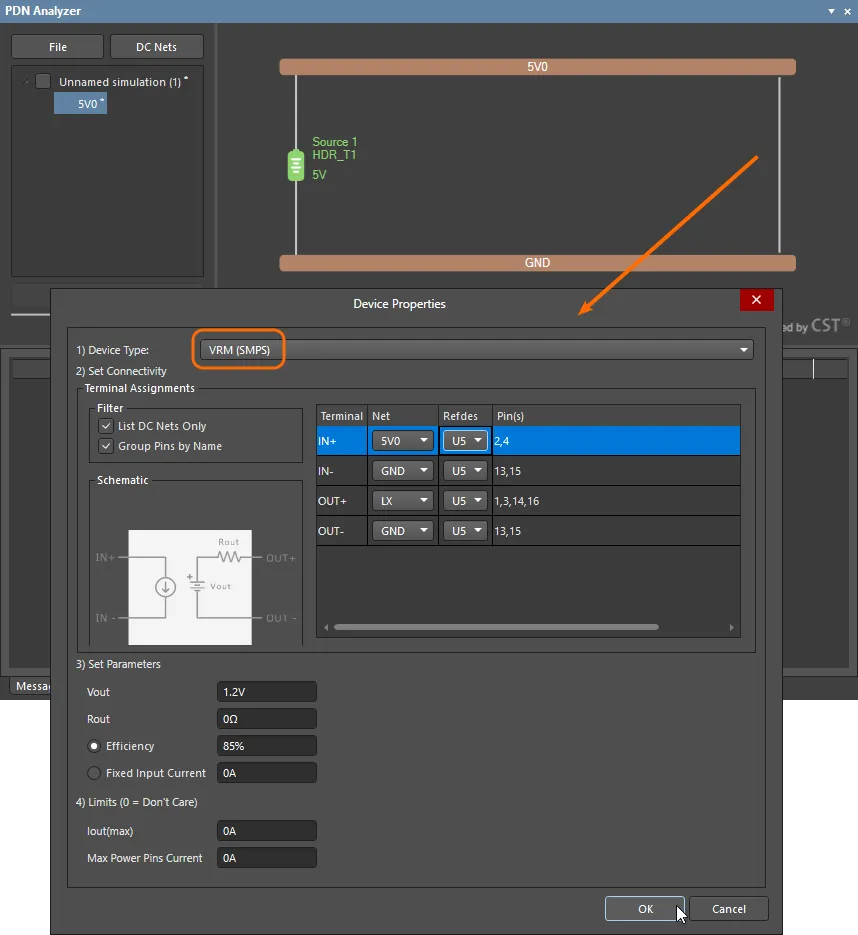

スイッチモード VRM

設計の SMPS 回路のモデルは、Device Properties ダイアログで Load Device Type として VRM(SMPS) を選択することで、5V 電源ネットワークに追加します。ダイアログ内のモデル回路図が示すとおり、IN と OUT のピンセットは別々に定義されています。

この回路に対してモデルを正しく定義するには、出力として LX を指定し、RefDes オプションに U5、さらに Vout パラメータとして 1.2V を指定します(上の回路図のとおり)。必要に応じて、Rout および効率/電流パラメータを、使用している SMPS デバイスに合わせて設定します。

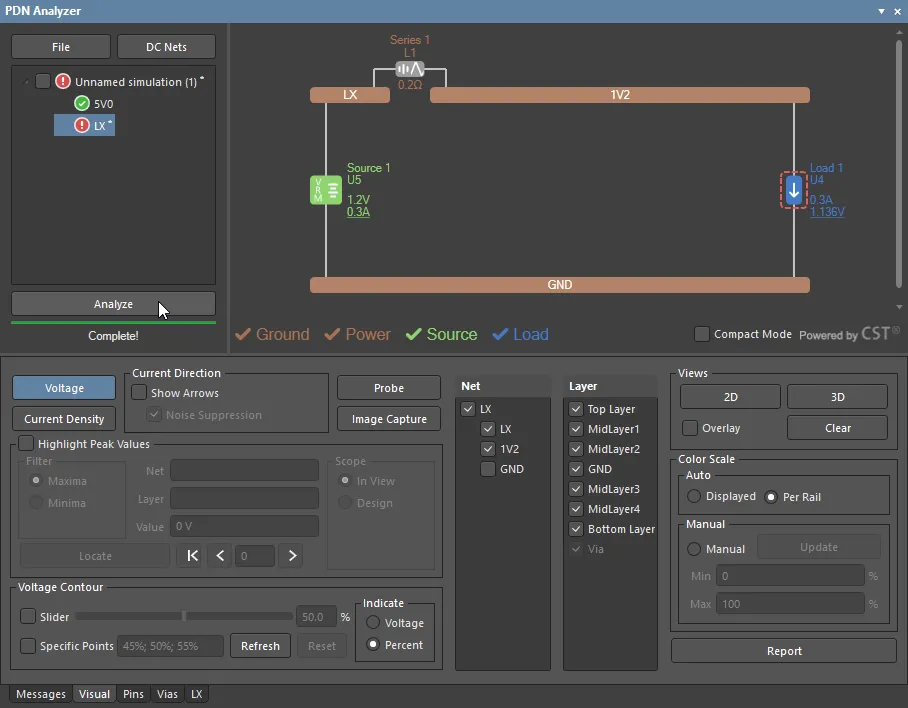

VRM をその出力ネットワーク(Add VRM To New Network)に追加して SMPS モデル実装を完了します。これは自動的に LX ネットワークとして選択されます。その後、LX ネットワークを schematic のとおりに拡張して、1.2V 電源ネットワークを含めることができます。

LX ネットワークと 1V2 ネットワークは、Series Element L1(SMPS の降圧インダクタ)で接続されており、適切な直列抵抗を示すように設定する必要があります。この例では、説明のためにやや大きい 0.2Ω に設定しています。

最後に、1V2 ネットワーク上に U4 を 0.3A Load として追加し、許容される負荷電圧偏差を +/-5% に指定します。なお、この例では Settings dialog の Limits タブにある電流密度上限オプションを 0(デフォルトの No Limit 条件)に設定してください。

解析を実行すると、複合ネットワーク LX 上の Load が Violation を示すことに気づくはずです。これは、Load(U4)における 1V2 ネットワーク電圧が許容できないほど低い(約 1.14V)ためです。

Data Probe

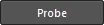

PCB Editor での PDNA グラフィックとスケールの視覚的な解釈に加え、PDN Analyzer は、アクティブな Probe など、設計レイアウト内の特定領域またはポイントにおける解析結果を解釈するためのツールを複数提供します。

Probe ツールを使用すると、設計レイアウト内で指定したポイントの電圧または電流密度データを記録し、比較できます。このツールの柔軟性により、任意のネットワークやレイヤ上の解析データ結果を正確に評価できます。ただしこの例では、1V2 ネットワーク Load における許容できない電圧降下の原因が、L1 Series Element の抵抗であることを確認するために使用できます。

1V2 ネットワークの電圧について差分プローブ測定を行うには、まず PNDA を Layer MidLayer 1(U4 への主要な 1.2V 経路)と Net 1V2 のみを表示するように設定します。 ボタンを選択して Probe ダイアログを開き、最初のプローブ位置(

ボタンを選択して Probe ダイアログを開き、最初のプローブ位置( )を有効にします。カーソルの十字を使って最高電圧ポイント(このレイヤ上での

)を有効にします。カーソルの十字を使って最高電圧ポイント(このレイヤ上での 1V2 ネットワークのソース)を指定し、その後プローブの Difference オプションをチェックして、2つ目の位置( )—

)— U4 Load にある最低電圧ポイント — を指定します。

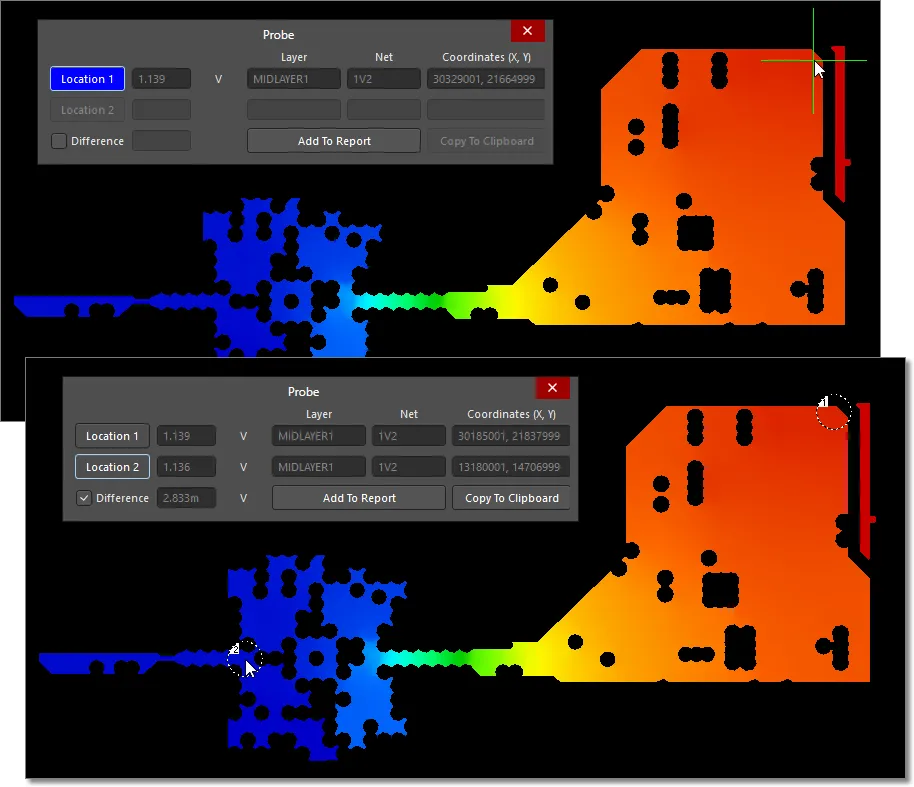

プローブの Difference 読み取り値は、ネットワーク経路の電圧降下が約 3mV に過ぎないことを示している点に注意してください。同様に、LX ネットワーク経路(Top と Bottom Layer をアクティブ)も確認すると、電圧降下は約 0.5mV 程度であることが分かります。

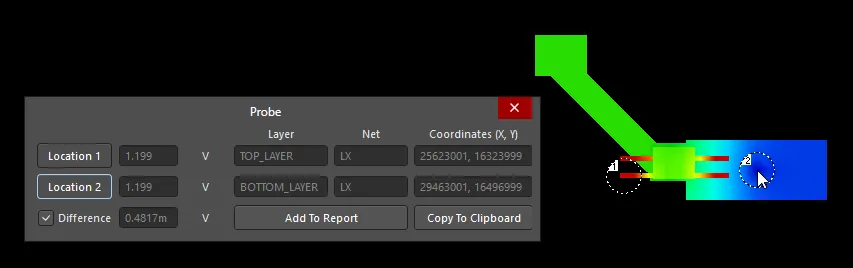

2つのネットワーク(Net LX と 1V2 を有効、Top と Bottom Layer)間でプローブによる電圧差テストを行うと、インダクタ L1 に 60mV の降下があることが分かります。これが、この analysis Violation を引き起こす主要な電圧損失です。

ここで示した電圧 Probe の調査により、電源ネットワークにおける IR 損失の主因が特定できましたが、PDNA の Pins タブでデバイスピン電圧データを確認すれば、より直接的に解決できた可能性もあります。Probe 機能は、位置精度を最大限に活かせる、より詳細な調査に最適です。

SMPS-sense VRM

この例で使用しているスイッチング電源回路では、通常は抵抗値がはるかに低いインダクタ(L1)を使用します。しかし、ここでの解析結果は、基本的な SMPS モデルでは L1 を通る損失を考慮できないことを示しています(ただし一般的に、実用回路では問題にならないでしょう)。

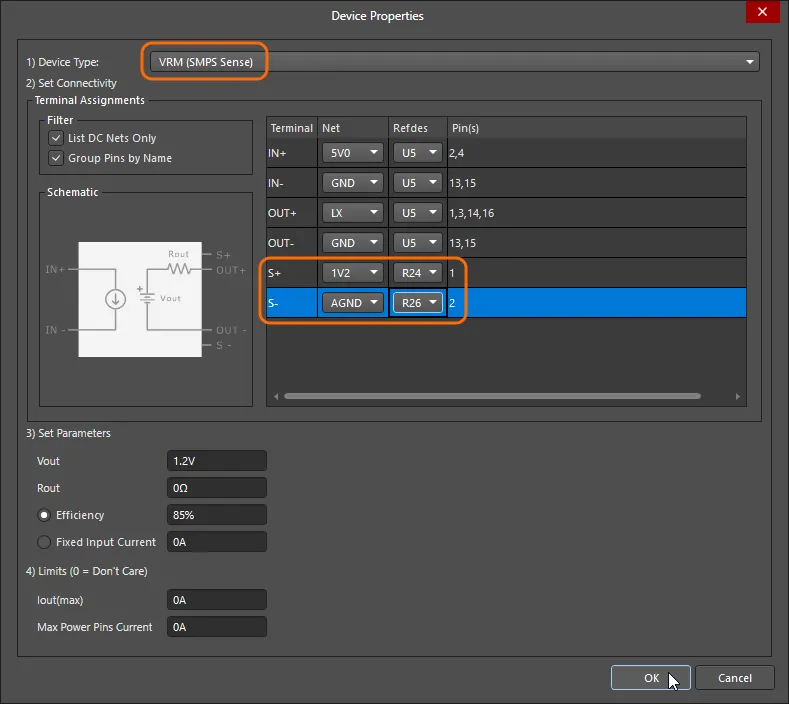

例のプロジェクトの SMPS 回路では、U5(ピン 8)で検出される電圧フィードバックは、1V2 出力ネットワークとアナロググランドネットワーク AGND の間にある抵抗チェーン R25–R26 から得られます。後者は、0Ω タイ抵抗 R118 を介して GND ネットワークに接続されています。

U5 周辺の回路動作をより正確にモデル化するため、標準の SMPS デバイスの代わりに、PDNA のリモートセンシング対応スイッチモードモデルを適用できます。このモデルは、別個の電圧センシング端子(S+ と S-)を備えており、指定した出力ネットワーク上の任意のピン(この回路では電圧検出用抵抗チェーンのピンなど)に「接続」できます。

U5 SMPS 回路のより完全なネットワークモデルを作成する最初のステップは、既存の GND ネットワークに AGND ネットワークを追加することです。Extend Network オプションを使用し、AGND ネットを選択します。

AGNDネットワークは、上記の回路図に示すように抵抗R118を介してGNDネットワークに接続されており、Resistanceの値を0Ωに設定する必要があります。

LXネットワーク内のSMPSモデルを更新するには、既存のU5ソースデバイス(Source 1)を削除し、代わりに代替のSMPS Senseモデルを追加します。モデルのINおよびOUT端子の接続はこれまでどおりに設定します。センシング端子(S+/S-)は、回路図に示すとおり、回路のフィードバック抵抗チェーンの両端に設定します。

LXネットワークからソース5Vネットワークへ置換したSMPSモデルを反映(伝播)させ、ネットワーク同士が対応するようにします。そのために、まずU5Loadを削除し、次にLXネットワークでAdd VRM To Existing Network » 5VSourceオプションを適用します。

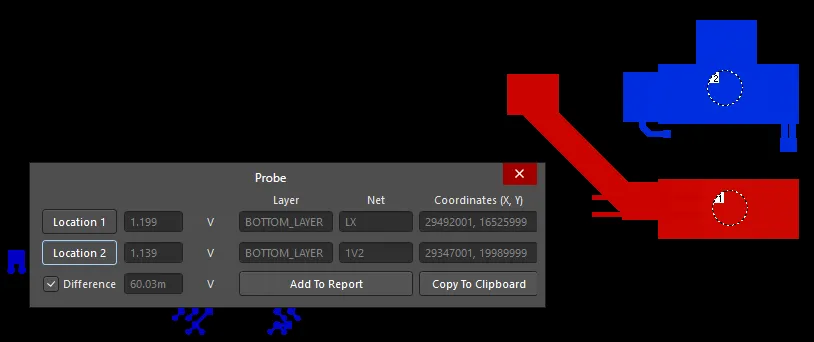

更新した回路は、その後再解析して結果を評価できます。 下の画像に示すように、負荷電圧は現在+/-5%要件の範囲内に十分収まっており、Violationは示されません。1V2ネットワークで出力電圧をセンシングすることにより、SMPSはSeries Element L1での電圧損失を補償しています。その結果、LXネットワークの電圧は60mV高くなります。

この特定の回路では高度なSMPS-senseモデルを使用することでより正確な解析結果が得られますが、リモートセンシング機能を備えたSMPSデバイスを実際に使用する場合、近傍のフィードバックネットワークではなく、センス端子から負荷そのものへ直接PCB接続することがあります。この場合、両方のセンスライン(S+およびS-))は、それぞれ負荷の対応する端(またはその近傍)まで専用のPCB配線(トラック)で引き回します。

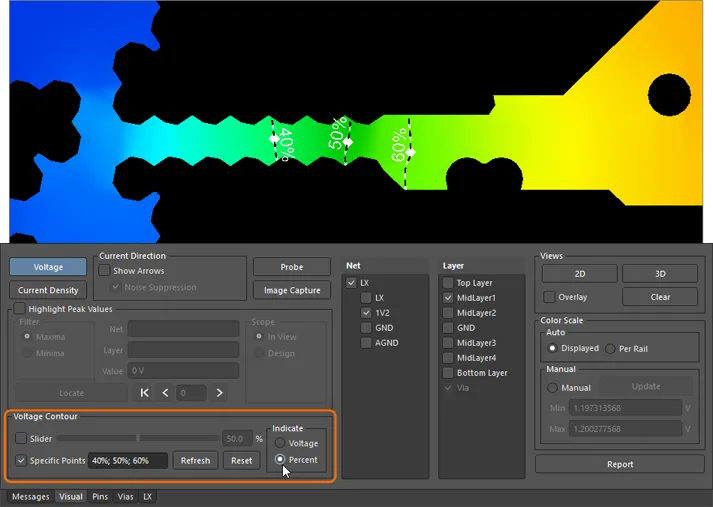

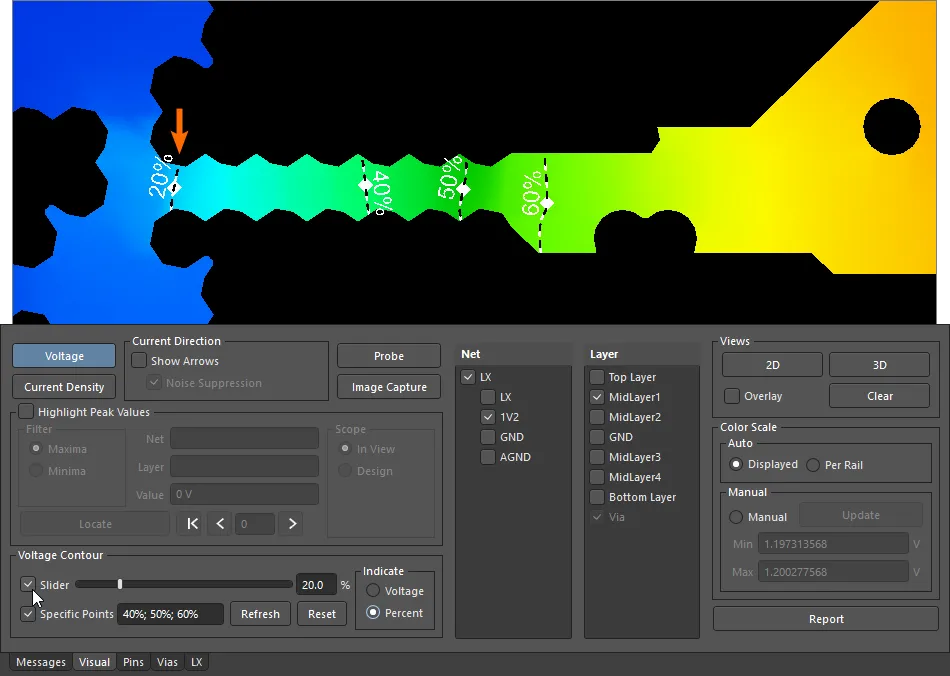

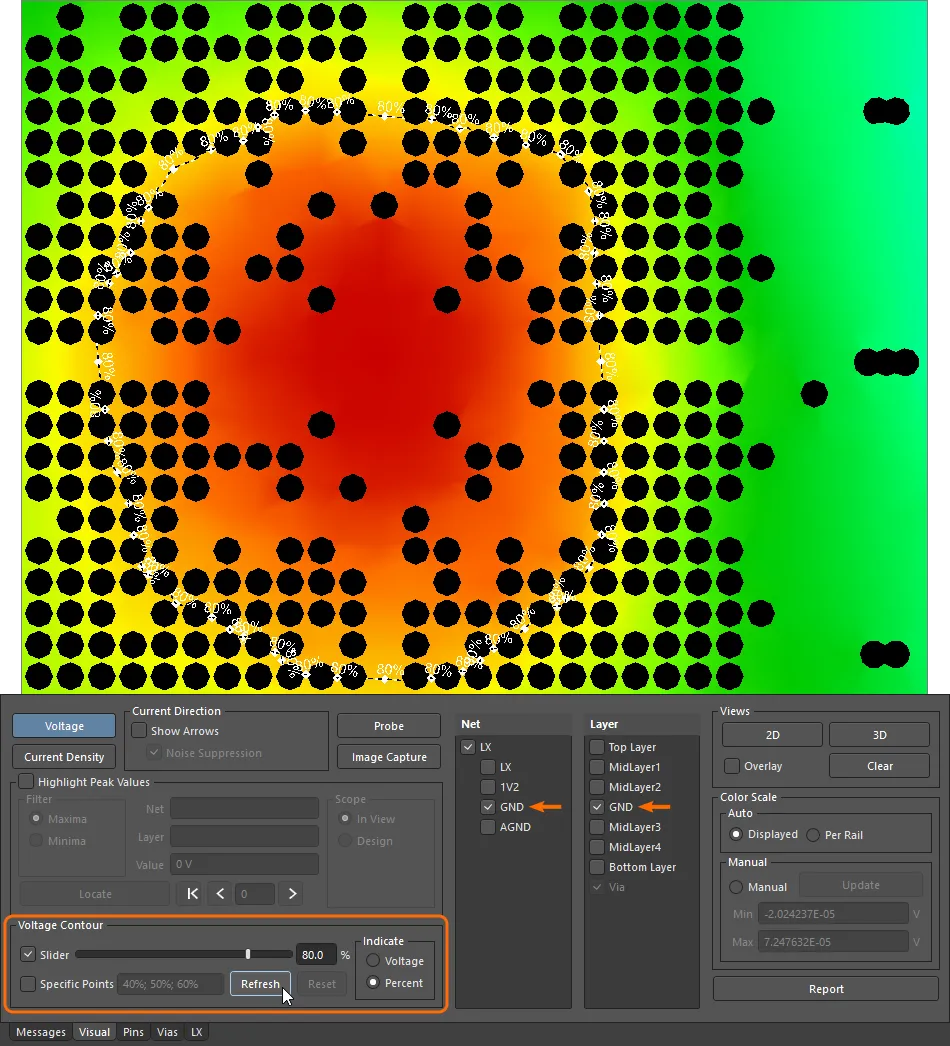

電圧コンター

上記のようにSMPSのリモートセンシングラインを最適に配置する判断は、PDN AnalyzerのVoltage Contour機能の多様な用途の一つであり、基板レイアウト上の主要な電圧遷移点をグラフィカルに示します。

この機能により、PCB Editorの表示レイヤー上に破線の電圧コンターラインをオーバーレイ表示できます。複数のコンターラインを指定でき、ネットワークの電圧降下に対する割合、または実電圧として表示できます。詳細はIndicateオプションを参照してください。

指定した割合ポイントのコンターライン一式に加えて、Sliderオプションを使用して追加のラインを含めることもでき、ラインの遷移点を連続的に調整して設定できます。

たとえばSMPSの適切な正側負荷センシング点を決めるには、センスラインが負荷での電圧降下のうち、たとえば20%未満の範囲内で接続されることが望ましいでしょう。上記のSMPS-sense例では、U5(S+)からのセンスライントラックは、U4負荷ピン(左側)と20%電圧コンターラインの間の任意の都合のよい位置で、1V2ネットワークの電源シェイプに接続します。

同様に、SMPS(U5)の負側センスライン(S-)の適切な取り出し位置を決めるには、GNDレイヤーにおける負荷(U4)のリターンパスに対して、たとえば80%の電圧コンターラインを設定できます。この場合、負荷リターン電流が負方向であるため、負側センスライン接続に望ましいGNDシェイプの位置は、80%コンターラインの外周内になります。

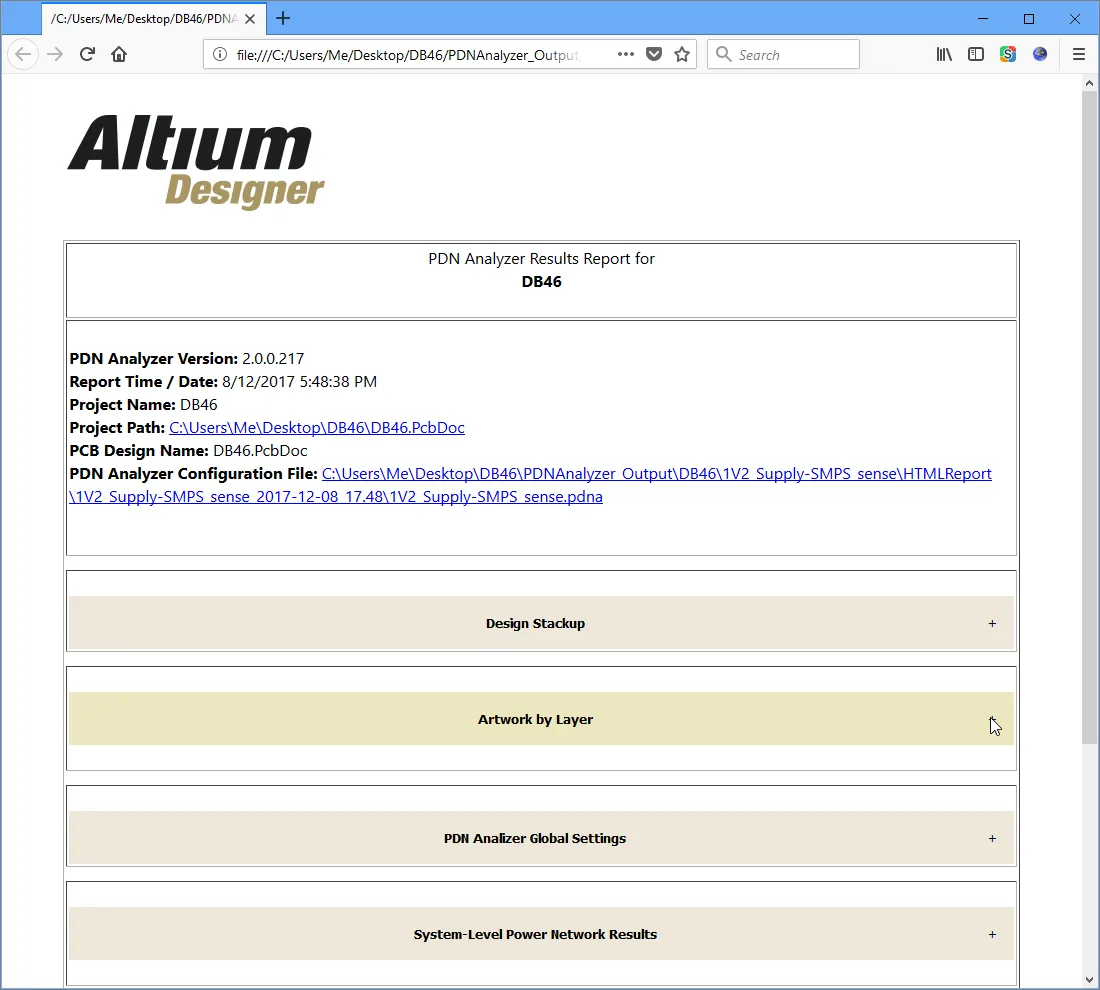

解析レポート

電源インテグリティ解析の結果を保存し、後で精査したり関係者へ配布したりするために、PDN AnalyzerはデータおよびドキュメントのReport機能を提供します。Report機能は、現在の解析結果と基板設計そのものの両方について、グラフィックスとデータを含む非常に包括的なHTMLベースのドキュメントを生成します。

HTML ReportダイアログでReportオプションを設定するには、 ボタンを選択します。Resultsの含有チェックボックスをオンにして、Reportに含める詳細度を設定し、Reportフォルダー(

ボタンを選択します。Resultsの含有チェックボックスをオンにして、Reportに含める詳細度を設定し、Reportフォルダー( )に含めるキャプチャ画像を確認します。解析結果画像をキャプチャするには、メインインターフェースの

)に含めるキャプチャ画像を確認します。解析結果画像をキャプチャするには、メインインターフェースの ボタンを使用します。

ボタンを使用します。

ボタンをクリックして対話型HTML Reportを生成し、その格納フォルダーを開きます。このフォルダーには、すべての画像(キャプチャしたものを含む)と、関連する解析設定ファイル(

ボタンをクリックして対話型HTML Reportを生成し、その格納フォルダーを開きます。このフォルダーには、すべての画像(キャプチャしたものを含む)と、関連する解析設定ファイル(*.pdna)が含まれます。