PCB 設計の改善

はんだマスク拡張ルールのデフォルトが 0 mil に変更(Open Beta)

パッドスタックのデフォルトに関する IPC-7351B 規格では、はんだマスク開口は通常ランド サイズと 1:1 の比率であることを踏まえ、Solder Mask Expansion ルール(PCB ドキュメント内)およびルール駆動のはんだマスク拡張(PCB ライブラリ ドキュメント内)の値は、デフォルトで 0 mil に設定されるようになりました(従来は 4 mil)。

PCB ライブラリ (*.PcbLib) では、これらの新しいデフォルト値のサポートはライブラリ レベルで提供され、そのライブラリ内で作成されるすべてのコンポーネント フットプリントに継承されます。同じ PCBlib を以前のバージョンの Altium Designer で開くと、すべてのオブジェクトのルール駆動はんだマスク拡張は 4 mil と表示され、このリリース以降で開くと 0 mil と表示されます。以下はパッド オブジェクトの例です。

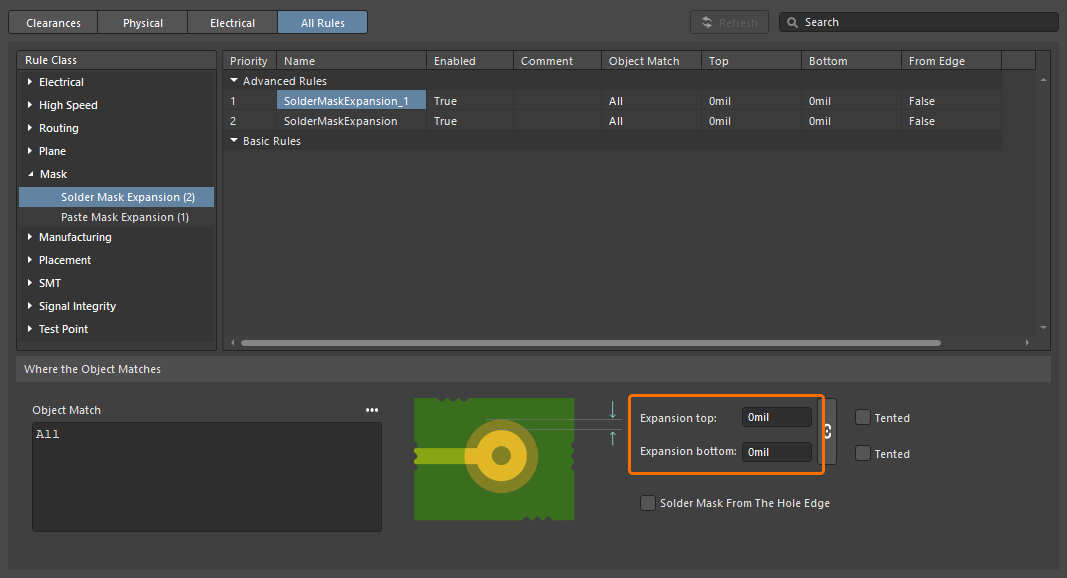

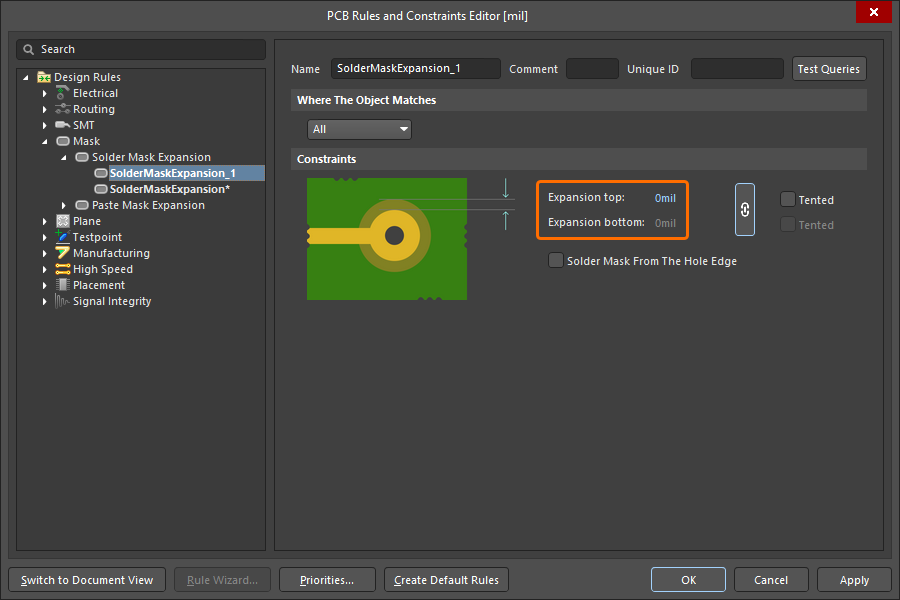

PCB ドキュメント(*.PcbDoc)では、既存のすべての Solder Mask Expansion ルールは初期値を保持します。新規作成されるルールに使用されるデフォルト値は、そのルールが作成された Altium Designer のバージョンによって決まり、別のバージョンの Altium Designer で開いても変更されません。したがって、以前のバージョンの Altium Designer で作成され、他の任意のバージョンで開かれた場合のデフォルトは 4 mil の拡張であり、このリリース(またはそれ以降)で作成され、他の任意のバージョンで開かれた場合のデフォルトは 0 mil の拡張です。以下に示すとおりです。

Constraint Manager で新規作成された Solder Mask Expansion デザインルール。

PCB Rules and Constraints Editor ダイアログで新規作成された Solder Mask Expansion デザインルール。

このリリースで新規作成されたドキュメントを表示する際に、新しい 0 mil のデフォルト拡張が正しく表示されるよう、該当パネル(PCB Library、Manufacturer Part Search、Components、および Explorer パネル)の関連プレビューウィンドウも更新されました。

Solder Mask Expansion デザインルールの詳細については、Mask Rule Types ページを参照してください。

Constraint Manager の改善

クラスをフィルタリングする機能を追加

多数のクラスを扱う作業を容易にするため、Constraint Manager の Clearances ビューにクラスをフィルタリングする機能が実装されました。これにより、クラスのフィルター(またはグループ化)を作成し、クリアランスマトリクスの対象を絞ったサブセットを切り替えながら作業できます。

Clearances ビューの右上にある  ボタンを使用すると、フィルターの作成、編集、削除、有効化/無効化を行えるポップアップにアクセスできます。

ボタンを使用すると、フィルターの作成、編集、削除、有効化/無効化を行えるポップアップにアクセスできます。

クリアランスマトリクスの操作の詳細については、Defining Design Requirements Using the Constraint Manager ページを参照してください。

Draftsman の改善

Draftsman ドキュメントへの DXF インポートを強化(Open Beta)

この機能により、製造図面ドキュメント(*.PCBDwf、*.HarDwf、*.MbDwf)への DXF ファイル バージョン R12 以降のインポートがサポートされます。スプラインを含む DXF ファイルのインポートもサポートされるようになりました。

DXF ファイルのインポートの詳細については、Draftsman Placement & Editing Techniques ページを参照してください。

Wire Bonding の改善

パネル内の Bond Wire プリミティブ

Bond wire は、以下の場所で正しいタイプ(Bond Wire)で表示されるようになりました。

Bond wire プリミティブを選択すると、デザインスペース内のその bond wire が選択/ハイライトされます。

さらに、bond wire の表示を切り替えるための対応する Show Bond Wires オプションが、領域の右クリック コンテキストメニューでも利用可能になりました。

Wire bonding の詳細については、Wire Bonding ページを参照してください。

3D-MID Design の改善

3D-MID デザインルールチェック(Open Beta)

このリリースでは、3D 基板上に配線されたトラックに対して、Width、Clearance、Length、および Matched Lengths ルール違反のバッチ Design Rule Checking(DRC)が提供されます。生成される DRC レポートにはこれらすべてのチェックに関する情報が含まれますが、デザインスペース内でハイライト表示されるのは clearance 違反のみである点に注意してください。

詳細については、3D-MID Design ページを参照してください。

Multi-board Design の改善

ハーネス エントリの「Termination Type」を定義可能に

ハーネス エントリの Termination Type をマルチボード回路図上で定義できるようになりました。利用可能な終端タイプは次のとおりです。

-

Connector – PCB 上の嵌合コネクタに接続する際に使用される標準オプションです。通常は標準的な基板実装コネクタが含まれます。

-

Crimps/Ferrules – 個々のワイヤは、PCB 側のコネクタに挿入される前に、圧着端子またはフェルールで終端処理されます。

-

Wire termination – ワイヤはハーネス端で切りっぱなしにされ、PCB に直接ねじ止めまたははんだ付けされます。これは、一部の JST コネクタのようなワイヤ対基板の直接接続で一般的です。

この情報は、選択したハーネス エントリおよび対応するモジュール エントリのプロパティに反映されます。

マルチボード回路図での接続操作の詳細については、Working with Connections ページを参照してください。

Harness Design の改善

ワイヤ同期の強化

ワイヤ ブレークで接続されたハーネス ワイヤは、Design Item ID が異なっていても認識されるようになりました。さらに、同じワイヤ ブレークで接続され、同じデジグネータを持つすべてのワイヤ セグメントが、部品番号、コメント、色、およびすべてのパラメータについて比較されるようになりました。差異が見つかった場合は、Mismatched parameters in connected wire segments 違反が報告されます。また、パラメータ間の競合が検出されたことを示す警告が、ワイヤおよびワイヤ ブレークの Properties panel に表示されます。警告内の Synchronize をクリックすると Conflict Wire Parameters ダイアログが開き、ワイヤ セグメントに使用するパラメータを選択できます。

ジャンクション ポイント上に被覆を配置可能に

ハーネス レイアウト図面(*.LdrDoc)で、ジャンクション ポイント(2 本以上のバンドルが合流するレイアウト図面上の接続点)の over にハーネス被覆を適用/延長できるようになりました。これにより、複数のコネクタを含むセクションで、ジャンクション ポイント間ごとに個別のハーネス被覆を設ける必要がなくなります。

さらに、被覆の開始位置はそのパスの最も左上の点として扱われるようになり、そのパスには被覆が載っているバンドルのみが含まれるようになりました。

詳細については、Creating the Layout Drawing ページを参照してください。

BOM の Quantity フィールドを特定オブジェクトで「As Required」に変更

ワイヤ、ケーブル、およびハーネス被覆は長さベースのオブジェクトであり、その値は Length フィールドに表示されます。混乱を避けるため、製造図面ドキュメント(*.HarDwf)内の部品表テーブルおよび ActiveBOM ドキュメントにおけるワイヤ、ケーブル、およびハーネス被覆エントリの Quantity フィールドは、現在 As Required になっています。

詳細については、Managing Your Bill of Materials (BOM) with ActiveBOM ページを参照してください。

配線リストでのピン グループ化を改善

ハーネス製造ドキュメント(*.HarDwf)に配置された配線リストにおけるピン グループ化が改善されました。このリリース以降、自動グループ化は最も多くのワイヤを持つコネクタに適用され、そのすべてのキャビティが、以下の画像に示すように配線リストの From 列で正しくグループ化されます。

ハーネス製造業者向け Excel Workbook

Output Job を通じて、ハーネス製造業者が使用するデータを含む単一の Excel Workbook を生成する機能が追加されました。これを実現するため、新しい出力機能 Manufacturing Data が Report Outputs セクションで利用可能です。

生成される Workbook には、4 つの個別シートが含まれます。

-

Bill of Materials – 見積もりを迅速に作成するのに役立ちます。

-

Wiring List – ワイヤ加工機で使用します。

-

Labels – ハーネス バンドル用に印刷する物理ラベルの概要で、Zebra などのプリンタで使用します。

-

Coverings – ハーネス バンドルに適用する被覆の概要です。

製造データ出力のソースとして、ハーネス設計プロジェクトの ActiveBOM ドキュメントを使用することを推奨します。

詳細については、Preparing Reports ページを参照してください。

プラットフォームの改善

.NET 8 への切り替え

このリリースより、Altium Designer は .NET 6 から .NET 8 に切り替わります。.NET 8 は Altium Designer の一部として同梱されており、一般的なパフォーマンス向上を含む、.NET の新しい機能や進展を活用できるようになります。

-

この切り替えに伴い、Altium Designer を実行するベース OS として Windows 7 および 8.x はサポート対象外となりました。

-

.NET 8 と互換性がないことが確認されたサードパーティ製拡張機能は、このリリースからソフトウェアから削除されています。今後、これらの拡張機能の更新版が Altium Designer 26.1 (またはそれ以降)に対応した場合は、beta.program@altium.com まで連絡して、インストールに再追加してもらってください。

詳細については、System Requirements ページを参照してください。

WebView2(オープンベータ)

このリリース以降、Altium Designer 内のブラウザ関連要素(例:Home ページ)には WebView2 が使用されます。これにより、Windows を更新するだけで、Altium Designer 内で最新の Web ブラウザエンジンを利用できます。

この機能はオープンベータであり、System.UseWebView2 オプションを Advanced Settings dialog で有効にすると利用できます。無効になっている場合、または接続先 Workspace が WebView2 をサポートしていない場合は、CefSharp v.126 が自動的に使用されます。

データ管理の改善

プロセスワークフローを使用した Workspace プロジェクトのコピー機能

定義済み(かつ有効化済み)のプロセスワークフローを使用して Workspace プロジェクトのコピーを作成できるようになりました。Workspace プロジェクトを開いた状態で、Projects panel のプロジェクト項目を右クリックし、Make a copy of the managed project サブメニューから有効化されたプロセス定義(Project Creations テーマの一部)を選択すると、そのプロセスの基盤となるワークフローに従ってプロジェクトのコピーが開始されます。

詳細については、Process-based Project Creation ページを参照してください。

モデルのリリース時にライフサイクル状態を保持する機能を追加

接続された Workspace にコンポーネントモデル(schematic symbol、PCB footprint、simulation model、または harness wiring)の新しいリビジョンをリリースする際に、モデルの現在のライフサイクル状態を保持できるようになりました。

この機能は、Allow to skip lifecycle state change for new revisions の運用権限が割り当てられているユーザーのみ利用可能です(詳細は Setting Global Operation Permissions for a Workspace を参照してください)。

Workspace コンテンツの編集の詳細については、Creating & Editing Content ページを参照してください。

設計レビューコメントのリンク

設計レビューの一環としてコメントが追加されると、そのレビューへのリンク(From <DesignReviewName>)が、Comments And Tasks panel 内の対応する項目およびそのコメントのコンテキストコメントウィンドウ(設計空間内)に表示されるようになりました。リンクをクリックすると、既定のブラウザの新しいタブでレビューの Overview ページが開きます。

ドキュメントコメントの詳細については、Document Commenting ページを参照してください。

追加の単位対応データ型のサポート

Altium Platform 上の接続された Workspace でコンポーネントテンプレートの一部としてユーザーパラメータを定義する際、以下の追加の単位対応データ型がサポートされるようになりました。

-

面積(mm2)

-

バール(bar)

-

ビット

-

カンデラ(cd)

-

10 進数

-

整数

-

ジュール(J)

-

ルーメン(lm)

-

ミリメートル(mm)

-

パスカル(Pa)

-

ポンド毎平方インチ(psi)

-

回転毎分(rpm)

-

ジーメンス(S)

-

テスラ(T)

これらの新しい単位型を使用するパラメータは、Components panel、コンポーネントエディタ(single および batch の両編集モード)、さらに Library Importer と Components Synchronization 機能(Properties panel の Parameter Mapping セクション内)など、ソフトウェアのさまざまな領域でサポートされます。

単位対応コンポーネントパラメータデータ型の詳細については、Component Templates ページを参照してください。

Components Synchronization 使用時に Part Choices を同期する機能

Components Synchronization 機能および関連する Components Synchronization Configuration ドキュメント(*.CmpSync)を使用して、part choice 情報を定義および同期する機能が追加されました。同期されるパラメータは、ドキュメント内でテーブルを選択した際に Properties panel の Part Choices Mapping 領域で制御できます。ボタンを使用して part choice パラメータのペア(Manufacturer / Part Number)を追加・削除し、ドロップダウンメニューオプションでマッピングを定義します。マッピングが定義されると、対応するパラメータがドキュメントのグリッド領域の Part Choice n 列の下に表示されます。

なお、同期プロセスを実行すると、手動で追加された part choice を除き、コンポーネントの part choice リストは新しくマッピングされた part choice で上書きされます。

Components Synchronization 機能の詳細については、Component Database to Workspace Data Synchronization ページを参照してください。

Workspace への接続問題に関する新しい警告

Workspace への接続に問題があり、プロジェクトドキュメントの最新の VCS 状態を更新できない場合、Refresh VCS Statuses コントロール(関連するツールチップ警告付き)が Projects panel のプロジェクト項目の横に表示されるようになりました。接続が復旧したら、その項目をクリックして VCS 状態を再同期し、最新の変更を確認できます。

ドキュメント状態の表示の詳細については、Managing Project Documents ページを参照してください。

BOM CoDesign の改善

BOM 比較結果からサプライヤ関連フィールドを除外(オープンベータ)

BOM CoDesign 機能を使用して ActiveBOM と選択した Managed BOM を比較する際、詳細設定が無効の場合、サプライヤ関連データ(Supplier および Supplier Part Number パラメータ)は、ActiveBOM ドキュメントからアクセスした Properties panel の Related BOMs タブにある Differences section から除外されます。

比較結果の確認の詳細については、BOM CoDesign ページを参照してください。

インポート/エクスポートの改善

Allegro 設計インポートの強化

必要なすべての設定ファイルが Allegro2Altium.bat ファイルに含まれるようになりました。これは Altium Designer のインストールに含まれるバッチファイルで、Allegro バイナリ(*.brd または *.dra)ファイルを ASCII 形式に変換するために使用されます(その設計/ライブラリが Altium Designer と同じ PC 上にない場合)。したがって、インポートに必要なのはこの bat ファイルのみで、追加ファイルは不要です。

詳細については、Importing a Design from Allegro ページを参照してください。

xDX Designer 設計からのコンポーネント代替ビューのサポート

xDX Designer 設計をインポートする際、生成された回路図ドキュメントおよび回路図ライブラリドキュメントの両方で、コンポーネントの代替ビューモードがサポートされるようになりました。

詳細については、Importing a Design from xDX Designer or DxDesigner ページを参照してください。

Altium Designer 26.1 で正式公開となった機能

以下の機能は、このリリースで正式に Public となりました。

Altium Designer 26.1 の追加機能