Working with the Differential Pairs Routing Design Rule on a PCB in Altium NEXUS

Rule category: Routing

Rule classification: Unary

Summary

This rule defines the routing width of each net in a differential pair, and the clearance (or gap) between the nets in that pair. Differential pairs are typically routed with specific width-gap settings to deliver the required differential impedance needed for that net-pair.

► Learn more about Differential Pair Routing

► Learn more about Controlled Impedance Routing

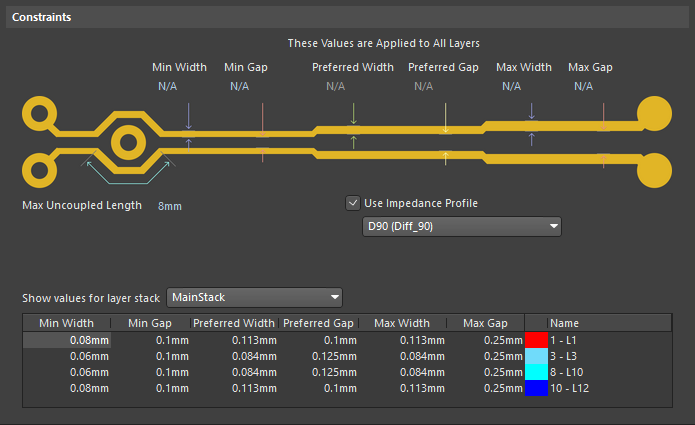

Constraints

Default constraints for the Differential Pairs Routing rule.

- Min Width - specifies the minimum permissible width to be used for tracks when routing the differential pair.

- Min Gap - specifies the minimum permissible clearance between primitives on different nets within the same differential pair. Gap settings are used as the differential pair is being routed, but not during rule checking, this requires a Clearance Constraint rule - refer to the Tips below for more information on how to manage this.

- Preferred Width - specifies the preferred width to be used for tracks when routing the differential pair.

- Preferred Gap - specifies the preferred clearance between primitives on different nets within the same differential pair.

- Max Width - specifies the maximum permissible width to be used for tracks when routing the differential pair.

- Max Gap - specifies the maximum permissible clearance between primitives on different nets within the same differential pair.

- Max Uncoupled Length - specifies the value for the maximum permissible uncoupled length between positive and negative nets within the differential pair.

- Use Impedance Profile - this option becomes available when there is at least one impedance profile defined in the Layer Stack Manager. When enabled, use the drop-down to select the required impedance profile. When the rule is configured in this mode, the Preferred Width and Preferred Gap required on each routing layer are calculated as part of the specified impedance profile. Once the rule is defined, as you route a differential pair that falls under the scope of the rule, the track widths and pair gap will automatically be set to the values required for that layer, to meet the specified impedance.

► Learn more about Configuring the Layer Stack for Controlled Impedance Routing - Show values for layer stack - this option appears in the dialog when there are multiple layer stacks defined in the Layer Stack Manager. If the board includes multiple layer stacks then the Differential Pairs Routing Constraints must be configured for each of the layer stacks, using either the all-layer fields above the image or the layer-specific fields in the Layer Attributes Table.

► Learn more about Defining and Configuring Substacks - Layer Attributes Table - the grid region at the bottom of the dialog displays all signal layers defined in the layer stack, unless the Use Impedance Profile option is enabled. If this option is enabled, then only the layers available as part of the selected impedance profile will be displayed. The minimum, maximum and preferred width and gap constraints are displayed, as well as other layer-specific information. The routing Width and Gap fields can be set globally by defining the values in the constraint fields above the image, or individually by typing values directly into the table. When the Use Impedance Profile option is enabled, the required width entries will be automatically calculated and entered for each layer in the table. In this mode the Preferred Width and Preferred Gap values cannot be edited, but the Min and Max values can.

How Duplicate Rule Contentions are Resolved

All rules are resolved by the priority setting. The system goes through the rules from highest to lowest priority and picks the first one whose scope expression matches the object(s) being checked.

Rule Application

Online DRC, Batch DRC, interactive routing (and re-routing), autorouting, interactive length tuning (Min Gap is applied), and when interactively modifying the pair, such as sliding a track segment of one of the nets in the pair.

Notes

- While the width of each net in a differential pair is monitored by the applicable Differential Pairs Routing rule (and not by a Width rule), clearance checking between the nets in that pair is still governed by the applicable Clearance design rule. In other words, a Clearance rule must be defined that targets the differential pair (on the specific layer where needed) with its connective checking mode set to Same Differential Pair, and whose clearance is set to be equal to, or lower than, the value for the Min Gap constraint defined for that layer as part of the applicable Differential Pairs Routing rule.

- The clearance from a net in a differential pair to any other electrical object that is not a part of the pair is monitored by the applicable Clearance rule.

- While the optimal width-gap settings may be achievable for most of the board, there will often be areas, such as under a BGA component, where smaller and tighter width-gap settings must be used. As well as switching the Width-Gap settings interactively, this requirement can also be achieved by defining multiple differential pair routing rules - a lower-priority rule that targets the differential pair across the board, and a higher-priority rule that targets the differential pair in specific areas. You then target the differential pair in a specific area by defining a Room Definition rule and use that room as part of the scope of a differential pair routing rule.

- Differential Pair classes, for use in rule scoping, can be defined on the schematic.