PDN Analyzer(PDNA)应用的使用相对直观,基本流程是:设置 PI-DC 仿真的网络参数、运行仿真,然后解读结果。PDN Analyzer 在电源网络仿真中使用的数据直接来自当前加载的 PCB 设计工程;你可以迭代编辑该工程以提升供电路径的电源完整性,然后重新运行 PDN 仿真来验证结果。

本演示指南使用 Altium 提供的两个参考设计:

-

The SpiritLevel-SL1 project: 下载 ZIP

-

The DB46 Xilinx Daughter Board project: 下载 ZIP

此外,PDN Analyzer 的安装包还包含 SpiritLevel PCB 工程以及若干分析配置文件示例。可通过 PDNA File » Explore Samples 菜单选项访问并解压该工程与示例。

本指南假设你的 Altium Designer 实例中已提供 PDN Analyzer,并且你对所使用的 PI-DC(直流电源完整性)原理有基本了解。

关于如何访问 PDN Analyzer 功能以及 PI-DC 仿真的基础知识,请参见 PDN Analyzer page。

PDN Analyzer 界面

PDN Analyzer 扩展的界面以 Altium Designer 的非模态窗口形式调用,可放置在工作区任意方便的位置,或在可用时放到另一块屏幕上。要打开主 PDN Analyzer 窗口,请打开某个工程的原理图或 PCB 文档,然后从 Tools 菜单(Tools » PDN Analyzer)中选择该应用。

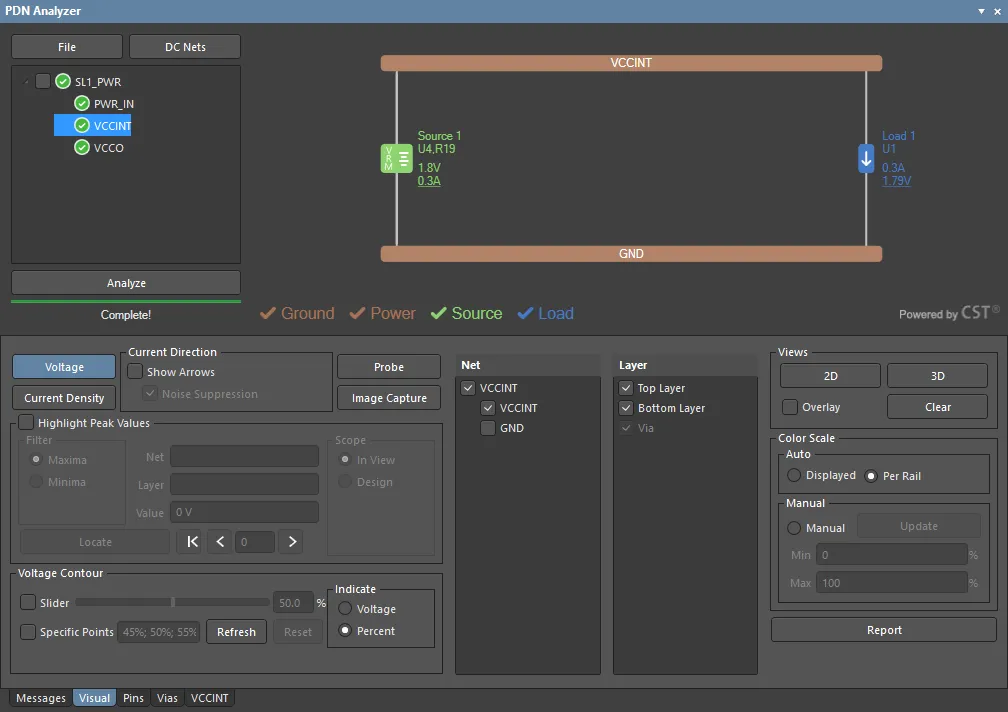

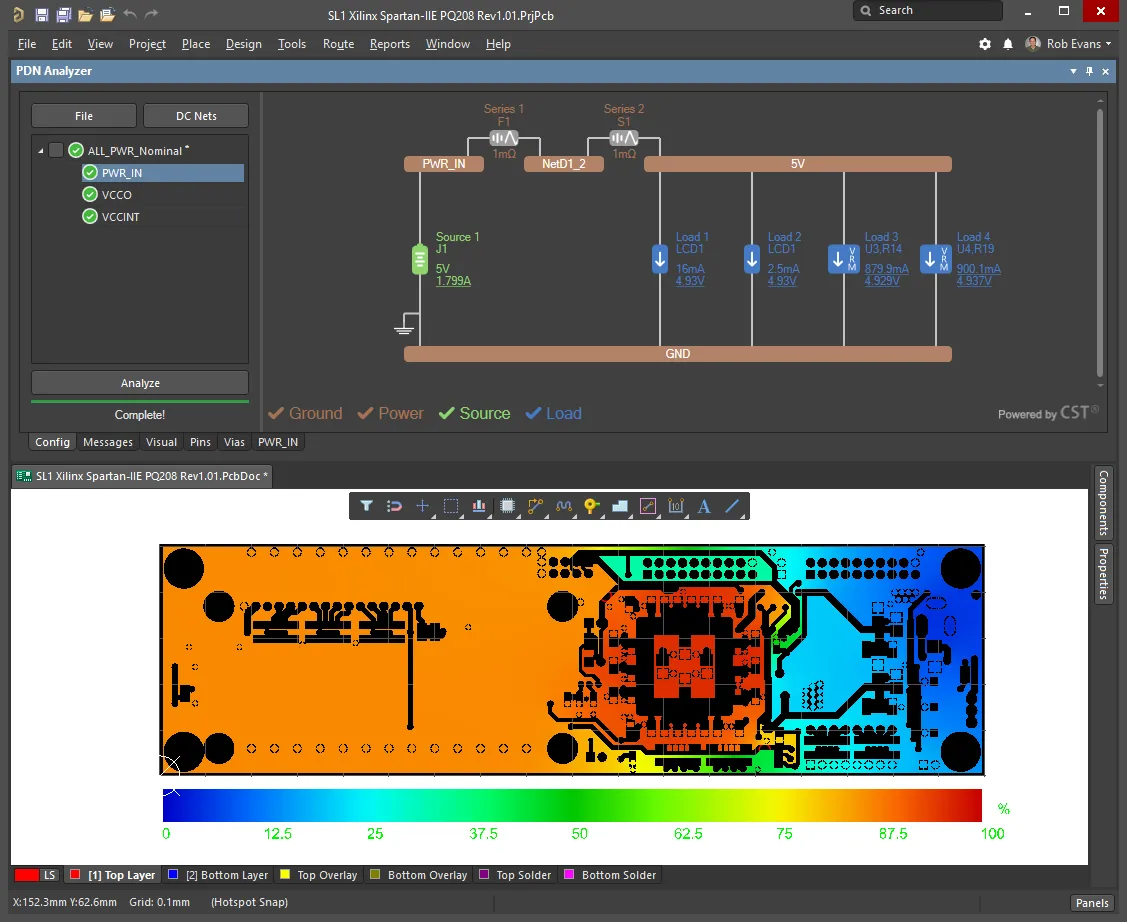

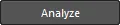

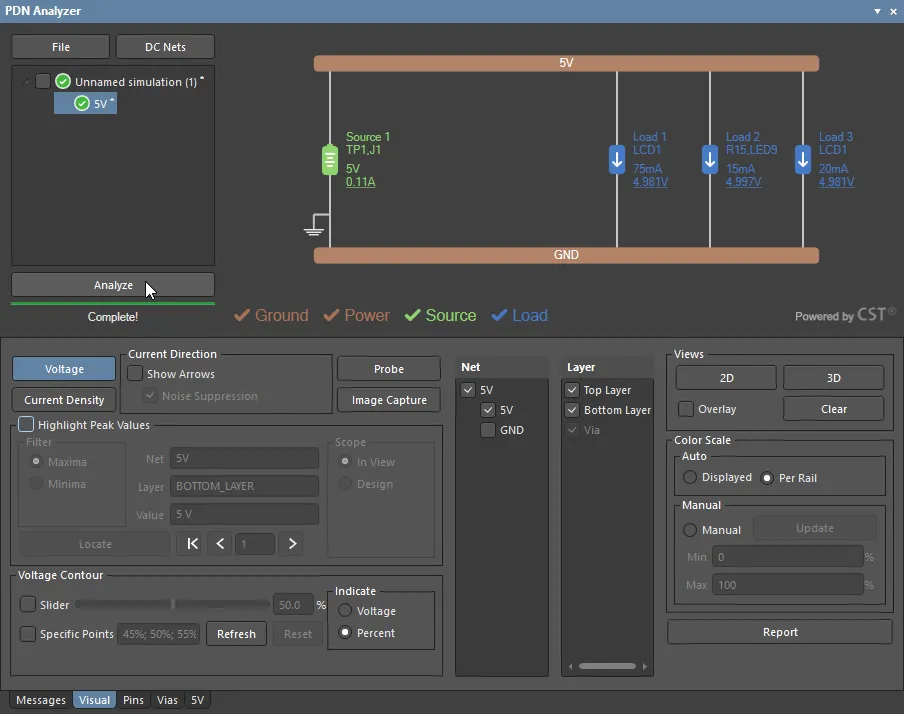

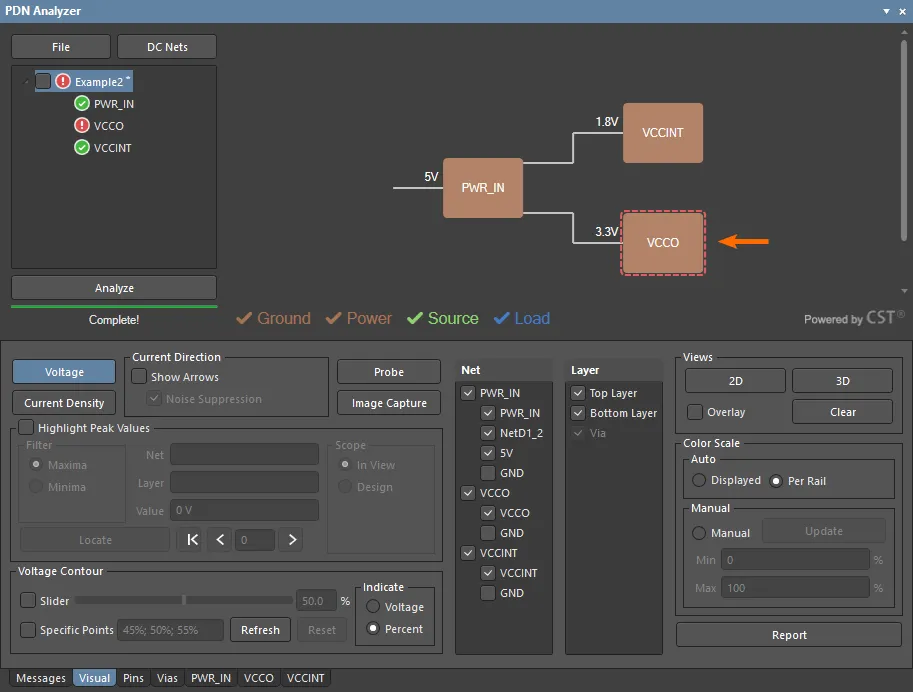

PDN Analyzer GUI:已选择单个电源网络。显示与结果配置位于下方面板区域。

PDN Analyzer GUI:已选择单个电源网络。显示与结果配置位于下方面板区域。

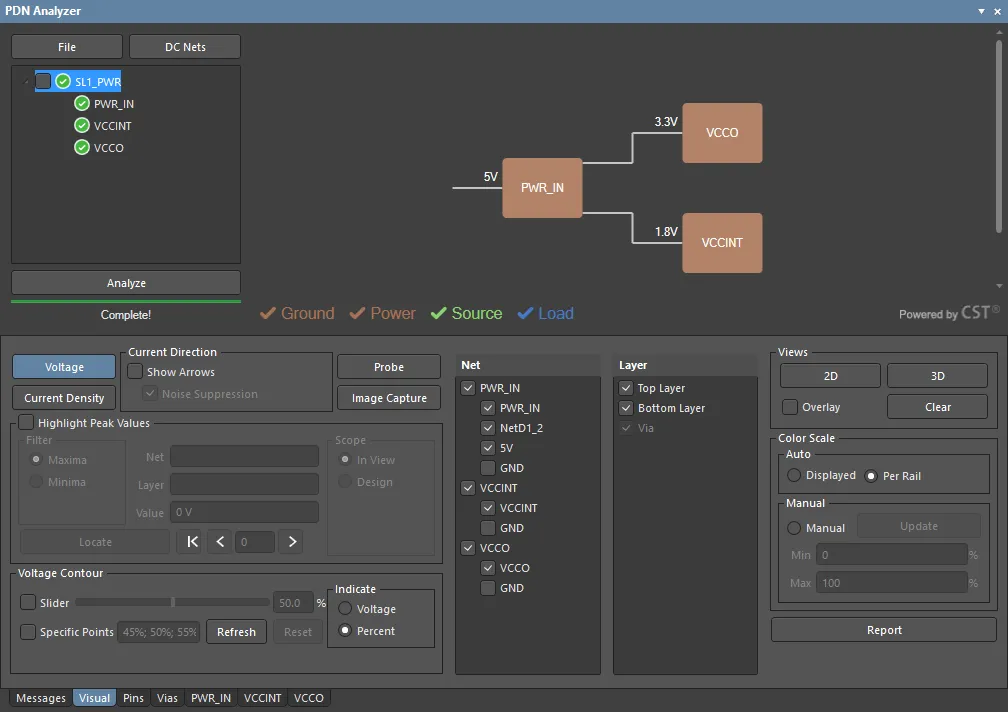

PDNA 窗口 GUI 的布局为:上半部分用于文件/网络控制以及对当前所选电源网络的交互式表示;下方面板区域用于访问分析选项、显示设置与结果数据。PDNA 版本 2 支持多个相互连接的网络,可将整个 PCB 设计的直流电源完整性按层级结构进行分析,或按单个电源网络分别分析。

PDN Analyzer GUI:已选择完整的电源网络层级结构。包含的网络与层的显示由下方面板区域控制。

PDN Analyzer GUI:已选择完整的电源网络层级结构。包含的网络与层的显示由下方面板区域控制。

PDN 界面还提供紧凑屏幕模式(File » Compact Layout),该模式不包含下方面板区域,适合在 Altium Designer 主界面中进行水平/垂直停靠。要为紧凑或标准屏幕模式启用停靠,请在 PDNA 界面标题栏上右键,从上下文菜单中选择 Allow Dock,然后选择 Horizontally 或 Vertically 选项。

有关 PDN Analyzer 面板用户界面的详细信息,请参见下方可折叠章节。

PDN Analyzer Panel

布局模式

可停靠的 PDN Analyzer 面板最好与软件的 PCB Editor 配合使用,这样分析运行后的可视化结果可立即在设计的铜箔布局中看到。在浮动(未停靠)模式下,可将面板移到第二显示器以保持对 PCB Editor 的可视访问;或者将面板在主设计屏幕中垂直/水平停靠,与 PCB Editor 共享屏幕空间。

对于后者,面板提供紧凑界面模式,会将其主要配置窗格移到单独的选项卡(Config)中。要切换到该模式,请在配置窗格/选项卡中的  按钮下拉菜单里选择 Compact Layout 选项。

按钮下拉菜单里选择 Compact Layout 选项。

在紧凑布局模式下,Configuration 窗格改为通过选项卡访问,从而为 PCB Editor 保留屏幕空间。

在紧凑布局模式下,Configuration 窗格改为通过选项卡访问,从而为 PCB Editor 保留屏幕空间。

配置

Configuration 窗格(或 Config 选项卡)用于仿真网络控制,并提供对当前所选电源网络的交互式图形表示。

仿真与网络管理

Configuration 窗格/选项卡左侧区域用于仿真文件管理,并以层级视图显示仿真中已加载的电源网络。可选择完整网络结构或单个电源网络。该区域的选项包括:

-

The

下拉菜单。

下拉菜单。

-

New Simulation – 基于单个电源/地网络启动新的 PDN 仿真。

-

Open – 打开先前保存的或示例仿真配置文件(

*.pdna)。

-

Save – 以当前名称将活动仿真配置保存到磁盘。

-

Save As – 以指定名称将活动仿真配置保存到磁盘。

-

Explore – 在活动仿真所在位置打开 Windows 文件浏览器。

-

Explore Samples – 在安装包示例工程所在位置打开 Windows 文件浏览器(以 zip 归档形式存储)——将该工程解压到方便的位置。注意:该工程还包含一组 PDN Analyzer 配置文件示例,每个示例对应特定的铜温度:25°C(标称)、100°C、175°C。

-

Compact layout – 上文所述的替代屏幕模式。

-

Right click options – 通过右键单击顶层仿真名称访问。

-

Import (1.x) – 加载从上一

1.xx 版本 PDN Analyzer(*.pidc_config)保存的仿真配置。

-

New Network – 在当前仿真配置中创建新的基础层网络。

-

Remove – 卸载所选仿真。

-

Delete – 从仿真中移除所选网络(在单个网络名称上右键时可用)。

-

Clear Results – 重置电源网络分析结果,包括上一次仿真运行缓存的结果。

-

Revert – 恢复上一次仿真分析结果及其对应配置。

-

Save – 以当前名称(

*.pdna)将活动仿真配置保存到磁盘。

-

Save As – 以指定名称将活动仿真配置保存到磁盘。

-

Copy – 克隆所选网络仿真。

-

Explore – 在 Windows 文件浏览器中打开当前仿真的

/PDNAnalyzer_Output 文件夹。注意:其中包含最近一次运行仿真的完整事件日志文件(PDNAnalyzer.log)。

-

Settings – 打开当前仿真配置的 Settings dialog。设置可导出/导入(

*.pdna.settings),并可重置为默认值。

该对话框包括:

-

Simulation 选项卡 – 指定物理板铜箔的金属电导率设置,以及层间连接过孔的重量(孔壁厚度)。

-

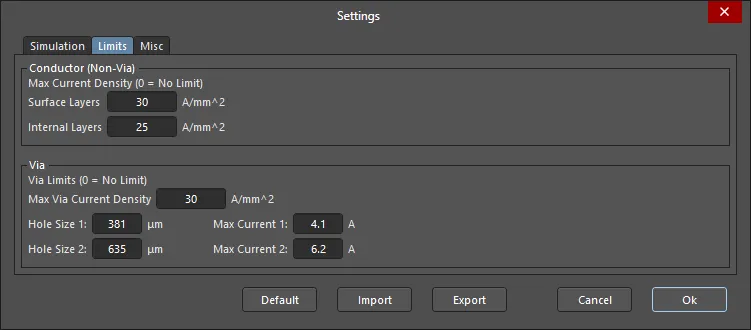

Limits 选项卡 – 指定仿真检测到的最大电流密度限制,分别针对铜层与两种尺寸的过孔。

-

Misc 选项卡 – 设置仿真参数,例如施加的电流密度单位、数据平滑(Noise Filtering),以及用于建立设计零电压参考的电压偏移方案。

-

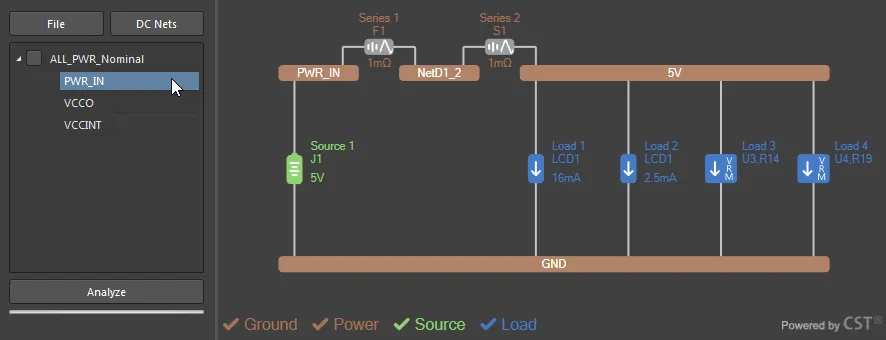

The

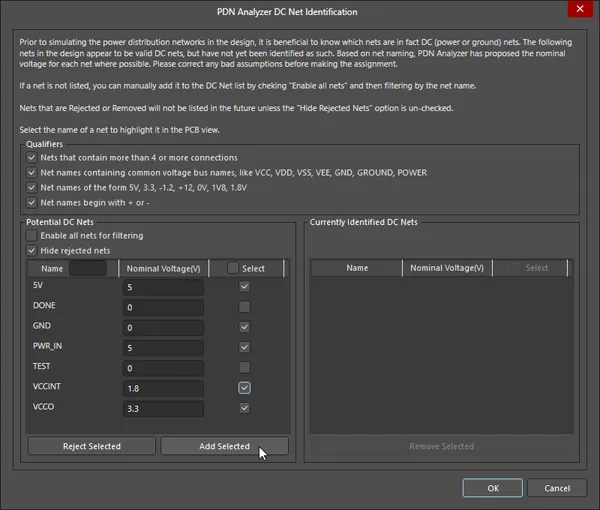

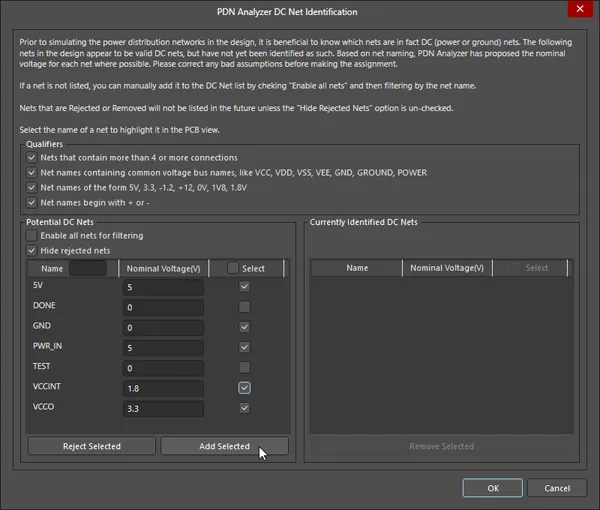

按钮,用于打开 PDN Analyzer DC Net Identification 对话框——在首次调用 PDN Analyzer 时也会打开。系统将尝试在当前 PCB 设计中自动检测合适的直流电源网络。

按钮,用于打开 PDN Analyzer DC Net Identification 对话框——在首次调用 PDN Analyzer 时也会打开。系统将尝试在当前 PCB 设计中自动检测合适的直流电源网络。

使用该对话框的选项来帮助正确识别直流网络及其标称电压等级。

-

Qualifiers – 如有需要,可取消选择限定条件过滤器,以便正确识别设计的直流网络。过滤器基于连接数量以及常见电源网络命名规则。

-

Potential DC Nets – 设计中已识别电源网络的表格列表。根据直流电源分析需要,可使用 Enable all 和/或 Hide rejected 选项来填充列表。

-

Name – 从板级设计网络数据中提取的网络名称。使用关联的搜索字段可按输入关键字过滤列表。

-

Nominal Voltage – 为电源网络输入合适的电压,作为分析的基础源数据。

-

Select – 使用复选框指定希望由 PDN 仿真注册(识别)的网络。

-

Reject/Add Selected – 使用

与

与  按钮管理哪些网络被填充到 Currently Identified DC Nets 列表中。

按钮管理哪些网络被填充到 Currently Identified DC Nets 列表中。

-

Currently Identified DC Nets – 将提供给 PDN 仿真的电源网络表格列表,由 Potential DC Nets 列表填充而来。

-

Select – 使用复选框选择将被

按钮移除的网络(从已识别网络列表移回到候选网络列表)。

按钮移除的网络(从已识别网络列表移回到候选网络列表)。

单击某个网络条目可在 PCB Editor 中交叉定位到该网络。

-

The

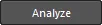

按钮,用于调用电源网络仿真与分析流程。当电源网络及其相关数据已完整配置时(由电源网络图中 Ground、Power、Source、Load 标签旁的勾选图标指示),该按钮将被启用。

按钮,用于调用电源网络仿真与分析流程。当电源网络及其相关数据已完整配置时(由电源网络图中 Ground、Power、Source、Load 标签旁的勾选图标指示),该按钮将被启用。

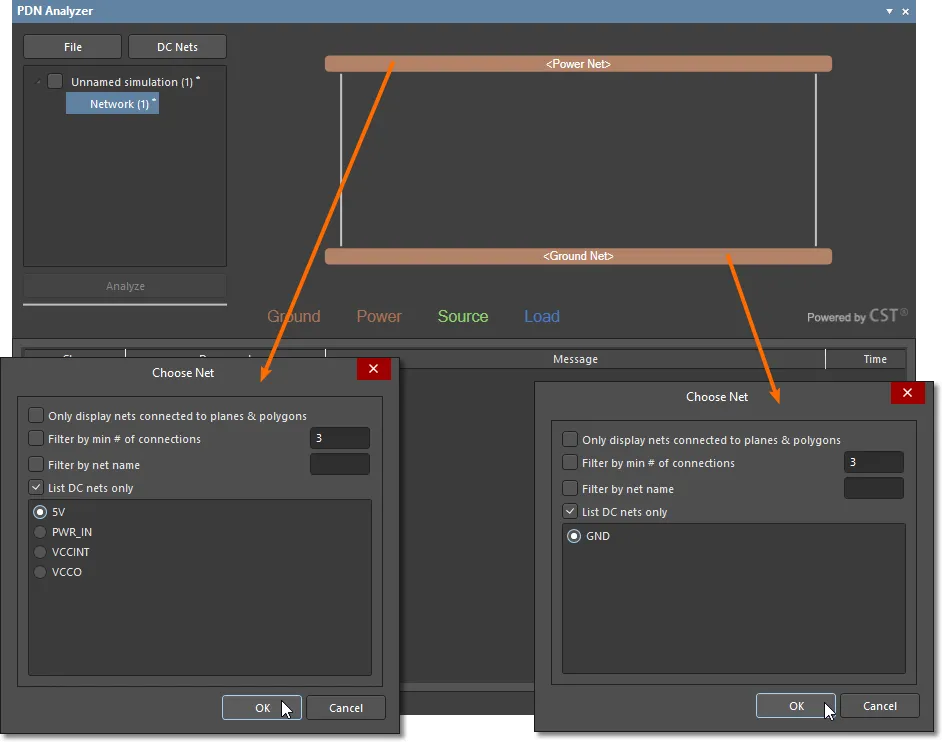

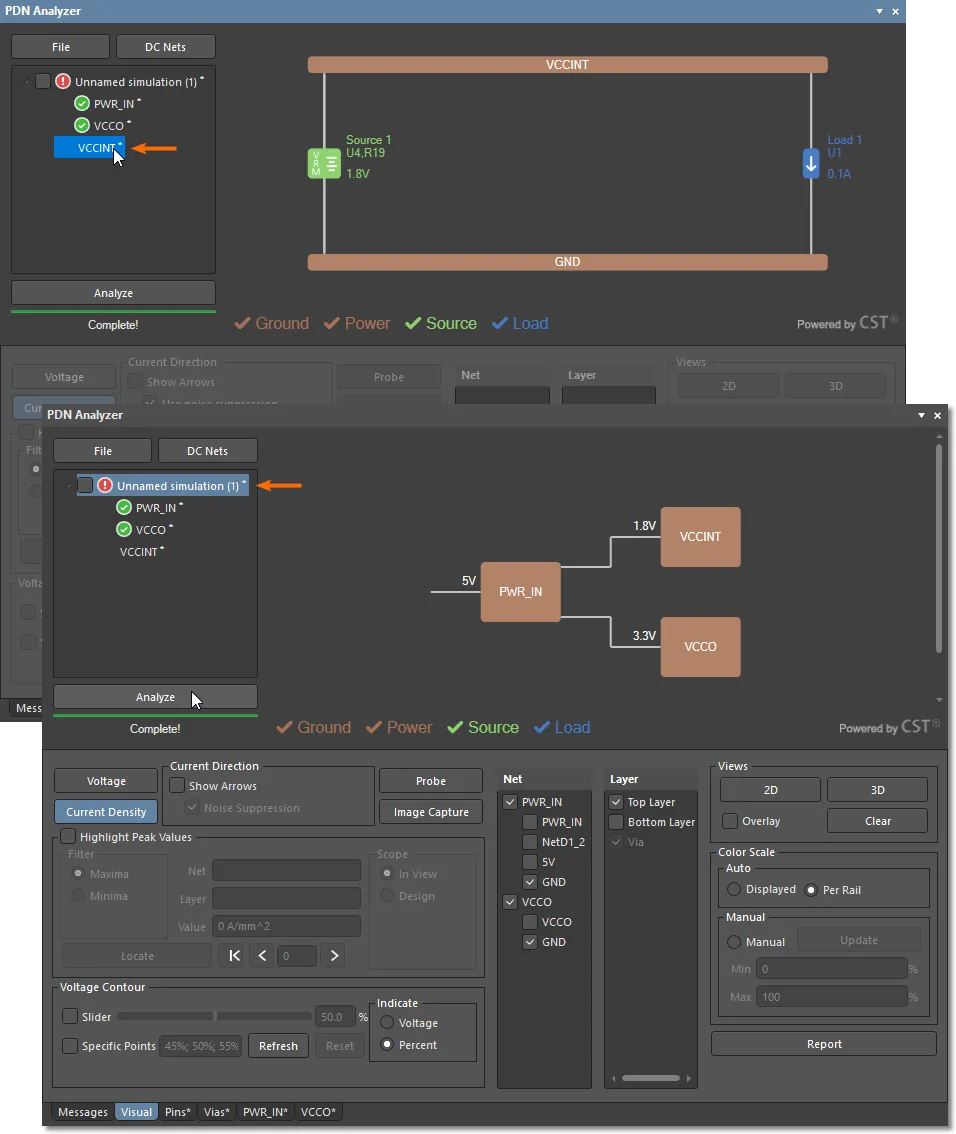

电源网络图形

Configuration 窗格的主体提供对仿真网络树(左侧)中所选电源网络结构的交互式图形表示。当选择顶层仿真名称时,图形会显示子电源网络的整体连通关系——双击某个子网络图形元素即可打开该子网络。该交互式图形也可用于基于 PCB 设计的网络数据与连通性来构建电源网络:可使用其右键选项,或通过双击图形元素来完成。

在配置图形或其某个元素上右键,可访问以下选项:

-

New Network– 在当前仿真中创建一个新的基础级网络(电源网与地网)。

-

Edit Net – 在 Choose Net 对话框中指定电源网络的设置(也可通过双击网络元素打开)。该对话框包含一个可选择的网络列表(仿真可用的网络,如在 PDN Analyzer Net Identification 对话框中定义;该对话框可通过

按钮打开),以及若干可用于限制列表范围的筛选选项。

按钮打开),以及若干可用于限制列表范围的筛选选项。

-

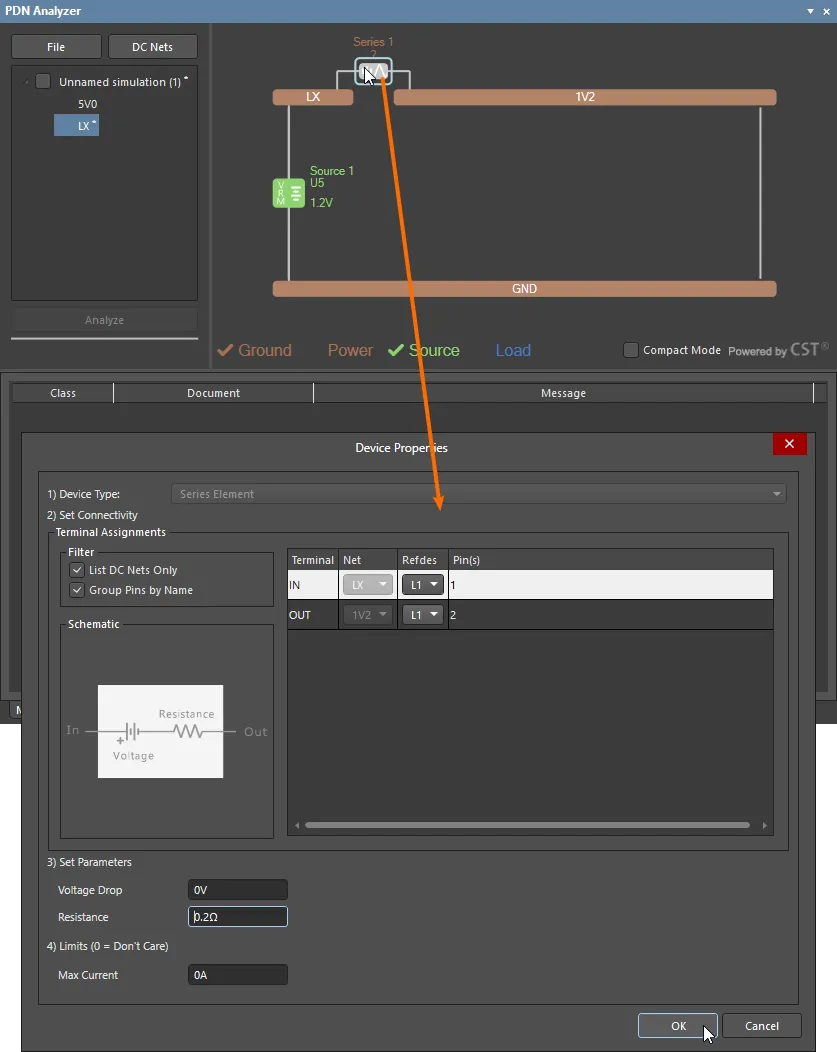

Extend Net – 用于通过一个串联元件将另一条网络添加到所选网络中,该串联元件将自动插入。附加网络在 Choose Net 对话框中选择,而插入的串联器件则通过双击其元素进入 Device Properties 对话框进行配置。更多信息请参见 通过串联元件扩展网络。

-

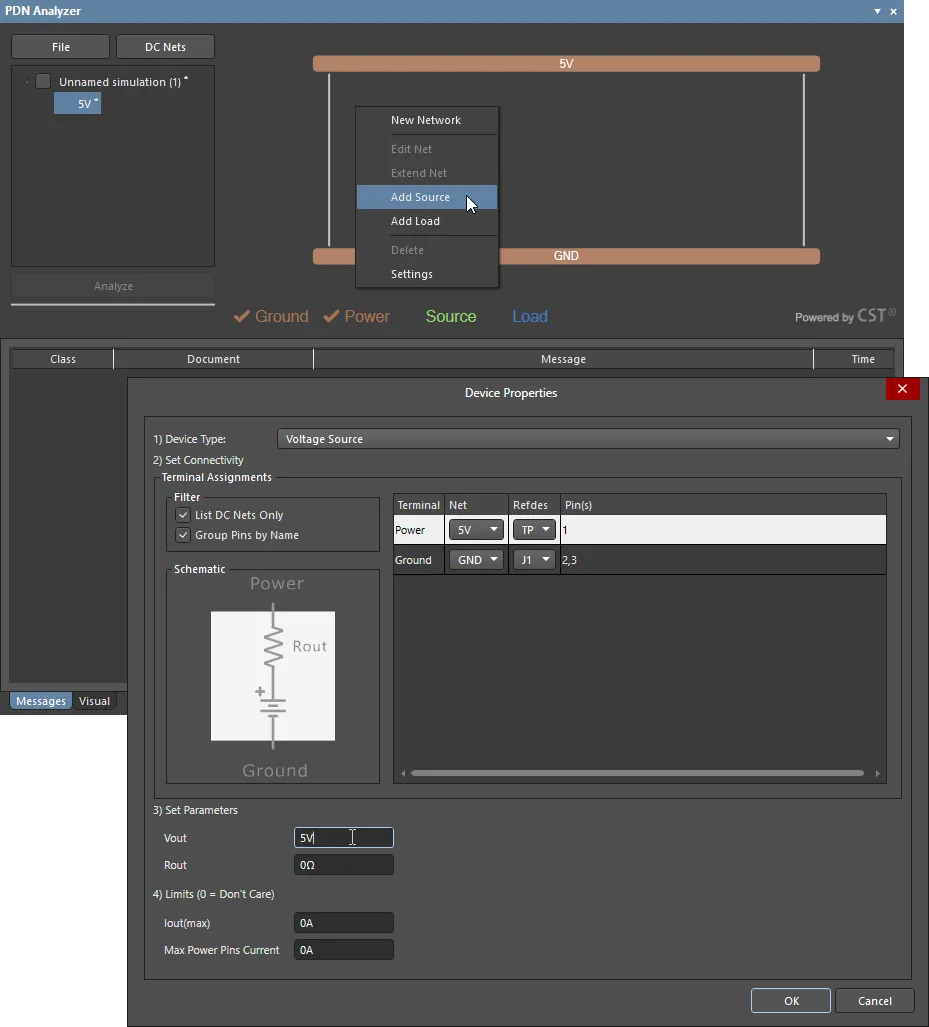

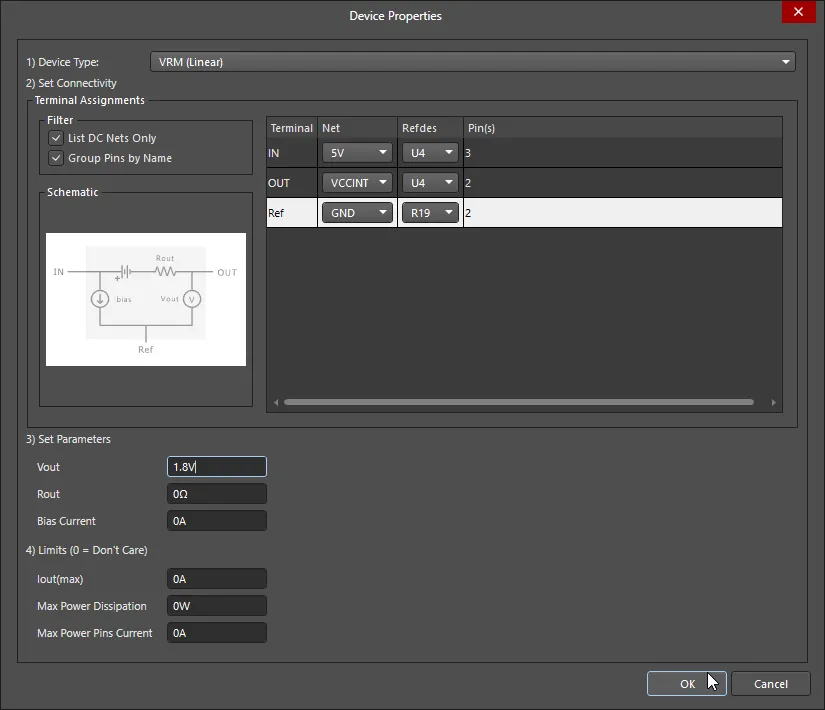

Add Source – 通过 Device Properties 对话框,在指定的电源/地网络对之间添加一个电压源或电压调节器模型(VRM)源器件。该对话框也可通过双击现有的 Source 元素打开。有关使用 VRM 的更多信息,请参见 包含电压调节器模型。

-

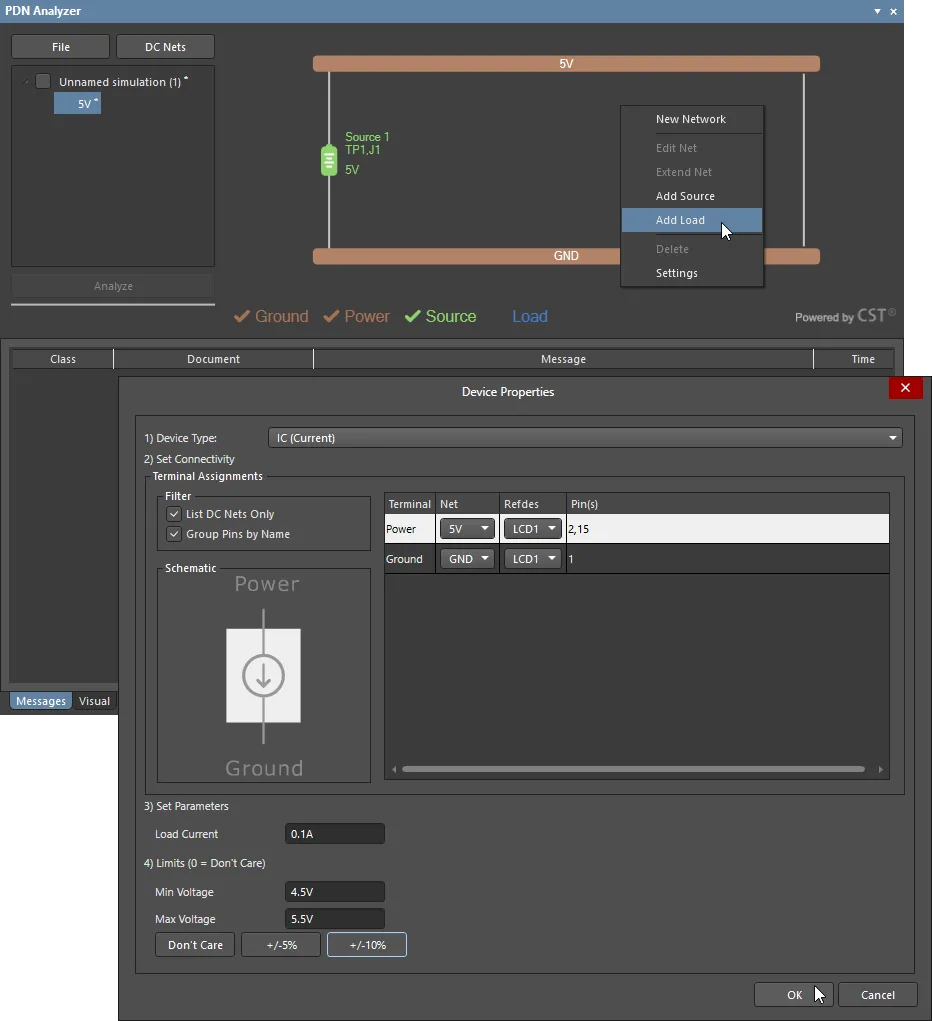

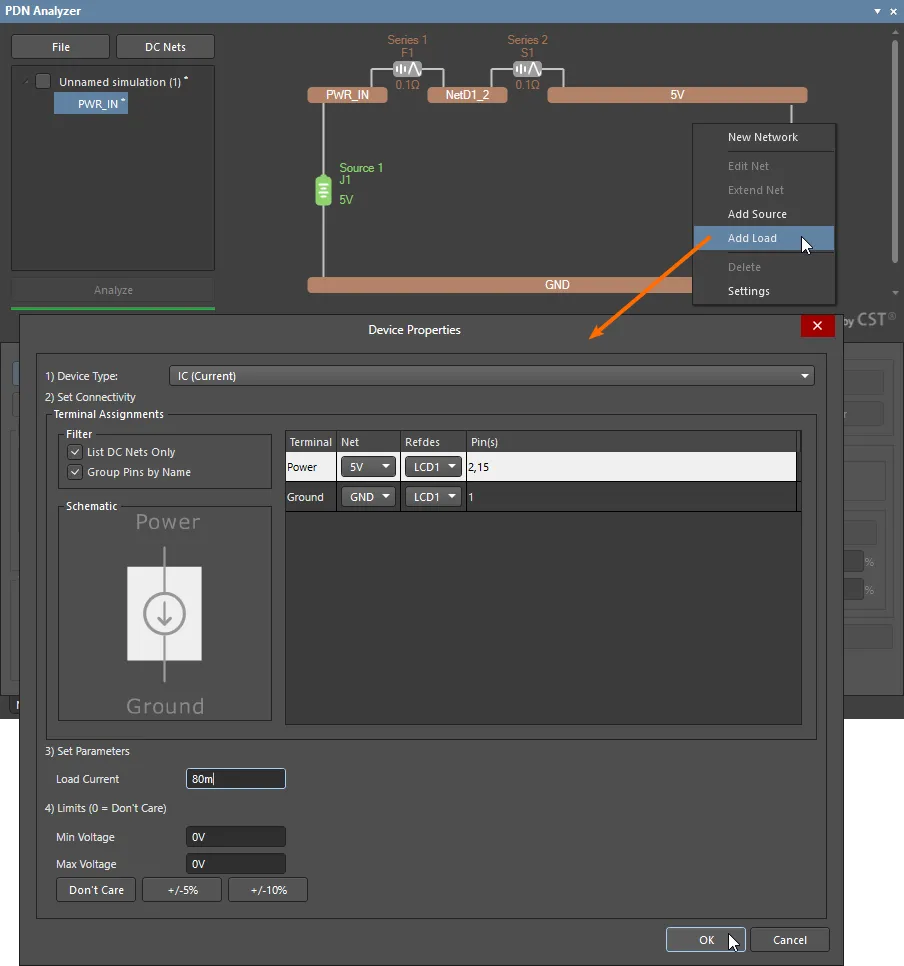

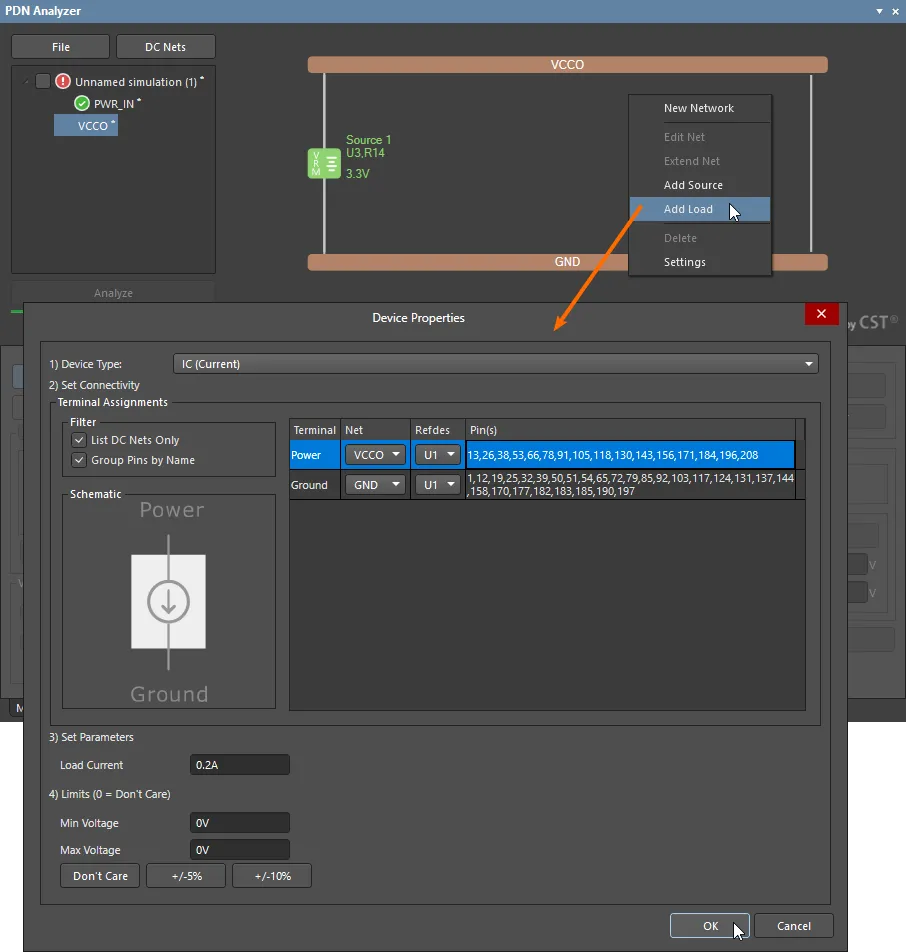

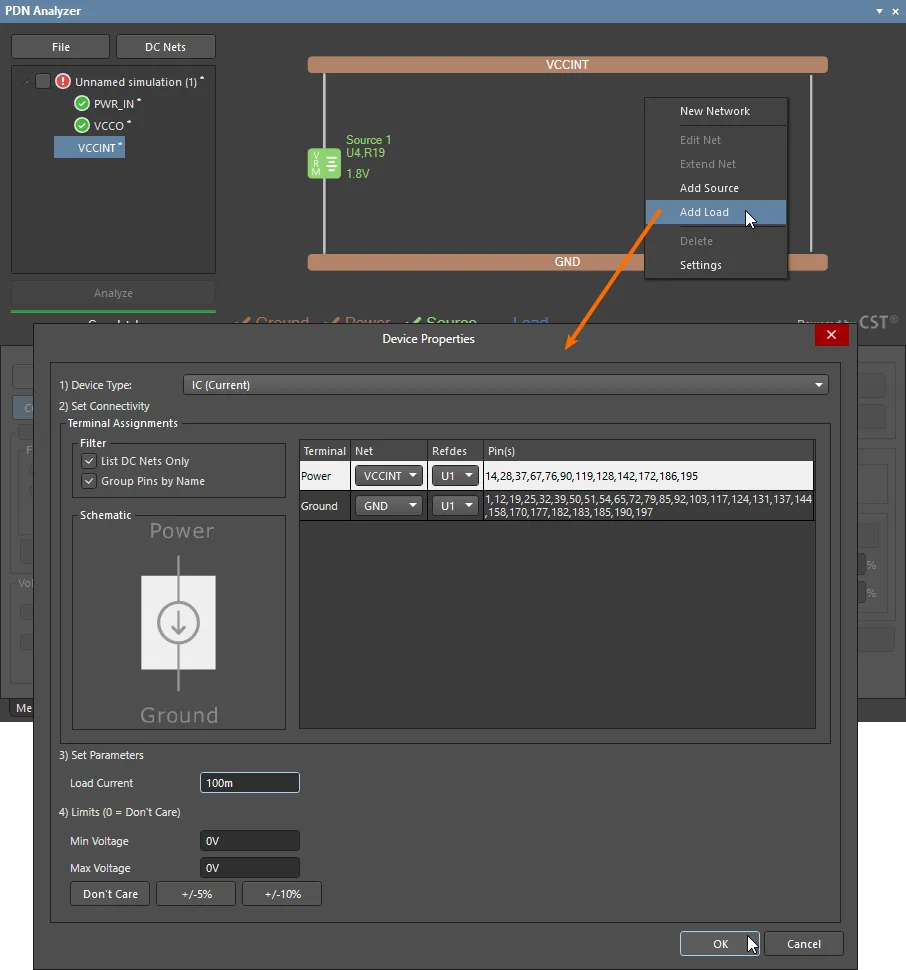

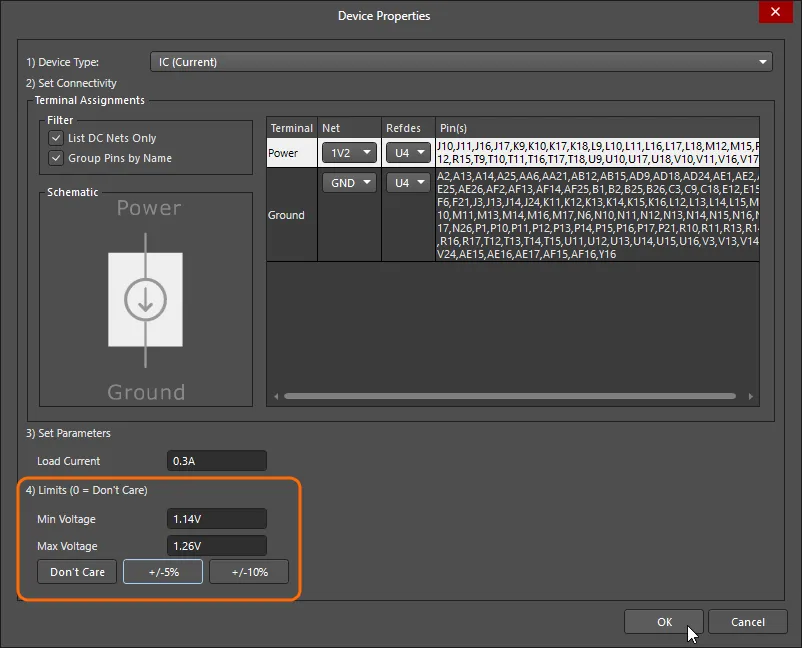

Add Load – 通过 Device Properties 对话框,在指定的电源/地网络对之间添加电阻器、电流吸收器(current sink)或电压调节器模型(VRM)负载器件。该对话框也可通过双击现有的 Load 元素打开。

-

Delete – 从仿真中移除该电源网络。注意:一个网络至少必须包含一条电源网和一条地网。

-

Settings – 打开 Settings 对话框,如上所述。

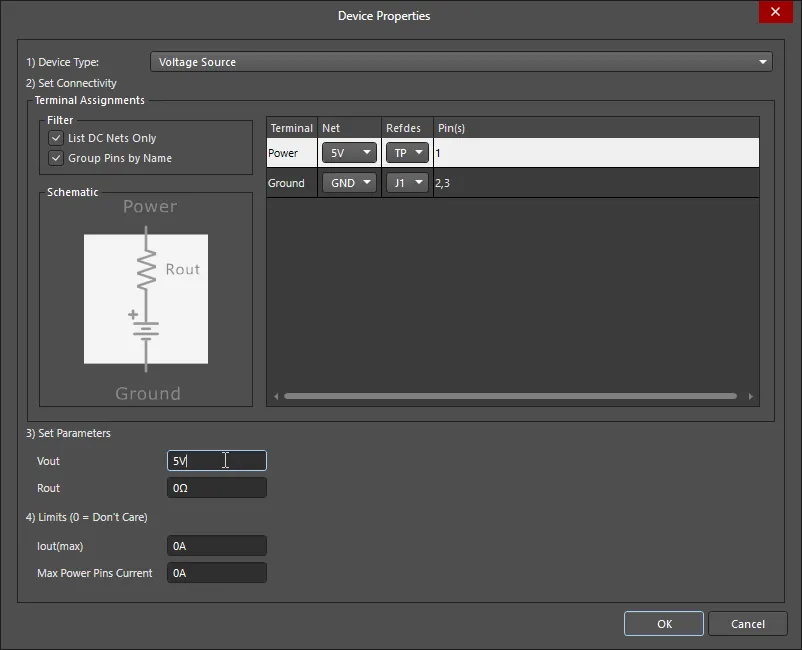

在添加或编辑现有器件元素(Load、Source 等)时使用的 Device Properties 对话框,提供用于指定器件类型、连接关系和参数的设置。

对话框中可用的设置选项取决于所放置或编辑的器件元素的功能,但通常如下:

-

Device Type – 使用下拉菜单选择器件类型,可用选项由元素类型(Source、Load 等)决定。

-

Set Connectivity – 使用列表中的 Net 与 Refdes 下拉选项,从可用的网络与节点中选择器件的 Terminal 连接,其中端子(Terminals)如 Schematic 仿真模型图形所示。网络连接 Pins 会根据所指定节点的网络连通性自动分配。

-

Filter – 使用 List DC Nets Only 选项来限制可用的 Net 选项,并使用 Group Pins by Name 选项来合并互连的器件引脚。禁用后者时,可通过点击 Pins 字段显示的 Select 复选框,按需选择/取消选择单个引脚。更多信息请参见 使用负载 中的 LCD 示例。

-

Set Parameters – 可用的参数选项取决于所放置(或编辑)的器件类型,但通常用于定义其基本属性,例如电压源的输出电压与内阻、电流吸收器的负载电流,或电阻负载的电阻值。

-

Limits – 器件的电压、电流或功率限制;当运行仿真时,超过限制将触发 Violation。Violation 会以红色虚线边框标示违规元素的图形,并在网络名称旁显示红色图标:示例请参见 电流密度限制违规 或 其他违规。

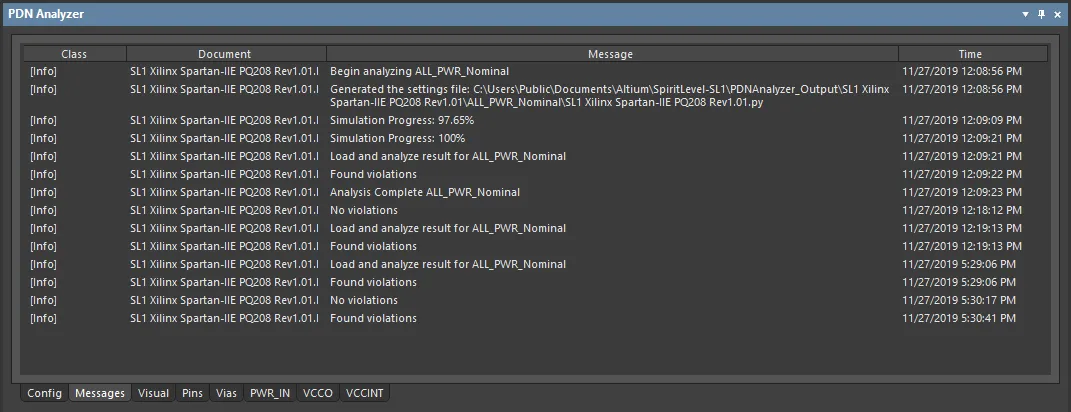

Messages 选项卡

Messages 选项卡包含最近一次 PDN 分析运行的仿真事件顺序列表,包括遇到的任何 Violation。若仿真运行失败,列表中将包含一条汇总问题的事件条目。有关一次仿真运行的更多信息,请参见可通过配置 Explore 选项访问的 PDN_Analyser.log 文件。

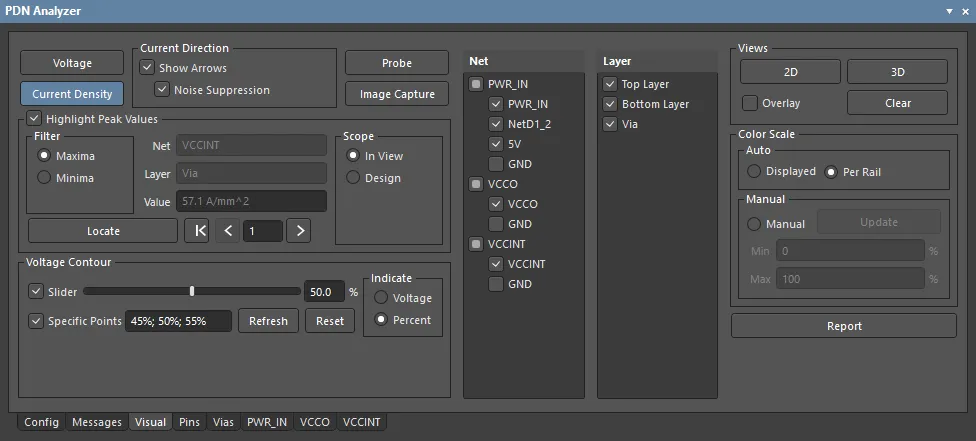

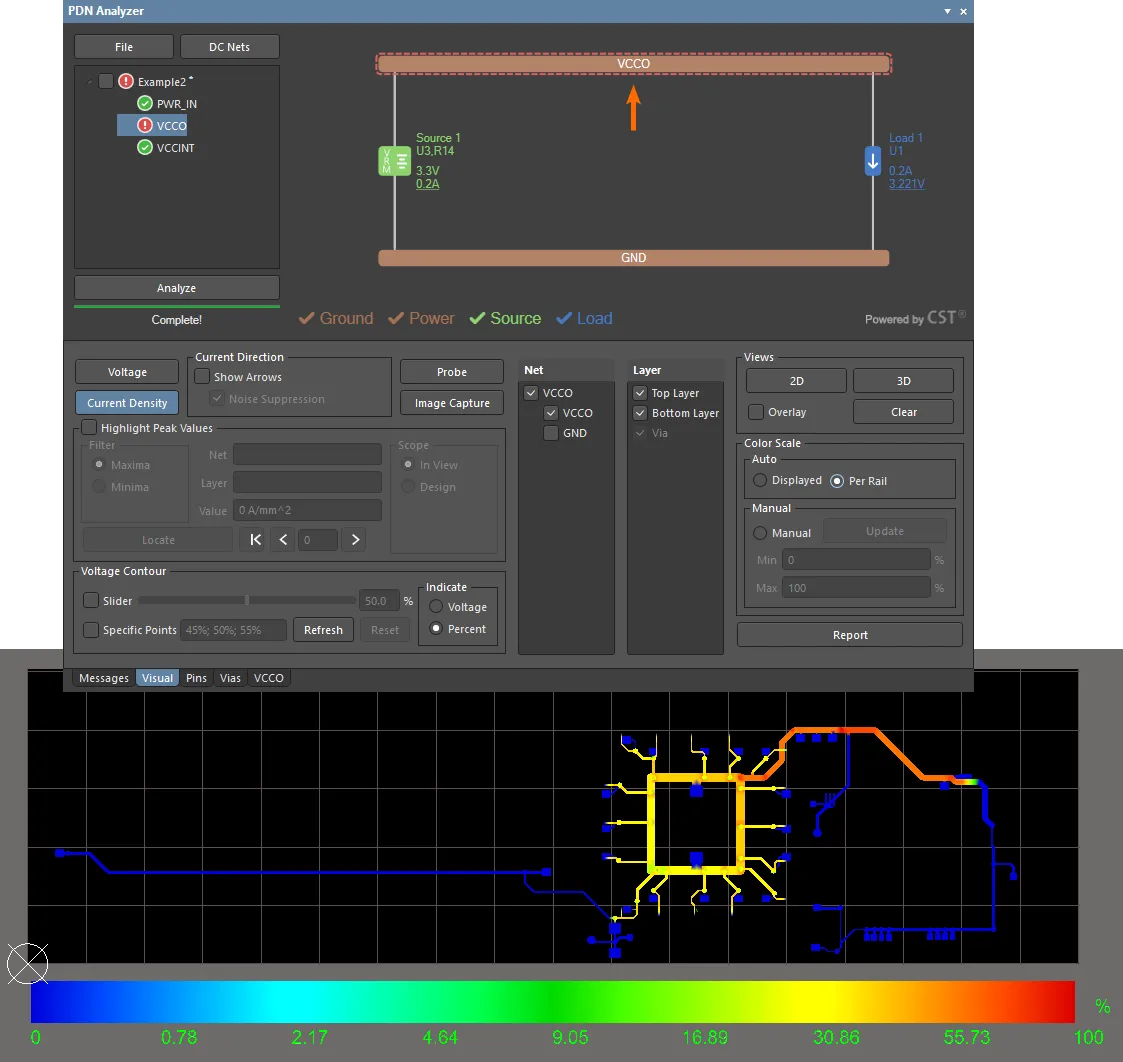

Visual 选项卡

PDN Analyzer 界面的 Visual 选项卡提供对电源网络分析数据在 PCB Editor 中显示方式的高级控制。它允许你指定 PCB 布局渲染中包含的信息类型、结果数据的缩放方式、是否以及如何高亮关注点,以及导出的信息内容。PCB Editor 中的渲染布局适用于当前在 PDN Analyzer 的 Configuration 网络层级中选中的电源网络。

建议以 Visual 选项卡的默认设置作为配置 PCB 布局显示的起点。默认设置为在 2D 模式下显示所有电源轨网络的颜色渐变电压分布——取消选择 Overlay 选项可查看纯分析结果。在 Visual 选项卡中所做的设置更改会立即反映到 PCB 渲染中。

Visual 选项卡选项包括:

-

Voltage – 选择

按钮以显示所有已启用网络的电压分布,并以伏特或整体百分比跨度进行缩放(见 Color Scale)。

按钮以显示所有已启用网络的电压分布,并以伏特或整体百分比跨度进行缩放(见 Color Scale)。

-

Current Density – 选择

按钮以显示所有已启用网络的电流密度分布,并以单位面积电流(安培/面积)或整体百分比跨度进行缩放(见 Color Scale)。

按钮以显示所有已启用网络的电流密度分布,并以单位面积电流(安培/面积)或整体百分比跨度进行缩放(见 Color Scale)。

-

Current Direction – 勾选 Show Arrows 选项,在渲染的 PCB 布局上叠加电流方向/分布指示箭头。选择 Noise Suppression 选项可对数据进行平滑处理,以获得更简洁的视觉效果。

-

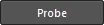

Probe – 选择

按钮打开 Probe 对话框,可在渲染布局中交互式选择两个数据位置并比较其数值。更多信息请参见 数据探针。

按钮打开 Probe 对话框,可在渲染布局中交互式选择两个数据位置并比较其数值。更多信息请参见 数据探针。

-

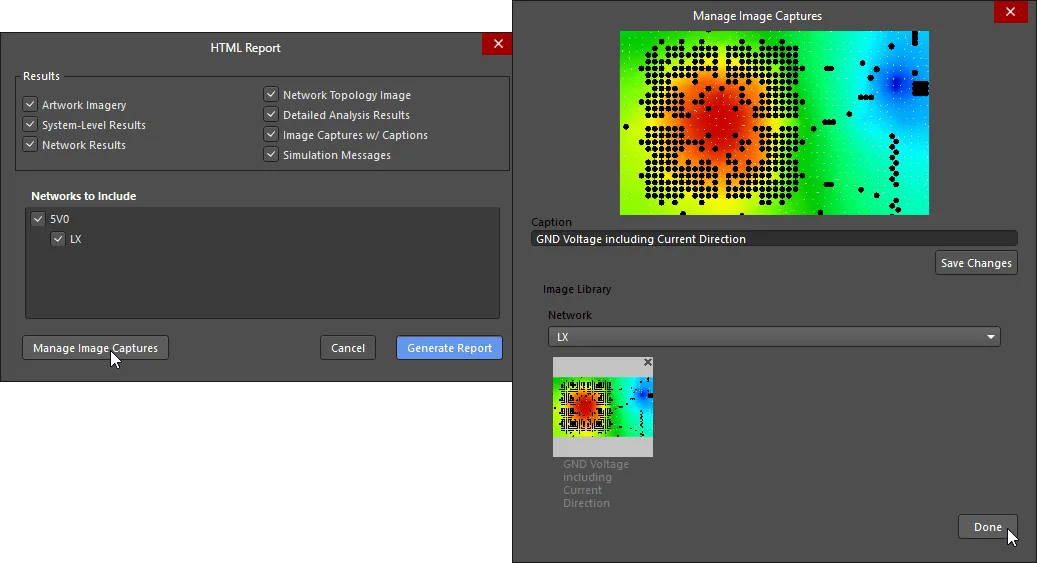

Image Capture – 选择

按钮打开 Manage Image Capture 对话框,可捕获并保存当前 PCB 渲染图。图像将存储在项目仿真的

按钮打开 Manage Image Capture 对话框,可捕获并保存当前 PCB 渲染图。图像将存储在项目仿真的 /HTMLReport/ImagesCache 文件夹中,以便后续纳入 Report。更多信息请参见 分析报告。

-

Peak Values – 选择 Highlight Peak Values 选项,以可视化方式标记并高亮当前所选网络与层中的最大值或最小值(由 Filter 选项决定)Value。使用 Scope 选项指定检测区域,使用 Locate 按钮可视化高亮峰值点,并使用数据点箭头(

)在相邻的数值序列中逐步浏览。示例信息请参见 定位电源完整性问题。

)在相邻的数值序列中逐步浏览。示例信息请参见 定位电源完整性问题。

-

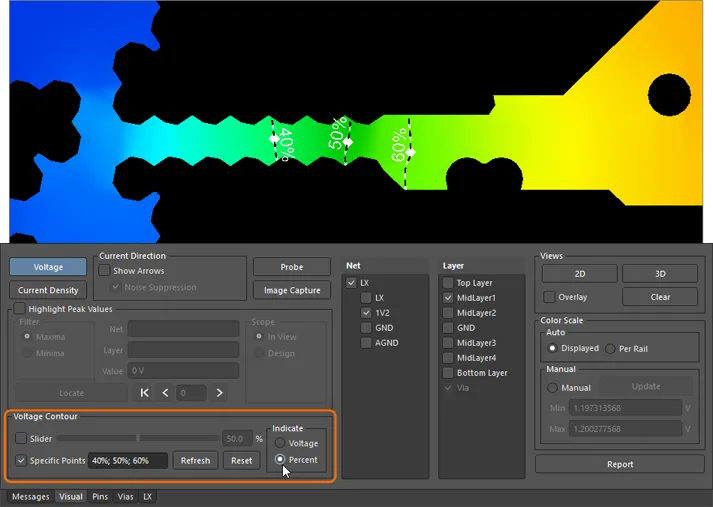

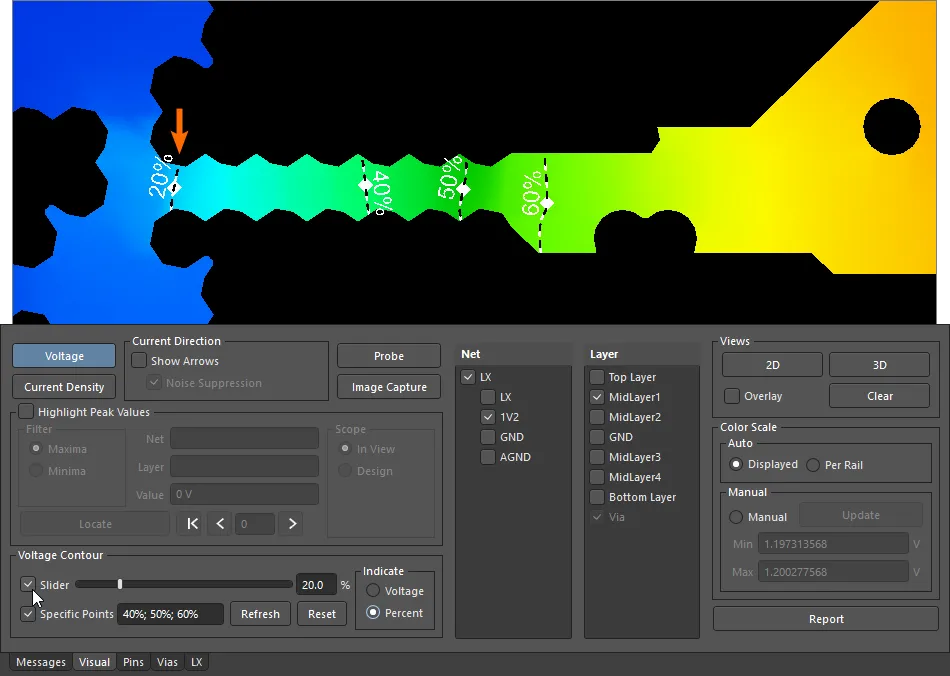

Voltage Contour – 选择 Slider 选项以启用虚线叠加层,用于表示该等值线处的电压水平。检测到的电平由滑块位置设定,并且其为电压值或百分比值,取决于相关的 Indicate 选项。选择 Specific Points 选项可在所示百分比点处启用各条电压等值线。点击

将 Specific Point 数值恢复为默认值,并点击

将 Specific Point 数值恢复为默认值,并点击  按钮更新/高亮所有已启用的电压等值线。更多信息请参见 电压等值线。

按钮更新/高亮所有已启用的电压等值线。更多信息请参见 电压等值线。

-

Net – 选择你希望在渲染的 PCB 分析结果中显示的 Nets。网络按可用的电源网络分组。

-

Layer – 选择你希望在渲染的 PCB 分析结果中显示的板层(Layers)。注意:在 3D 视图模式下可选择 Vias。

-

Views – 使用

与

与  按钮在 PCB Editor 的 2D/3D 模式之间切换渲染显示,使用 Overlay 选项启用/禁用编辑器的标准 PCB 显示视图,并使用

按钮在 PCB Editor 的 2D/3D 模式之间切换渲染显示,使用 Overlay 选项启用/禁用编辑器的标准 PCB 显示视图,并使用  按钮将渲染显示恢复为标准视图。更多信息请参见 显示控制与选项。

按钮将渲染显示恢复为标准视图。更多信息请参见 显示控制与选项。

-

Color Scale – 设置 Auto 选项,将渲染的颜色渐变显示为整体百分比范围(Per Rail),或显示为与完整电压跨度数据相对应的渐变(Displayed)。后者更适合仅显示单一网络时使用。选择 Manual 模式可将显示范围覆盖为在 Min 与 Max 字段中输入的电压值。更多信息请参见 在 PCB Editor 中的可视化渲染。

-

Report – 点击

按钮,通过 HTML Report 对话框配置并生成基于 HTML 的 PDN 分析报告。更多信息请参见 分析报告。

按钮,通过 HTML Report 对话框配置并生成基于 HTML 的 PDN 分析报告。更多信息请参见 分析报告。

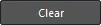

Pins 选项卡

Pins 选项卡列出设计中连接到已配置电源网络的所有元件引脚。每个元件引脚条目包含其编号、所连接的网络,以及上一次仿真运行得到的相关 Voltage 与 Current 数值结果。点击列标题可按该名称对列表排序,再次点击可反向排序。

双击某个条目可在 PCB Editor 中交叉探测到该引脚。如果在渲染视图中看不到该引脚(焊盘)连接,请确保其所连接的 Layer 以及电源 Net 已在 Configuration 面板/选项卡中启用。

Pins 选项卡列表按元件位号排序;——将光标悬停在图像上——按引脚电流排序。

Pins 选项卡列表按元件位号排序;——将光标悬停在图像上——按引脚电流排序。

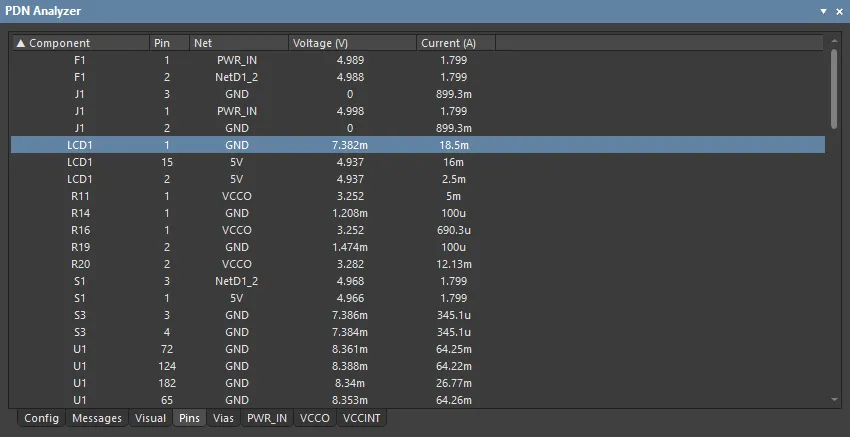

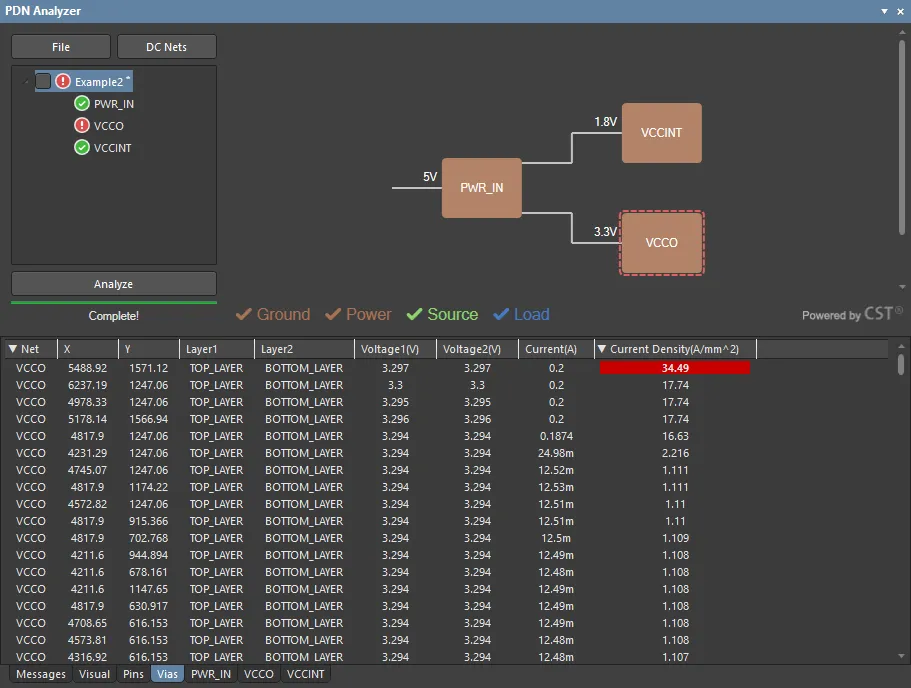

Vias 选项卡

Vias 选项卡列出设计中连接到已配置电源网络的所有 PCB 过孔。每个过孔条目包含其连接的网络、位置坐标、层对,以及上一次仿真运行得到的端到端 Voltage, Current 与 Current Density 数值结果。点击列标题可按该名称对列表排序,再次点击可反向排序。

双击某个条目可在 PCB Editor 中交叉探测到该过孔。如果在渲染视图中看不到该过孔,请确保在 Layer 列表中勾选了 Via(在 3D 视图中可用),并且其连接的电源 Net 已在 Configuration 面板/选项卡中启用。

Vias 选项卡列表按网络连接排序;——将光标悬停在图像上——按电流密度排序。

Vias 选项卡列表按网络连接排序;——将光标悬停在图像上——按电流密度排序。

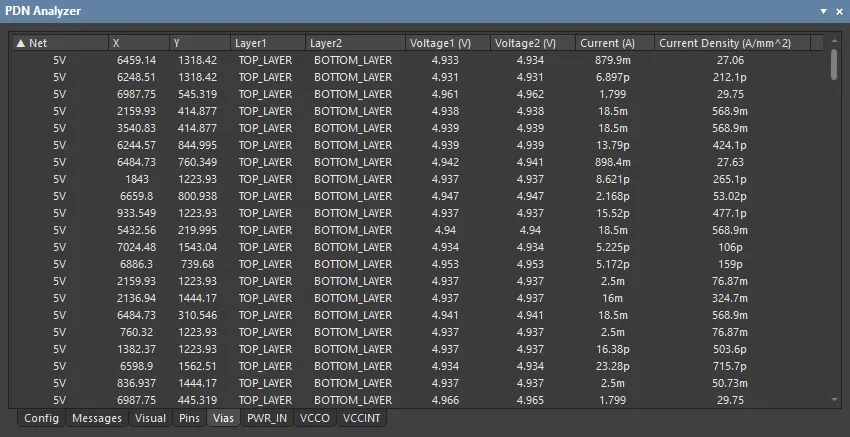

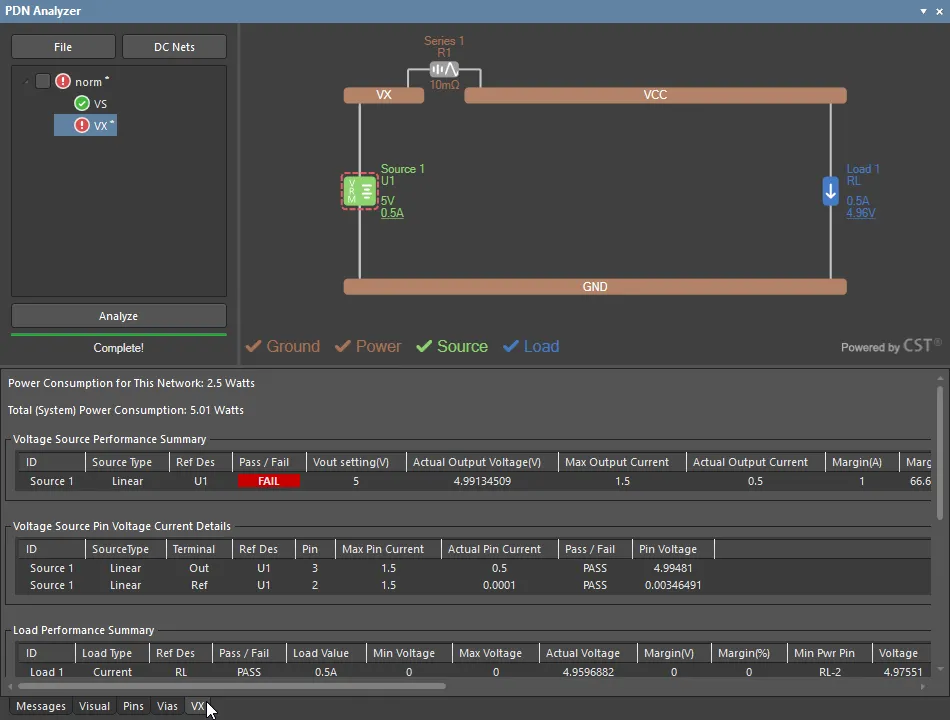

Power Network 选项卡

在仿真配置中,每个可用的电源网络都有一个对应的选项卡视图——哪些网络选项卡可见由 Configuration 窗格/选项卡中的电源网络选择决定。电源网络选项卡以网络名称标注,提供适用于该电源网络的分组仿真结果与计算数据的完整列表,同时还包含网络功耗汇总。

列表中的数据分组适用于该电源网络内的器件(电源、负载以及串联元件),并且每个器件都会包含一条 Performance Summary 和一条 Pin Voltage/Current Details 数据记录。除器件本身的详细信息外,这些数据分组还会给出关键的电压与电流数值;对于 Performance 汇总,还会给出与器件极限相关的计算安全裕量,而这些器件极限是在 Device Properties 对话框中指定的。

DC Net Identification

当首次为某个 PCB 设计打开 PDN Analyzer 时,它会尝试基于设计的网络数据,并依据常见的电源网络命名规则来识别所有直流电源网络。 如果仍有潜在的电源网络未被识别,请取消选择相应的 Qualifiers 过滤选项;或者要查看所有网络,请选择 Enable all nets for filtering 选项。

使用 Select 复选框选择哪些电源网络将提供给 PDNA 分析器使用,并在对应的 Nominal Voltage 字段中输入合适的电压等级。点击 Add Selected 按钮以填充 Currently Identified DC Nets 列表,并确认这些网络为已识别的电源网络。

注意,在对话框中双击列表里的某个网络条目,会在 PCB 布局中交叉定位到该网络。

在 PDN 分析设置过程中,还可以通过在分析器 GUI 中选择 DC Nets 按钮来识别并应用更多网络。

下面的分析示例用于演示 PDN Analyzer 的主要能力与特性。每个示例仅展示了众多可能参数配置中的一种,用于从不同关注点出发、以不同方式评估网络的电源完整性。注意:成功完成的分析可以保存为 PDNA 配置文件(*.pdna)并在任何时候重新加载——File » Save As 和 File » Open(默认位于项目的 PDNAnalyzer_Config 文件夹中)

Example 1

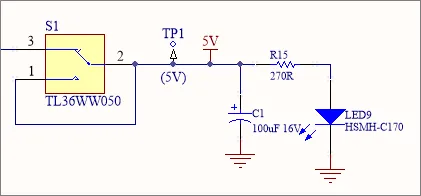

本示例演示如何使用一个简单电源网络及其电流负载来完成电源完整性仿真的基本设置。它被配置为评估 SpiritLevel-SL1 参考项目中 5V 供电轨的分配及其地回流路径,并假设设计的 LCD 显示屏处于负载状态。在此情况下,5V 供电轨被视为一个简单的电压源,其连接的网络(例如通过开关 S1)不包含在内。

该 PDN 仿真示例的前置条件为:

-

Spirit Level PCB 项目已在 Altium Designer 中打开

-

PDN Analyzer 应用已激活(Tools » PDN Analyzer)

-

PCB 设计的 DC Nets 已在 PDN Analyzer DC Net Identification 对话框中完成识别,如 outlined above 所述。

通过指定电源网络与地网络来开始分析流程。在 GUI 网络图中双击 <Power Net> 和 <Ground Net> 元素以打开 Choose Net 对话框,该对话框将提供已识别电源网络的选择。

如有需要,可使用对话框的限定/过滤选项来收窄或扩展网络列表;或者返回主界面并选择  按钮以重新识别 DC power nets。

按钮以重新识别 DC power nets。

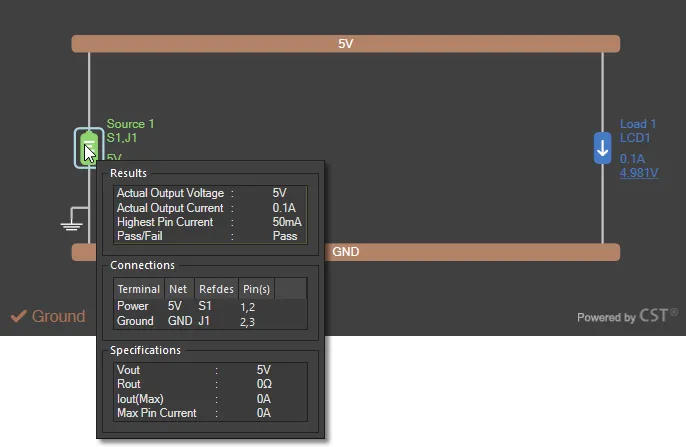

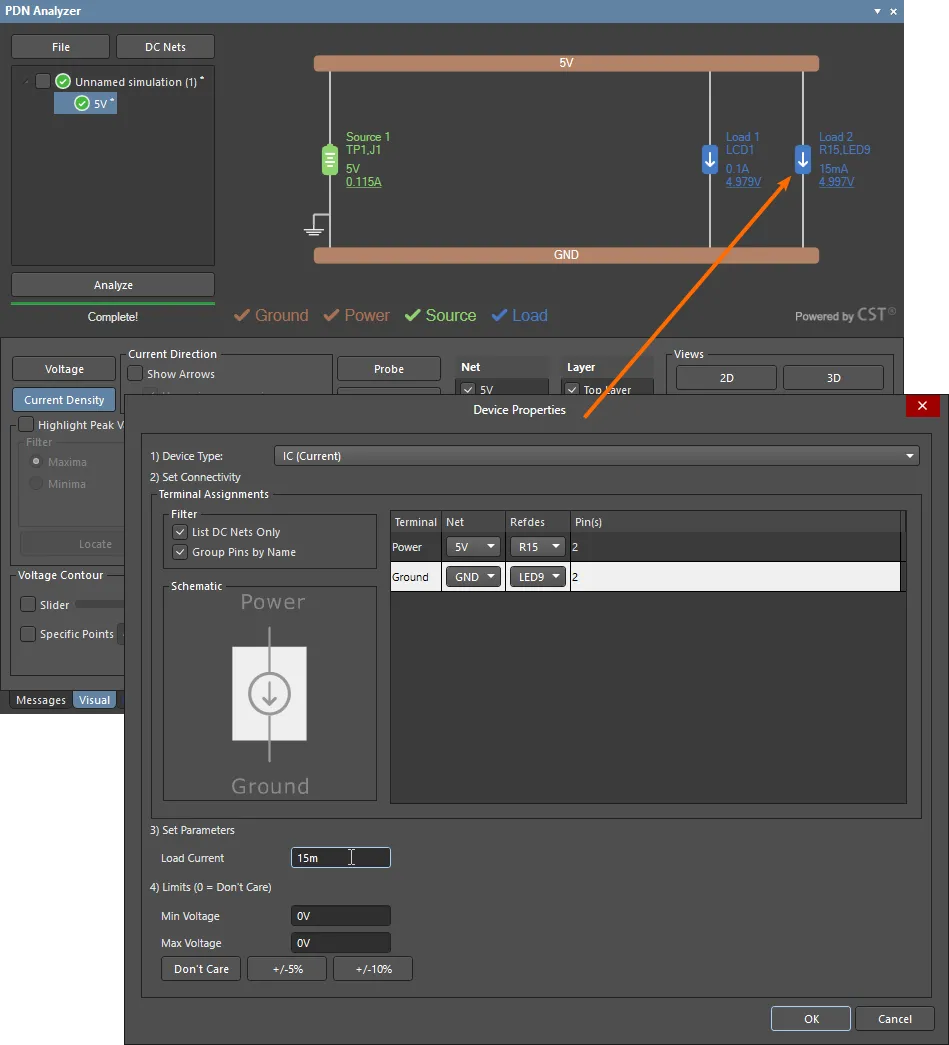

现在可以在指定的电源网络与地网络之间添加 Source 或 Load 元素——注意 Ground 与 Power 状态指示器会变为已勾选状态(✔)。在网络图工作区中右键并从上下文菜单选择 Add Source(或 Add Load)以打开 Device Properties 对话框。对话框中指示的步骤如下:

-

要为网络添加电源 Source(本例为简单电压源),请在对话框的 Device Type 下拉菜单中选择 Voltage Source 选项。

-

在源连接关系列表中,PDNA 会根据电源网络参数尝试自动选择正确的网络连接选项——即在

5V 与 GND 网络之间。使用 Refdes 下拉菜单选项来指定源电压的器件连接点。本例中,源电压点指定为 TP1,其地回流指定为设计的 DC 输入插座 J1(引脚 2 与 3)。

-

在对话框下半部分,源参数用于指定电压源仿真模型的属性。此处源电压(Vout)设置为

5V,模型的内阻(Rout)保持默认 0Ω 设置。

-

最后,最大源电流与引脚电流(适用于具有多个输出引脚的电源)保持默认设置(

0A: Don't Care)。当 Limits 被设置为特定电流值时,如果仿真结果超过这些数值,PDN 分析将标记为 Violation。

使用与向网络添加 Source 相同的方法,添加一个 Load,并在 Device Properties 对话框中指定其参数。

本例添加了一个电流吸收型负载(Device Type: IC (Current)),用于表示设计的 LCD 器件从 5V 供电轨汲取的电流。注意:也可以选择纯电阻负载选项,只需将 Device Type 选择为 Resistor。

将负载连接设置为 LCD1,并指定它将从 5V 供电中汲取的 Load Current——注意支持单位前缀(例如用 500m 表示 0.5A)。虽然电压 Limits 设置是可选的,但此处已设置为 +/-10%(使用相关按钮),这会在负载处电压低于 4.5V(或高于 5.5V)时触发仿真违规。

当电源网络已定义且所有参数均已指定(所有网络元素都具有 ✔ 状态)后,可选择  按钮运行 PDN 分析。仿真进度会在 Messages 选项卡下以事件流形式显示;如果流程无法完成,该处也会指示仿真失败的原因。

按钮运行 PDN 分析。仿真进度会在 Messages 选项卡下以事件流形式显示;如果流程无法完成,该处也会指示仿真失败的原因。

当运行分析时,当前仿真配置——所指定的网络、sources/loads 等及其相关参数——会与分析结果数据一同存储(File » Explore;参见 PDNAnalyzer_Ouput 文件夹)。在当前仿真中,随时可通过右键单击仿真名称并从上下文菜单选择 Revert 来恢复该配置设置。

PDN 分析的即时结果可在网络图中查看,其中包括计算得到的负载/电源电压与电流水平(如适用),以及对导致参数 Violation 的网络区段进行高亮显示。注意此时 Visual 选项卡已聚焦并处于活动状态。

将光标悬停在网络中的任意元素(Load、Source 或 Series Element)上,可查看其指定参数与分析结果等附加信息。

Visual Rendering in the PCB Editor

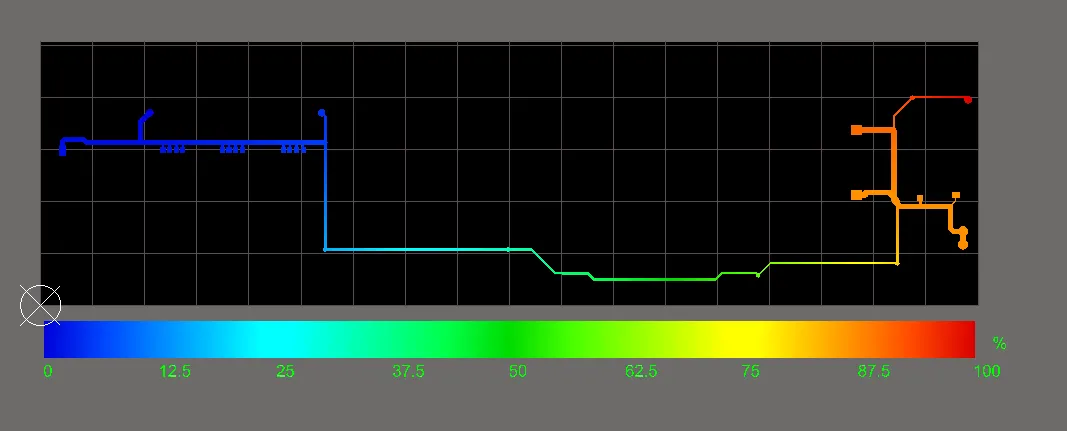

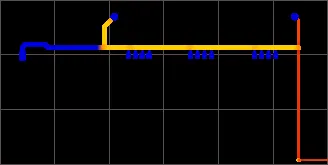

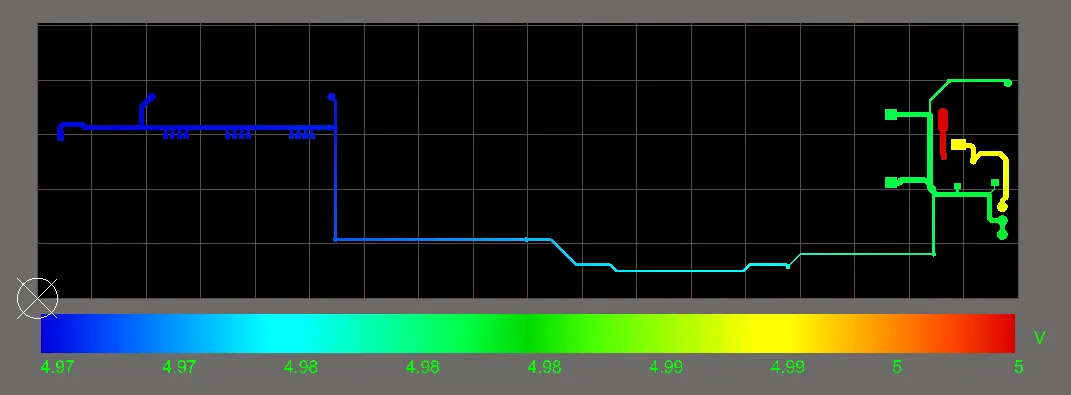

现在可以在 Altium Designer PCB 编辑器中以图形方式查看仿真结果,并由 PDNA 的 Visual 选项卡中的设置进行控制。将可视化选项设置为对 5V Net 的 Layers(Top 和 Bottom)都显示 Voltage——这是初始默认显示设置。分析器结果会在 PCB 编辑器中渲染显示,以替换现有的 PCB 图形叠加层。

所选网络路径的电压降视图(本例为从 TP1 处的 5V 电源到 LCD1 器件)会以颜色渐变方式渲染,并与视图底部给出的 Voltage 标尺相对应。该标尺可显示为电压百分比(Color Scale 下的 Per Rail 选项),或显示为实际电压跨度(Displayed 选项)。

在下图中,沿板上网络路径的颜色过渡表示整体电压降:由于 IR 损耗导致的最小电平(0%: 蓝色)位于 LCD1 器件处,而最大电平(100%:红色)位于指定的电压源点(TP1)。

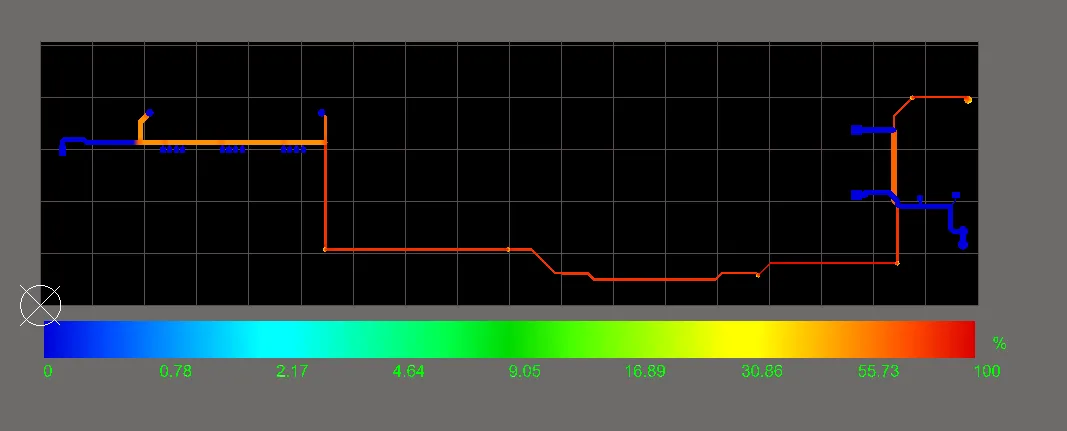

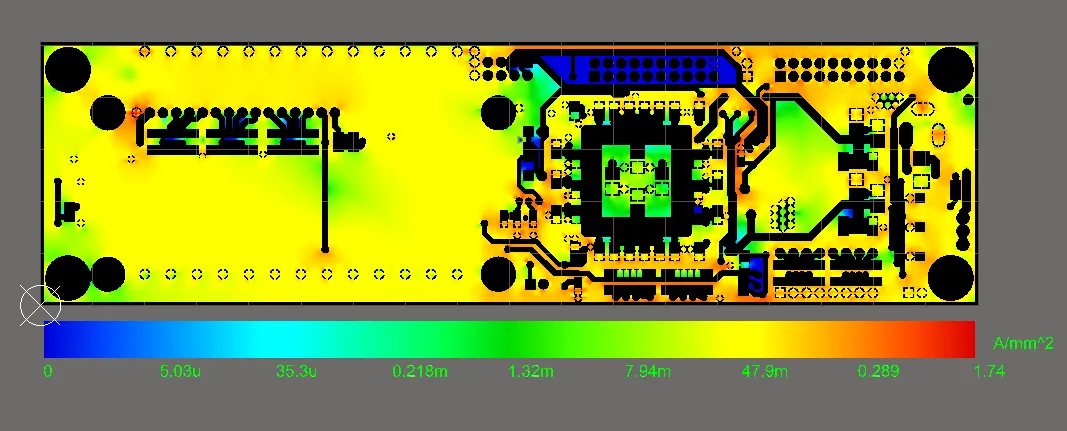

要显示该网络对应的电流分析,请选择 Visual 选项卡中的 Current Density 选项。此时,板上网络路径中的颜色等级对应电流密度变化的百分比:100%(红色)表示网络路径布局中计算得到的最大电流密度,0%(蓝色)为最小值——很可能是 0A/mm2。

注意:尽管替代的电压/电流标尺选项(Displayed)对于显示单个网络而言更直观,但在同时显示多个电压网络时可提供的有效信息有限——例如本例中的 5V and GND,或当设计中分析了多个电源网络时。

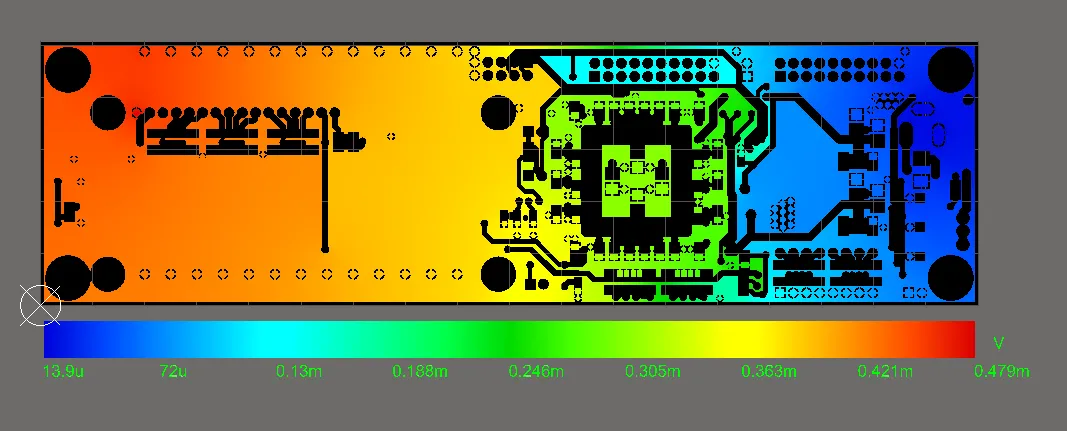

要显示并分析示例中 GND 回流路径的电源完整性结果,请在 PDNA 的 Visual 选项卡下的 Net 列表中取消选择 5V 网络选项,然后选择 GND 网络。地回流路径同时经过设计的 Top 与 Bottom 层;在 PCB 编辑器中可通过选择 PDNA 的 Layer 列表中的各个条目来分别显示每一层。

下图显示了 GND 网络底层的电压显示,其中 Color Scale 标尺设置为 Displayed。电压降最高的位置(红色:约 0.5mV)位于 LCD 的 GND 引脚处,而电压降最小的位置(蓝色:约 0V)位于电压源回流点(J1)。

切换到 PDNA 的 Current Density 选项会以红色显示最大电流“热点”。最大电流密度水平本身(1.74 A/mm2)非常低,且完全在可接受范围内。

显示控制与选项

PDN Analyzer 提供多种交互式显示选项,用于决定在 Altium Designer PCB 编辑器中如何以图形方式呈现分析结果。除显示 Color Scale 的选项外,图形还可在 2D 与 3D 渲染之间切换,后者可通过过孔以及层间视图为分析结果提供非常有价值的洞察。

还提供了一个选项,可将分析结果从编辑器显示中 Clear,并自动将图形渲染恢复为标准板级布局。相对地,视图的 Overlay 选项可启用板级布局视图,并与当前显示的任何分析结果一起渲染。该选项特别适用于确认分析结果中的关注点在板级布局中的具体位置。

处理负载

可根据需要向网络中添加更多负载,并重新运行电源分析以评估结果。例如,要添加由设计中的电源 LED 引起的小负载电流(例如 15mA),可选择其串联电阻(R15)作为 5V 电源轨连接点,并将 LED 引脚作为 GND 连接点。

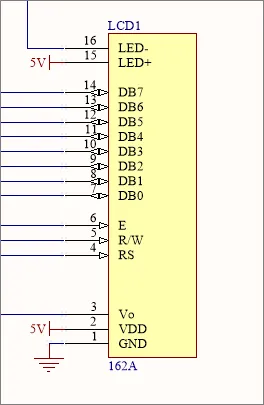

PDN Analyzer 还允许为负载指定器件引脚连接方式,从而可为同一个器件创建多个负载模型,使其通过不同引脚消耗不同电流。

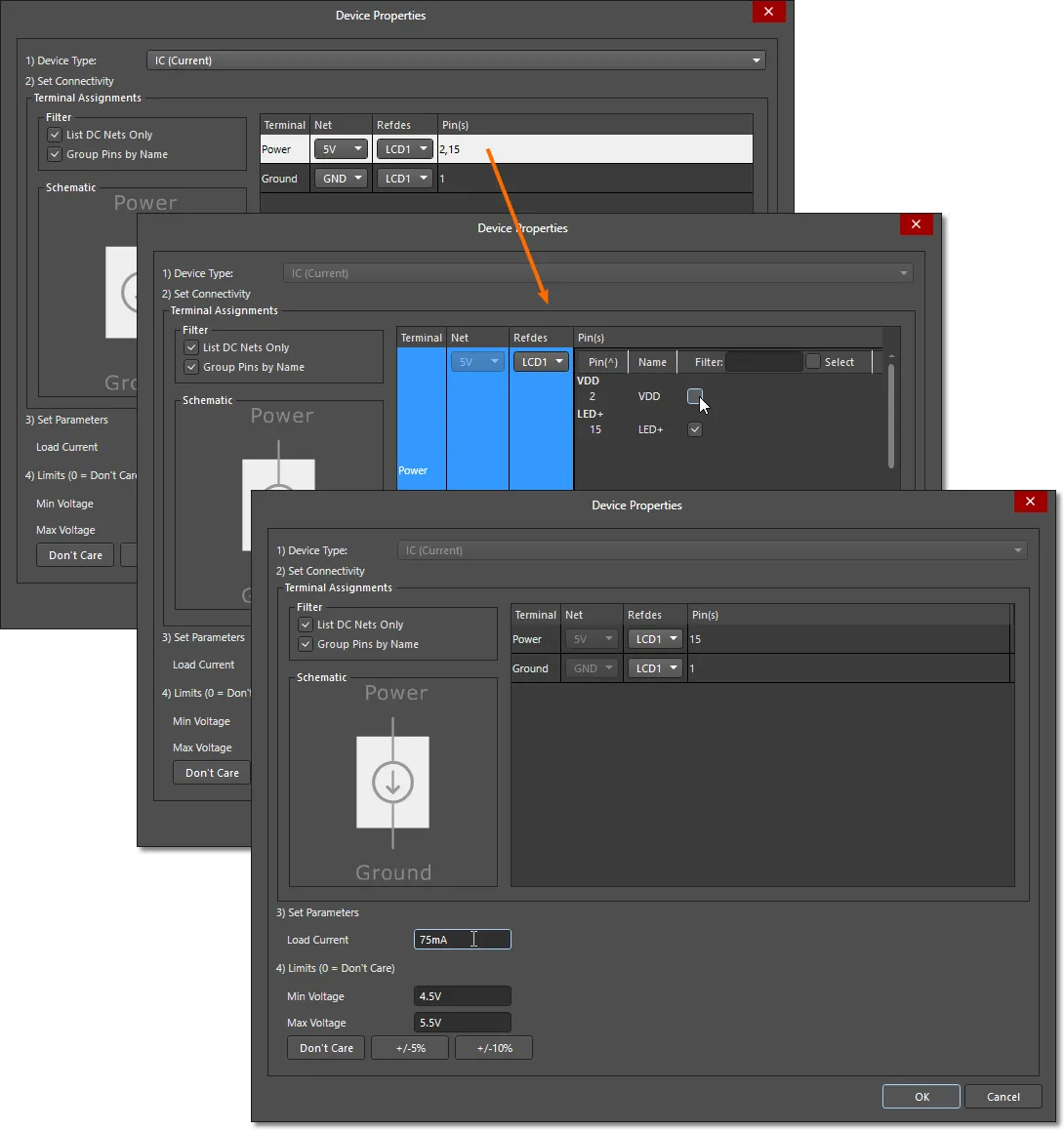

示例工程中的 LCD 器件就体现了这种情况:其 15 脚的 5V 连接(LED+)为显示背光供电,而 2 脚的 5V 连接(VDD)为内部逻辑供电——在实际中,15 脚消耗的电流会显著大于 2 脚。

当之前将 已添加 为单一 PDNA 负载模型时,LCD1 的两个引脚都被(默认)指定为 5V 负载连接点,PDN 分析会将 LCD1 的负载电流在这些引脚之间平均分配。为提高电源分析的准确性,可将 LCD1 元件表示为 two 个负载模型:每个 5V 引脚各一个,并为其分配对应的负载电流。可通过编辑现有 LCD1 负载模型的引脚参数来实现该更改,然后再为分离出来的引脚添加另一个负载。

在网络图中双击现有 LCD1 负载模型的图标以打开 Device Properties 对话框,然后在 5V 电源网络条目的 Pins(s) 字段中双击。进入的引脚编辑模式允许为该负载选择单独的器件引脚。取消选择 2 脚,将负载重新配置为仅使用 15 脚(LED+),并将 Load Current 参数调整为例如 75mA,以表示 LCD 背光电流。

接着,为 LCD1 再创建一个 5V 网络负载,并将 2 脚设为启用(同时禁用 15 脚),以表示 VDD 负载;其 Load Current 可设置为更低的合适值——例如 20mA。

随后即可重新分析 5V 电源网络,以更准确地反映 LCD1 负载在网络路径中的分布情况。

对比原始与更新后的负载配置时,可以从 LCD1 电源网络走线的电流密度中看到负载电流分布的差异。下方电流密度分析图中,左侧为原始的 LCD1 单负载模型结果,右侧为更新后的多负载结果。

请注意为 2 脚(LCD 焊盘偏左)与 15 脚供电的走线中的电流密度。更新后的版本正确显示大部分 LCD 电流流向 15 脚(LCD 焊盘偏右),而不是像之前那样在两个引脚之间平均分配(左图)。

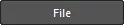

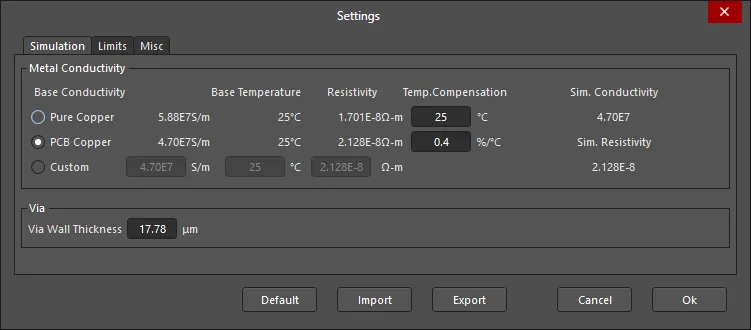

仿真设置

分析结果,尤其是板形状中的 IR 损耗程度,也取决于板上铜的电导率规格以及过孔壁厚。要查看并编辑这些设置,请在 Settings 对话框中选择 Simulation 选项卡——要访问该对话框,可在当前分析名称上右键并从上下文菜单中选择 Settings。

金属电导率

对话框的 Metal Conductivity 区域提供了设计中所用金属电导率(电阻率的倒数;1/R)的详细信息与设置。可在对话框中选择或修改基准电导率(或电阻率)、温度系数和/或温度,以反映设计的板材构造特性:

-

Pure Copper – 通常假设铜在

25°C 时的电导率为 5.88e7S/m,其电导率温度系数为 0.4%/°C。该正温度系数意味着:将对话框中的 Temp. Compensation 设置从 25°C 提高到 125°C(100°C 的变化量)会使仿真电导率降低 40%,例如降至 3.53e7S/m。

-

PCB Copper – 这是仿真的默认设置,反映了行业文献中报告的、可代表 PCB 电沉积(ED)铜的电导率数值:测得其在

25°C 时为 4.7e7S/m,热系数为 0.4%/°C。

-

Custom – 选择此选项可为仿真输入特定的电导率或电阻率数值。

请注意,显示的 Sim Conductivity 数值表示综合所有参数后的最终电导率;Sim Resistivity 数值为其倒数。

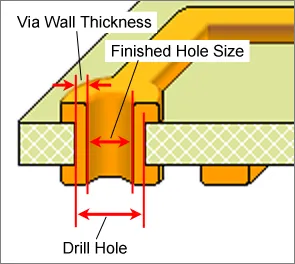

过孔

设置对话框中的 Via Wall Thickness 数值,以指定设计仿真分析中所有过孔的过孔壁金属重量。

该设置会显著影响电源网络的直流损耗,因为薄壁(电镀较薄)的过孔本身具有一定电阻。然而,当过孔尺寸/重量足够时,过孔不会阻碍设计的直流性能,并会显示与其连接的电源走线相同的电流密度——且其连接点之间不会出现显著电压损耗。关于过孔损耗的直流分析示例见下方 section below。

就仿真而言,过孔尺寸与壁厚有效地定义了过孔所代表的导电材料量,从而决定其电阻/电导率。仿真假设过孔直径为成品孔径,而过孔壁厚会增加过孔直径。因此:Finished Hole Diameter + (2 x Wall_Thickness) = Drill Diameter。

示例 2

本示例演示如何实现一系列相互连接的网络,并将其作为整体进行分析,同时考虑连接它们的串联元件参数。它还概述了如何添加电压调节器模型(VRM)源(其同样作为网络之间的互连),以及如何构建完整的设计电源网络层级结构。

该示例对 PWR_IN 到 5V 的网络进行建模,基于 SpiritLevel-SL1 参考工程,并包含 3.3V(VCCO)与 1.8V(VCCINT)两个 VRM,以创建完整的电源网络结构。

该 PDN 仿真示例的前置条件为:

-

Spirit Level PCB 工程已在 Altium Designer 中打开

-

PDN Analyzer 应用已激活(Tools » PDN Analyzer)

-

PCB 设计的 DC 网络已在 PDN Analyzer DC Net Identification 对话框中识别,正如上文 outlined above 所述。

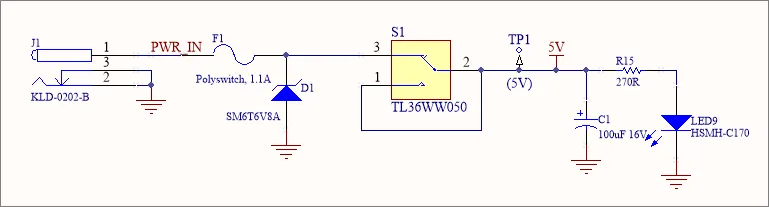

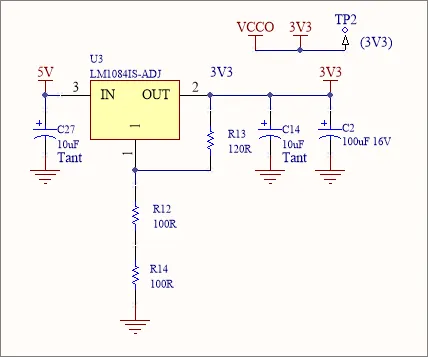

通过在新仿真中指定输入电源网络(PWR_IN)来开始构建示例电源网络(如有需要,选择 File » New Simulation)。如工程原理图所示,PDN <Power Net> 参数为 PWR_IN,<Ground Net> 为 GND,而 Source 为 J1。

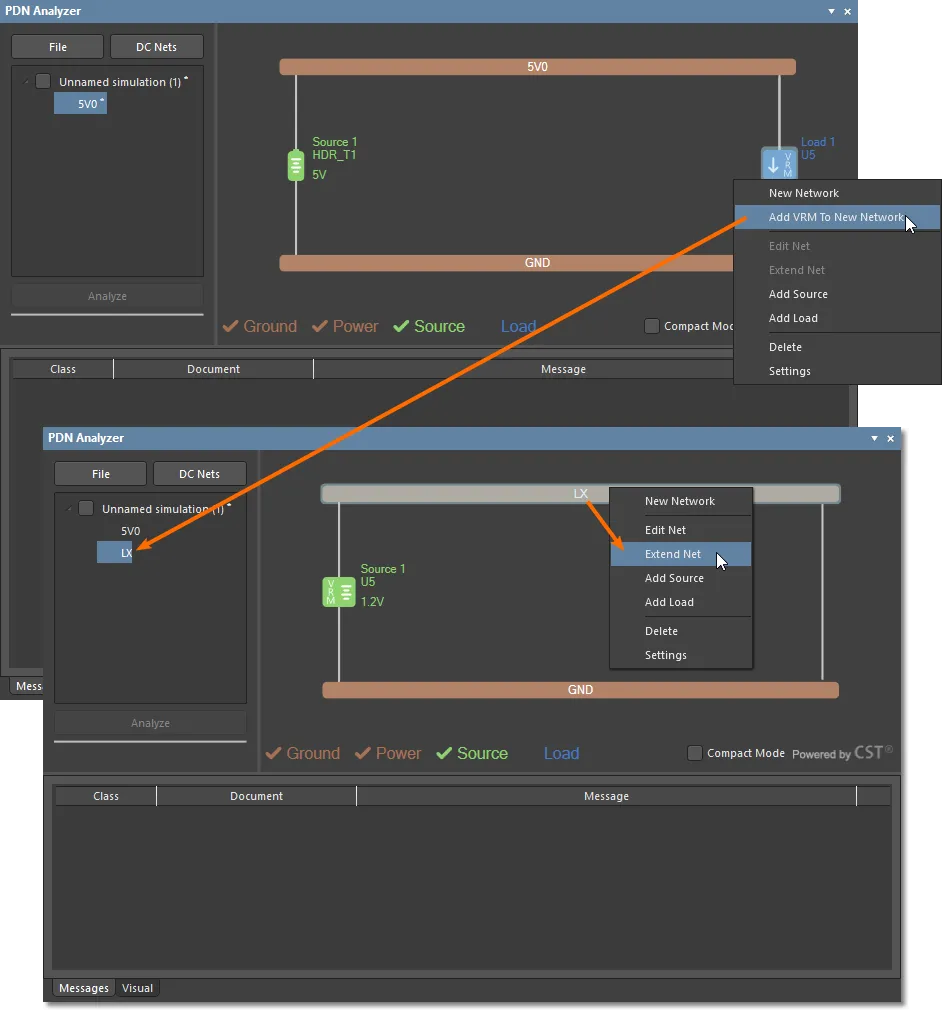

通过串联元件扩展网络

要对从 PWR_IN 网络到 5V 网络的完整电源路径建模,需要添加串联保险丝(F1)与开关(S1)元件以及它们之间的网络。在 PDNA 界面中,可通过按顺序扩展电源网络来添加这些内容。每个网络“扩展”都通过一个通用串联元件模型连接。

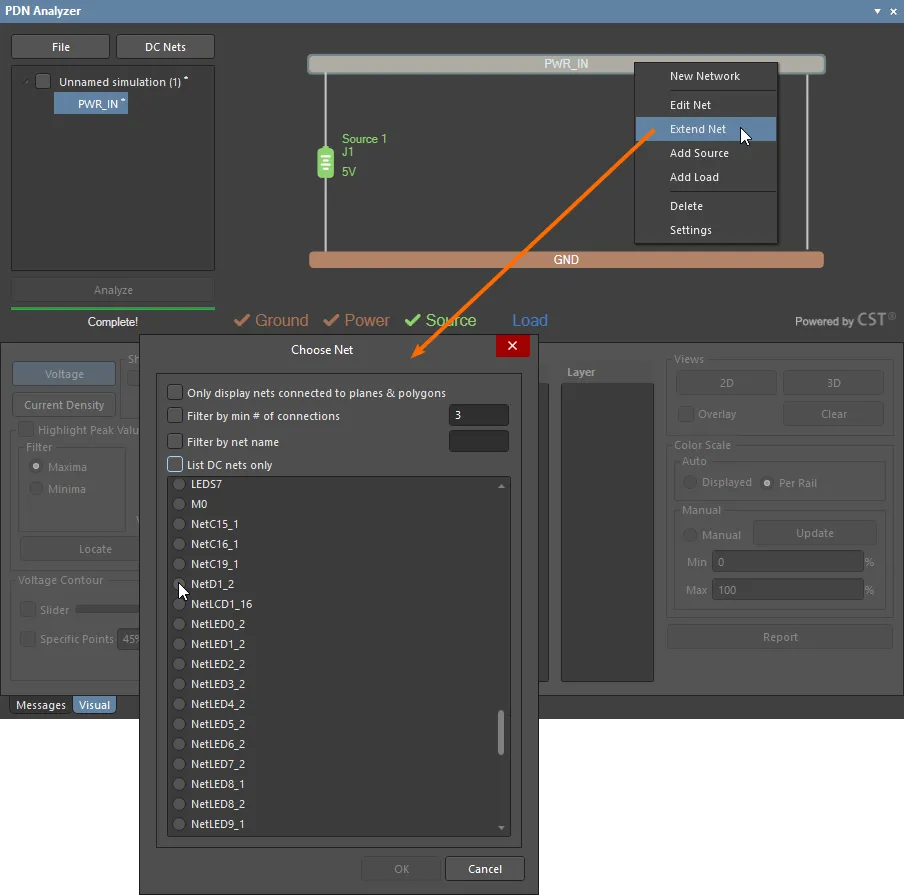

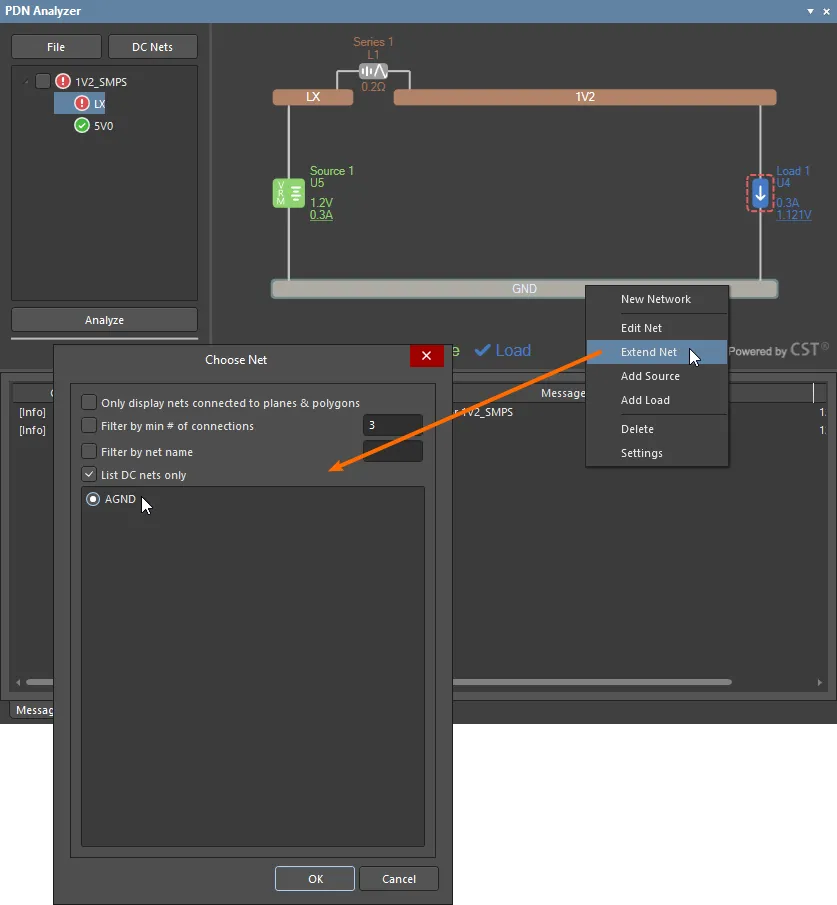

扩展网络的方法是:先在要添加到的网络中右键,然后从上下文菜单中选择 Extend Network 选项。在 Choose Net 对话框中,选择通过串联元件与 PWR_IN 相连的网络;在本例中为 NetD1_2——该网络连接 F1 与 S1 的 3 脚,并被识别为二极管 D1 的 2 脚。

由于该网络很可能未在初始 DC Net Identification 阶段登记,请在 Choose Net 对话框中取消选择 List DC nets only 选项,以将该网络显示出来供选择。

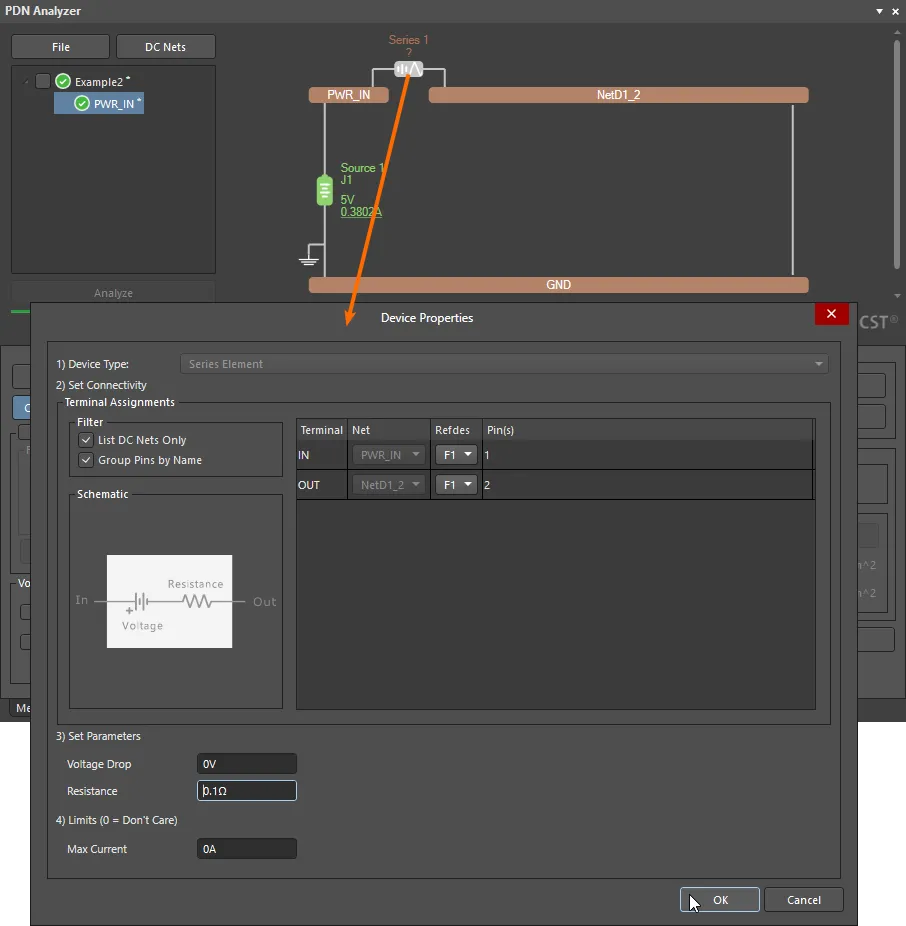

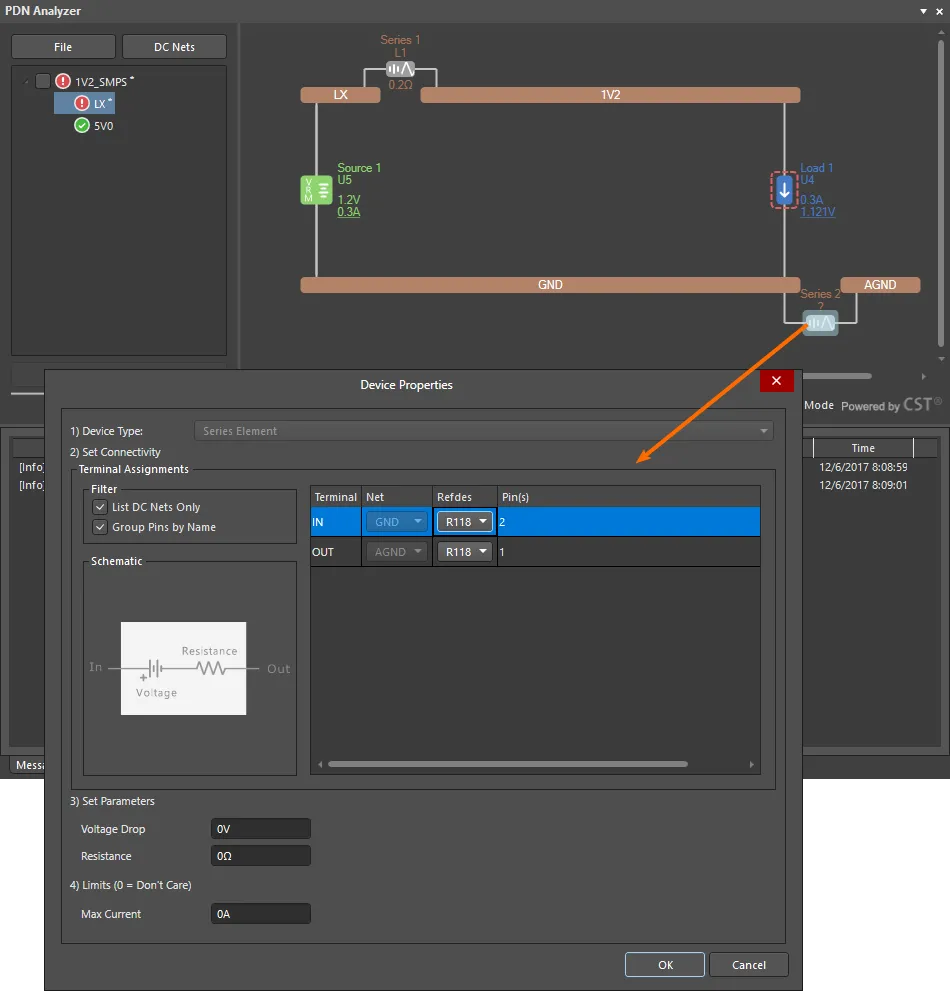

网络扩展过程会在两个网络之间自动添加一个串联元件——双击该元件可在 Device Properties 对话框中指定其连接关系与参数。串联元件模型由一个与电阻串联的电压源组成,可用于对电阻、电感、二极管、开关等器件进行基础建模。

在本例中,该串联元件为保险丝器件 F1,在连接关系 RefDes 选项中选定,并赋予标称内部 Resistance 为 0.1Ω。如果串联元件是半导体器件(如二极管),则需要指定 Voltage Drop 参数以及器件的内部 Resistance 数值。

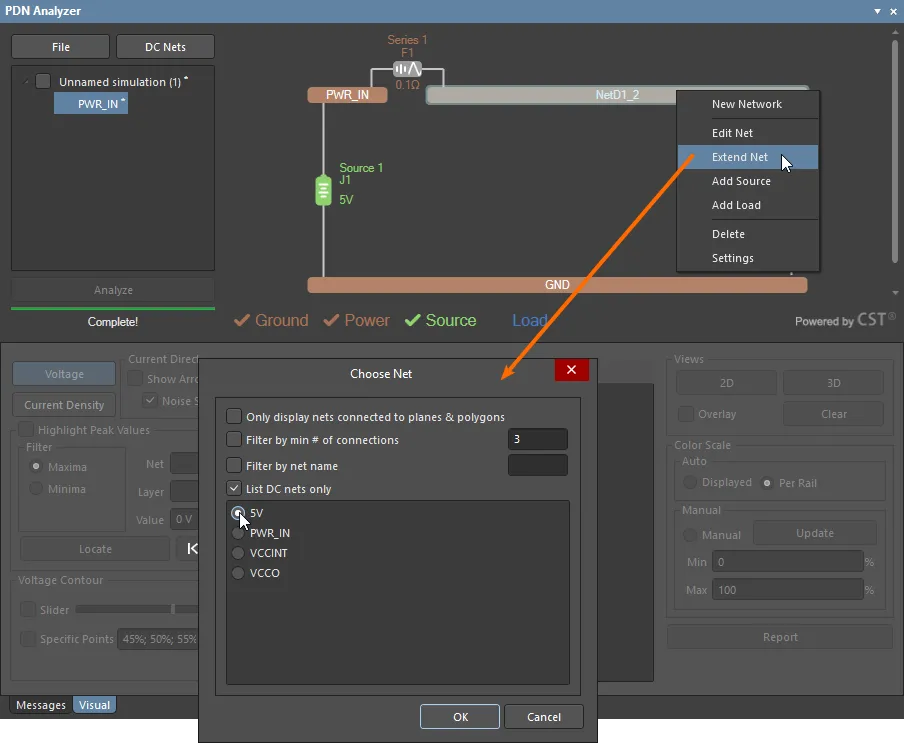

沿着原理图继续,下一步是通过开关器件 S1 将网络 D1_2 扩展到 5V 电源网络。如上所述,从右键上下文菜单中选择 Extend Net,并在 Choose Net 对话框中选择要扩展到的网络。

本例中新增的串联元件(Series Element)是 S1,它通过 3 脚到 2 脚将 D1_2 网络连接到 5V 输出网络(见 schematic)。由于 S1 的备用输入开关(1 脚)与其输出连接(2 脚)相连,且不承载负载电流,作为示例,可在 Device Properties 对话框中使用 pin selection options 将 1 脚从网络分析中移除——双击 OUT 端子条目中的 Pin(s) 字段。现在可以在已连接的电源网络的 5V 部分添加负载——本例为显示模块 LCD1 的负载。

重新运行分析后,PCB Editor 中的数据与图形显示将包含全部三个已连接的电源网络,并显示通过互连串联元件计算得到的电流与压降。

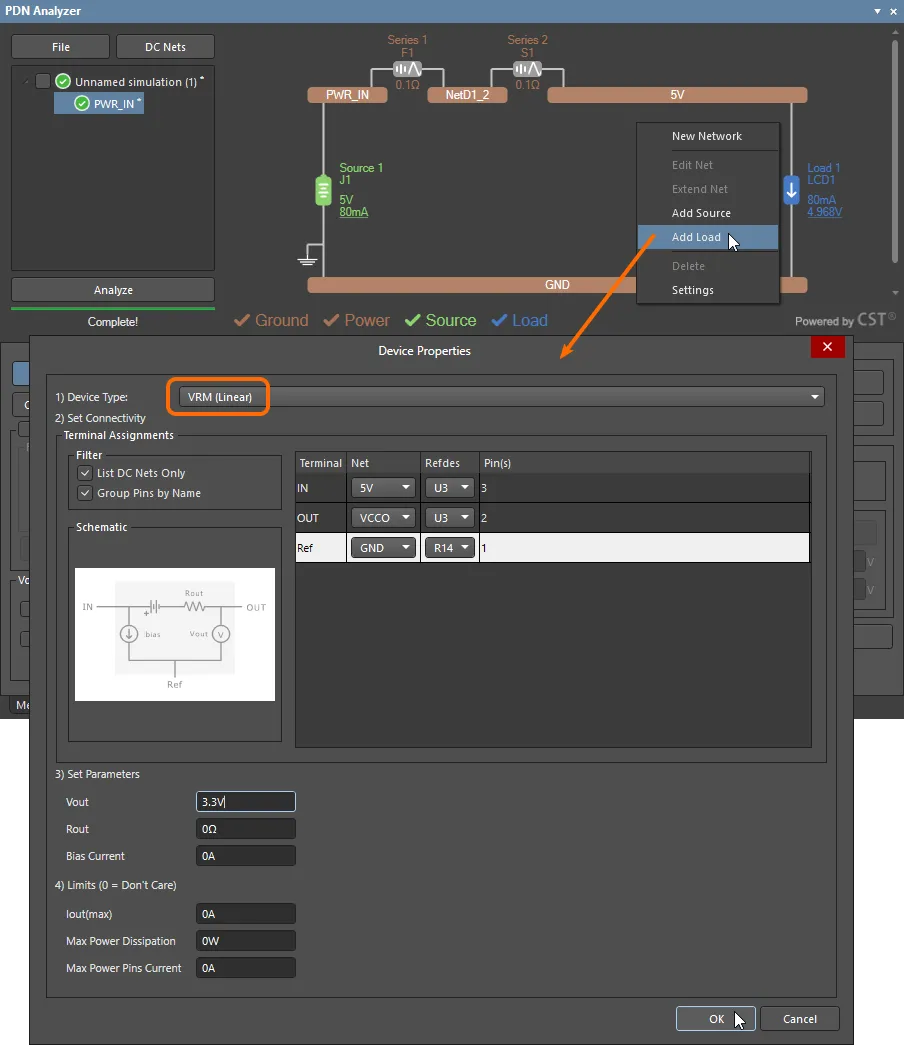

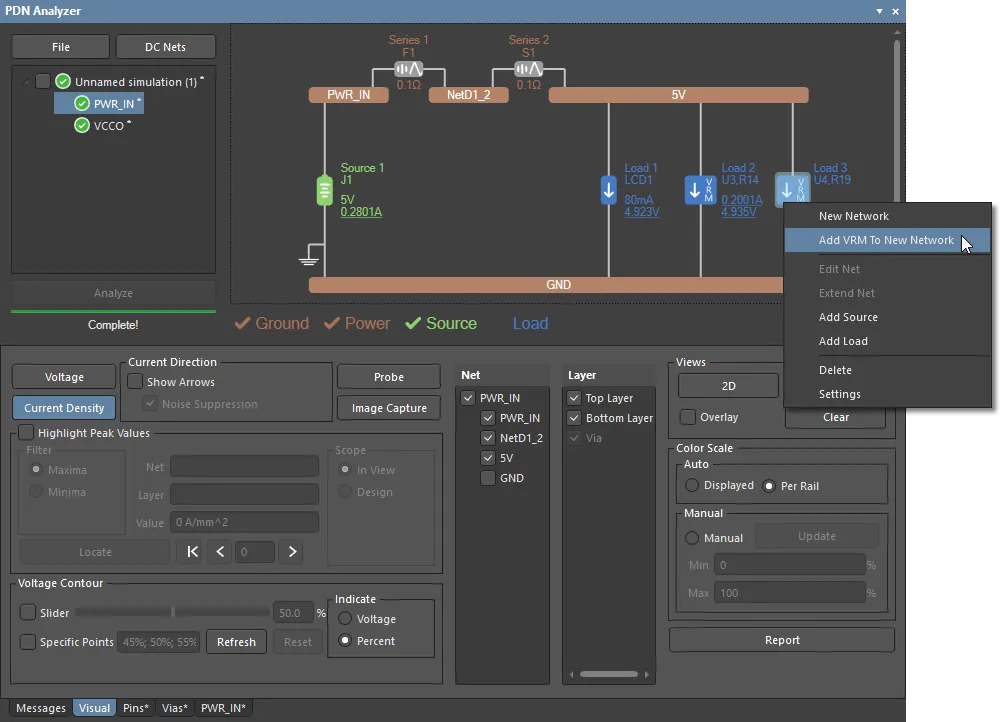

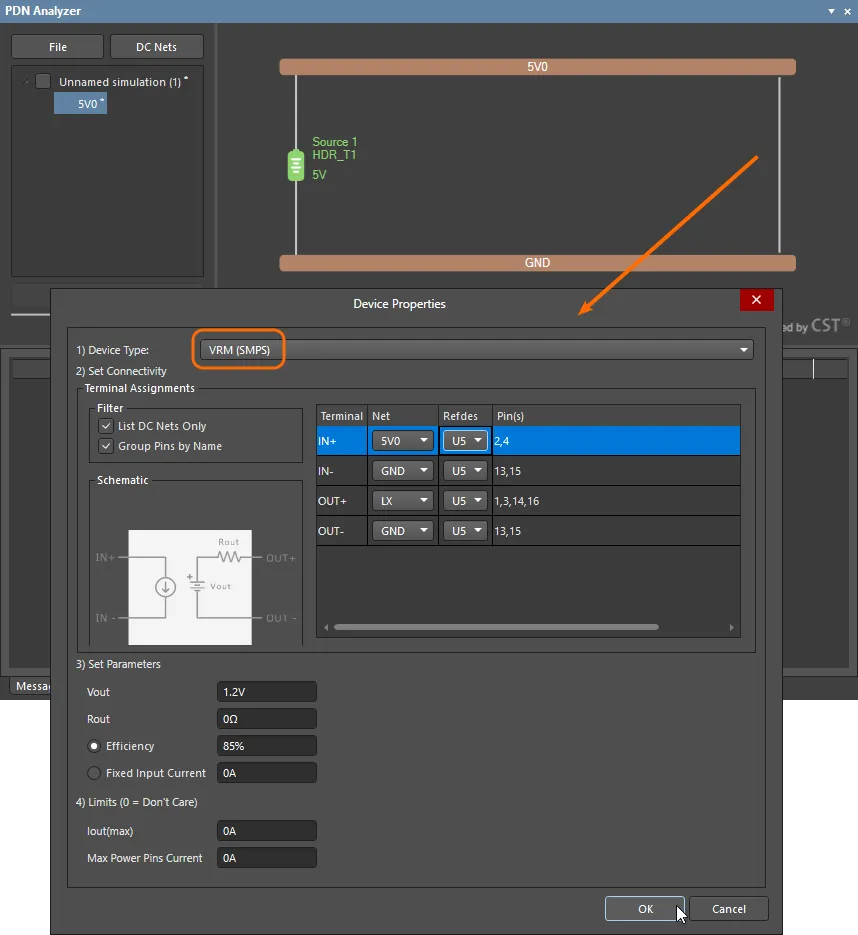

包含稳压器模型

PDN Analyzer 提供可插入在电压输入与输出网络之间的有源稳压器模型(VRM)。当它们被添加到 PDNA 电源网络中时,会同时表现为:电压输入网络上的一个负载(Load),以及电压输出网络上的一个源(Source)。VRM 模型选项包括线性(Linear)、开关模式(Switchmode)以及带远端采样(remote-sensing)的开关模式稳压器。

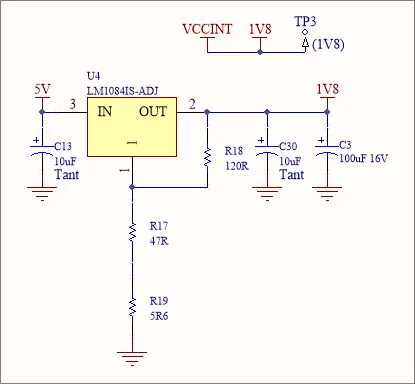

SpiritLevel-SL1 参考工程使用线性稳压器生成 3.3V(VCCO)和 1.8V(VCCINT)电源轨。当将 VCCO 稳压器(U3)加入 PDNA 仿真网络时,它会作为 5V 输入网络上的负载出现,并作为 3.3V 网络的电源(Source)出现。

要将线性稳压器 U3 放置为 5V 网络上的负载(如上述流程所实现),请向 5V 网络添加一个 Load,并在 Device Properties 对话框中将 VRM (Linear) 选项选作 Device Type。按原理图所示设置模型连接,并将 Ref 引脚指定为 R14 的 GND 连接。根据 GND 网络的布局,该参考点也可以位于 PCB 局部区域内不同且可能更合适的位置。

为完成 VRM 设置,请设置其输出电压参数(Vout: 3.3V),并可选设置输出(内部)电阻、静态偏置电流,以及你希望在分析期间被检测到的任何 Limits。

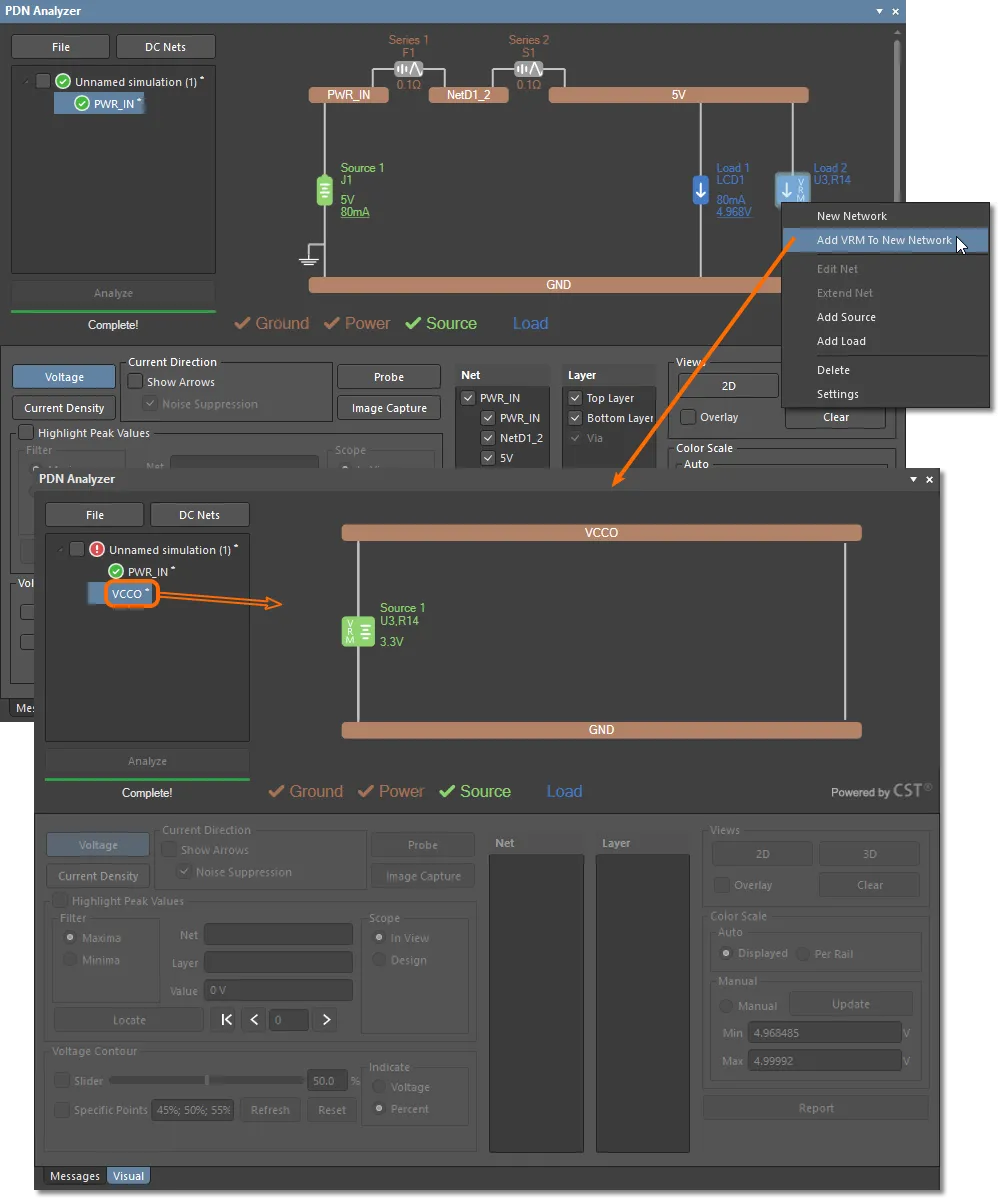

PDNA 提供一种方式,可自动将 VRM 输出侧模型作为 Source 添加到目标输出电压网络,并在必要时创建该网络。

在本示例中,右键单击刚创建的 VRM 负载模型(Load2: U3),并选择 Add VRM To New Network 选项。这将自动创建 VCCO 网络,并将 VRM(Source 1: U3)输出侧模型作为电压源(3.3V)。

请注意,3.3V VRM 的两种表现形式——其输入模型作为 5V 网络上的负载,以及其输出模型作为 3.3V 网络的电源——是交互关联的,且本质上是同一个模型。因此,在 PDNA 界面中可从任一网络访问并编辑该 VRM。

现在可以选择新的 VCCO 网络并添加合适的负载。本例中,这是由器件

U1 的多个引脚汲取的 0.2A 负载电流。

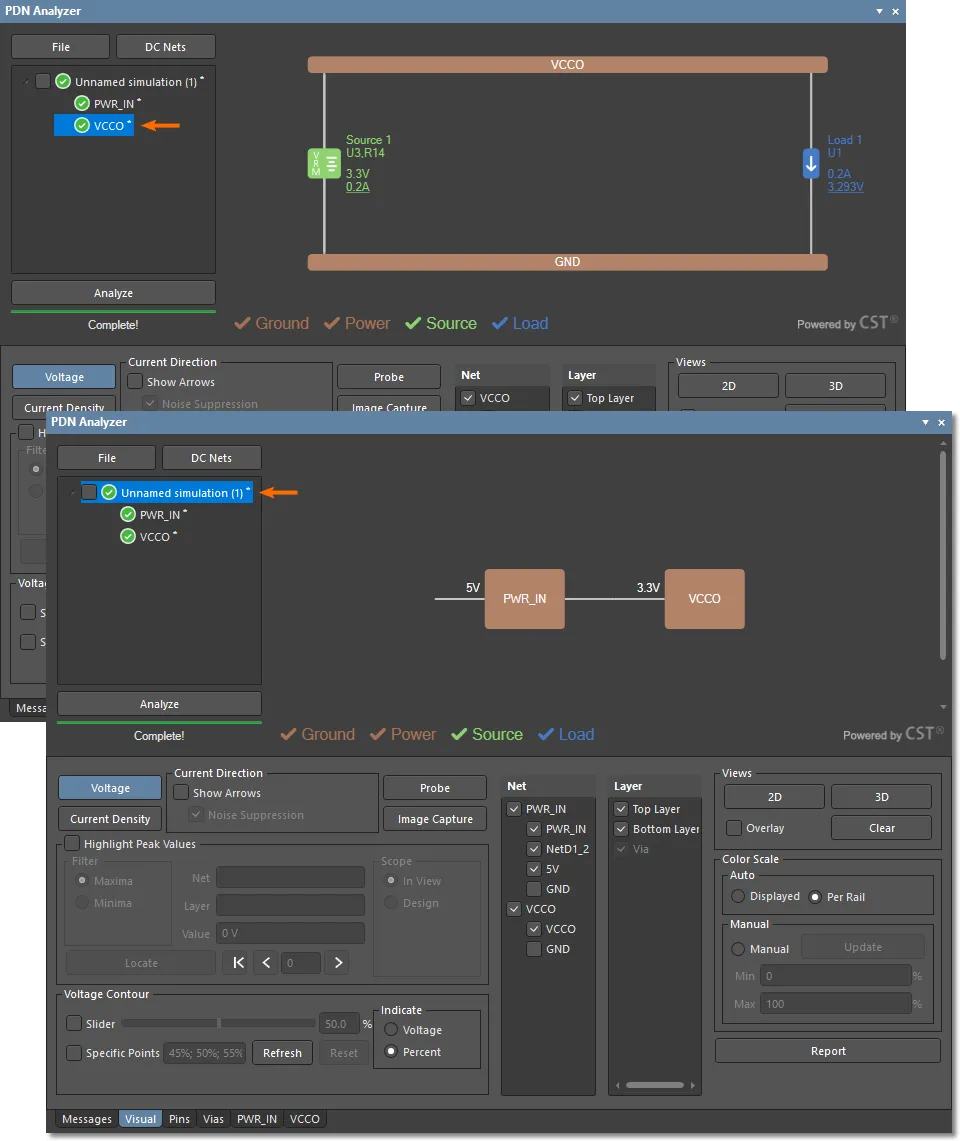

完成后的电源网络结构现在包含两个网络(PWR_IN 和 VCCO),它们通过 3.3V 线性类型 VRM 连接在一起。当在当前 PDNA 文件结构中选择网络层级的顶层时,网络图形会以块图样式概览电源网络的互连关系。

在本示例中,VRM 作为负载被添加到 5V(输入电压)网络,然后用于自动创建 3.3V(

VCCO)电压输出网络,并将 VRM 作为电源。该过程也可以反向执行,在某些情况下可能更方便:先将 VRM 作为电源添加到输出电压网络,再将该模型作为负载添加到“输入”电压网络(

Add VRM To New Network 或

Add VRM To Existing Network)。

PDN 分析将给出包含 VRM 在内的复合网络结果。从图形上看,当在 PDNA 界面中选择网络层级的顶层时,PCB Editor 将显示所有网络。在列表中选择单个网络可将渲染图形限制为该网络,并切换下方面板的

Net 与

Layer 选项以进一步控制视图。

另请注意,本示例的 GND 网络路径现在将包含来自

PWR_IN 与

VCCO 两个网络的回流电流贡献。

通过添加剩余的 VRM(

U4)及其 1.8V 电源输出网络(

VCCINT),即可完成示例工程的配电网络。

按前述方法向 5V 网络添加一个线性 VRM,并将其 Vout 参数设置为 1.8V。

将 VRM(此处为 Load 3)添加到一个新网络,以创建 1.8V(VCCINT)电源网络。

向 VCCINT 网络添加合适的负载——此处为器件 U1 的 1.8V 电源引脚。

此时,PDNA 界面的网络层级将显示全部三个互连网络。

PDN 分析将给出包含 VRM 在内的复合网络结果。

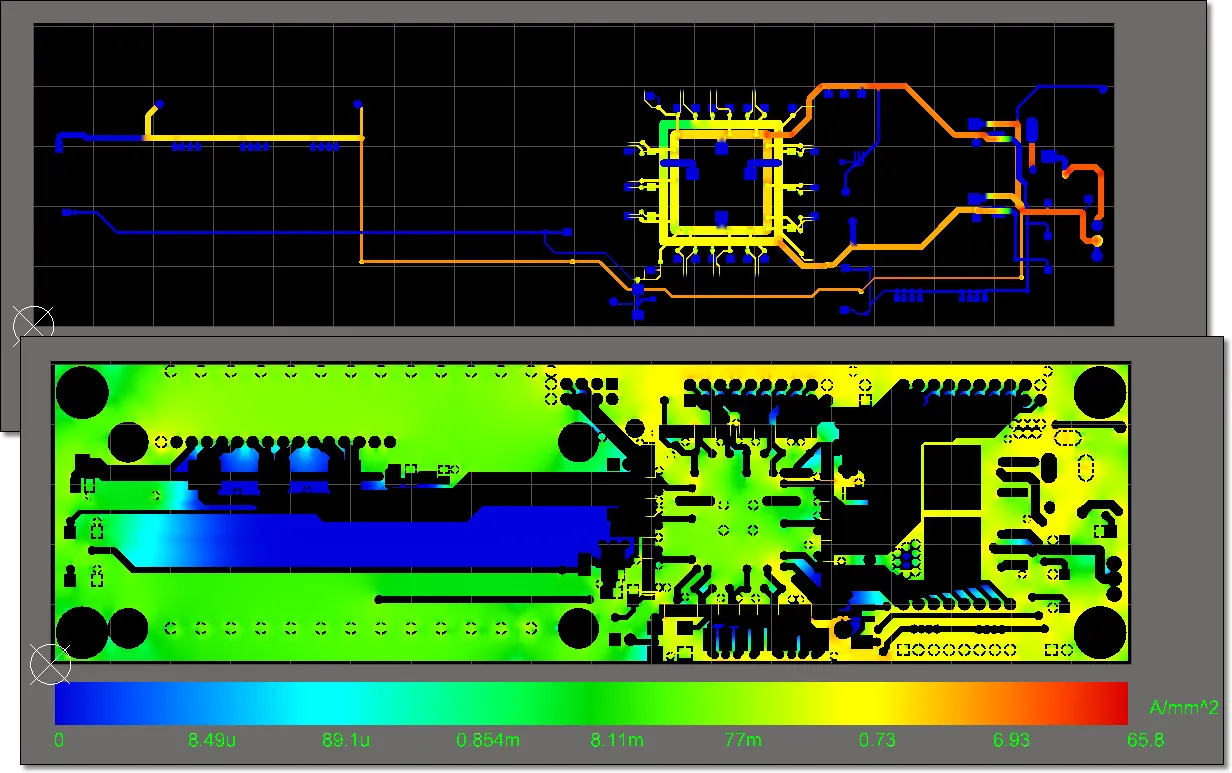

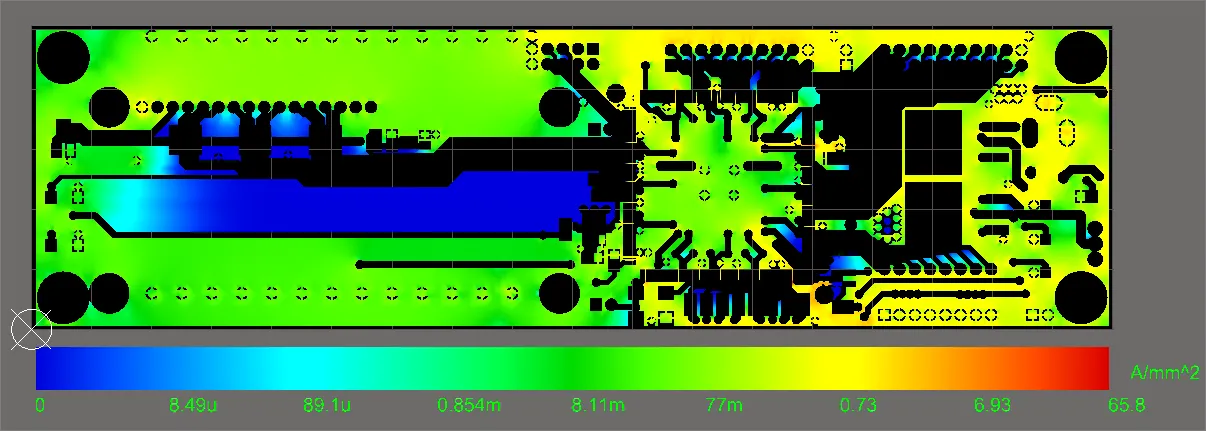

再次注意,GND 网络现在包含三个网络的全部回流电流,因为它们使用公共的 GND 层覆铜形状。其最大电流密度水平(65.8 A/mm2)现在很高,可能会超过可接受的限制。

定位电源完整性问题

PDN Analyzer 提供全面的图形与数据信息,可用于评估并排查已分析 PCB 设计的电源完整性问题。

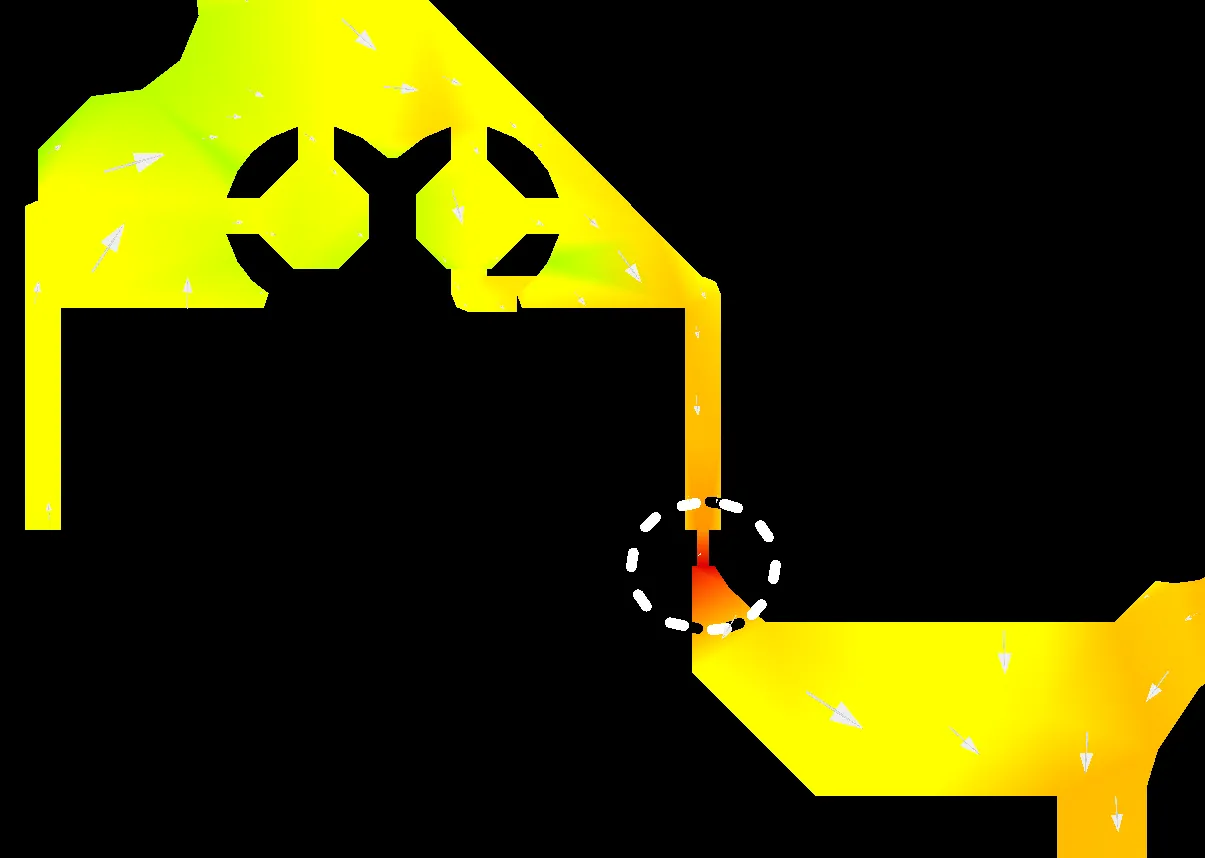

以上述示例为例,对 Top Layer GND 网络路径的分析表明存在不可接受的高电流密度,如最大刻度读数 65.8A/mm2 所示。问题区域的位置并不直观,但可使用 PDNA 的 Highlight Peak Values 功能将其暴露出来。

选择该功能并将 Filter 选项设置为 Maxima 后,峰值电流密度区域将在 PCB Editor 的分析图形中被高亮并标记。

单击  按钮可重复图形高亮,或使用相关按钮(

按钮可重复图形高亮,或使用相关按钮( )按顺序逐个浏览最高峰值读数/位置。设置 Scope 选项,以便仅高亮当前可见 PCB 区域内的峰值(In View)),或高亮整个版图的所有峰值(Design)——后者在逐步浏览时会自动平移与缩放到每个位置。

)按顺序逐个浏览最高峰值读数/位置。设置 Scope 选项,以便仅高亮当前可见 PCB 区域内的峰值(In View)),或高亮整个版图的所有峰值(Design)——后者在逐步浏览时会自动平移与缩放到每个位置。

通过启用 PDNA 的 Show Arrows 功能,还可推断关注区域的更多信息。该功能会叠加多个箭头图形,用于指示该位置的电流方向(箭头角度)与相对大小(箭头尺寸)。在本例中,它确认高密度区域是从 U1(上方)返回到板下边缘 GND 区域的回流路径。

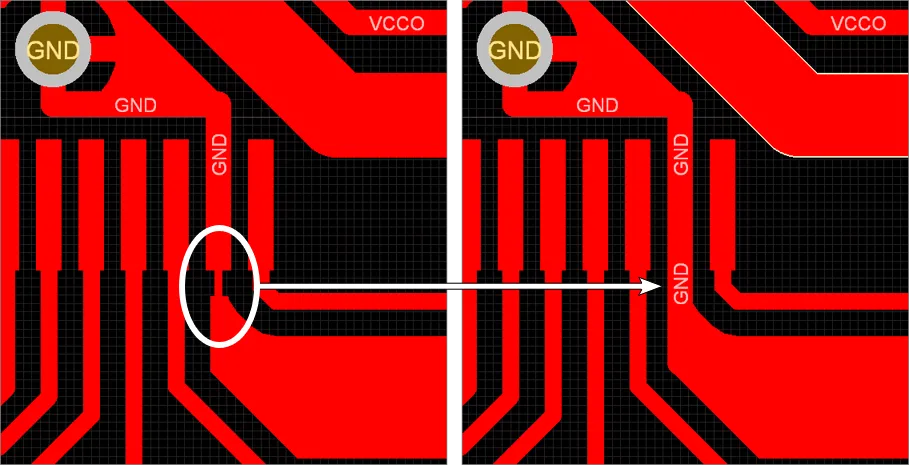

解决该问题的一种方法是增大关注区域内走线的宽度。

在 PDN Analyzer 处于活动状态时也可以完成 PCB 编辑,从而实现迭代式的布局改进并重新分析。在 Views 区域单击 Clear 按钮以在 PCB Editor 中禁用 PDNA 结果,然后继续进行所需的 PCB 编辑。

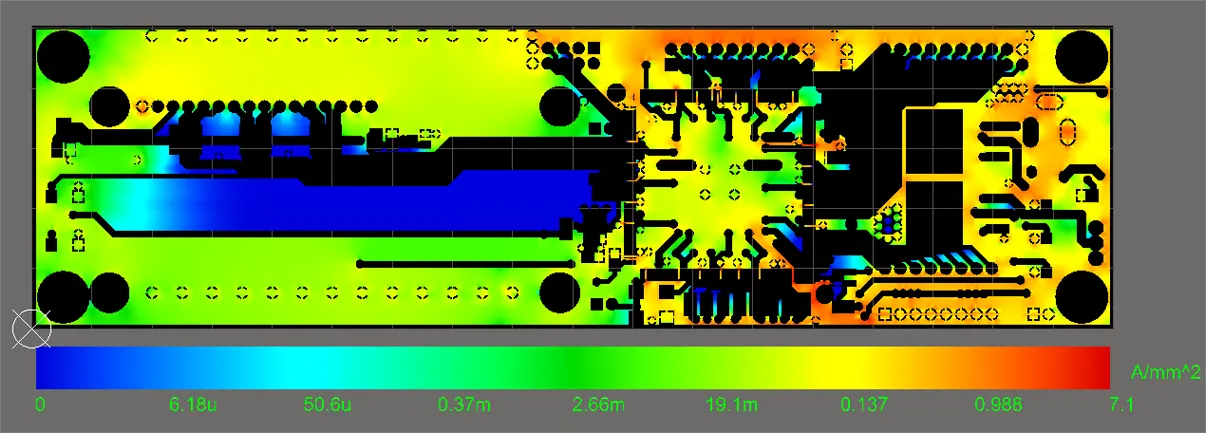

随后可重复进行 PDN 分析(单击  )以检查电源完整性结果。下方两张图展示了在关键点增大走线宽度后,GND 网络(在

)以检查电源完整性结果。下方两张图展示了在关键点增大走线宽度后,GND 网络(在 Top Layer 上)的电流密度变化——上图为初始电流密度结果,下图为 PCB 修改后的电流密度图形。

该“修改前(上图)/修改后(下图)”对比中的要点包括:

-

GND 层的最大电流密度水平已降低到可接受范围,约为之前的十分之一——从

65.8A/mm2 降至 7.1A/mm2。

-

最大电流区域(现在数值更低)在 GND 回流路径中分布更均匀,而不再集中在单一问题位置。

-

若要进行更直观的图形对比,可手动将电流密度刻度设置为之前的数值——选择 Manual 刻度选项,在 Max 字段中输入

65.8,并单击  按钮刷新显示。

按钮刷新显示。

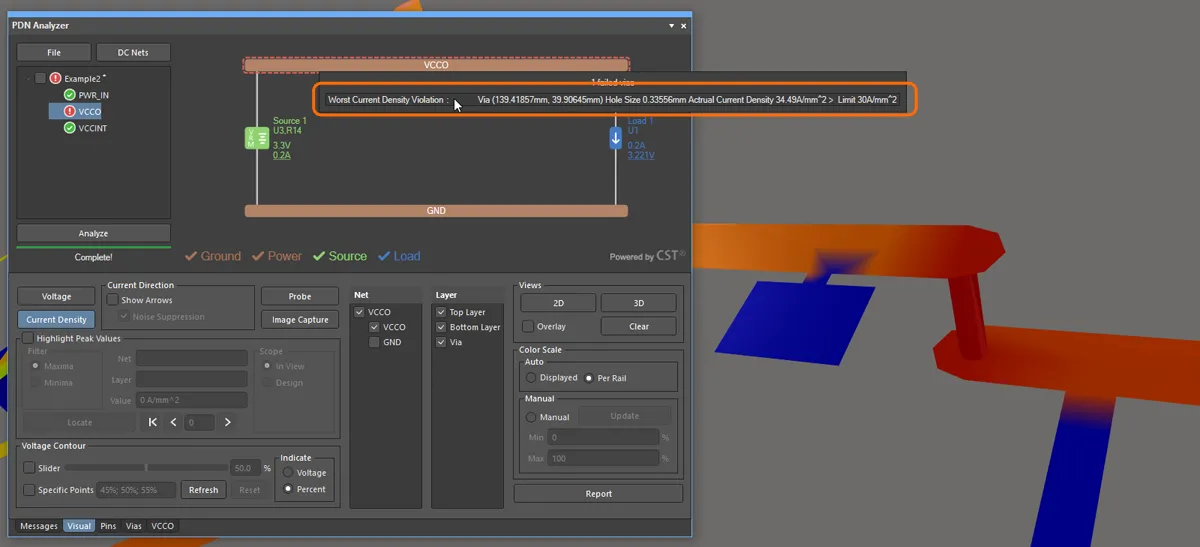

电流密度超限违规

定位并解决 PCB 设计电流路径中的电源完整性问题,一个更客观的方法是定义明确的电流密度限制,一旦超过即触发违规。有关 其他类型的违规 请见下文。

表层/内层与过孔的电流密度限制在 Settings 对话框的 Limits 选项卡下指定。该对话框可通过右键单击当前 PDN 仿真名称并从上下文菜单中选择 Settings 打开。所施加的 Limit 设置将适用于板级设计中的所有表层/内层与过孔。

所指定的电流密度限制适用于当前分析结果,并且无需重新运行仿真即可修改与重新评估——Limit 检测是分析后的处理过程。包含违规的任何网络将以红色虚线轮廓显示。

在此处所示示例中,VCCO 电源网络包含电流密度违规。当选择 VCCO 网络本身时,VCCO 电源路径会通过其高亮轮廓显示为违规。

将光标悬停在发生违规的网络上,会弹出一个列表,显示其当前违规项及相关细节。本例中只有一条记录,表示过孔中的电流密度(约为 34.5A/mm2)超过了已定义的限制(30A/mm2)。

双击该违规条目即可交叉探测到(平移并缩放到)其在板上的位置。在下图中,PDNA 图形视图设置为 3D 模式,从而更清晰地呈现所关注的过孔及其与顶层/底层的连接。

该过孔的相关数据(包括其电流密度违规指示)可在 PDNA 界面的 Via 选项卡下查看。

过孔信息列表适用于当前设计中包含的所有网络。切换 Net 和 Current Density 列标题,可对列表进行排序,以按电流密度对 VCCO 网络的过孔进行排列。任何超过已定义限制的电流密度数值都会以红色高亮显示。

双击过孔列表中的任意条目,即可交叉探测到其在 PDNA 板级图形中的位置。

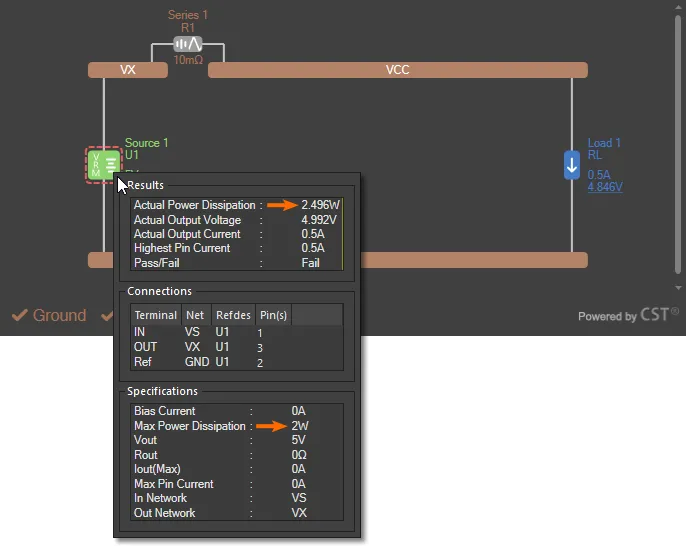

其他违规项

除了检测指定的电流密度限制外,PDN Analyzer 还会检测目标网络的性能违规,例如在添加 Load、Source 或 Series Element 时,在仿真配置中指定的任何 Limit 参数。

这些仿真 Limit 参数包括:

-

Load 处可接受的电压范围

-

Source 的最大输出电流

-

线性稳压器 Source 允许的功耗,以及其最大输出电流。

-

开关稳压器 Source 的最大输出电流。

-

Series Element 的最大电流。

与网络元件的仿真参数(例如 Source 电压或 Load 电流设置)不同,后者会在运行分析时被处理;而对任何 Limit 参数违规(例如在 Load 处指定的最小电压)的检测属于分析后的处理流程。这意味着,修改 Limit 参数的数值会被立即检测到,无需重新运行仿真分析。

当指定了 Limit 参数(其值非零)时,若该参数发生违规,违规的网络元件会在 PDNA 界面的网络图形中被高亮显示。将光标悬停在该元件上即可查看其参数与分析结果。

在下方示例中,Source 1(电压调节器 U1)的计算功耗已超过其定义的最大功耗参数 2W。

关于电源网络性能的更详细信息可在其网络选项卡下查看,该选项卡以表格形式呈现分析结果数据,并包含计算得到的网络功耗数值。

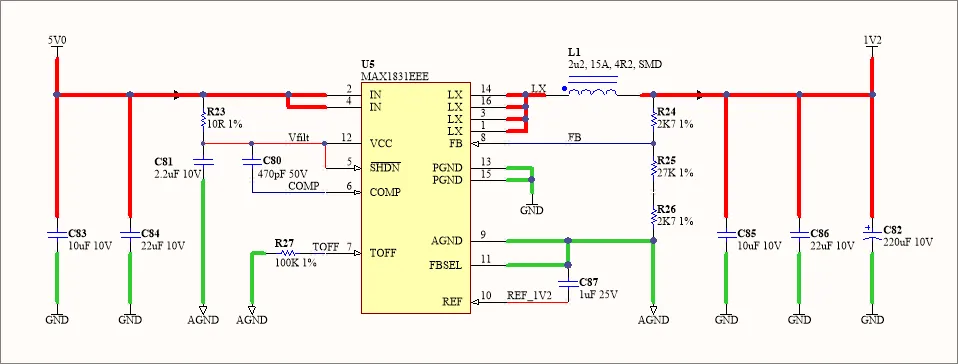

示例 3

本示例演示了在电源网络中应用 PDN Analyzer 的开关模式电源(SMPS)仿真模型(VRM),并展示更新后的网络模型如何提供更准确的电源分析结果。该示例还概述了如何使用 PDNA 的 Voltage Probe 与 Contour 功能,以显示板级布局形状中特定点或区域的电压数据。

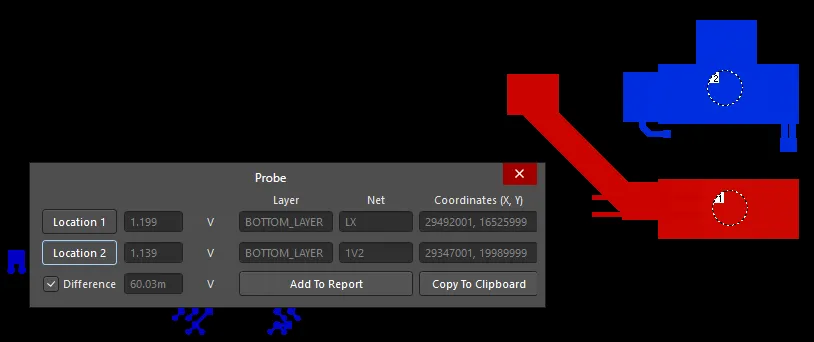

该示例基于 Altium 的 DB46 Xilinx Daughter Board 参考工程,并聚焦于用于该设计 1.2V 电源网络(1V2)的 SMPS 部分(U5)。

同样,本 PDN 仿真示例的前置条件为:

-

DB46 Xilinx Daughter Board 工程已在 Altium Designer 中打开

-

PDN Analyzer 应用已激活(Tools » PDN Analyzer)

-

PCB 设计的 DC Nets 已在 PDN Analyzer DC Net Identification 对话框中识别,如上文 所述。注意:本示例还需要网络

LX 和 AGND。

通过在新仿真中指定输入电源网络来开始构建示例电源网络的流程(如有需要,选择 File » New Simulation)。如上方原理图所示,PDN <Power Net> 为 5V,而 <Ground Net> 为 GND。5V 网络的 Source 为连接器排针 HDR_T1 或 HDR_B1。

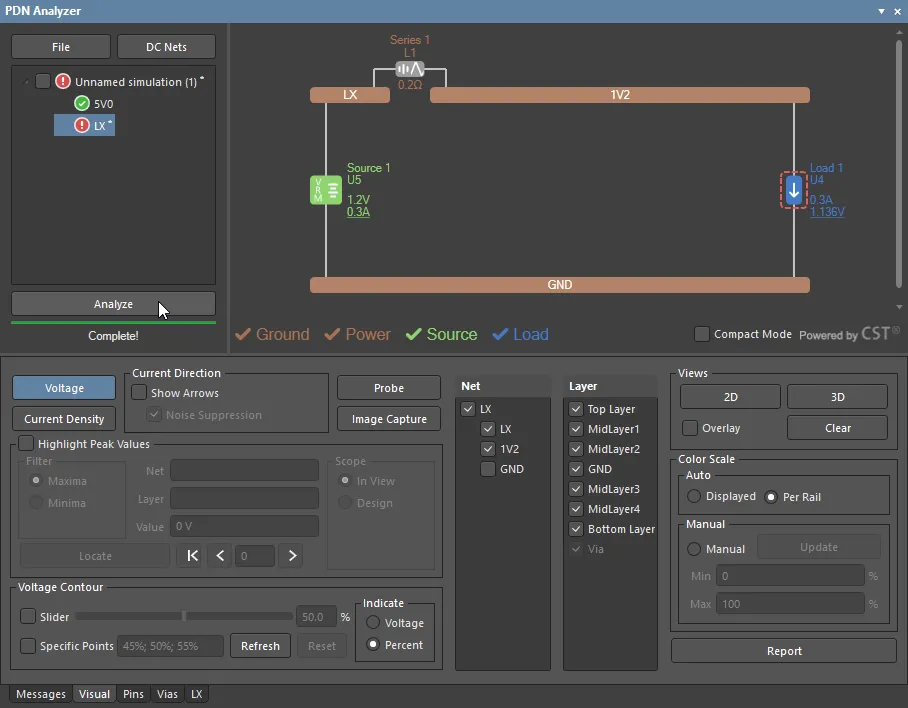

开关模式 VRM

在 Device Properties 对话框中选择 VRM(SMPS) 作为 Device Type,即可将该设计 SMPS 电路的模型添加到 5V 电源网络中。根据对话框中模型的原理图,IN 与 OUT 引脚组是分别定义的。

为正确地为该电路定义此模型,请将 LX 指定为输出,将 U5 用于 RefDes 选项,并将 1.2V 设为 Vout 参数——如上方原理图所示。可选地,将 Rout 以及效率/电流参数设置为与所用 SMPS 器件相对应。

通过将 VRM 添加到其输出网络(Add VRM To New Network)来完成 SMPS 模型的实现,该网络将自动被选为 LX 网络。随后可按 schematic 将 LX 网络扩展以包含 1.2V 电源网络。

LX 与 1V2 网络通过 Series Element L1(SMPS 降压电感)相连,该元件应设置为具有合适的串联电阻。为便于本示例演示,这里将其设置为相对较高的 0.2Ω。

最后,在 1V2 网络上添加 U4 作为 0.3A Load,并指定可接受的负载电压偏差为 +/-5%。注意:本示例中,Settings dialog 的 Limits 选项卡下的电流密度限制选项应设置为 0(默认的 No Limit 状态)。

运行分析后可注意到,复合网络 LX 上的 Load 显示 Violation,这是因为该负载处的 1V2 网络电压(U4)低得不可接受(约为 1.14V)。

数据探针

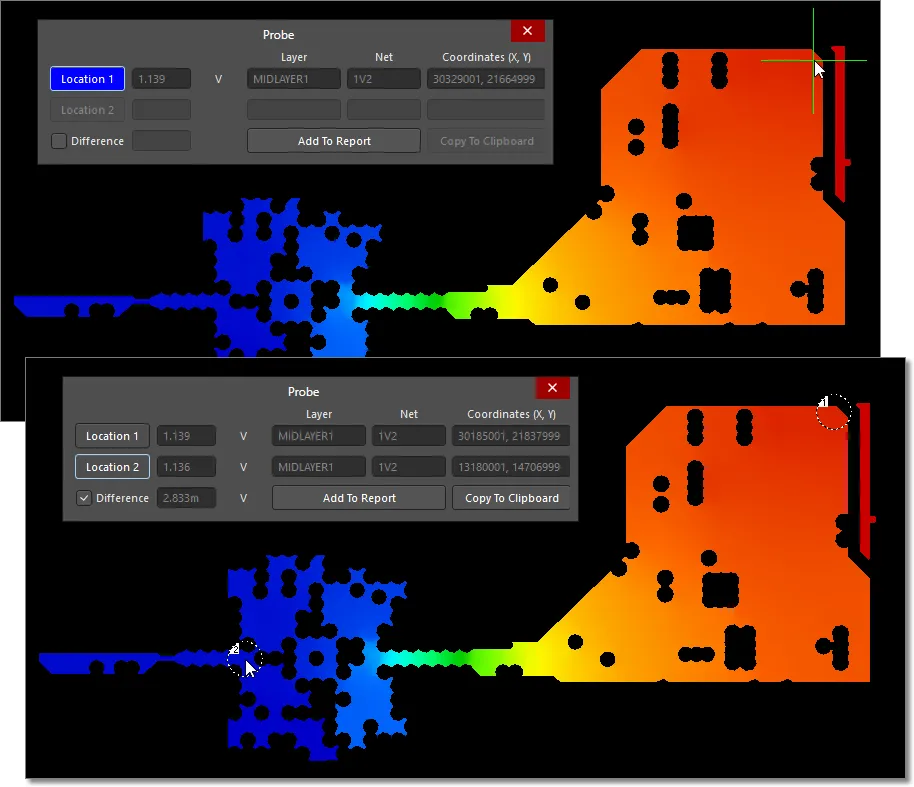

除了在 PCB Editor 中对 PDNA 图形与比例尺进行可视化解读外,PDN Analyzer 还提供了多种工具,用于解读设计布局中特定区域或点位的分析结果数据,例如当前激活的 Probe。

Probe 工具允许记录并比较设计布局中指定点位的电压或电流密度数据。该工具的灵活性提供了一种方法,可在任意网络或层上准确判断分析数据结果。不过在本示例中,它可用于确认 1V2 网络负载处不可接受的压降来源——显然是由 L1 Series Element 的电阻导致。

要对 1V2 网络电压执行差分探针读数,首先将 PNDA 设置为仅显示 Layer MidLayer 1(这是通往 U4 的主要 1.2V 路径)以及 Net 1V2。选择  按钮打开 Probe 对话框并启用第一个探针位置(

按钮打开 Probe 对话框并启用第一个探针位置( )。使用光标十字准星指定最高电压点(该层上

)。使用光标十字准星指定最高电压点(该层上 1V2 网络的源端),然后勾选探针的 Difference 选项并指定第二个位置( )——最低电压点,即

)——最低电压点,即 U4 负载处。

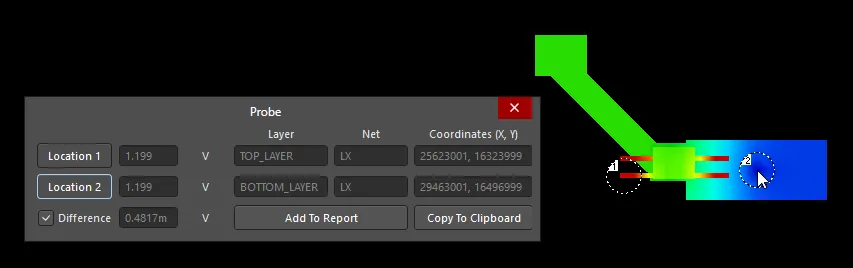

注意,探针的 Difference 读数表明该网络路径的压降仅约为 3mV。同样地,检查 LX 网络路径(Top 与 Bottom Layer 激活),将显示约 0.5mV 的压降。

对两个网络(启用 Net LX 与 1V2,Top 与 Bottom Layer)执行探测电压差测试 between,可显示电感 L1 上的 60mV 压降,这是触发该特定 analysis Violation 的主要电压损失。

尽管此处所示的电压 Probe 调查已确定电源网络中 IR 损耗的主要原因,但也可以通过检查 PDNA 的 Pins 选项卡下的器件引脚电压数据,更直接地解决该问题。Probe 功能更适用于需要更深入调查的场景,在这些场景中可充分利用其位置精度优势。

SMPS-sense VRM

本示例中使用的开关模式电源电路通常会使用电阻值低得多的电感(L1)。不过,此处的分析结果确实凸显了基础 SMPS 模型无法考虑 L1 中的损耗——但一般而言,这在实际电路中并不会成为问题。

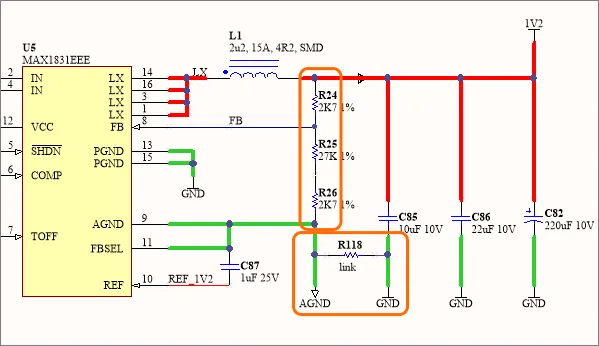

在示例工程的 SMPS 电路中,由 U5(引脚 8)感测的电压反馈来自电阻链 R25–R26,该电阻链位于 1V2 输出网络与模拟地网络 AGND 之间。后者通过 0Ω 连接电阻 R118 与 GND 网络相连。

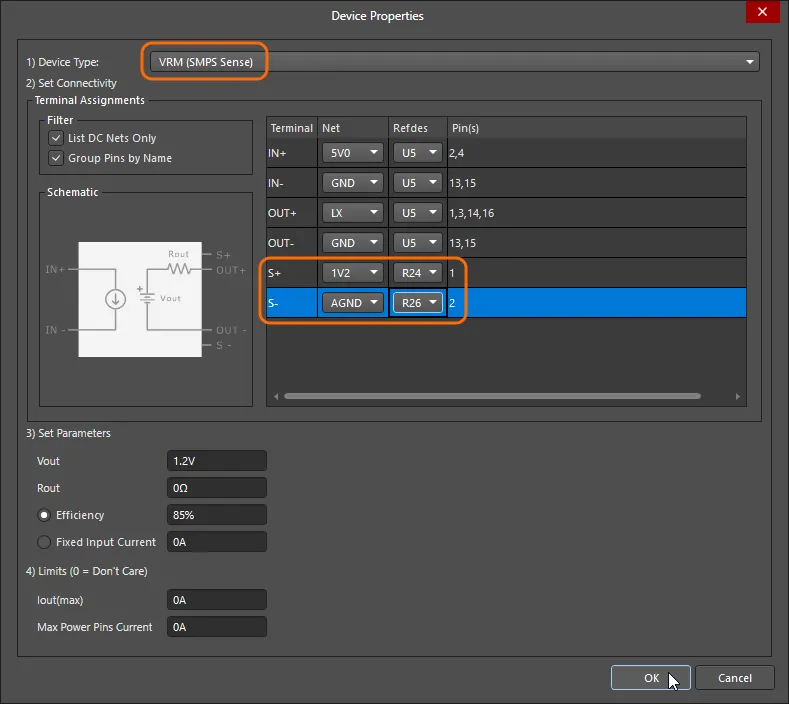

为更准确地建模 U5 周边的电路行为,可使用 PDNA 的远端采样开关模式模型来替代标准 SMPS 器件。该模型提供独立的电压采样端子(S+ 与 S-),可“连接”到指定输出网络上的任意引脚——例如本电路中电压采样电阻链的引脚。

为 U5 SMPS 电路创建更完整网络模型的第一步,是将 AGND 网络添加到现有的 GND 网络中。使用 Extend Network 选项并选择 AGND 网络。

AGND 网络通过电阻 R118 与 GND 网络相连,如上方 schematic 所示,其应设置为 Resistance 值 0Ω。

要更新 LX 网络中的 SMPS 模型,请删除现有的 U5 源器件(Source 1),然后在其位置添加替代的 SMPS Sense 模型。按之前方式设置该模型的 IN 和 OUT 端子连接。感测端子(S+/S-)按 schematic 所示,设置在电路反馈电阻链的两端。

将替换后的 SMPS 模型从 LX 网络传播到源 5V 网络,使网络相互对应:先删除其 U5 Load,然后在 LX 网络中应用 Add VRM To Existing Network » 5V Source 选项。

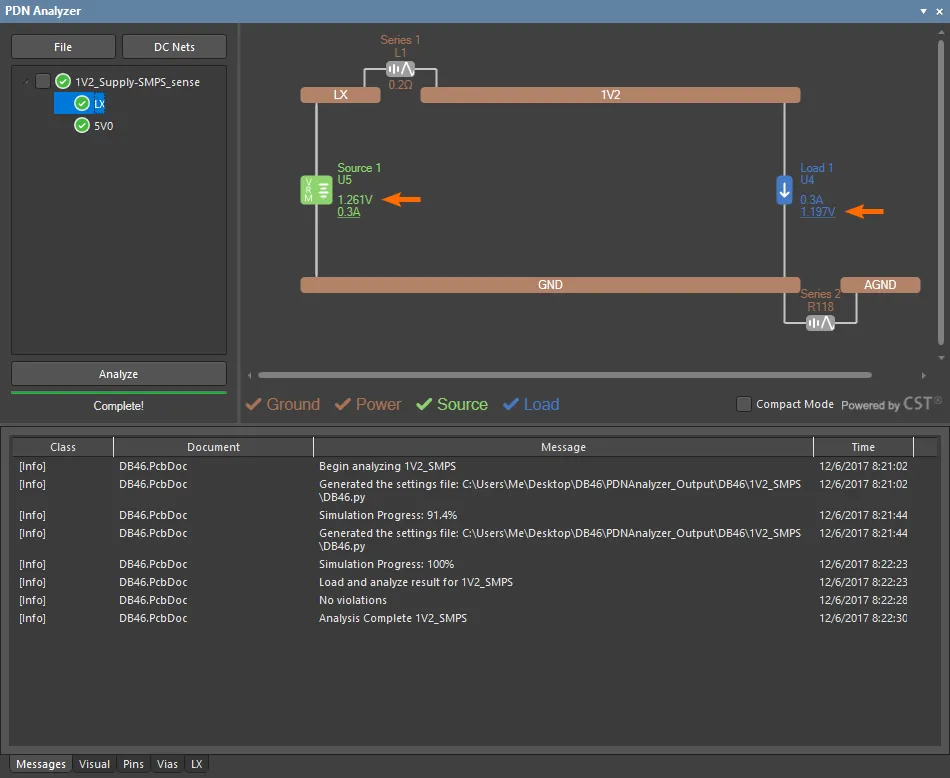

随后即可对更新后的电路重新进行分析以评估结果。 如下图所示,负载电压现在完全满足 +/-5% 要求,并且不再显示 Violation。由于在 1V2 网络处对输出电压进行感测,SMPS 已对串联元件 L1 中的电压损耗进行了补偿——因此,LX 网络处的电压会 60mV 更高。

虽然针对该特定电路使用高级 SMPS-sense 模型能得到更准确的分析结果,但在实际应用中,具备远端感测能力的 SMPS 器件可能会将感测端子直接通过 PCB 连接到负载本体,而不是连接到附近的反馈网络。在这种情况下,两条感测线(S+ 和 S-))会通过专用 PCB 走线连接到(或接近)负载各自对应的端点。

Voltage Contour

如上所述,决定将 SMPS 远端感测线放在何处,是 PDN Analyzer 的 Voltage Contour 功能众多用途之一;该功能以图形方式指示板级布局中的关键电压过渡点。

该功能可在 PCB Editor 图形界面中,对所显示的层叠加虚线电压等值线。可指定并显示多条等值线,既可以按网络压降的百分比显示,也可以按实际电压值显示——参见 Indicate 选项。

除在指定百分比点设置的一组等值线外,还可使用 Slider 选项加入一条额外的线,该选项提供一种连续调节的方法来设置线的过渡点。

例如,为 SMPS 确定合适的正端负载感测点时,理想情况下感测线应连接在负载处电压降小于(例如)20% 的位置。对于上方所示的 SMPS-sense 示例,从 U5(S+)引出的感测线走线,可在 U4 负载引脚(左侧)与 20% 电压等值线之间的任意便捷位置,连接到 1V2 网络的电源覆铜区域。

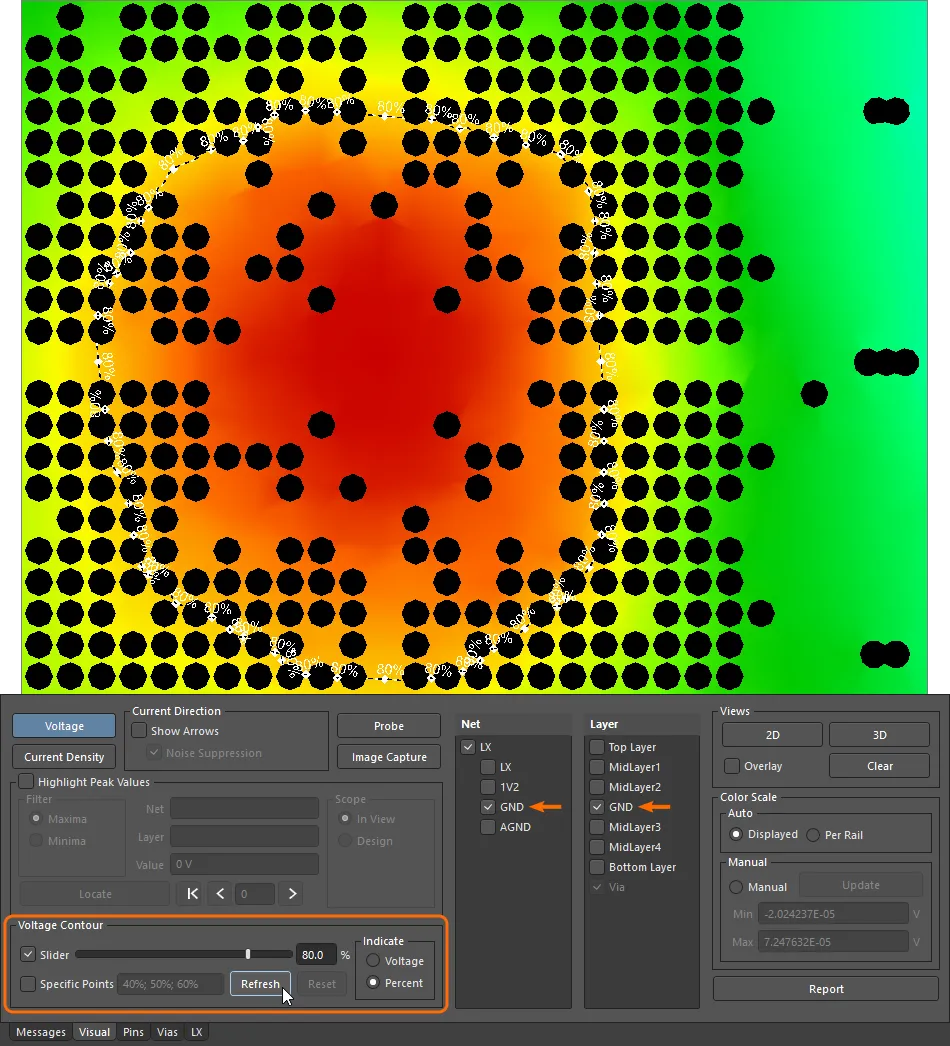

同样地,为确定 SMPS(U5)的负端感测线(S-)的合适取样位置,可在 GND 层为负载(U4)回流路径设置例如 80% 的 Voltage Contour 线。在这种情况下,由于这是负载回流电流(负向回流),负端感测线连接所需的理想地覆铜位置应位于 80% 等值线的边界范围内。

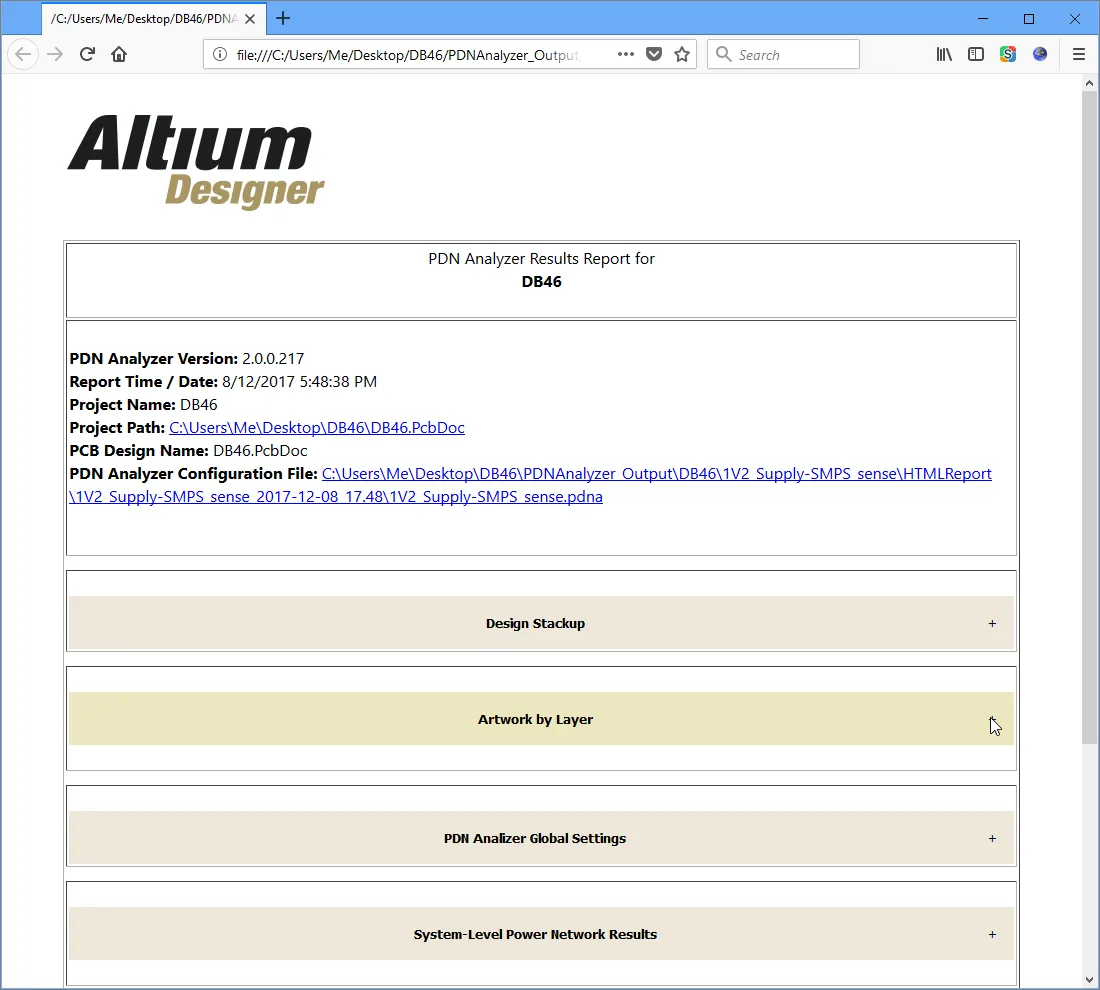

Analysis Report

为保存电源完整性分析结果以便进一步检查或分发给相关方,PDN Analyzer 提供数据与文档 Report 功能。Report 功能会生成一份非常全面的、基于 HTML 的文档,其中包含当前分析结果以及板级设计本身的图形与数据。

选择  按钮,在 HTML Report 对话框中配置 Report 选项。勾选 Results 包含项复选框以设置 Report 中包含的细节程度,并检查要包含在 Report 文件夹(

按钮,在 HTML Report 对话框中配置 Report 选项。勾选 Results 包含项复选框以设置 Report 中包含的细节程度,并检查要包含在 Report 文件夹( )中的已捕获图像——使用主界面中的

)中的已捕获图像——使用主界面中的  按钮来捕获分析结果图像。

按钮来捕获分析结果图像。

点击  按钮生成可交互的 HTML Report 并打开其所在文件夹;该文件夹将包含所有图像(包括已捕获的图像)以及相关的分析配置文件(

按钮生成可交互的 HTML Report 并打开其所在文件夹;该文件夹将包含所有图像(包括已捕获的图像)以及相关的分析配置文件(*.pdna)。