PDN Analyzer (by CST)

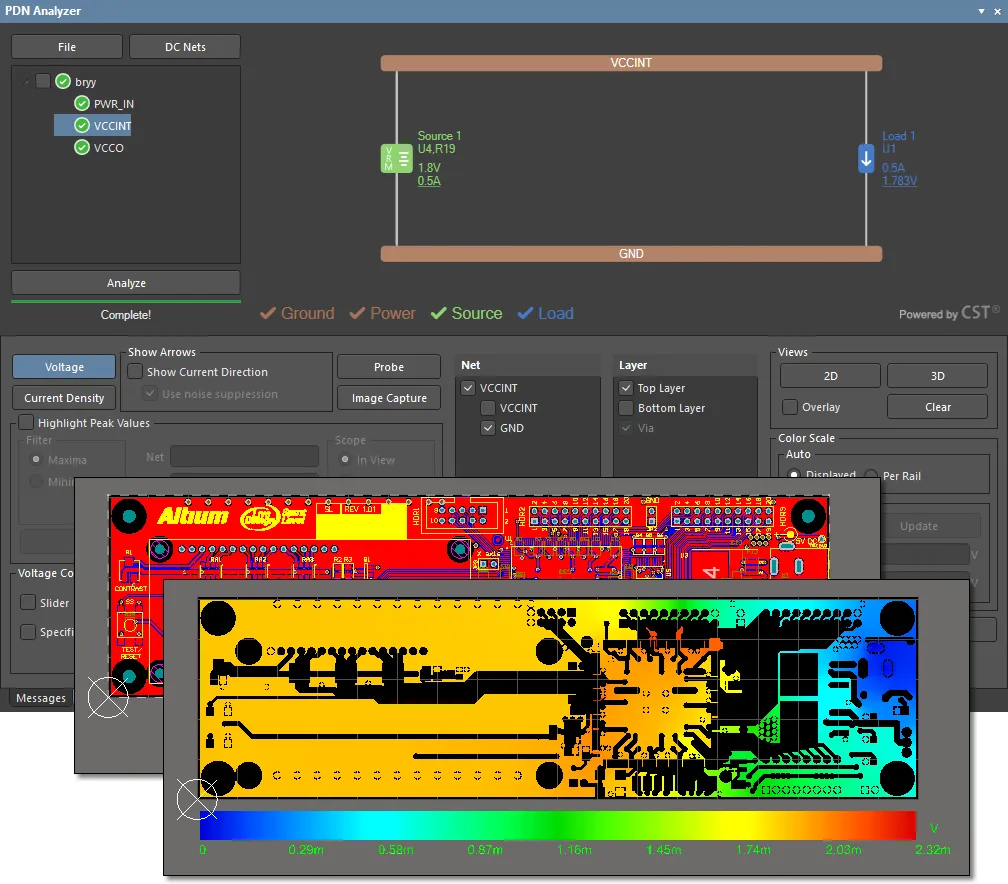

PDN Analyzer powered by CST® (Computer Simulation Technology) si integra direttamente con Altium Designer per consentire la simulazione e l’analisi PI-DC del progetto PCB corrente. Poiché il PDN Analyzer funziona all’interno di Altium Designer, non sono necessari import/export manuali dei dati, conversioni dei dati o l’esecuzione di applicazioni separate: basta avviare il PDN Analyzer dall’editor Schematic o PCB, impostare i parametri di test desiderati ed eseguire la simulazione. I risultati vengono forniti principalmente tramite la modellazione 2D/3D del layout in rame della scheda, consentendo una rapida valutazione dei risultati e la possibilità di effettuare test esplorativi “what if” sul progetto di layout del PCB.

L’interfaccia PDN Analyzer mostrata con il PCB di esempio Altium Designer Spirit Level, e i risultati di una simulazione PI-DC Voltage Drop del ritorno della net GND sul suo layer Top per l’alimentazione VCCINT.

Accesso alla funzionalità PDN Analyzer

Per accedere alla funzionalità PDN Analyzer in Altium Designer, l’estensione software deve essere installata. Questa estensione può essere installata o rimossa manualmente.

Per maggiori informazioni sulla gestione delle estensioni, fai riferimento alla pagina Extending Your Installation (Altium Designer Develop, Altium Designer Agile, Altium Designer).

Per accedere alla funzionalità, devi anche avere un abbonamento valido a PDN Analyzer.

Fondamenti di Power Integrity

In sostanza, il problema PI-DC (o “IR drop”) è piuttosto semplice: la resistenza presente nelle forme di alimentazione della scheda (tracce, poligoni, piani, ecc.) consuma potenza e tensione, sottraendole ai vari carichi. Come ci si può aspettare, i problemi di IR aumentano di complessità con il numero di carichi sull’alimentazione, a causa dell’interazione nei percorsi in rame di alimentazione e di massa.

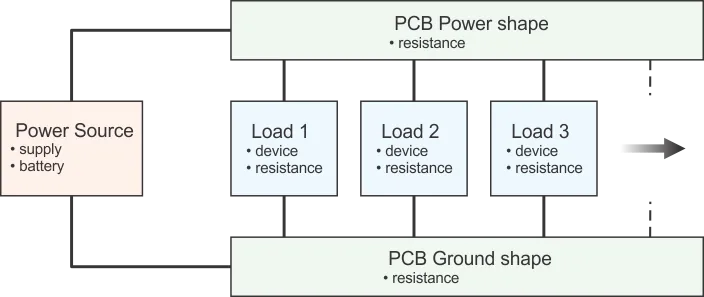

Figura 1: Diagramma a blocchi di base delle forme di alimentazione e di massa e dei carichi applicati.

La Figura 1 (sopra) mostra un semplice diagramma a blocchi della sorgente di alimentazione di un circuito e delle sue forme di alimentazione e di massa (tracce e piani) che forniscono energia ai vari carichi (memorie, microcontrollori, ecc.). Nota che tutti i carichi sono collegati alle stesse forme di alimentazione e di massa e dipendono da esse per ottenere la/le propria/e tensione/i di esercizio. In generale, tendiamo a supporre che queste forme di alimentazione e di massa abbiano una resistenza di 0Ω, cosa che non è necessariamente vera, e questa supposizione può causare problemi. Poiché spesso sono coinvolte correnti relativamente elevate, anche piccole resistenze nelle forme di alimentazione e di massa possono causare un consumo significativo di potenza (perdita) e cadute di tensione.

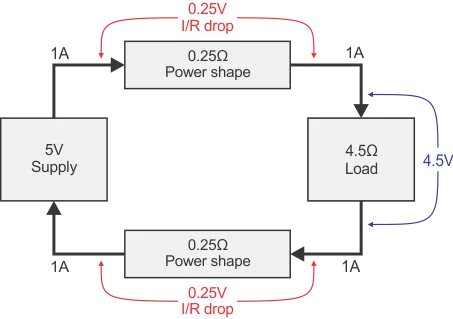

Figura 2: Effetti dell’“IR Drop”

La Figura 2 mostra un esempio dei problemi che possono sorgere se la resistenza delle forme di alimentazione e di massa non viene considerata correttamente. Anche se ciascuna forma ha una resistenza relativamente piccola di soli 0,25Ω, esse hanno causato una caduta della tensione sul carico da 5V a 4,5V. Il progettista deve essere consapevole di questa caduta e assicurarsi che possa essere tollerata, oppure modificare il progetto per ridurla, così da garantire che il progetto finale non fallisca sul campo.

Il problema, tuttavia, sembra facile da risolvere: basta semplicemente rendere le forme di alimentazione e di massa corte o abbastanza grandi da rappresentare una resistenza trascurabile, usando la seguente relazione: R = ρ * L/A, dove:

-

Rè la resistenza totale di una forma (traccia o piano) -

ρè la resistività del materiale usato per la forma (tipicamente rame,ρ ≈ 1.7µΩ-cm) -

Lè la lunghezza della forma -

Aè l’area della sezione trasversale della forma (larghezzaxspessore)

In parole semplici, se rendi le forme di alimentazione e di massa corte, spesse e larghe, ne minimizzerai la resistenza.

La difficoltà, tuttavia, è che forme eccessivamente grandi consumano prezioso spazio di sbroglio e possono limitare lo spazio disponibile per altre forme di tensione. Un progetto con forme di alimentazione e di massa dimensionate correttamente sarà più compatto e userà meno layer rispetto a uno che utilizza arbitrariamente piani o tracce eccessivamente grandi. Lo scopo dell’analisi PI-DC è informare il progettista che le forme di alimentazione e di massa del progetto della scheda sono adeguate, ma non eccessivamente grandi.

Un’altra considerazione relativa all’IR drop è il fatto che la quantità di potenza consumata è I2R – quindi un piccolo aumento della corrente attraverso una resistenza provoca un grande aumento del consumo di potenza. Questo può manifestarsi come problemi termici, in cui il progetto si riscalda in modo significativo perché le forme di alimentazione e/o di massa non sono abbastanza grandi da gestire la corrente che le attraversa. Garantendo un IR drop molto ridotto attraverso le forme di alimentazione e di massa, il consumo di potenza in tali forme viene minimizzato.

Nel caso estremo, se una forma è sufficientemente resistiva (molto stretta e lunga) e vi scorre una corrente sufficiente, quella forma diventa essenzialmente un “fusibile”, fondendo quindi la forma in rame e causando il guasto del progetto, con possibile creazione di una situazione pericolosa. Lo standard IPC-2152 per la capacità di trasporto di corrente dei PCB affronta questo problema, ma con ipotesi pessimistiche (ad esempio, nessun rame termicamente conduttivo nelle vicinanze che aiuti a dissipare il calore) e i progettisti spesso applicano tale specifica usando le ipotesi più conservative, come consentire solo un aumento minimo della temperatura. Sebbene PI-DC non possa sostituire lo standard IPC-2152 come linea guida per le considerazioni termiche, può fornire preziose indicazioni su come un progetto possa essere ottimizzato in sicurezza studiando le cadute di tensione e le densità di corrente del sistema di distribuzione dell’alimentazione. Un progetto ottimizzato per la minima densità di corrente e la minima caduta di tensione tra le sorgenti e tutti i carichi genererà anche meno calore e avrà meno probabilità di problemi termici.

Un altro aspetto affrontato dall’analisi PI-DC è il numero di vias usati per la distribuzione dell’alimentazione. Il problema è molto simile a quello del corretto dimensionamento delle forme in rame: se non ci sono abbastanza vias, si perde tensione e si spreca potenza a causa dell’IR drop, ma se si usano troppi vias, si spreca prezioso spazio di routing. In particolare, se si usano troppi vias per un determinato percorso di tensione, questi vias attraversano forme su altri layer e ne riducono la sezione di rame, causando quindi problemi per quelle altre tensioni. Allo stesso modo del corretto dimensionamento delle forme, l’analisi della tensione nei punti di carico consente il corretto dimensionamento e/o numero dei vias.

Infine, c’è un vantaggio significativo nel simulare il progetto finale esattamente come appare fisicamente, per assicurarsi che sia ottimizzato. La simulazione PI-DC fornisce una verifica finale che connettori e regolatori siano dimensionati correttamente, nel caso in cui durante il processo di progettazione siano stati rimossi o aggiunti carichi, per esempio.

In assenza di dati affidabili sulla caduta di tensione attraverso le varie forme di alimentazione, forme di massa e vias di un PCB, un progettista è costretto a essere conservativo usando forme di piano, dimensioni delle tracce e vias eccessivi, che consumano prezioso spazio di progetto e aumentano il numero di layer e il form factor del progetto. Altium PDN Analyzer fornisce informazioni accurate sull’idoneità della distribuzione di potenza DC di un progetto in modo semplice e diretto, consentendo ai progettisti di realizzare i progetti di distribuzione dell’alimentazione più efficienti possibile.

I risultati non sono adatti solo alla verifica finale del progetto, ma possono anche essere utilizzati nelle fasi di pianificazione di un progetto per progettare in anticipo la distribuzione dell’alimentazione nel modo più efficiente possibile. PI-DC è uno strumento preziosissimo per ottenere la rete di distribuzione dell’alimentazione più efficiente e robusta possibile; il PDN Analyzer rende semplice, intuitivo ed efficiente l’esecuzione di questo processo di simulazione e analisi.

Tra questi e altri vantaggi che il PDN Analyzer apporta ai tuoi progetti PCB, offre anche i seguenti benefici:

- Affidabilità del prodotto: aiuta a garantire le corrette prestazioni delle singole alimentazioni all’interno del progetto, in termini di livelli di tensione stazionari, stabilità della tensione e riscaldamento/danneggiamento delle tracce.

- Miglioramento del layout PCB: fornisce informazioni applicabili alla creazione dell’uso più efficace dello spazio sulla scheda e consente di identificare e correggere facilmente le aree problematiche ad alta densità di corrente.

- Conoscenza: non affidarti più a regole empiriche o a calcoli approssimativi quando consideri il layout dei percorsi di corrente continua.

Simulazione con PDN Analyzer

Nella sua forma più basilare, un layout di scheda soggetto ad analisi PI-DC potrebbe essere composto da una sorgente Voltage Regulator e dal suo carico, con aree di rame interconnesse di varie forme e larghezze di traccia.

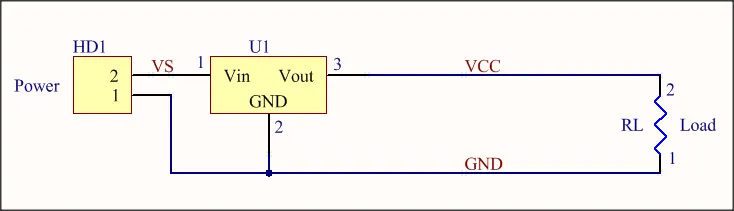

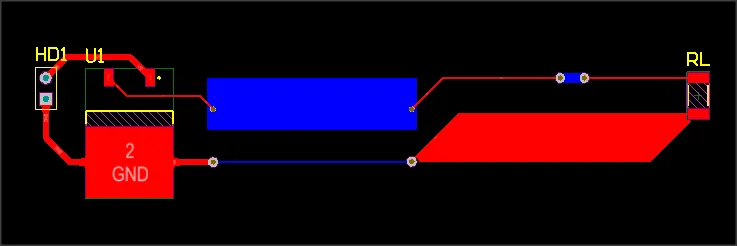

Un esempio di circuito base con una sorgente di alimentazione e un carico.

Il layout PCB del circuito base, con una gamma di forme in rame e tracce collegate tramite layer e vias.

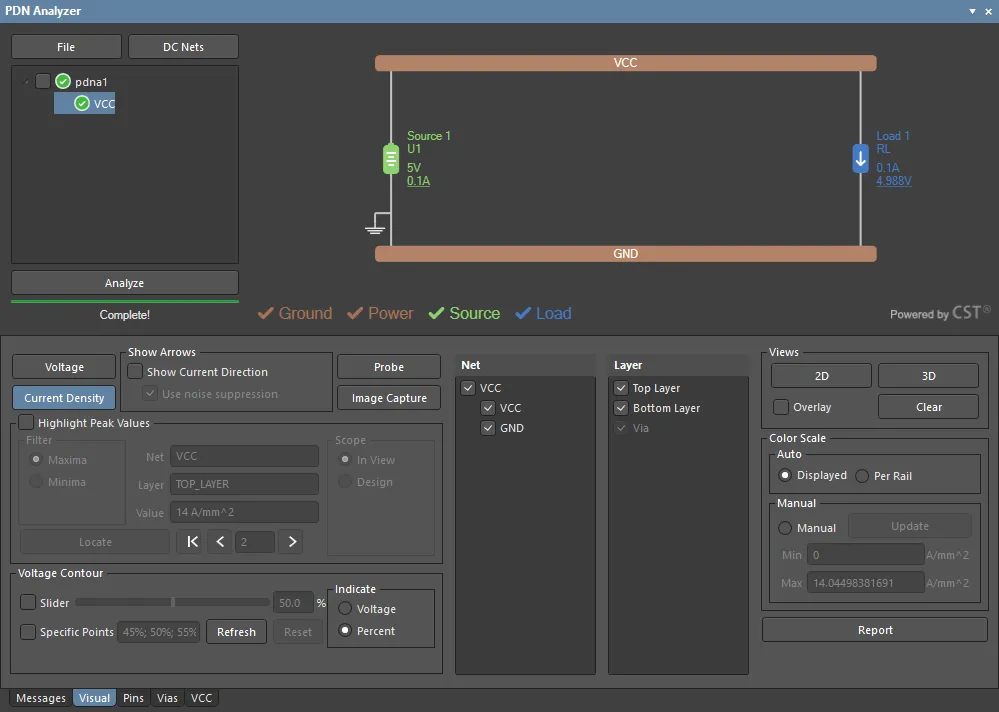

L’interfaccia del pannello PDN Analyzer (Tools » PDN Analyzer) emula visivamente una net di circuito da Power Source a Load che incorpora percorsi reali di Power e Ground, proprio come mostrato nel circuito sopra e anche nel diagramma a blocchi concettuale (Fig. 1). L’applicazione estrae automaticamente tutte le informazioni fisiche ed elettriche (netlist, dispositivi e forme dei layer, ecc.) dal progetto PCB attualmente attivo, che fornisce i dati per il motore di simulazione PI-DC.

L’interfaccia del pannello PDN Analyzer che mostra una configurazione di simulazione PI per il circuito base e il layout della scheda.

Qui, la sorgente di tensione è l’uscita di U1 (5V tra i pin 3 e 2), e il carico è una corrente specificata attraverso RL (0,1A). Una volta inseriti i parametri iniziali tramite l’interfaccia (tensioni e correnti di sorgente/carico, ecc.) ed eseguita la simulazione, i dati di analisi risultanti vengono modellati graficamente nell’editor PCB come immagine renderizzata 2D o 3D.

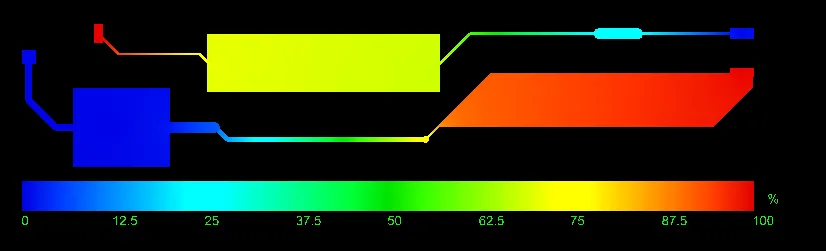

I risultati della simulazione Voltage Drop per il rame delle net PWR e GND della scheda (da U1 a RL e da RL a U1).

I risultati della simulazione Voltage Drop per il rame delle net PWR e GND della scheda (da U1 a RL e da RL a U1).

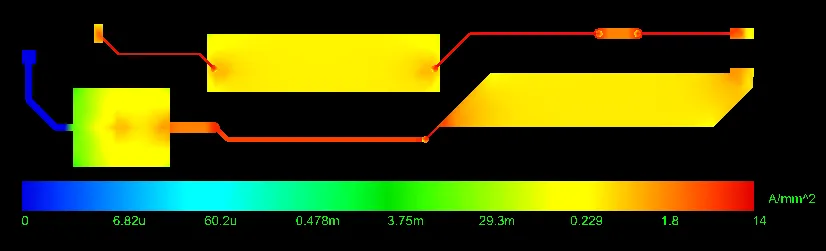

La simulazione PI di PDN Analyzer può essere impostata per mostrare i risultati di Tensione (IR Drop, immagine sopra) oppure di Densità di corrente (immagine sotto) per tutti i layer della scheda applicabili.

La mappa della densità di corrente per entrambe le net PWR e GND (da U1 a RL).

► Consulta la guida di esempio di PDN Analyzer per una descrizione completa dell'utilizzo di PDN Analyzer e dell'interpretazione dei suoi risultati.

Localizzato tramite A

Localizzato tramite A