PDN Analyzer

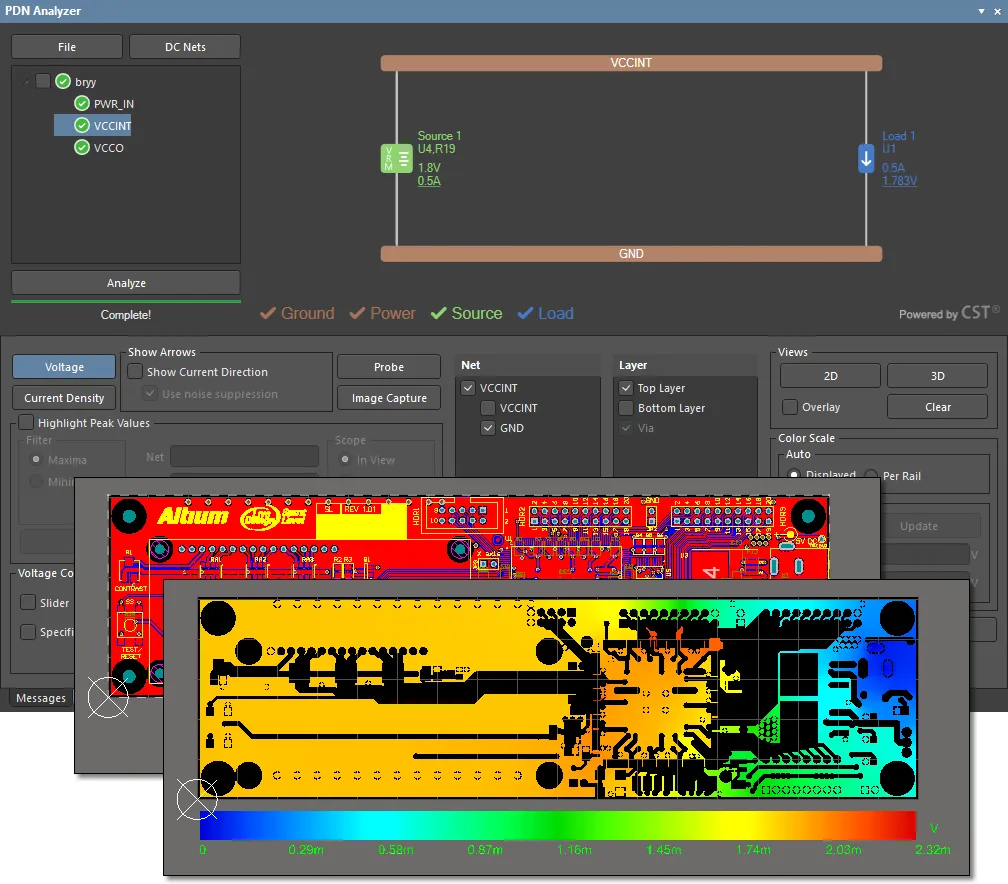

PDN Analyzer powered by CST®(Computer Simulation Technology)はAltium Designerに直接統合されており、現在のPCBプロジェクトに対してPI-DCシミュレーションと解析を行えます。PDN AnalyzerはAltium Designer内で動作するため、手動でのデータのインポート/エクスポート、データ変換、別アプリケーションの起動は不要です。回路図エディタまたはPCBエディタからPDN Analyzerを起動し、必要なテストパラメータを設定してシミュレーションを実行するだけです。結果は主に基板の銅箔レイアウトの2D/3Dモデリングとして提示されるため、結果を素早く評価でき、PCBレイアウト設計に対する探索的な「もし〜なら」テストも行えます。

Altium DesignerのSpirit LevelサンプルPCBを用いて示したPDN Analyzerインターフェースと、VCCINT電源に対するトップ層GNDネットのリターンについてPI-DC電圧降下シミュレーションを行った結果。

PDN Analyzer機能へのアクセス

Altium DesignerでPDN Analyzer機能にアクセスするには、 PDN Analyzer software extension をインストールする必要があります。この拡張機能は手動でインストール/削除できます。

拡張機能の管理について詳しくは、 Extending Your Installation ページ(Altium Designer Develop、Altium Designer Agile、Altium Designer)を参照してください。

また、この機能にアクセスするには、PDN Analyzerへの有効なサブスクリプションも必要です。

Power Integrityの基礎

本質的に、PI-DC(または「IR drop」)の問題は比較的単純です。基板の電源供給形状(配線、ポリゴン、プレーンなど)に内在する抵抗によって電力と電圧が消費され、その分が各負荷から奪われます。想像できるとおり、電源に接続される負荷の数が増えるほど、電源およびGNDの銅箔パスでの相互作用によりIRの問題は複雑になります。

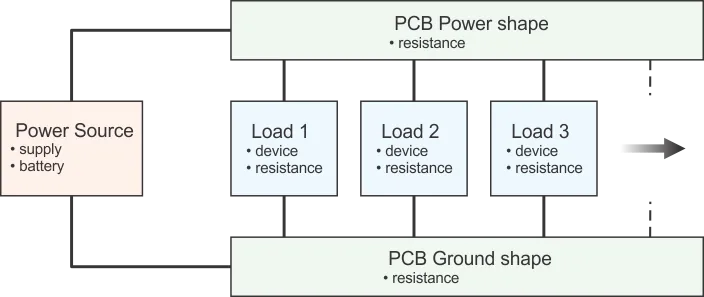

図1:電源およびGND形状と、印加される負荷の基本ブロック図。

図1(上)は、回路の電源と、各負荷(メモリ、マイコンなど)へ電力を供給する電源/GND形状(配線およびプレーン)の簡単なブロック図を示しています。 すべての負荷は同じ電源およびGND形状に接続され、それらの形状が動作電圧を供給することに依存している点に注意してください。 一般に、これらの電源/GND形状は抵抗が0Ωであると仮定しがちですが、必ずしもそうではなく、その仮定が問題を引き起こすことがあります。 比較的大きな電流が関与することが多いため、電源/GND形状にわずかな抵抗があるだけでも、顕著な電力消費(損失)や電圧降下を招く可能性があります。

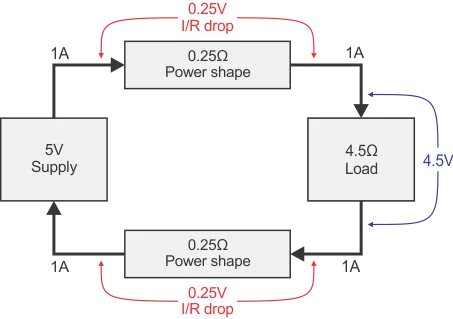

図2:「IR Drop」の影響

図2は、電源およびGND形状の抵抗を適切に考慮しない場合に生じ得る問題の例を示しています。 各形状の抵抗は0.25Ωと比較的小さいにもかかわらず、負荷点の電圧は5Vから4.5Vまで低下しています。 設計者はこの低下を把握し、許容できることを確認するか、低下を抑えるよう設計を変更して、最終設計が現場で故障しないようにする必要があります。

しかし、この問題は一見すると解決が容易に思えます。次の関係式に従って、電源およびGND形状を十分に短く、または十分に大きくして、抵抗が無視できるようにすればよいのです:R = ρ * L/A、ここで:

-

Rは形状(配線またはプレーン)の総抵抗 -

ρは形状に使用される材料の抵抗率(通常は銅、ρ ≈ 1.7µΩ-cm) -

Lは形状の長さ -

Aは形状の断面積(幅x厚み)

要するに、電源およびGND形状を短く、厚く、広くすれば、抵抗を最小化できます。

ただし、その場合の難しさは、形状を過度に大きくすると貴重な配線スペースを消費し、他の電圧形状に割けるスペースを制限してしまう点です。 適切なサイズの電源/GND形状を持つ設計は、過度に大きなプレーンや配線を恣意的に用いる設計よりもコンパクトで、層数も少なくて済みます。 PI-DC解析の目的は、基板設計の電源/GND形状が十分である一方で、過剰に大きくはないことを設計者に示すことです。

IR dropに関する別の考慮点として、消費電力がI2Rであることが挙げられます。つまり、抵抗に流れる電流がわずかに増えるだけで、消費電力は大きく増加します。 これは、電源および/またはGND形状が流れる電流に対して十分な大きさでないために、設計が大きく発熱するという熱問題として現れることがあります。 電源/GND形状でのIR dropを非常に小さく抑えることで、それらの形状での電力消費を最小化できます。

極端な場合、形状が十分に抵抗性(非常に細く長い)で、かつ十分な電流が流れると、その形状は実質的に「ヒューズ」となり、銅箔が溶断して設計が故障し、場合によっては危険な状況を引き起こす可能性があります。 PCBの電流許容能力に関するIPC-2152規格はこの問題を扱っていますが、(例えば近傍に熱を逃がすための熱伝導性の高い銅がない、など)悲観的な前提に基づいており、設計者はしばしば最も保守的な仮定(温度上昇を最小限に抑える、など)でこの仕様を適用します。 PI-DCは熱設計の指針としてIPC-2152規格を置き換えるものではありませんが、電力供給システムの電圧降下と電流密度を調べることで、設計を安全に最適化するための有用な洞察を提供できます。 電源からすべての負荷までの間で電流密度と電圧降下が最小となるよう最適化された設計は、発熱も少なく、熱問題が起こる可能性も低くなります。

PI-DC解析が扱う別の側面として、電力供給に使用されるビアの数があります。 問題は銅箔形状の適切なサイズ決めと非常によく似ています。ビアが不足するとIR dropによって電圧が失われ電力が無駄になりますが、ビアが多すぎると貴重な配線領域が無駄になります。 特に、特定の電圧パスにビアを使いすぎると、それらのビアが他層の形状を貫通してその銅断面を減らし、他の電圧に問題を引き起こす可能性があります。 形状の寸法を正しく決めるのと同様に、負荷点での電圧を解析することで、適切なビア径および/または本数を決定できます。

最後に、最終設計を物理的な実装どおりに正確にシミュレーションし、最適化されていることを確認できる点には大きな利点があります。 PI-DCシミュレーションは、例えば設計プロセス中に負荷が削除/追加された場合でも、コネクタやレギュレータの定格が適切であることを確認する最終チェックを提供します。

PCBの各種電源形状、GND形状、ビアにおける電圧降下について信頼できるデータがない場合、設計者は過度に大きなプレーン形状、配線幅、ビアを用いるという保守的な設計を余儀なくされ、貴重な設計領域を消費し、層数やフォームファクタの増大につながります。 Altium PDN Analyzerは、設計のDC電力分配の適合性について正確な情報を、使いやすく分かりやすい形で提供し、設計者が可能な限り効率的な電力分配設計を行えるようにします。

結果は最終設計の検証に適しているだけでなく、設計の計画段階で、事前に電力供給をできるだけ効率的にアーキテクトするためにも利用できます。 PI-DCは、可能な限り効率的で堅牢な電力供給ネットワークを実現するうえで非常に価値の高いツールであり、PDN Analyzerはそのシミュレーションと解析プロセスを、分かりやすく直感的かつ効率的に実行できるようにします。

PDN AnalyzerがPCB設計にもたらすこれらの利点に加え、次のメリットも提供します:

- 製品信頼性:定常電圧レベル、電圧安定性、配線の発熱/損傷の観点から、設計内の各電源が正しく動作することを支援します。

- PCBレイアウトの改善:基板スペースを最も効果的に活用するために適用できる情報を提供し、問題となる高電流密度領域を容易に特定して修正できます。

- 知見:DC電流パスのレイアウト検討において、経験則や概算計算に頼る必要がなくなります。

PDN Analyzerシミュレーション

最も基本的な形では、PI-DC解析の対象となる基板レイアウトは、電圧レギュレータのソースとその負荷、そしてそれらを接続するさまざまな形状や配線幅の銅箔領域で構成されます。

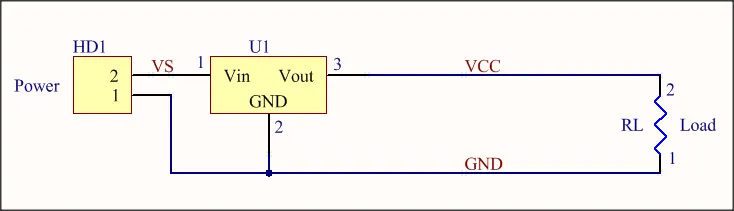

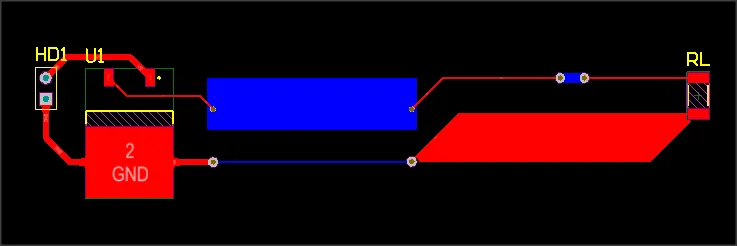

電源と負荷の基本回路例。

層とビアで接続された、さまざまな銅箔形状と配線を備える基本回路のPCBレイアウト。

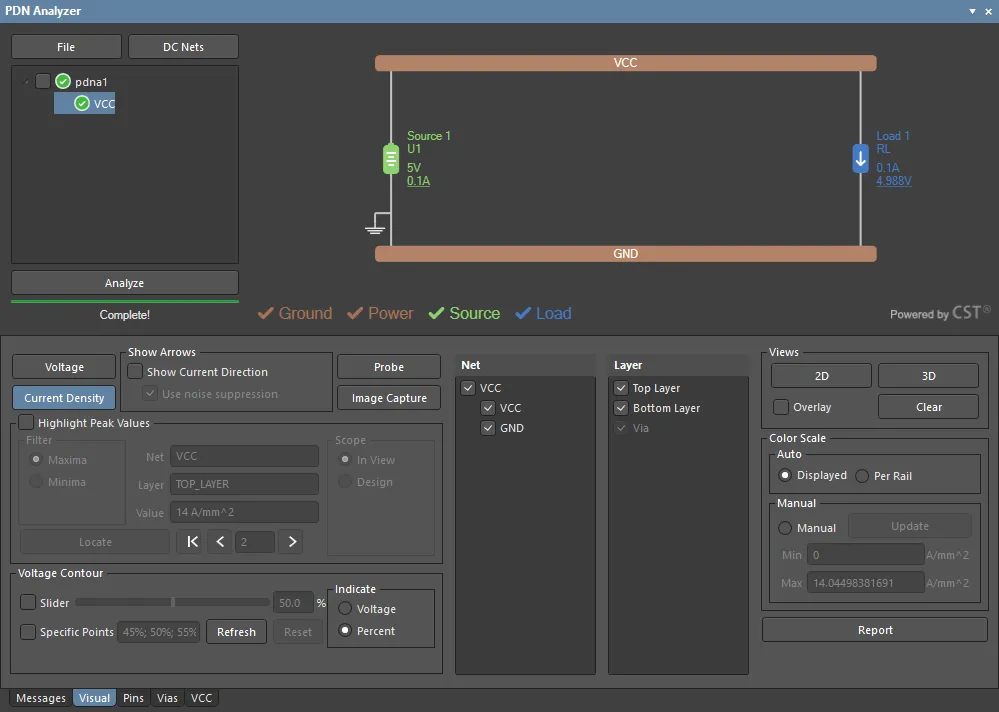

PDN Analyzerパネルインターフェース(Tools » PDN Analyzer)は、実体のある電源およびGNDパスを含む「電源→負荷」の回路ネットを視覚的にエミュレートします。これは上記の回路や概念ブロック図(図1)に示したものと同様です。アプリケーションは、現在アクティブなPCB設計から、すべての物理情報および電気情報(ネットリスト、デバイス、層の形状など)を自動的に抽出し、PI-DCシミュレーションエンジンのデータとして提供します。

基本回路と基板レイアウトに対するPIシミュレーション設定を示すPDN Analyzer パネルインターフェース。

ここでは、電圧源はU1の出力(ピン3と2の間で5V)で、負荷はRLに流れる指定電流(0.1A)です。インターフェースから初期パラメータ(ソース/負荷の電圧や電流など)を入力してシミュレーションを実行すると、得られた解析データはPCBエディタ上で2Dまたは3Dのレンダリング画像としてグラフィカルにモデル化されます。

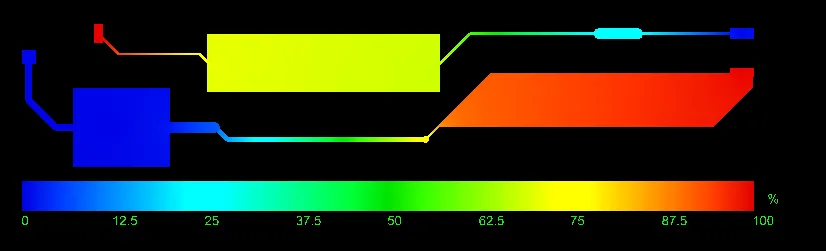

基板のPWRおよびGNDネットの銅箔(U1→RL、およびRL→U1)に対する電圧降下シミュレーション結果。

基板のPWRおよびGNDネットの銅箔(U1→RL、およびRL→U1)に対する電圧降下シミュレーション結果。

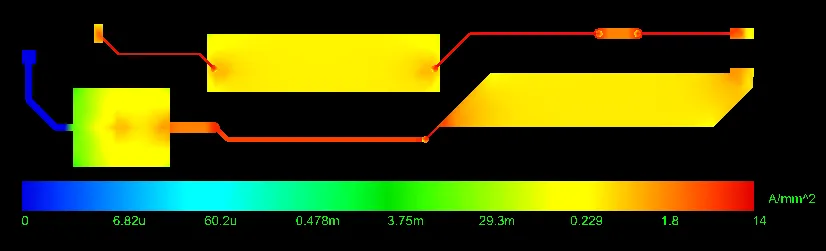

PDN Analyzer の PI シミュレーションは、適用可能なすべての基板レイヤーについて、電圧(IR ドロップ、上の画像)または電流密度(下の画像)の結果を表示するように設定できます。

PWR および GND ネット(U1 から RL)両方の電流密度マップ。

► PDN Analyzer の使用方法と結果の解釈を完全に説明した PDN Analyzer example guide を参照してください。

AI で翻訳

AI で翻訳