PDN Analyzer

PDN Analyzer powered by CST® (Computer Simulation Technology) интегрируется напрямую с Altium Designer, позволяя выполнять PI-DC моделирование и анализ текущего проекта печатной платы. Поскольку PDN Analyzer работает внутри Altium Designer, не требуется ручной импорт/экспорт данных, преобразование форматов или запуск отдельных приложений — просто запустите PDN Analyzer из редактора схемы или PCB, задайте нужные параметры теста и выполните моделирование. Результаты в основном предоставляются в виде 2D/3D-моделирования медной топологии платы, что позволяет быстро оценить итоги и выполнить исследовательские проверки «а что если» для варианта разводки PCB.

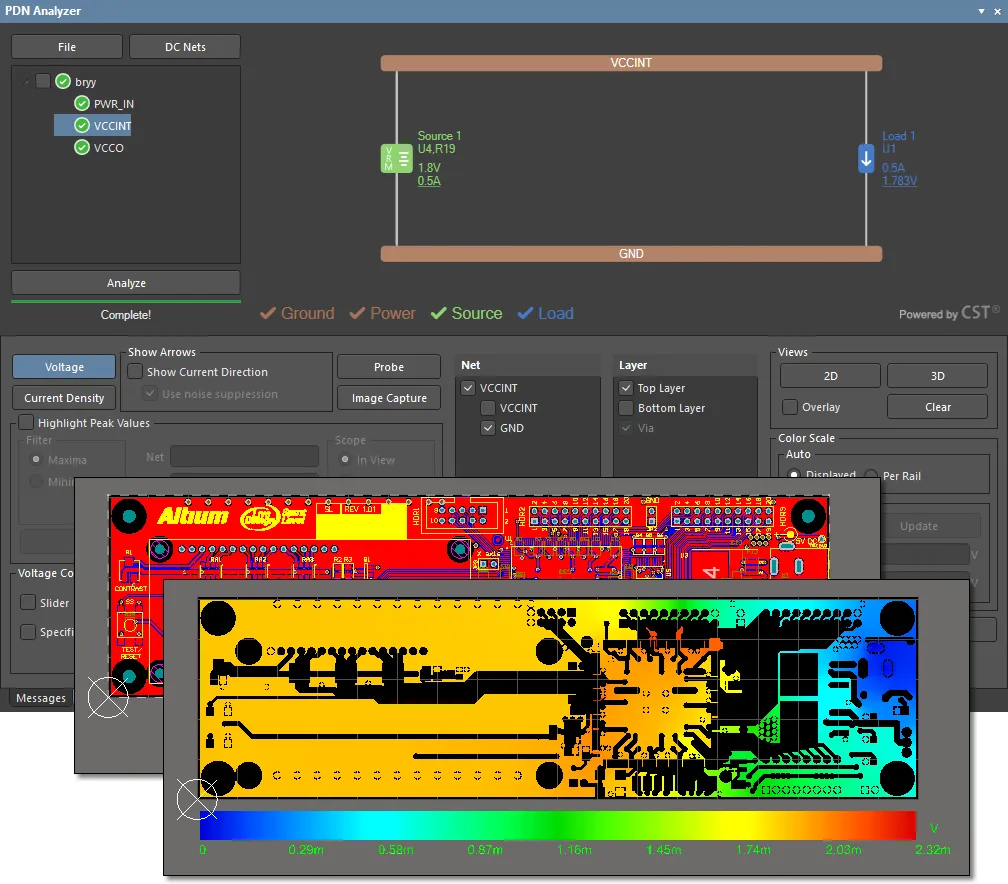

Показан интерфейс PDN Analyzer на примере PCB Altium Designer Spirit Level, а также результаты PI-DC моделирования падения напряжения для возвратного пути сети GND на верхнем слое (Top) для питания VCCINT.

Доступ к функциональности PDN Analyzer

Чтобы получить доступ к функциональности PDN Analyzer в Altium Designer, необходимо установить PDN Analyzer программное расширение . Это расширение можно установить или удалить вручную.

Дополнительные сведения об управлении расширениями см. на Extending Your Installation странице (Altium Designer Develop, Altium Designer Agile, Altium Designer).

Чтобы получить доступ к функциональности, также требуется действующая подписка на PDN Analyzer.

Основы Power Integrity

По сути, задача PI-DC (или «IR drop») довольно проста: сопротивление, присущее силовым проводникам на плате (дорожки, полигоны, плоскости и т. п.), потребляет мощность и «съедает» напряжение, отнимая их у различных нагрузок. Как и ожидается, проблемы IR drop усложняются по мере увеличения числа нагрузок на одной линии питания из‑за взаимодействия токов в медных путях питания и земли.

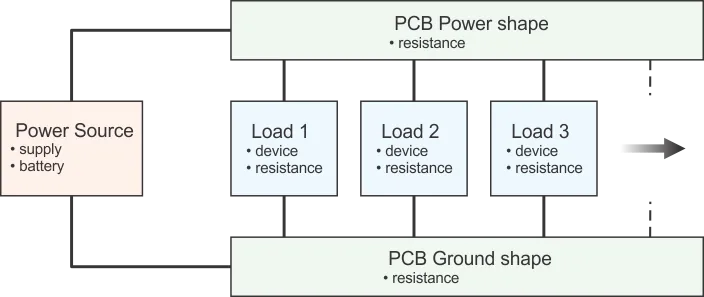

Рисунок 1: базовая блок-схема силовых и земляных проводников и подключённых нагрузок.

На рисунке 1 (выше) показана простая блок-схема источника питания схемы и её силовых и земляных проводников (дорожек и плоскостей), которые подают питание на различные нагрузки (память, микроконтроллеры и т. д.). Обратите внимание: все нагрузки подключены к одним и тем же силовым и земляным проводникам и зависят от них в части получения рабочих напряжений. Обычно мы склонны считать, что эти силовые и земляные проводники имеют сопротивление 0 Ом, что не всегда верно, и такое допущение может приводить к проблемам. Поскольку часто протекают сравнительно большие токи, даже небольшие сопротивления в силовых и земляных проводниках могут вызывать заметное потребление (потери) мощности и падение напряжения.

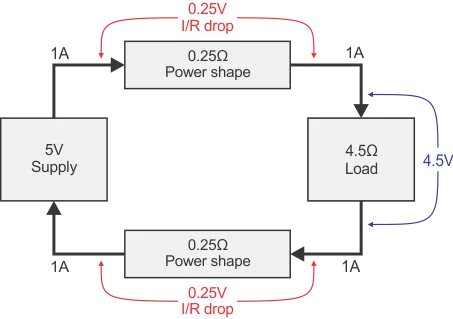

Рисунок 2: эффекты «IR Drop»

На рисунке 2 показан пример проблем, которые могут возникнуть, если сопротивление силовых и земляных проводников не учтено должным образом. Хотя каждый проводник имеет относительно небольшое сопротивление всего 0,25 Ом, из‑за этого напряжение на нагрузке снизилось с 5 В до 4,5 В. Разработчик должен учитывать это падение и убедиться, что оно допустимо, либо изменить конструкцию, чтобы уменьшить его — чтобы итоговое изделие не отказало в эксплуатации.

Однако задача кажется простой — достаточно сделать силовые и земляные проводники достаточно короткими или достаточно большими, чтобы их сопротивление было пренебрежимо малым, используя следующее соотношение: R = ρ * L/A, где:

-

R— полное сопротивление проводника (дорожки или плоскости) -

ρ— удельное сопротивление материала проводника (обычно медь,ρ ≈ 1.7µΩ-cm) -

L— длина проводника -

A— площадь поперечного сечения проводника (ширинаxтолщина)

Проще говоря, если сделать силовые и земляные проводники короткими, толстыми и широкими, их сопротивление будет минимальным.

Сложность, однако, в том, что чрезмерно крупные проводники занимают ценное пространство для трассировки и могут ограничивать место для других цепей напряжений. Конструкция с правильно подобранными силовыми и земляными проводниками будет более компактной и потребует меньше слоёв, чем та, где произвольно используются чрезмерно большие плоскости или дорожки. Цель PI-DC анализа — сообщить разработчику, что силовые и земляные проводники в проекте платы достаточны, но не избыточны.

Ещё один аспект IR drop — то, что потребляемая мощность равна I2R — поэтому небольшое увеличение тока через сопротивление приводит к значительному росту рассеиваемой мощности. Это может проявляться как тепловые проблемы, когда конструкция заметно нагревается из‑за того, что силовые и/или земляные проводники недостаточно велики для протекающего по ним тока. Обеспечивая очень малое IR drop на силовых и земляных проводниках, можно минимизировать потери мощности в этих проводниках.

В предельном случае, если проводник достаточно резистивен (очень узкий и длинный) и через него протекает достаточный ток, он фактически становится «предохранителем», расплавляя медь и приводя к отказу конструкции — и потенциально создавая опасную ситуацию. Стандарт IPC-2152 по токовой нагрузочной способности печатных плат рассматривает этот вопрос, но с пессимистичными допущениями (например, отсутствие рядом теплопроводящей меди, которая могла бы отводить тепло), и разработчики часто применяют этот стандарт с максимально консервативными предположениями, например, допуская лишь минимальный рост температуры. Хотя PI-DC не может заменить IPC-2152 как руководство по тепловым аспектам, он может дать ценную информацию о том, как безопасно оптимизировать конструкцию, анализируя падения напряжения и плотности тока в системе питания. Конструкция, оптимизированная на минимальную плотность тока и падение напряжения между источниками и всеми нагрузками, будет также выделять меньше тепла и иметь меньший риск тепловых проблем.

Ещё один аспект, который рассматривает PI-DC анализ, — количество переходных отверстий (via), используемых для подачи питания. Проблема очень похожа на правильный подбор размеров медных проводников: если via недостаточно, напряжение теряется и мощность расходуется из‑за IR drop, но если via слишком много, расходуется ценное пространство для трассировки. В частности, если для определённого пути напряжения используется слишком много via, эти via проходят через проводники на других слоях и уменьшают их поперечное сечение меди, тем самым создавая проблемы для других напряжений. Аналогично правильному выбору размеров проводников, анализ напряжения в точках нагрузки позволяет корректно подобрать размер via и/или их количество.

Наконец, существенное преимущество даёт моделирование финальной конструкции в точности в том виде, как она выглядит физически, чтобы убедиться в её оптимальности. PI-DC моделирование обеспечивает финальную проверку того, что разъёмы и стабилизаторы выбраны правильно, например, если в процессе проектирования нагрузки были добавлены или удалены.

При отсутствии надёжных данных о падении напряжения на различных силовых проводниках, земляных проводниках и via на PCB разработчик вынужден действовать консервативно, используя избыточные плоскости, ширины дорожек и количество via, что расходует ценное пространство, увеличивает число слоёв и габариты изделия. Altium PDN Analyzer предоставляет точную информацию о пригодности DC-распределения питания в проекте в удобной и понятной форме, позволяя разработчикам создавать максимально эффективные системы распределения питания.

Результаты подходят не только для финальной верификации проекта, но и могут использоваться на этапах планирования, чтобы заранее максимально эффективно спроектировать архитектуру подачи питания. PI-DC — незаменимый инструмент для создания максимально эффективной и надёжной сети питания, а PDN Analyzer делает процесс моделирования и анализа простым, интуитивным и эффективным.

Помимо этих и других преимуществ, которые PDN Analyzer привносит в ваши проекты PCB, он также обеспечивает следующие выгоды:

- Надёжность изделия: помогает обеспечить корректную работу отдельных источников питания в проекте с точки зрения установившихся уровней напряжения, стабильности напряжения и нагрева/повреждения дорожек.

- Улучшенная разводка PCB: предоставляет информацию, которую можно использовать для наиболее эффективного использования пространства платы, и позволяет легко выявлять и исправлять проблемные области с высокой плотностью тока.

- Знания: больше не нужно полагаться на эмпирические правила или приблизительные расчёты при оценке разводки путей DC-токов.

Моделирование в PDN Analyzer

В самом базовом виде разводка платы, которая будет подвергаться PI-DC анализу, может состоять из источника — стабилизатора напряжения — и его нагрузки, соединённых медными областями различных форм и дорожками разной ширины.

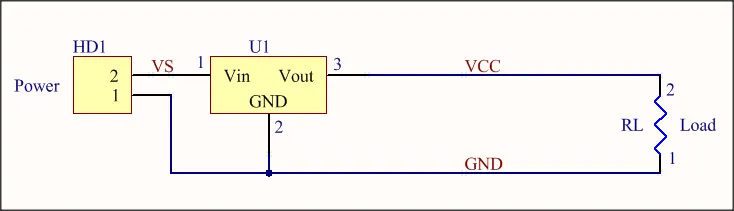

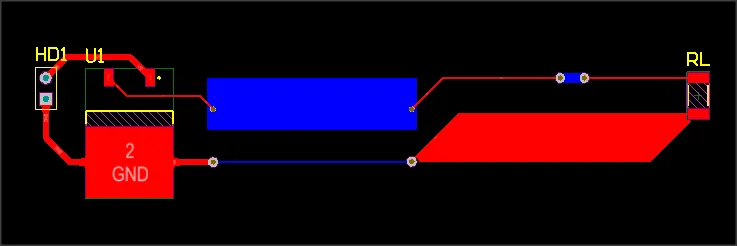

Базовый пример схемы источника питания и нагрузки.

Разводка PCB базовой схемы с набором медных областей и дорожек, соединённых слоями и via.

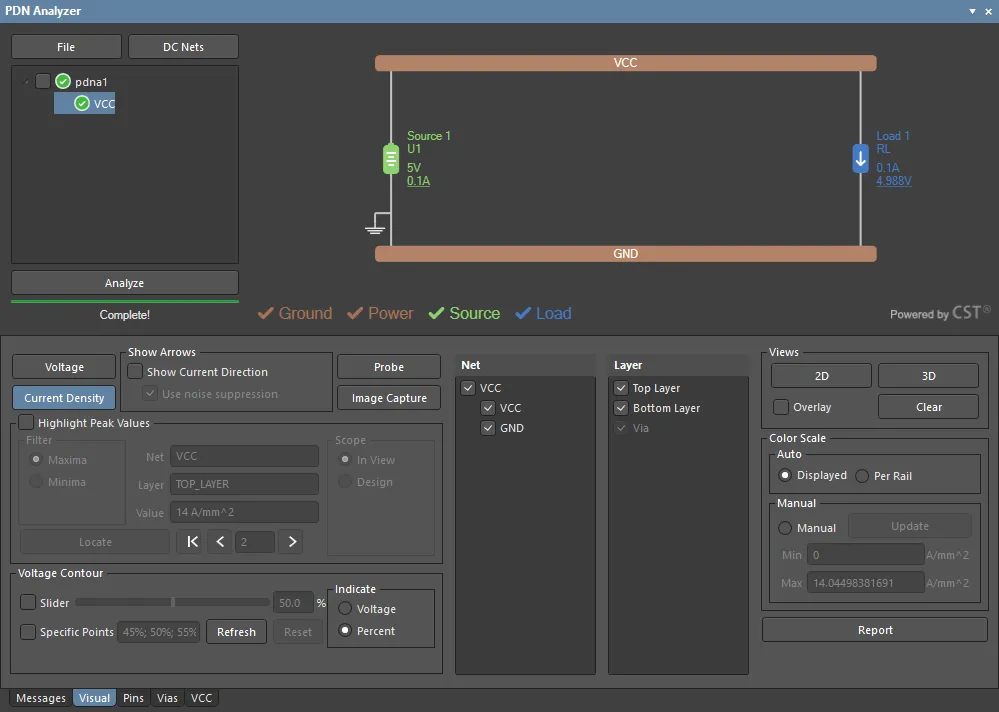

Интерфейс панели PDN Analyzer (Tools » PDN Analyzer) визуально имитирует цепь сети от источника питания к нагрузке, включающую реальные пути питания и земли — как показано в схеме выше и в концептуальной блок-схеме (рис. 1). Приложение автоматически извлекает всю физическую и электрическую информацию (нетлист, устройства и геометрию слоёв и т. п.) из текущего активного проекта PCB, предоставляя данные для движка PI-DC моделирования.

Интерфейс панели PDN Analyzer , показывающий настройку PI моделирования для базовой схемы и разводки платы.

Здесь источник напряжения — это выход U1 (5 В между выводами 3 и 2), а нагрузка — заданный ток через RL (0,1 А). После ввода исходных параметров через интерфейс (напряжения и токи источника/нагрузки и т. п.) и запуска моделирования полученные данные анализа графически отображаются в редакторе PCB в виде визуализированного 2D или 3D изображения.

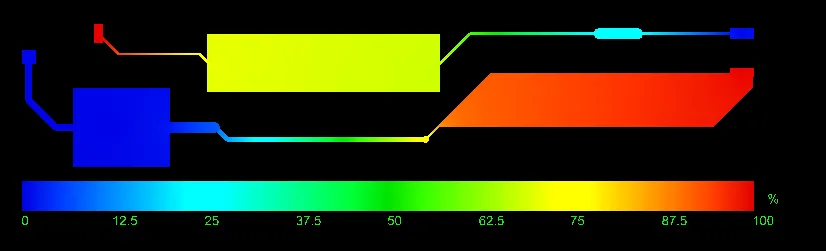

Результаты моделирования падения напряжения для меди сетей PWR и GND платы (от U1 к RL и от RL к U1).

Результаты моделирования падения напряжения для меди сетей PWR и GND платы (от U1 к RL и от RL к U1).

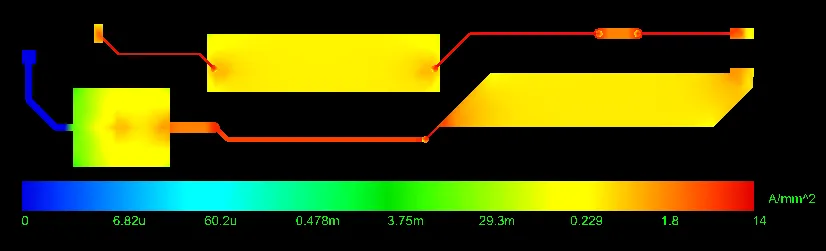

PI-симуляцию PDN Analyzer можно настроить так, чтобы она отображала результаты по напряжению (падение IR, на изображении выше) или по плотности тока (на изображении ниже) для всех применимых слоёв платы.

Карта плотности тока для сетей PWR и GND (от U1 до RL).

► См. руководство по примеру PDN Analyzer — там приведено полное описание использования PDN Analyzer и интерпретации его результатов.

Локализовано с помощью ИИ

Локализовано с помощью ИИ