PDN Analyzer (by CST)

PDN Analyzer powered by CST®(Computer Simulation Technology)可直接与 Altium Designer 集成,从而对当前 PCB 项目进行 PI-DC 仿真与分析。由于 PDN Analyzer 在 Altium Designer 内运行,因此无需手动导入/导出数据、无需数据转换,也无需运行独立应用程序——只需从原理图或 PCB 编辑器启动 PDN Analyzer,设置所需的测试参数并运行仿真即可。结果主要通过对电路板铜箔布局的 2D/3D 建模来呈现,便于快速评估结果,并有机会对 PCB 布局设计进行探索性的“假设(what if)”测试。

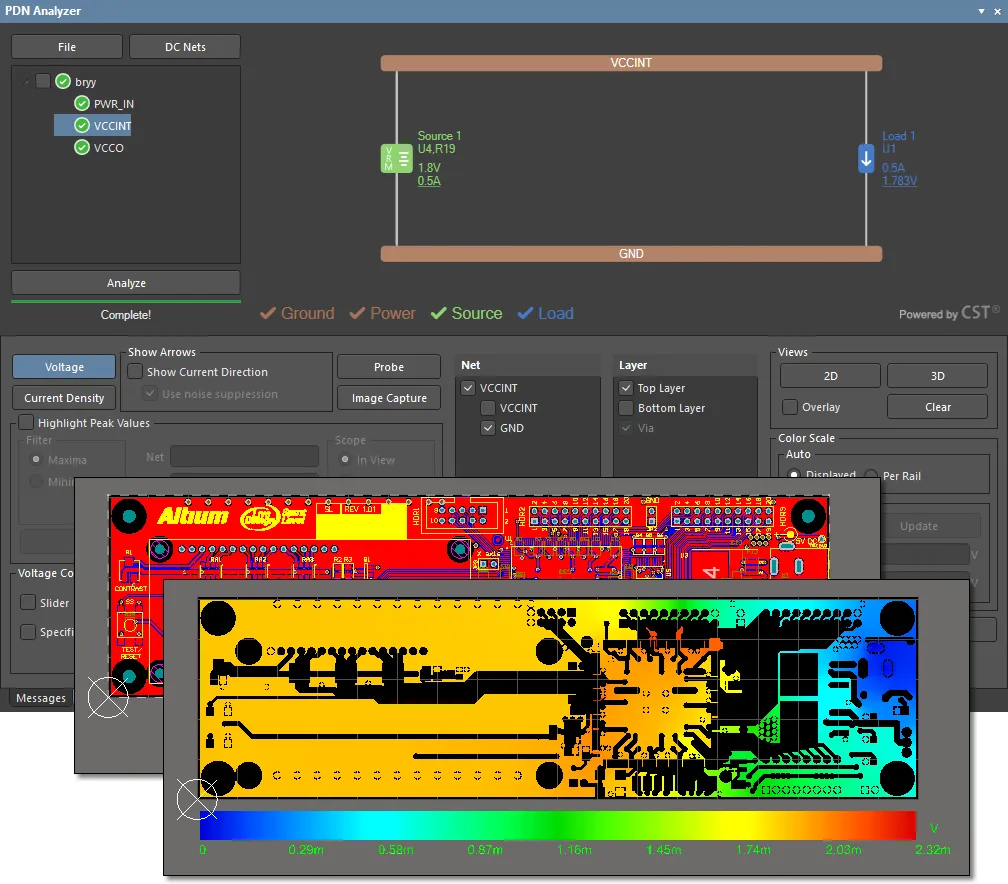

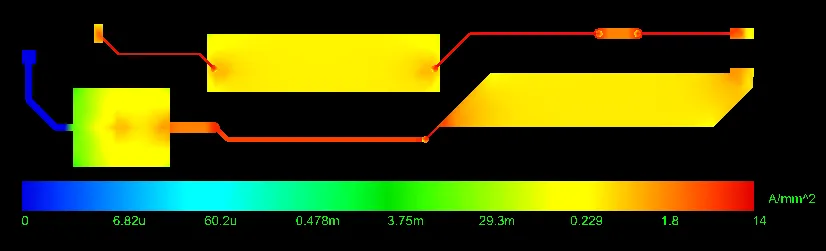

所示为 Altium Designer Spirit Level 示例 PCB 的 PDN Analyzer 界面,以及其针对 VCCINT 供电的顶层 GND 网络回流路径所做的 PI-DC 压降仿真结果。

访问 PDN Analyzer 功能

要在 Altium Designer 中访问 PDN Analyzer 功能,必须安装 PDN Analyzer 软件 扩展 。该扩展可手动安装或移除。

有关扩展管理的更多信息,请参阅 Extending Your Installation 页面(Altium Designer Develop、Altium Designer Agile、Altium Designer)。

要访问该功能,你还需要拥有有效的 PDN Analyzer 订阅。

电源完整性基础

本质上,PI-DC(或“IR drop/压降”)问题相当直观:板上电源供电图形(走线、覆铜、多边形、平面等)所体现的电阻会消耗功率与电压,从而使各个负载可用的电压/功率减少。正如你所预期的那样,随着同一电源上负载数量增加,并通过电源与地的铜箔路径相互影响,IR 问题的复杂度也会随之上升。

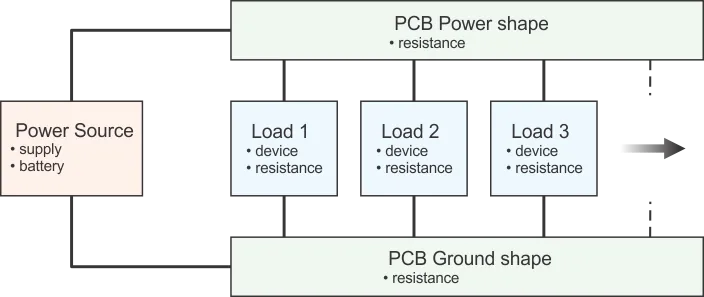

图 1(上)展示了一个简单的框图:电路的电源以及向各个负载(存储器、微控制器等)供电的电源与地的图形(走线与平面)。 请注意,所有负载都连接到同一组电源与地的图形,并依赖这些图形来提供其工作电压。 通常我们倾向于假设这些电源与地的图形电阻为 0Ω,但这并不一定成立,而这种假设可能会引发问题。 由于往往涉及较大的电流,即使电源与地图形中很小的电阻,也会造成显著的功率消耗(损耗)与电压下降。

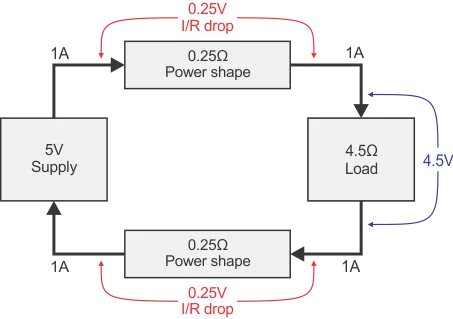

图 2 展示了当未正确考虑电源与地图形电阻时可能出现的问题示例。 尽管每个图形的电阻相对较小,仅为 0.25Ω,但它们已导致负载端电压从 5V 降至 4.5V。 设计人员必须意识到这种压降并确保系统能够容忍,或通过修改设计来减小压降,以确保最终设计不会在现场失效。

然而,这个问题看起来似乎很容易解决——只需将电源与地的图形做得足够短或足够大,使其电阻可以忽略不计,使用如下关系式:R = ρ * L/A,其中:

-

R为图形(走线或平面)的总电阻 -

ρ为图形所用材料的电阻率(通常为铜,ρ ≈ 1.7µΩ-cm) -

L为图形长度 -

A为图形的横截面积(宽度x厚度)

简而言之,如果将电源与地的图形做得更短、更厚、更宽,就能将其电阻降到最低。

但困难在于,过大的图形会占用宝贵的布线空间,并可能限制其他电压图形的可用空间。 电源与地图形尺寸恰当的设计,会比随意使用过大平面或走线的设计更紧凑、层数更少。 PI-DC 分析的目的,是告知设计人员板级设计中的电源与地图形是否足够,但又不过度冗余。

IR 压降的另一个考量是功耗满足 I2R——因此,电阻上的电流略微增加,就会导致功耗大幅上升。 这可能表现为热问题:由于电源和/或地的图形不足以承载通过的电流,设计会显著升温。 通过确保电源与地图形上的 IR 压降极小,可将这些图形中的功耗降到最低。

在极端情况下,如果某个图形电阻足够大(非常窄且很长),并且有足够电流流过,那么该图形本质上会变成“保险丝”,从而熔化铜箔并导致设计失效——甚至可能带来危险。 IPC-2152 标准针对 PCB 载流能力讨论了这一问题,但其假设较为悲观(例如假设附近没有导热铜来帮助散热),而设计人员在应用该规范时往往采用最保守的假设,例如只允许最小的温升。 虽然 PI-DC 不能替代 IPC-2152 作为热方面的指导标准,但它可以通过研究供电系统的压降与电流密度,为如何安全优化设计提供有价值的洞察。 在源端与所有负载之间实现最低电流密度与最低压降的优化设计,也会产生更少热量,并更不易出现热问题。

PI-DC 分析还涉及供电所用过孔数量。 其问题与正确确定铜箔图形尺寸非常相似:过孔不足会因 IR 压降导致电压损失与功率浪费;但过孔过多又会浪费宝贵的布线资源。 尤其是,当某一电压路径使用过多过孔时,这些过孔会穿过其他层的图形并减少其铜箔横截面积,从而给其他电压带来问题。 与正确设定图形尺寸同理,通过分析负载点电压即可确定合适的过孔尺寸和/或数量。

最后,按最终物理外观对成品设计进行精确仿真以确保其优化,是一个显著优势。 例如,如果在设计过程中增减了负载,PI-DC 仿真可作为最终检查,确保连接器与稳压器的规格/尺寸仍然合适。

在缺乏关于 PCB 各类电源图形、地图形与过孔压降的可靠数据时,设计人员往往被迫采取保守策略:使用过大的平面、走线尺寸与过孔数量,这会占用宝贵的设计空间、增加层数并增大外形尺寸。 Altium PDN Analyzer 以易用且直观的方式提供关于设计直流配电适用性的准确信息,使设计人员能够实现尽可能高效的配电设计。

这些结果不仅适用于最终设计验证,也可用于设计规划阶段,以便提前尽可能高效地构建供电架构。 PI-DC 是实现最高效、最稳健供电网络的关键工具;PDN Analyzer 让仿真与分析流程变得直接、直观且高效。

除上述及其他优势外,PDN Analyzer 还为你的 PCB 设计带来以下收益:

- 产品可靠性:有助于确保设计中各路电源在静态电压水平、电压稳定性以及走线发热/损伤方面的正确表现。

- 改进 PCB 布局:提供可用于更有效利用板上空间的信息,并可轻松识别与修正高电流密度的问题区域。

- 知识:在考虑直流电流路径布局时,不再依赖经验法则或近似计算。

PDN Analyzer 仿真

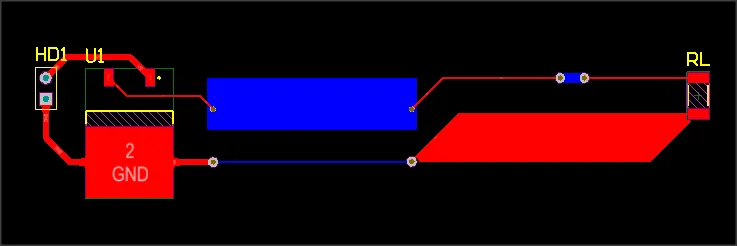

在最基本的形式下,进行 PI-DC 分析的板级布局可能由一个稳压器电源及其负载组成,并通过不同形状的铜箔区域与不同线宽的走线相互连接。

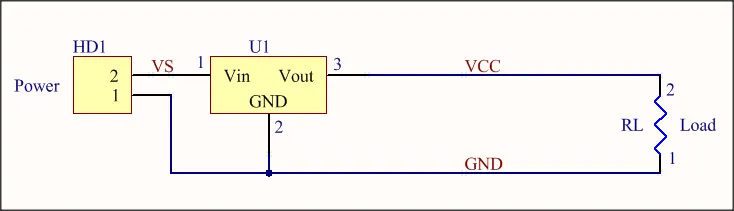

基础电路的 PCB 布局,包含一系列通过层与过孔连接的铜箔图形与走线。

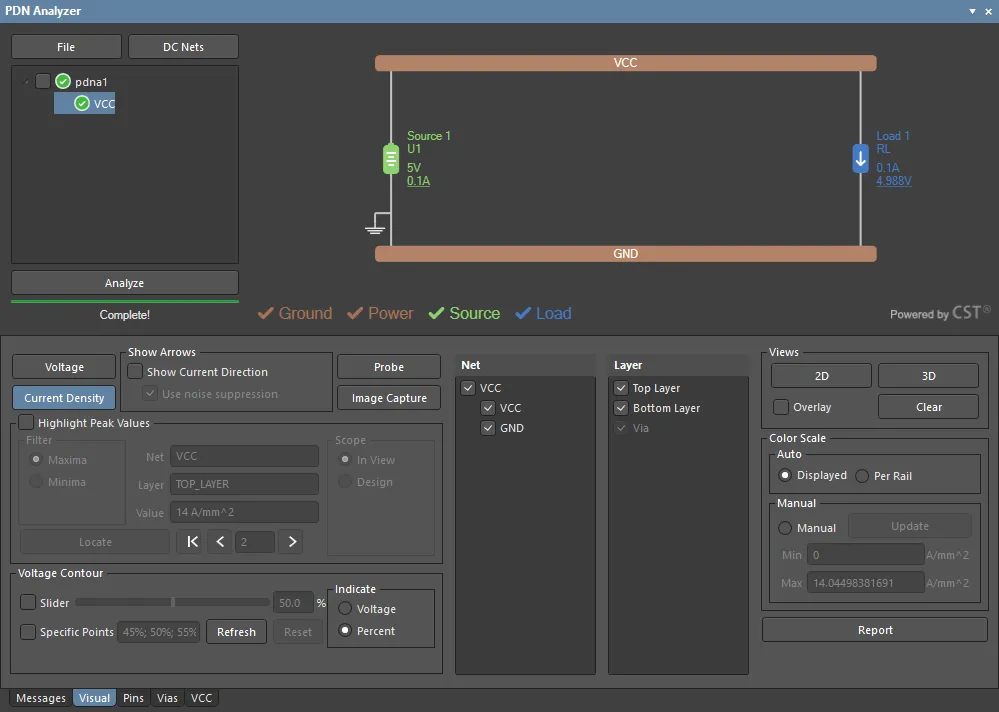

PDN Analyzer面板界面(Tools » PDN Analyzer)在视觉上模拟了一个从电源到负载的电路网络,其中包含真实的电源与地路径——如上方电路以及概念框图(图 1)所示。应用程序会从当前活动的 PCB 设计中自动提取所有物理与电气信息(网表、器件与层图形等),为 PI-DC 仿真引擎提供数据。

PDN Analyzer 面板界面显示了针对该基础电路与板级布局的 PI 仿真设置。

此处,电压源为 U1 的输出(引脚 3 与 2 之间为 5V),负载为流经 RL 的指定电流(0.1A)。通过界面输入初始参数(源/负载电压与电流等)并运行仿真后,分析数据会在 PCB 编辑器中以渲染的 2D 或 3D 图像形式进行图形化建模展示。

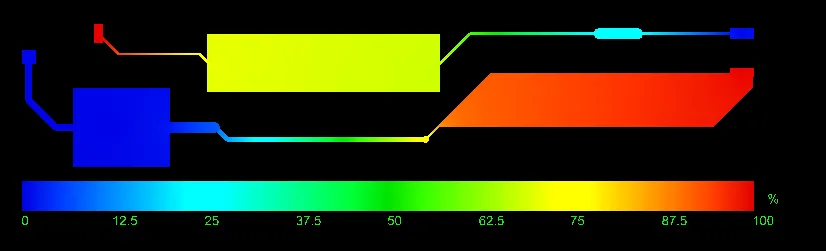

该板 PWR 与 GND 网络铜箔的压降仿真结果(U1 到 RL,以及 RL 到 U1)。

该板 PWR 与 GND 网络铜箔的压降仿真结果(U1 到 RL,以及 RL 到 U1)。

PDN Analyzer 的 PI 仿真可设置为显示所有适用电路板层的电压(IR 压降,如上图)或电流密度(如下图)结果。

PWR 和 GND 网络(U1 到 RL)的电流密度分布图。

► 请参阅 PDN Analyzer 示例指南,以获取关于如何使用 PDN Analyzer 以及如何解读其结果的完整说明。

AI 翻译

AI 翻译