为了成功对设计进行信号完整性(Signal Integrity)分析并获得准确结果,在运行分析之前必须完成以下工作。

-

尽管可以对每条网络进行筛选以提供网络与阻抗数据,但并非所有网络都能进行信号完整性特性(电压与时序)分析。要想成功筛选出所有特性,被测网络中必须至少包含一个带输出引脚的 IC,且不包含其他元件。例如电阻、电容和电感由于缺少可提供驱动源的输出引脚,单独无法给出仿真结果。需要注意的是,当对双向网络进行筛选时,会对两个方向都进行仿真,并显示最差情况结果。

-

每个元件所关联的信号完整性模型类型必须正确。可通过 Signal Integrity Model Assignments 对话框实现,或在编辑与原理图源文档中已放置元件相关联的信号完整性模型时,在 Signal Integrity Model 对话框中手动为 Type 字段设置正确条目来实现。如果未定义该条目,Signal Integrity Model Assignments 对话框会尝试根据元件特性来猜测其类型。如果仍未定义,将默认认为类型为集成电路(Integrated Circuit)。更多信息请参阅 Adding SI Models Using the Signal Integrity Model Assignments Dialog。

-

必须存在电源网络(Supply Nets)设计规则。通常至少应有两条规则:一条用于电源网络,一条用于地网络。其作用域可以是网络(net)或网络类(net class)。电源网络无法在信号完整性中进行分析。更多信息请参阅 Signal Integrity Design Rules in Schematic 或 Signal Integrity Design Rules in PCB。

-

可以设置“信号激励(Signal Stimulus)”设计规则。只有在你想覆盖默认激励时才需要激励规则,因此一般不必设置。

-

PCB 的层叠(layer stack)必须正确设置。Signal Integrity Analyzer 需要连续的电源平面(power plane)。不支持分割平面(split planes),因此会使用分配给该平面的网络。如果这些平面不存在,则会被假定存在,所以最好显式添加并正确配置。板上所有层、芯板(core)与半固化片(prepreg)的厚度也必须设置正确。使用 Design » Layer Stack Manager 命令在 PCB 编辑器中设置层叠。仅在原理图模式下运行信号完整性时,会使用默认的两层板并带两个内电源平面。如果需要更多控制,你可以创建一个已设置好层叠的空白 PCB。更多内容请参阅 Defining the Layer Stack 页面。

信号的特性(例如电压电平)由被测网络中输出引脚所分配的模型决定。引脚模型是在元件模型分配流程中作为一部分进行分配的,并且这些元件级模型分配可通过更新原理图来保留。也可以覆盖单个引脚模型,例如在 Signal Integrity 面板中双击某个引脚——但请注意,这些引脚级的重新分配不会在不同编辑会话之间保留。

使用 Signal Integrity Model Assignments Dialog 添加 SI 模型

向设计中添加信号完整性模型的最简单方法是使用 Signal Integrity Model Assignments 对话框。

-

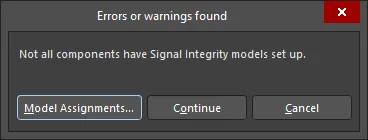

从菜单中选择 Tools » Signal Integrity。如果你刚开始在项目中使用信号完整性,并且存在未附加信号完整性模型的元件,Errors or warnings found 对话框会提示你使用 Signal Integrity Model Assignments 对话框来设置模型分配。

Errors or warnings found 对话框

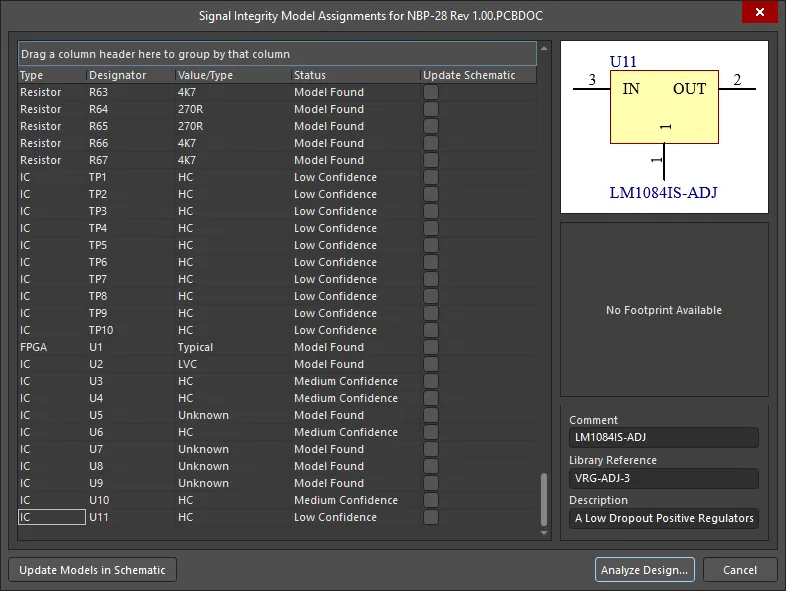

Signal Integrity Model Assignments 对话框

或者,如果你已点击 Continue 且 Signal Integrity 面板可见,则可随时通过点击面板中的 Model Assignments 按钮进入 Signal Integrity Model Assignments 对话框。注意,这样做会清除并重新计算所有结果,因为对模型分配的任何更改都会使现有结果失效。

如果所有元件的模型都已设置完成,则会显示 SI Setup Options 对话框。更多信息请参阅 Configuring the SI Setup Options 。

-

如果你在 Errors or warnings found 对话框中点击 Model Assignments,将显示 Signal Integrity Model Assignments 对话框。

运行时,Signal Integrity Models Assignment 对话框会尝试对每个未包含信号完整性模型的元件所需的模型进行“合理推断”。所有元件(包括已定义模型的元件及其模型信息)都会显示在 Signal Integrity Models Assignment 对话框中。每个元件都会被分配一个状态,如下表所述。

| 状态 |

定义 |

| 无匹配 |

Signal Integrity Model Assignments 对话框无法找到将该元件与某一特定类型关联的任何特征。很可能需要用户修改才能正确设置。 |

| 低置信度 |

Signal Integrity Model Assignments 对话框已为该元件选择了一个类型,但证据不充分。 |

| 中等置信度 |

Signal Integrity Model Assignments 对话框已为该元件选择了一个类型,并对该推断有合理把握。 |

| 高置信度 |

Signal Integrity Model Assignments 对话框已为该元件选择了一个类型,并且符合通常与该类型元件相关的大多数特征。 |

| 找到模型 |

已为该元件找到现有模型。 |

| 用户已修改 |

当用户在 Signal Integrity Model Assignments 对话框中修改了其初始推断后,元件状态将变为此项。 |

| 已添加模型 |

当用户使用 Signal Integrity Model Assignments 对话框修改原理图文档以保存新模型时使用此状态。

|

使用 Signal Integrity Model Assignments Dialog 修改元件模型

-

选择你要修改其模型的元件。

-

选择正确的类型。信号完整性支持七种元件类型——电阻(resistor)、电容(capacitor)、电感(inductor)、二极管(diode)、BJT、连接器(connector)和 IC。每个元件的类型可通过 Type 列中的下拉框选择,或通过右键菜单选择。

-

为电阻、电容或电感设置数值。如果可能,Signal Integrity Model Assignments 对话框会尝试根据元件的注释字段(comment field)和参数,将正确的数值填入该列。如果需要修改(或未填入),应在此时完成。对于器件阵列(例如电阻阵列)这一特殊情况,需要通过单独的对话框完成:点击该列即可进入(更多细节参见 Manually Adding Signal Integrity Models to Components)。

-

如果元件是 IC,工艺/技术类型(technology type)的选择很重要,因为它将决定分析中所用引脚模型的特性。可通过 Value/Type 列中的下拉列表选择,或通过右键菜单(Change Technology)访问。

-

最后,可能需要指定比 Signal Integrity Model Assignments 对话框所允许的更详细信息,例如 IBIS 模型。可通过在右键菜单中选择 Advanced 来实现。关于该流程的更多信息请参阅 Manually Adding Signal Integrity Models to Components。

保存模型

为任意或全部元件选择好模型后,可以更新原理图文档以永久保存这些信息。

-

在 Signal Integrity Model Assignments 对话框中勾选所有需要更新的元件对应的 Update Schematic 列,然后点击 Update Models in Schematic 按钮。

-

每个所选元件的所有新信号完整性模型(或对现有模型的修改)都会被添加到原理图文档中。之后需要保存原理图文档。

继续进行信号完整性分析并不要求必须保存模型。如果不保存,分析将使用 Signal Integrity Model Assignments 对话框中当前显示的所有模型配置继续进行。但下一次使用信号完整性工具时,这些更改将会丢失。

手动为元件添加信号完整性模型

要为原理图元件添加信号完整性模型:

-

对于在原理图编辑器中已放置的元件——选择该元件并打开 Properties 面板。

-

对于在原理图符号编辑器中正在编辑的元件——在 SCH Library 面板中选择其条目以激活所需元件,并 打开 Properties 面板。

在 Properties 面板的 Parameters 区域中点击 Add 按钮并选择 Signal Integrity。将打开 Signal Integrity Model 对话框。

设置你的模型并点击 OK。

设置无源器件

在设置电阻、电容等器件时,通常只需输入类型和值即可。 数值可在 Value 字段中输入,并可作为整个元件的参数进行设置。

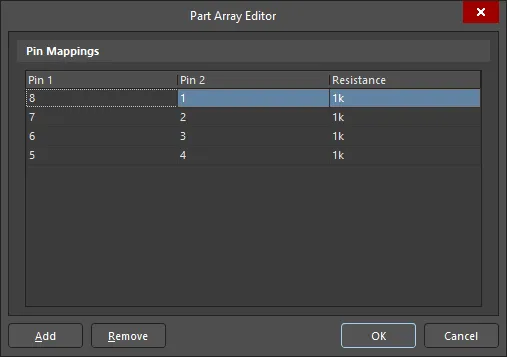

也支持电阻阵列等元件。实现方式为:选择元件类型后,在 Signal Integrity Model 对话框中点击 Setup Part Array 按钮。Part Array Editor 对话框允许配置引脚之间的连接关系,以及这些连接对应的数值/模型。

Part Array Editor 对话框

设置 IC

在设置 IC 类型模型时有多种选择。

导入 IBIS 文件

另一个重要选项是能够导入 IBIS 文件。

-

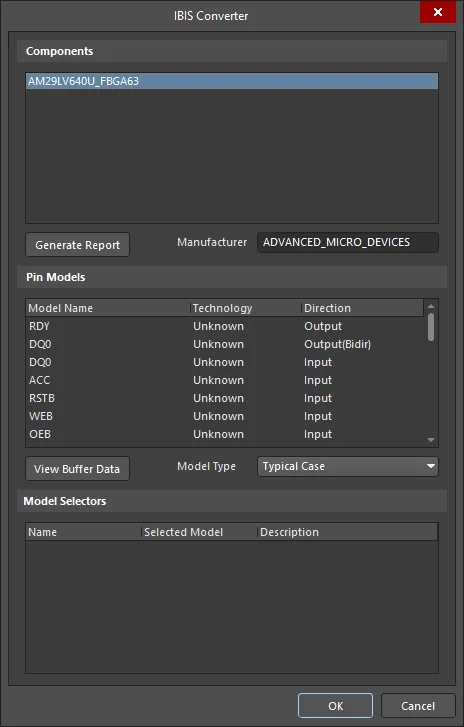

要使用 IBIS(Input/Output Buffer Information,输入/输出缓冲器信息)文件来指定 IC 模型的输入与输出特性,请在 Signal Integrity Model 对话框中单击 Import IBIS 按钮。在 Open IBIS File 对话框中选择 IBIS 文件并单击 Open。将显示 IBIS Converter 对话框。

IBIS Converter 对话框

-

选择 IBIS 文件中包含的所需器件。Altium Designer 将读取 IBIS 文件,并把其中的引脚模型导入到已安装的引脚模型库中。如果发现重复模型,系统会询问是否要覆盖现有模型。此外,器件上的所有引脚都会按 IBIS 文件中的指定分配相应的引脚模型。

-

系统会自动生成一份报告,说明哪些引脚已成功分配、哪些未成功分配。也可以按上述说明,通过手动为相应引脚选择模型来进行进一步自定义。

-

单击 OK 完成 IBIS 信息导入并返回 Signal Integrity Model 对话框。

编辑引脚模型

可以通过指定该引脚的各种电气特性来添加或编辑现有引脚模型。 请注意,这同样适用于 BJT、连接器和二极管等其他类型。

-

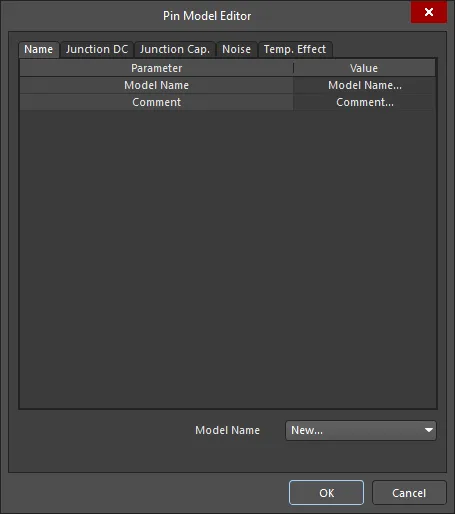

要修改引脚模型,如果该类型提供此按钮,请在 Signal Integrity Model 对话框中单击 Add/Edit Model 按钮。将显示 Pin Model Editor 对话框。

Pin Model Editor 对话框

-

在 Model Name 的下拉列表中单击 New。

-

进行必要的更改并单击 OK。

-

如果这是一个新的引脚模型,那么该模型现在将可用于在此(以及其他)器件的引脚上进行选择。

使用 Ibis Model Implementation Editor

为支持需要专用 IBIS 模型进行信号完整性仿真的第三方工具(且无法使用 Altium Designer 自身的信号完整性模型格式,即 SI Macro Models),Altium Designer 集成了专用的 IBIS 模型实现编辑器,可将 IBIS 模型附加到原理图器件上。因此你可以选择:

-

如上所述,在信号完整性分析期间将 IBIS 引脚模型导入到器件引脚中(并以 Altium Designer SI Macro Models 的形式存储)(参见 导入 IBIS 文件),或

-

按下文所述,将 IBIS 模型附加到原理图器件。

该功能支持所有版本的 IBIS 模型规范,最高支持到 4.0 版(含)。

要向原理图器件添加 IBIS 模型:

-

对于在原理图编辑器中已放置的器件——选择该器件并打开 Properties 面板。

-

对于在原理图符号编辑器中正在编辑的器件——在 SCH Library 面板中选择其条目以激活所需器件,并 打开 Properties 面板。

在 Properties 面板的 Parameters 区域中单击 Add 按钮并选择 Ibis Model。将打开 IBIS Model 对话框。

可以为一个原理图器件定义任意数量的 IBIS 模型链接,但在任意时刻只能有一个处于活动状态。

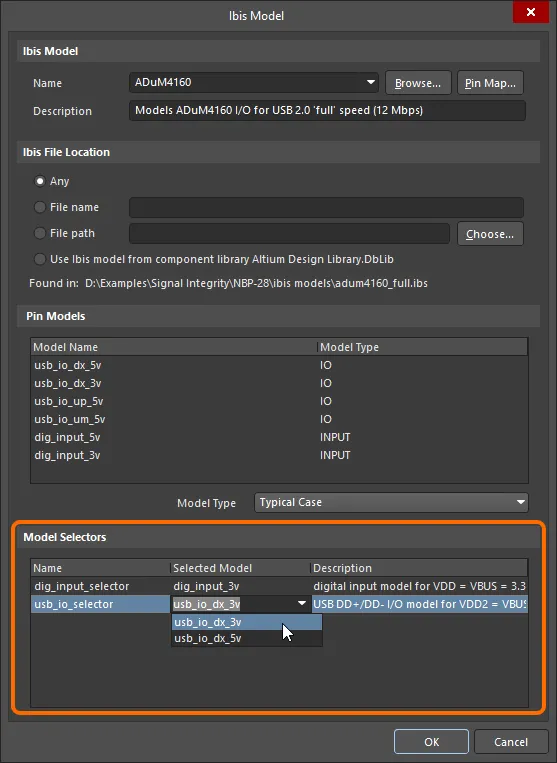

IBIS 模型

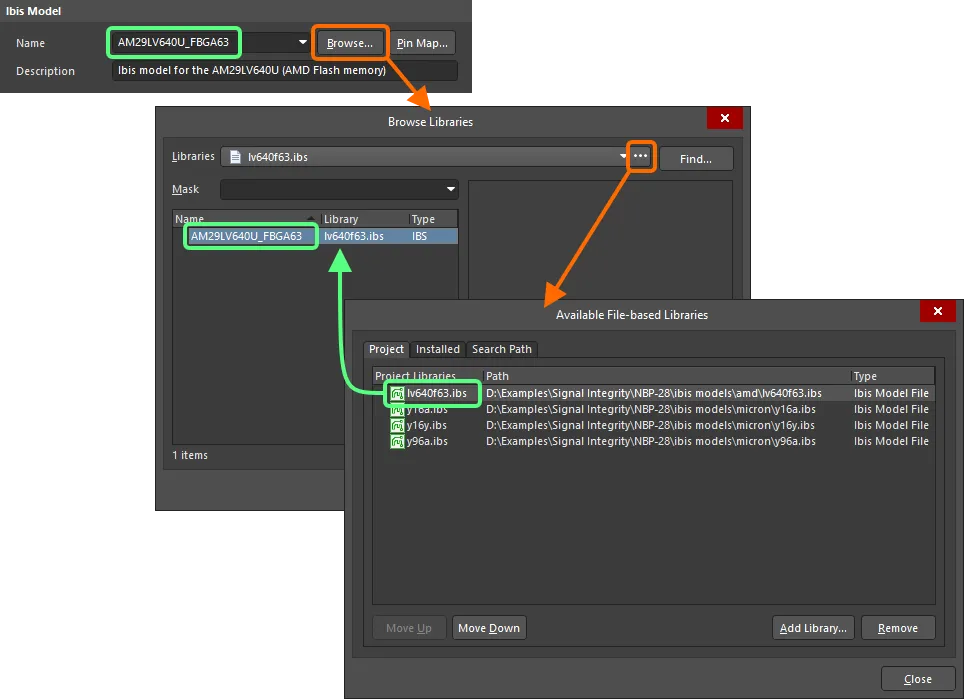

为模型指定名称 ——必须与 .ibs 文件中出现的名称完全一致——并为该模型链接取一个有意义的名称,例如描述该域中的实现所代表的内容。

或者,尤其当你不确定名称时,可使用 Browse 按钮访问 Browse Libraries 对话框。使用该对话框可在所有当前 可用库 中浏览 IBIS 模型文件。如果所需模型文件不在当前可用库中,可使用该对话框中的 Find 功能。

可直接指定模型名称,或浏览选择。

浏览 IBIS 文件时,“名称”下拉列表将按名称列出该文件中定义的所有模型。只需选择所需模型即可。

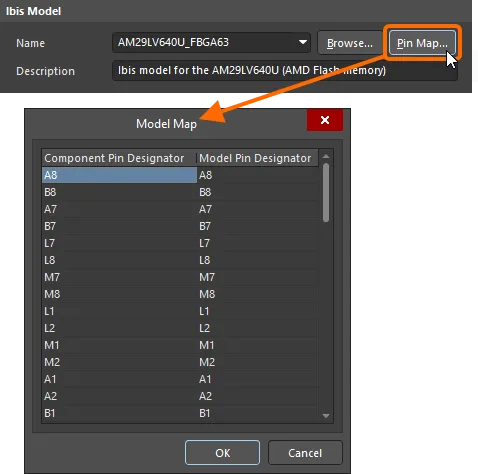

原理图器件引脚与 IBIS 模型引脚的映射在 Model Map 对话框中定义,可通过单击 Pin Map 按钮访问。

在 Model Map 对话框中验证器件到模型的引脚映射。

IBIS 文件位置

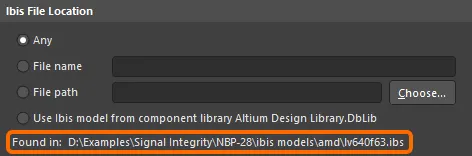

在 IBIS Model 对话框的此区域提供选项,用于指定软件如何定位模型——前提是已定义模型名称:

-

Any – 使用所有可用库(工程库、已安装库以及在已定义搜索路径中找到的库)来查找模型。

-

File name – 输入模型所在的完整文件名(例如

lv640f63.ibs)。使用所有可用库来查找模型。如果在此未找到,将查询默认库路径(即 Preferences 对话框的 System – Default Locations 页面上的 Library Path 字段),以查看是否能在那里找到该命名文件。

-

File path – 输入文件的完整路径/名称。单击 Choose 按钮浏览到该文件。此选项由于是显式指定,因此总能找到模型(当然前提是文件仍保留在该目录中!)。

-

Integrated/Database Library – 放置后,如果器件来自集成库或数据库库,则只要该库属于“可用库”集合,模型即可直接从同一库中获取。

如果成功定位,将显示模型的找到位置提示。

指定如何查找 IBIS 模型。

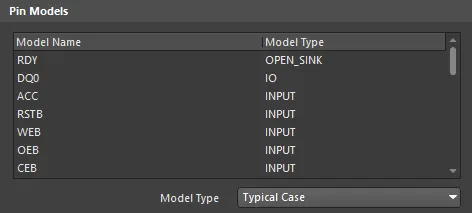

引脚模型

该区域以只读方式列出为所选 IBIS 模型定义的引脚模型。不过,你可以将 Model Type 从默认的 Typical Case,分别更改为 Strong Case 或 Weak Case 。

所选 IBIS 模型的引脚模型。

模型选择器

如果所选 IBIS 模型包含模型选择器,则对话框中的 Model Selectors 区域将被填充。这允许你选择要使用的模型(例如,一个引脚可能针对不同电压等级有不同模型;3.3V、5V 等)。

带有已定义模型选择器的 IBIS 模型示例。

原理图中的信号完整性设计规则

如果将其作为参数添加,则可在原理图中定义用于信号完整性的 PCB 专用设计规则。

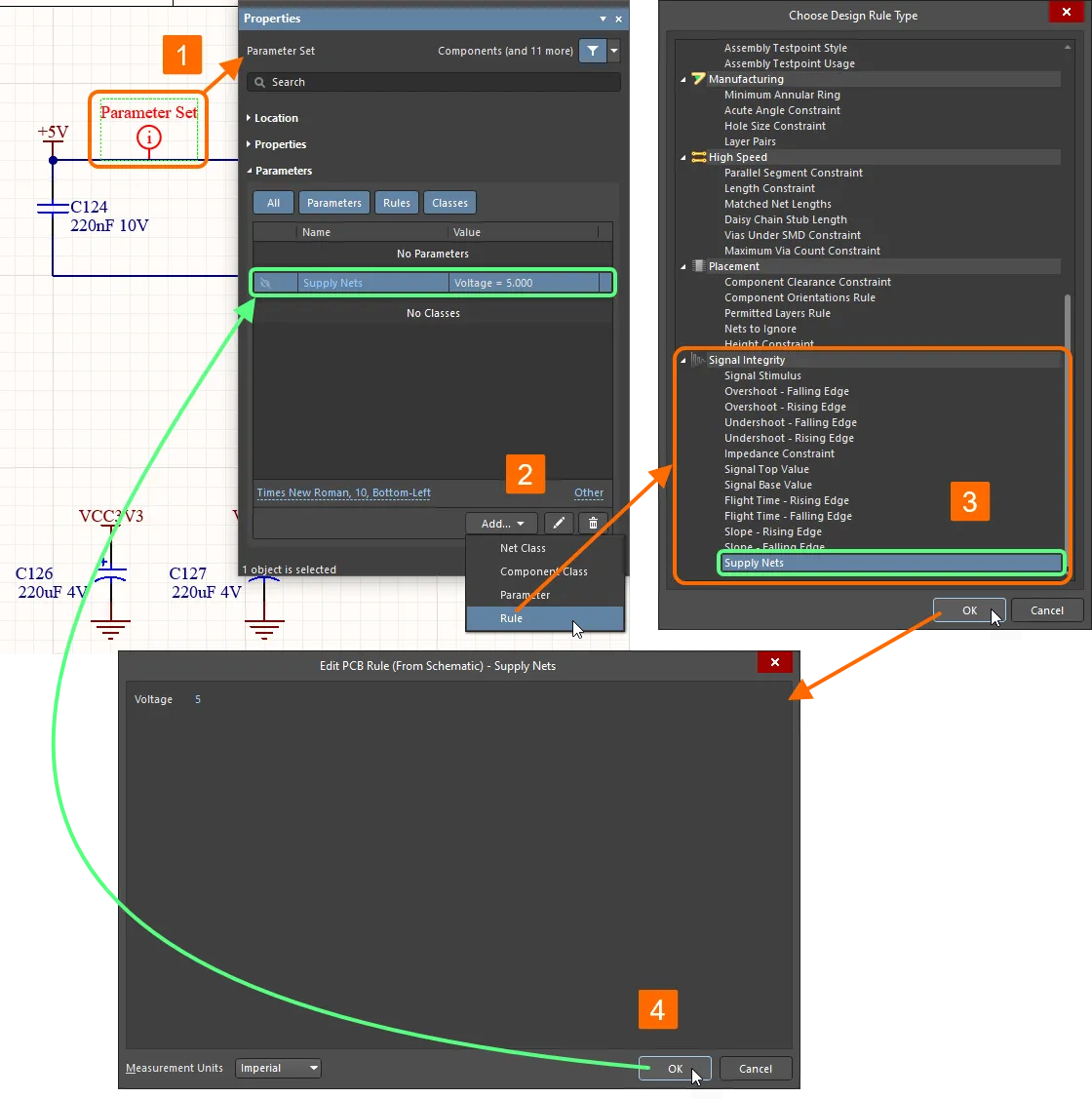

电源网络 设计规则

对于信号完整性分析,应添加一条 PCB 规则,通过使用 Parameter Set directive 来标识电源网络及其电压。要在原理图中添加电源网络设计规则:

-

将 Parameter Set directive(Place » Directive » Parameter Set)放置在相应网络上。

-

选中已放置的指令后,在 Properties 面板的 Parameters 区域中单击 Add 按钮,并从下拉菜单中选择 Rule。

-

将打开 Choose Design Rule Type 对话框,可在其中选择规则类型。 向下滚动到 Signal Integrity 规则并选择 Supply Nets ,然后单击 OK。

-

将显示 Edit PCB Rule (From Schematic) - Supply Nets 对话框。输入该电源网络的电压并单击 OK。该规则条目将列在 Properties 面板中。

可使用 Parameter Set 指令直接在原理图中添加信号完整性设计规则。

将设计传输到 PCB 布局后,该规则会被添加到 PCB 设计规则中(可在 PCB Editor 中通过 Design » Rules 命令打开的 PCB Rules and Constraints Editor 对话框里查看和编辑)。

请注意,在原理图编辑器中,规则的作用域(规则将作用到的对象集合)由参数添加的位置决定,例如添加在导线或引脚上。而在 PCB Editor 中,规则的作用域是在规则本身内部定义的。

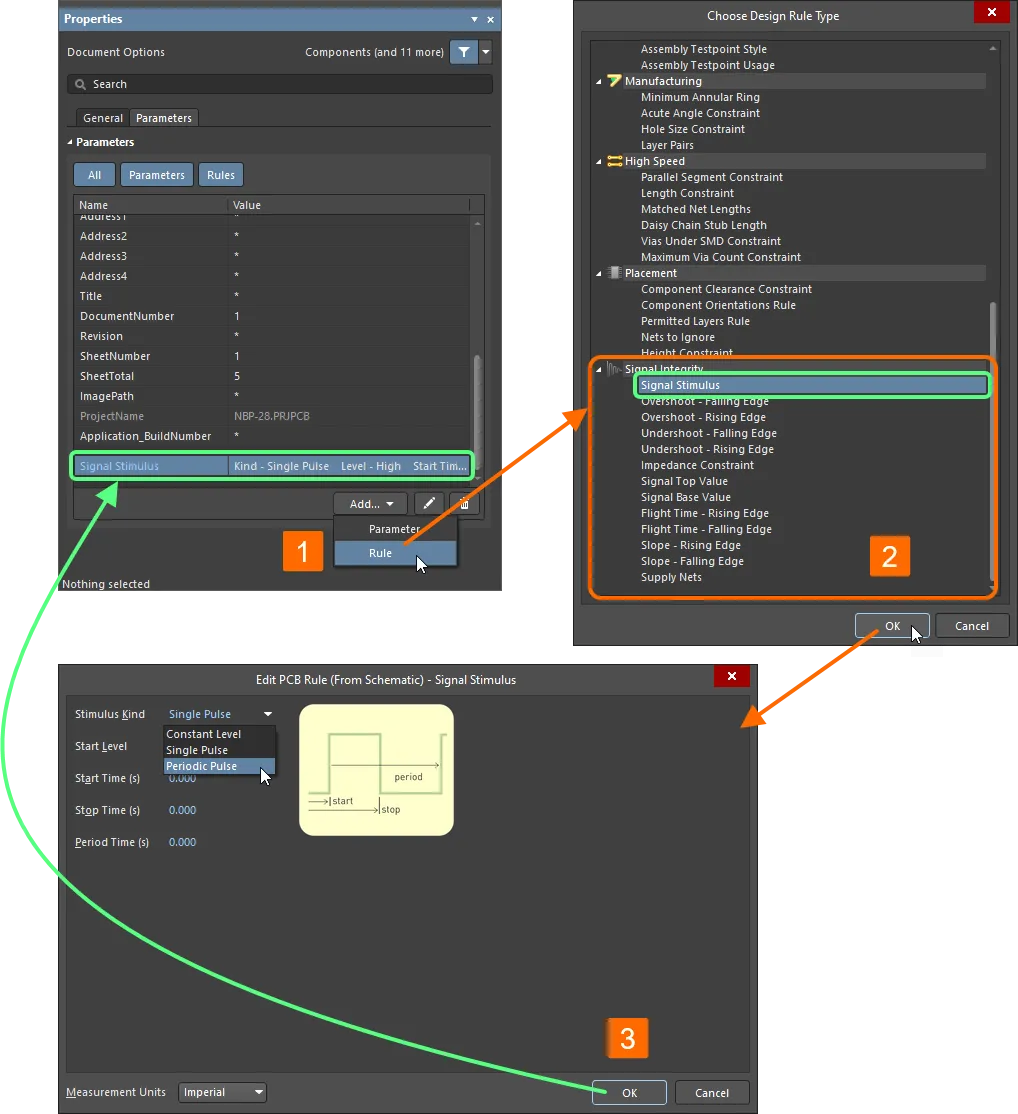

Signal Stimulus 设计规则

另一个可以在原理图编辑器中设置的设计规则是 Signal Stimulus 规则。运行该规则时,会在被分析网络上的每个输出引脚处注入激励。这需要一个作用域为“all”的设计规则,因此你需要为该规则创建一个 sheet parameter。如果不设置该规则,将使用默认的规则选项。

-

当原理图页中未选中任何对象时,打开 Properties 面板。在面板的 Parameters 选项卡上,单击 Add 按钮,并从下拉菜单中选择 Rule。

-

将打开 Choose Design Rule Type 对话框,可在其中选择规则类型。向下滚动到 Signal Integrity 规则并选择 Supply Nets,然后单击 OK。

-

将显示 Edit PCB Rule (From Schematic) - Signal Stimulus 对话框。选择激励类型、起始电平和时间,然后单击 OK。该规则条目会列在 Properties 面板中。

可以将 Signal Integrity 设计规则作为原理图 sheet parameter 添加。

PCB 中的 Signal Integrity 设计规则

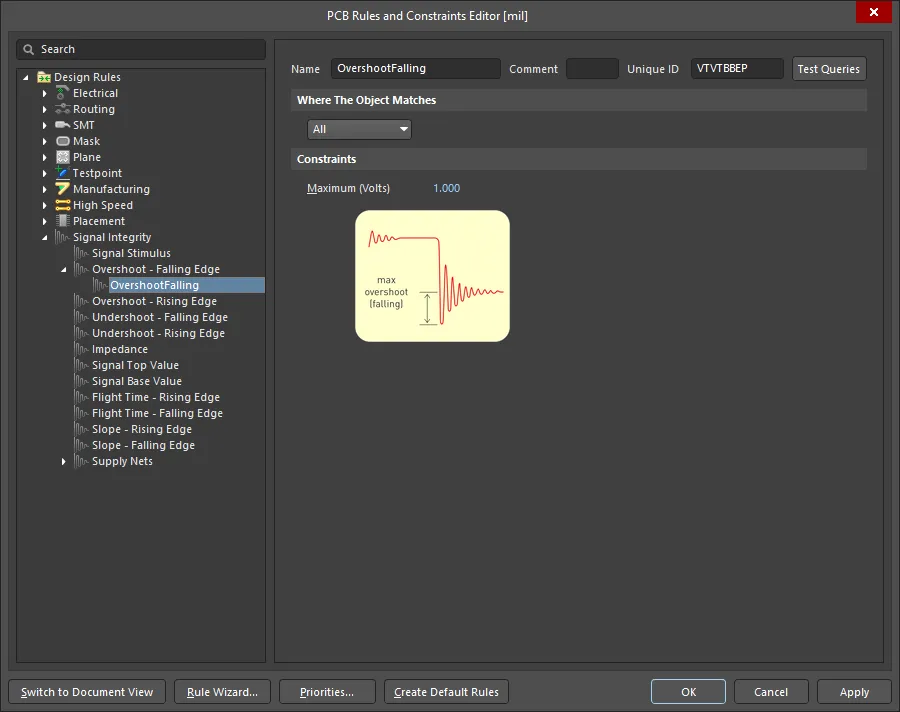

Signal Integrity 参数(例如过冲、下冲、阻抗以及信号斜率要求)可以作为标准 PCB 设计规则来指定。在 PCB Editor 中选择 Design » Rules 以访问 PCB Rules and Constraints Editor 对话框,在其中可设置这些规则。你也可以在原理图编辑器中使用参数来设置这些规则,设计传输到 PCB 布局后,它们会出现在 PCB Rules and Constraint Editor 对话框中。

浏览 Overshoot - Falling Edge 设计规则时的 PCB Rules and Constraint Editor 对话框

这些规则有两个用途。其一是在 PCB 内运行标准 DRC 检查时——可使用标准筛查分析让电路板按这些规则进行检查。其二是在使用 Signal Integrity 面板时——这些规则可被配置并启用为测试项,面板会以图形方式显示哪些网络未通过哪些测试。

当设计准备就绪后,配置并运行信号完整性分析。