パッドとビアの概要

パッドは、部品ピンへの機械的な固定と電気的接続の両方を提供するために使用されます

パッドは、部品ピンへの機械的な固定と電気的接続の両方を提供するために使用されます

パッドはプリミティブ設計オブジェクトです。パッドは、部品を基板に固定し、部品ピンから基板上の配線への相互接続ポイントを作成するために使用されます。パッドは単一レイヤー上に存在することもできます。たとえば、表面実装デバイスのパッドとして使用される場合です。また、Z平面(垂直方向)に樽状の本体を持ち、各(水平)銅レイヤー上に平坦な領域を持つ、三次元のスルーホールパッドであることもあります。パッドの樽状の本体は、製造時に基板へ穴あけとスルーホールめっきが行われることで形成されます。XおよびY平面では、パッドは円形、長方形、八角形、角丸長方形、面取り長方形、またはカスタム形状にできます。パッドは設計内で単独のフリーパッドとして使用することもできますが、一般的にはPCB Libraryエディターで他のプリミティブと組み合わせて部品フットプリントに組み込まれて使用されます。

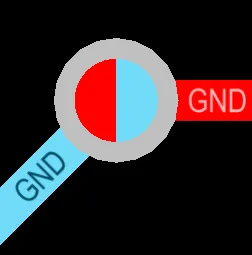

トップレイヤー(赤)からボトムレイヤー(青)まで貫通して接続し、さらに1つの内部電源プレーン(緑)にも接続するビア。

ビアはプリミティブ設計オブジェクトです。ビアは、PCBの2つ以上の電気レイヤー間に垂直方向の電気的接続を形成するために使用されます。ビアは三次元オブジェクトであり、Z平面(垂直方向)に樽状の本体を持ち、各(水平)銅レイヤー上に平坦なリングを持ちます。ビアの樽状の本体は、製造時に基板へ穴あけとスルーホールめっきが行われることで形成されます。ビアは、円形パッドと同様に、XおよびY平面では円形です。ビアとパッドの主な違いは、ビアは基板の全レイヤー(トップからボトム)を貫通できるだけでなく、表面レイヤーから内部レイヤーへ、または2つの内部レイヤー間を接続することもできる点です。

ビアには次の種類があります。

-

Thru-Hole – このタイプのビアはトップレイヤーからボトムレイヤーまで貫通し、すべての内部信号レイヤーへの接続を可能にします。

-

Blind – このタイプのビアは基板表面から内部信号レイヤーへ接続します。

-

Buried – このタイプのビアは1つの内部信号レイヤーから別の内部信号レイヤーへ接続します。

設計で使用できるビアタイプは Layer Stack Manager で定義されます。詳細については、Blind, Buried & Micro Via Definition ページを参照してください。

外部の Pad Via Library にリンクされていない Pad Via テンプレートは PCB ドキュメント内に保存されるため、読み込み時間が短縮されます。

この機能は、Advanced Settings dialog で PCB.Performance.PadViaTemplate.LoadingOptimization オプションを有効にすると利用できます。

PCBエディターでは、'via instancing' という概念 を利用しています。これは、ビアテンプレートそのものではなく、ビアのインスタンスのジオメトリを構築するためのアプローチです。これにより、メモリ消費量とシーン構築時間の両方を削減しつつ、パフォーマンスが向上します。

この機能は Open Beta であり、Advanced Settings dialog で PCB.ViaInstancing オプションを有効にすると利用できます。

パッドおよびビアの直接配置

パッドとビアは、PCBエディターとPCB Footprintエディターの両方で配置できます。ビアは通常、インタラクティブルーティングまたは自動ルーティングの処理中に自動配置されますが、必要に応じて手動で配置することもできます。手動で配置されたビアは「フリー」ビアと呼ばれます。パッド(Place » Pad)またはビア(Place » Via)の配置コマンドを起動すると、カーソルが十字カーソルに変わり、配置モードに入ります。

-

カーソルを位置決めし、クリックするか Enter を押してパッド/ビアを配置します。

-

さらにパッド/ビアを続けて配置するか、右クリックまたは Esc を押して配置モードを終了します。

パッド/ビアを、すでにネットに接続されているオブジェクトの上に配置すると、そのネット名が割り当てられます。

配置中に Alt キーを押すと、初期の移動方向に応じて移動方向が水平方向または垂直方向に制限されます。

Multi-layer レイヤー上のフリーパッドはビアに変更できます。フリーパッドとは、親コンポーネントオブジェクトの一部ではないパッドのことです。フリーパッドをビアに変更することは、インポートしたGerberファイルを手動でPCB形式に戻す際に役立ちます。設計空間で変換したいすべてのフリーパッドを選択し、メインメニューから Tools » Convert » Convert Selected Free Pads to Vias コマンドを選択します。フリーパッドは同じ穴径のビアに変換されます。パッドの利用可能なすべてのXYサイズの組み合わせ(異なるレイヤー上のパッドサイズに対応)の中で最も大きい値が、ビアの直径として使用されます。

また、ビアをフリーパッドに変更することもできます。ビアをフリーパッドに変更することは、PADS-PCB および PADS 2000 ファイルをインポートする際に、ビアが電源層およびグランド層への接続に使用されている場合に役立ちます。これにより、編集可能なパッドを使用して内部電源プレーンへ適切に接続できます。設計空間で変換したいすべてのビアを選択し、メインメニューから Tools » Convert » Convert Selected Vias to Free Pads コマンドを選択します。ビアは、同じスタイル(Simple、Top-Middle-Bottom、または Full Stack)で、同じ穴径のフリーパッドに変換されます。ビアの直径サイズは、該当レイヤー上のパッドのXYサイズとして使用されます。パッドの形状は Round に設定されます。

グラフィカル編集

パッドおよびビアは、位置以外のプロパティをグラフィカルに変更することはできません。

-

フリーパッドを移動し、接続された配線も一緒に移動するには、パッドをクリックして押したまま移動します。接続された配線は、パッドの移動中も接続されたままになります。なお、そのパッドがコンポーネントに属している場合は移動できません。

-

PCB または PCB Library Editor で、接続された配線を移動せずにフリーパッドを移動するには、Edit » Move » Move コマンドを選択してから、パッドをクリックして押したまま移動します。

-

component パッドの周囲を選択矩形でクリック&ドラッグしても、それらは実際にはコンポーネントの子オブジェクトであるため選択されません。パッドだけをサブ選択するには、Ctrl を押しながら選択ウィンドウをクリック&ドラッグします。

-

ビアを配線とともに移動して、より多くの配線スペースまたは部品スペースを確保する場合、配線を移動するより再配線した方が効率的なことがあります。ソフトウェアには Loop Removal と呼ばれる機能があります。この機能を有効にすると、新しい経路に沿って配線し(元の配線上のどこかで開始し、どこかで終了)、インタラクティブルーティングモードを終了するために右クリックするとすぐに、古い配線(ループ)が削除され、冗長なビアも含めて取り除かれます。

Properties パネルによる非グラフィカル編集

この編集方法では、Properties パネルの関連モードを使用して Pad/Via オブジェクトのプロパティを変更します。

Pad Properties

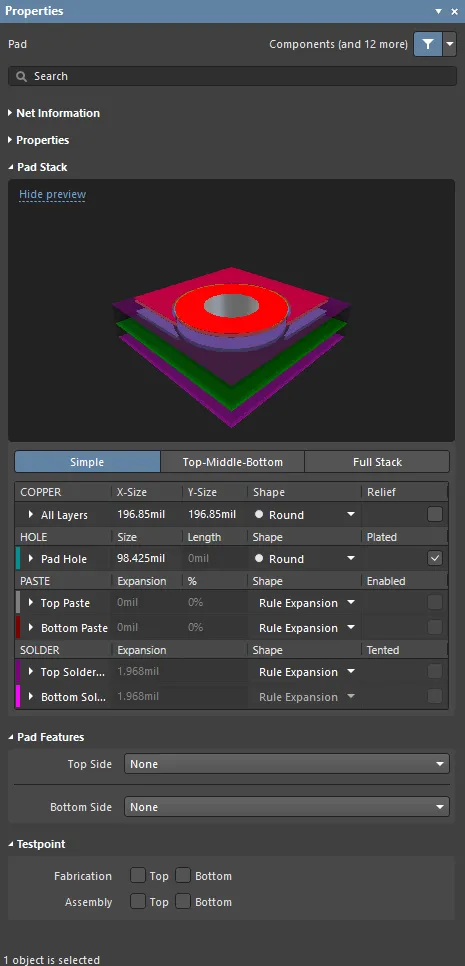

Pad モードの Properties パネル

ネット情報

この領域には、パッドが属するネットに関する情報、およびそのネットがメンバーである場合は差動ペアや xSignal に関する情報が表示されます。必要に応じてクラス情報も表示されます。Delay および Length の値も提供されます。

ネット情報の詳細については、PCB Placement & Editing Techniques ページを参照してください。

プロパティ

-

Component – このフィールドは、選択した Pad が PCB Component の構成要素である場合にのみ PCB エディターで表示され、親 PCB コンポーネントのデジグネーターを表示します。クリック可能な Component リンクを選択すると、親コンポーネントの Component mode of the Properties panel が開きます。

-

Designator – このフィールドには現在のパッドデジグネーターが表示されます。パッドがコンポーネントの一部である場合、デジグネーターは通常、対応する部品ピン番号に設定されます。フリーパッドにはデジグネーターを含めることもできますし、フィールドを空のままにすることもできます。デジグネーターの先頭または末尾が数字で始まる、または終わる場合、複数のパッドを連続して配置するとその数字は自動的にインクリメントされます。パッドデジグネーターを変更するには、このフィールドの値を編集します。

-

Layer – パッドが割り当てられるレイヤーを選択します。スルーホールパッドを定義するには Multi-Layer を選択します。

-

Net – パッドのネットを選択するために使用します。アクティブな基板設計内のすべてのネットがドロップダウンリストに表示されます。パッドがどのネットにも接続されていないことを指定するには、No Net を選択します。プリミティブの Net プロパティは、PCB オブジェクトが適切に配置されているかどうかを Design Rule Checker が判定するために使用されます。あるいは、Assign Net アイコン( )をクリックして設計空間内のオブジェクトを選択することもできます。そのオブジェクトのネットが、選択したパッドに割り当てられます。

)をクリックして設計空間内のオブジェクトを選択することもできます。そのオブジェクトのネットが、選択したパッドに割り当てられます。

-

Electrical Type – このフィールドには、パッドの現在の電気的ステータスが表示されます。このステータスはコンポーネントパッドにのみ関係し、これらのパッドの伝送線路特性を設定します。パッドは、Load、Source、または Terminator として指定できます。Source および Terminator の設定は、ネットで Daisy chain 配線トポロジのいずれかが必要な場合に使用されます。フィールドをクリックすると、ドロップダウンリストから電気タイプを変更できます。

-

Propagation Delay – このフィールドには伝搬遅延が表示されます。これは、信号の先頭が送信側から受信側へ到達するまでにかかる時間です。

-

Pin Package Length – Pin Package Length は、PCB パネルに表示される Signal Length の計算に自動的に含まれます。選択したネット内のピンの Pin/Pkg Length の値を確認(または編集)するには、PCB パネルを Nets モードに設定します。

-

Jumper – PCB 上でジャンパ接続を使用する場合、このフィールドではパッドにジャンパ接続識別番号(1 ~ 1000 の範囲)を割り当てます。ジャンパ接続では、ワイヤを使用して PCB 上のパッド同士を物理的に接続し、基板上のトラックや電気オブジェクトは使用しません。Jumper の値は、どのパッドを「接続済み」として扱うかをソフトウェアに指示します。ジャンパ接続は、コンポーネントフットプリント内のパッド間でのみ作成できます。使用するパッドは同じ Jumper 値を使用し、かつ同じネットを共有している必要があります。ジャンパ接続は、PCB Editor では曲線の接続線として表示されます。スクロール矢印を使用するか、目的のジャンパ接続識別番号を直接入力してください。

-

Template – パッドの現在のテンプレートを表示します。ドロップダウンを使用して別のテンプレートを選択します。関連付けられた Library がある場合は、そのライブラリが表示されます。 ボタンをクリックすると、関連付けられた Pad/Via Template ライブラリからテンプレートのリンクを解除できます。

ボタンをクリックすると、関連付けられた Pad/Via Template ライブラリからテンプレートのリンクを解除できます。

パッドテンプレートのリストは PCB ファイルを最初に開いたときに作成され、その後、現在の編集セッション中に配置されたパッドがそのリストに追加される点に注意してください。テンプレートパッドの配置済みインスタンスをすべて基板から削除しても、そのパッドは PCB ファイルを保存して閉じ、再度開くまでテンプレートリストに残ります。

-

(X/Y)

-

X (最初のフィールド)– このフィールドには、現在の原点を基準としたパッド中心の現在の X 位置が表示されます。フィールド内の値を編集すると、現在の原点に対するパッドの位置を変更できます。値はメートル法またはヤード・ポンド法のいずれでも入力できます。現在のデフォルトと異なる単位の値を入力する場合は、単位を含めてください。デフォルト単位(メートル法またはヤード・ポンド法)は、Board モードの Properties パネル内、Other 領域の Units 設定によって決まり(設計空間でオブジェクトが選択されていないときにアクセス可能)、単位が指定されていない場合に使用されます。

-

Y (2 番目のフィールド)– このフィールドには、現在の原点を基準としたパッド中心の現在の Y 位置が表示されます。フィールド内の値を編集すると、現在の原点に対するパッドの位置を変更できます。値はメートル法またはヤード・ポンド法のいずれでも入力できます。現在のデフォルトと異なる単位の値を入力する場合は、単位を含めてください。デフォルト単位(メートル法またはヤード・ポンド法)は、Board モードの Properties パネル内、Other 領域の Units 設定によって決まり(設計空間でオブジェクトが選択されていないときにアクセス可能)、単位が指定されていない場合に使用されます。

この領域の右側にある

アイコンは、

X フィールドおよび

Y フィールドにアクセスするために、

(ロック解除)として表示されている必要があります。ロック/ロック解除アイコンを切り替えることで、ロック状態を変更できます。ロックされている場合、位置は編集できません。

-

Rotation – パッドの回転角度(度単位)で、ゼロ(3 o'clock 水平)から反時計回りに測定されます。このフィールドを編集してパッドの回転を変更します。最小角度分解能は 0.001° です。

Pad Stack

-

Simple / Top-Middle-Bottom / Full Stack – スルーホールパッド用の目的のパッドスタックモードを選択します(つまり、パッドの Layer として Multi-Layer が選択されている場合)。その他のレイヤでは、Simple モードのオプションが適用されます。

-

Simple – シンプルな積層パッドを選択します。このパッドのすべての信号銅箔レイヤに共通するパッド形状属性を定義できます。

-

Top-Middle-Bottom – Top-Middle-Bottom 積層パッドを選択します。このパッドの上部・中間・下部の各信号銅箔レイヤについて、X サイズ、Y サイズ、および形状属性を定義できます。

-

Full Stack – Full Stack 積層パッドを選択します。このパッドのすべての信号銅箔レイヤについて、X サイズ、Y サイズ、および形状属性を定義できます。

-

Copper – 折りたたみ可能な領域を展開するか、グリッドを使用して信号銅箔レイヤ上のパッド属性を定義します。使用可能な銅箔レイヤのセットは、パッドが配置されているレイヤおよび選択したパッドスタックモードによって異なります。

-

Shape– パッド形状を選択します。標準のパッド形状(Round、Rectangular、Octagonal、Rounded Rectangle、Chamfered Rectangle、および Donut)は、X および Y の設定を変更することで、非対称のパッド形状に調整できます。非標準形状のパッドを定義するには、Custom Shape を選択します(learn more)。

-

Edit Shape – クリックして、デザインスペース内でカスタム形状パッドの領域をインタラクティブに編集します。 このボタンは、Custom Shape が Shape として選択されている場合にのみ使用できます。

-

(X/Y) – パッドの X(水平)および Y(垂直)サイズを定義します。 X と Y のサイズは個別に設定でき、非対称のパッド形状を定義できます。値はメートル法またはヤード・ポンド法のいずれでも入力でき、現在のデフォルトと異なる単位で値を入力する場合は単位を含めてください。デフォルト単位(メートル法またはヤード・ポンド法)は、Board モードの Properties パネル内 Other 領域の Units 設定によって決まり(デザインスペースで何も選択されていないときにアクセス)、単位が指定されていない場合に使用されます。このオプションは、Rounded Rectangle または Chamfered Rectangle が Shape として選択されている場合にのみ使用できます。

-

Corner Radius – パッド角の半径/面取りの絶対値を入力します。値は、パッドの短辺の半分以下である必要があります。 計算されたパーセンテージ値(短辺の半分に対する割合)がフィールドの右側に表示されます。半径/面取りをパッド短辺の半分に対する割合として定義するには、値の後に % 記号を付けて入力します。この場合、100% は短辺を完全に丸めることを意味し(この場合は計算された絶対値がフィールド右側に表示されます)、このオプションは、対応する銅箔レイヤー上のパッド Shape に対して Rounded Rectangle または Chamfered Rectangle が選択されている場合にのみ使用できます。

角の半径/面取りを絶対値として定義する機能は、

PCB.Pad.CustomShape.CornerRadiusAbsolute オプションが

Advanced Settings dialog で有効になっている場合に利用できます。このオプションが無効な場合、

Corner Radius フィールドの値は、パッドの短辺の半分に対する割合としてのみ定義できます。

-

Upper Left、Upper Right、Lower Left、Lower Right – パッド形状の角を丸める/面取りするよう有効にします。 これらのオプションは、対応する銅箔レイヤー上のパッド Shape に対して Rounded Rectangle または Chamfered Rectangle が選択されている場合にのみ使用できます。

-

Outer Diameter – パッドの外径を入力します。 このオプションは、対応する銅箔レイヤー上のパッド Shape に対して Donut が選択されている場合にのみ使用できます。

-

Width – パッドの幅を入力します。 このオプションは、対応する銅箔レイヤー上のパッド Shape に対して Donut が選択されている場合にのみ使用できます。

-

Thermal Relief – 有効にすると、パッドのサーマルリリーフをカスタマイズし、適用される Polygon Connect Style ルールを上書きします。チェックを入れた後、リンクをクリックして Polygon Connect Style ダイアログを開くと、必要に応じてサーマルリリーフのオプションを変更できます。Edit Points ボタンをクリックすると、サーマルリリーフスポークの接続ポイントを手動で定義できます。 Defining Custom Thermal Reliefs の詳細をご覧ください。

-

Center Offset (X/Y) (SMD パッドのみ、つまり Multi-Layer 以外のレイヤーがパッドの Layer として選択されている場合)– パッドのランディング領域を中心からオフセットする値を入力します。

-

Hole – 折りたたみ可能セクションを展開するか、グリッドを使用してパッド穴の属性を定義します。 穴オプションはスルーホールパッドでのみ使用できます (つまり、Multi-Layer がパッドの Layer として選択されている場合)。

-

Shape – 希望する穴形状を選択します。

-

Round – パッドの穴サイズに対して丸穴形状を指定します。穴の種類ごと、およびめっきあり/なしごとに、個別のドリルファイル(NC Drill Excellon format 2)が生成されます。これらの種類に対して、最大6種類の異なるドリルファイルが作成されます。

-

Rectangular – このパッドに対して長方形(打ち抜き)穴を指定します。 長方形穴は、めっきありにもめっきなしにもできます。穴の種類ごと、およびめっきあり/なしごとに、個別のドリルファイル(NC Drill Excellon format 2)が生成されます。これらの種類に対して、最大6種類の異なるドリルファイルが作成されます。

-

Slot – このパッドに対して両端が丸いスロット穴を指定します。スロット穴は、めっきありにもめっきなしにもできます。穴の種類ごと、およびめっきあり/なしごとに、個別のドリルファイル(NC Drill Excellon format 2)が生成されます。これらの種類に対して、最大6種類の異なるドリルファイルが作成されます。

-

Size – このフィールドには、パッドの現在の穴サイズが表示されます。この値は、製造時にパッドに形成される丸穴の直径(または長方形穴やスロット穴の幅)を mil または mm で指定します。SMD パッドまたはエッジコネクタの場合は、これを 0 に設定する必要があります。穴サイズは 0 ~ 1000mil の範囲で設定でき、パッドより大きく設定して(銅なしの)機械穴を定義することもできますが、Length または Rectangular 穴、あるいは Slot 穴の Length より大きくすることはできません。 このフィールドの値を編集して、パッドの穴サイズを変更します。値はメートル系またはヤード・ポンド系のいずれでも入力できます。現在のデフォルトと異なる単位で値を入力する場合は、単位を含めてください。 デフォルト単位(メートル系またはヤード・ポンド系)は、Board モードの Properties パネル内、Other 領域にある Units 設定によって決まり(デザインスペースで何も選択されていないときにアクセス可能)、単位が指定されていない場合に使用されます。

-

Tolerance – 穴公差属性を設定することで、基板のはめあいと許容限界の判断に役立ちます。穴の最小公差(-)および最大公差(+)を指定します。

部品のデータシートには、経年変化、摩耗、温度、めっき、材料、加工などによるばらつきを考慮して、プラス/マイナスの公差が記載されています。穴あけ時には、ドリルビットが摩耗して小さくなったり、ドリルが穴の中でわずかに振動またはぶれたりして、穴がやや大きくなることがあります。さらに取付穴にはめっきが施され、そのめっき厚はロットごとや基板上の位置ごとに異なる場合があります。また、PCB 基材が加工中に熱膨張または収縮することも考慮しなければなりません。そのため、設計プロセスにおいて穴公差は非常に重要であり、あらゆる公差、ドリルの摩耗やぶれ、めっきのばらつきに対応するために必要です。

-

Length – 穴の Shape が Rectangular または Slot に設定されている場合に、パッド内の穴の長さを表示します。この値は、製造時にパッド内で NC ルーティングされる長さを mm または mil で指定します。穴サイズは 0 ~ 1000mil の範囲で設定でき、パッドより大きく設定して(銅なしの)機械穴を定義することもできますが、Rectangular または Slot 穴の Size より小さくすることはできません(必要な X-Y 形式を実現するには Rotation 設定を使用してください)。 このフィールドの値を編集して長さを変更します。値はメートル系またはヤード・ポンド系のいずれでも入力できます。現在のデフォルトと異なる単位で値を入力する場合は、単位を含めてください。 デフォルト単位(メートル系またはヤード・ポンド系)は、Board モードの Properties パネル内、Other 領域にある Units 設定によって決まり(デザインスペースで何も選択されていないときにアクセス可能)、単位が指定されていない場合に使用されます。 このオプションは、穴の Shape が Round に設定されている場合は使用できません。

公称出力のサポートは、ODB++、Gerber、PDF 印刷出力など、他の製造出力にも提供されています。これらに加え、Gerber X2 や IPC-2581 形式など、Altium Designer で利用可能な新しい高度な製造標準では、現在、長方形穴はスロットとして表現されます。

長方形(または正方形)穴を製造できるかどうか、また適切な製造出力形式や、設計内に長方形/正方形穴が存在することを通知する方法については、基板製造業者に確認してください。

-

Rotation – 現在の穴の、パッドに対する反時計回りの回転角度を度単位で表示します。このフィールドを編集して回転を変更します。最小角度分解能は 0.001° です。このオプションは、Rectangular または Slot が穴の Shape として選択されている場合にのみ使用できます。

-

Copper Offset (X/Y) – 値を入力して、パッドの着地領域をパッド穴の中心からオフセットします。

-

Plated – このオプションは、パッドにめっき穴があるかどうかを決定します。このフィールドにチェックマークを入れると、そのパッドはめっき穴パッドとして設定されます。設計内にめっきありパッドとめっきなしパッドの両方が存在する場合、NC ドリルファイルでは、めっきなし穴はめっき穴とは異なるツールを使用するよう設定されます。

-

Paste – 折りたたみ可能な領域を展開するか、グリッドを使用して、ペーストマスク層上のパッド属性を定義します。使用可能なペーストマスク層のセットは、パッドが配置されている層によって異なります。

-

Solder – 折りたたみ可能な領域を展開するか、グリッドを使用して、ソルダーマスクレイヤー上のパッド属性を定義します。使用可能なソルダーマスクレイヤーのセットは、パッドが配置されているレイヤーによって異なります。

Pad Features

Top Side / Bottom Side – 基板の top/bottom 側にある pad counterhole に対して希望するオプションを選択します。使用可能なオプション: None, Counterbore, Countersink。 これらのオプションは、丸形のスルーホールパッドでのみ使用できます(つまり、Multi-Layer がそのパッドの Layer として選択され、かつ Round がそのパッドの hole shape として選択されている場合)。

積層板内の counterhole は、ねじ頭のためのスペースを確保します。countersink hole と counterbore hole は 2 種類の counterhole で、異なる種類のねじに対応できます。このリリースでは、counterbore または countersink hole を選択できるようになりました。countersink と counterbore の主な違いは穴のサイズと形状にあります。counterbore hole はより広く、より四角に近い形状で、ワッシャーを追加できるようになっています。 countersink hole は、皿ねじの裏面にある角度付き形状に一致する円錐状の穴を作成します。countersink は積層板に切削される円錐形の穴です。通常、ねじのテーパー頭部が積層板上面と面一になるようにするために使用されます。これに対して、counterbore は底が平らな穴を作り、側面はまっすぐ下にドリル加工されます。これは通常、六角頭のキャップまたはねじを収めるために使用されます。各パッドにつき、countersink または counterbore hole は 1 つだけ許可されます。

アクティブレイヤー上では、2D で counter hole の輪郭を示す破線がパッドの周囲に表示されます。counterhole は 2D、3D、および Draftsman でサポートされています。

counterhole のサイズがパッドサイズ以上の場合、PCB の対応する側からパッド形状は削除されます(counterhole の加工時にこのパッド形状がドリルで除去されるためです)。

Testpoint

Fabrication/Assembly – これらのオプションでは、製造および/または組み立てテストで testpoint 位置として使用するパッド(スルーホールまたは SMD)を指定できます。 Top を有効にすると、このパッドは top layer の testpoint として定義されます。Bottom を有効にすると、このパッドは bottom layer の testpoint として定義されます。

Via Properties

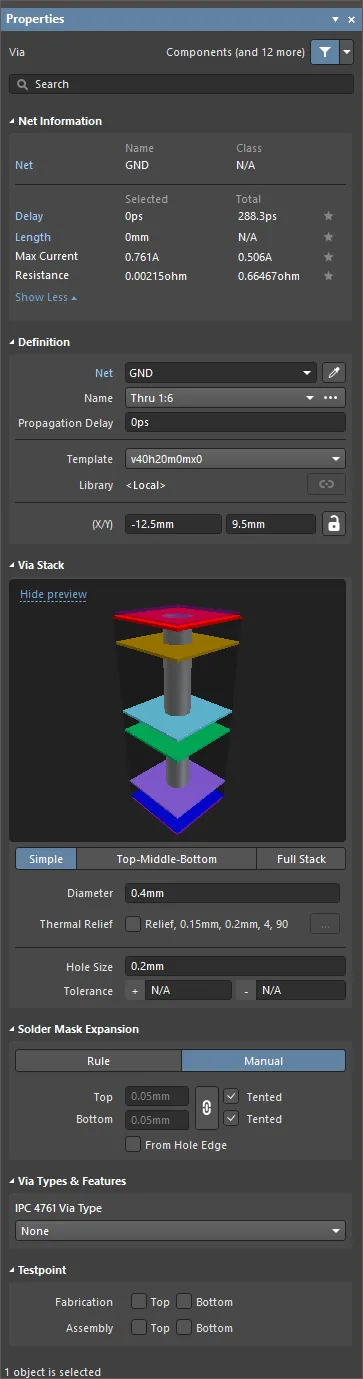

Via モードの Properties パネル

Net Information

この領域には、その via が属するネットに関する情報、およびそのネットがメンバーである場合は differential pair や xSignal に関する情報が表示されます。必要に応じてクラス情報も表示されます。Delay, Length, Max Current, および Resistance の値も提供されます。

ネット情報の詳細については、PCB Placement & Editing Techniques ページを参照してください。

Definition

-

Component – このフィールドは、選択したビアがPCBコンポーネントの構成要素である場合にのみPCBエディターで表示され、親PCBコンポーネントのデジグネーターを表示します。クリック可能なComponentリンクを選択すると、親コンポーネントのComponent mode of the Properties panelが開きます。

-

Net – ビアのネットを選択するために使用します。アクティブな基板設計内のすべてのネットがドロップダウンリストに表示されます。No Net を選択すると、そのビアがどのネットにも接続されていないことを指定できます。プリミティブのNetプロパティは、PCBオブジェクトが適切に配置されているかどうかをDesign Rule Checkerが判定するために使用されます。あるいは、Assign Netアイコン( )をクリックして設計空間内のオブジェクトを選択することもできます。そのオブジェクトのネットが選択したビアに割り当てられます。

)をクリックして設計空間内のオブジェクトを選択することもできます。そのオブジェクトのネットが選択したビアに割り当てられます。

-

Name – 1つ以上のビアが選択されている場合、ドロップダウンをクリックするとビア名が表示されます。このリストには、Layer Stackで定義されているすべてのビアスパンが表示されます。基板上で使用されるすべてのビアは、Layer Stackで定義されたビアスパンのいずれかである必要があります。

-

Propagational Delay – このフィールドには伝搬遅延が表示されます。これは、信号の先頭が送信側から受信側へ到達するまでにかかる時間です。

-

Template – ビアの現在のテンプレートを表示します。ドロップダウンを使用して別のテンプレートを選択します。関連付けられたLibraryがある場合は、そのライブラリが表示されます。

ビアテンプレートのリストはPCBファイルを最初に開いたときに作成され、その後、現在の編集セッション中に配置されたビアがそのリストに追加される点に注意してください。テンプレートビアの配置済みインスタンスをすべて基板から削除しても、そのビアはPCBファイルを保存して閉じ、再度開くまでテンプレートリストに残ります。

-

Library – 現在のライブラリに含まれるビアテンプレートを表示します。Pad Via Library(*.PvLib)からビアを配置した場合、このフィールドにはそのライブラリ名が含まれます。配置後は、 アイコンが有効になり、配置済みビアのプロパティがライブラリで定義されていて、もはや編集できないことを示します。

アイコンが有効になり、配置済みビアのプロパティがライブラリで定義されていて、もはや編集できないことを示します。 アイコンが有効でない場合は、内容を引き続き編集できます。

アイコンが有効でない場合は、内容を引き続き編集できます。

-

(X/Y)

-

X (最初のフィールド) – このフィールドには、現在の原点を基準としたビア中心の現在のX位置が表示されます。フィールド内の値を編集して、現在の原点に対するビアの位置を変更します。値はメートル法またはヤード・ポンド法のいずれでも入力できます。現在のデフォルトと異なる単位で値を入力する場合は、単位を含めてください。デフォルト単位(メートル法またはヤード・ポンド法)は、Board modeのPropertiesパネル内Other領域にあるUnits 設定によって決まり(設計空間で何も選択されていないときにアクセス可能)、単位が指定されていない場合に使用されます。

-

Y (2番目のフィールド) – このフィールドには、現在の原点を基準としたビア中心の現在のY位置が表示されます。フィールド内の値を編集して、現在の原点に対するビアの位置を変更します。値はメートル法またはヤード・ポンド法のいずれでも入力できます。現在のデフォルトと異なる単位で値を入力する場合は、単位を含めてください。デフォルト単位(メートル法またはヤード・ポンド法)は、Board modeのPropertiesパネル内Other領域にあるUnits 設定によって決まり(設計空間で何も選択されていないときにアクセス可能)、単位が指定されていない場合に使用されます。

この領域の右側にある

アイコンは、

(ロック解除)として表示されていなければ、

Xフィールドおよび

Yフィールドにアクセスできません。ロック/ロック解除アイコンを切り替えて、ロック状態を変更してください。

Via Stack

-

Simple – シンプルビアを選択するにはこれを選択します。

-

Top-Middle-Bottom – トップレイヤー、すべての内部信号層、およびBottom Layerで異なる径を選択するにはこれを選択します。

-

Full Stack – Full Stackビアオブジェクトを選択するにはこれを選択します。

-

Hole Size – このフィールドには、ビアの現在の穴径が表示されます。この値は、製造時にビアへドリル加工される穴の直径(円形、正方形、またはスロット形状)をmilまたはmmで指定します。穴径は0~1000milの範囲で設定でき、ビア径より大きく設定して、銅なしの機械穴を定義することもできます。このフィールドの値を編集して、ビアの穴径を変更します。値はメートル法またはヤード・ポンド法のいずれでも入力できます。現在のデフォルトと異なる単位で値を入力する場合は、単位を含めてください。デフォルト単位(メートル法またはヤード・ポンド法)は、Board modeのPropertiesパネル内Other領域にあるUnits 設定によって決まり(設計空間で何も選択されていないときにアクセス可能)、単位が指定されていない場合に使用されます。

-

Tolerance – 穴公差属性を設定すると、基板のはめあいと許容限界の判断に役立ちます。穴の最小(-)および最大(+)公差を指定してください。Altium Designerにはデフォルトの穴公差値はありません。

部品のデータシートには、経年変化、摩耗、温度、めっき、材料、加工などによるばらつきを考慮するために、プラス/マイナスの公差が記載されています。穴あけ時には、ドリルビットが摩耗して小さくなったり、ドリルが穴の中でわずかに振動またはぶれたりして、やや大きな穴になることがあります。さらに取付穴にはめっきが施され、そのめっき厚はロットごと、あるいは基板上の位置ごとに異なる場合があります。また、プリント基板(PCB)基材が加工中に熱膨張または収縮することも考慮する必要があります。そのため、設計プロセスにおいて穴公差は非常に重要であり、あらゆる公差、ドリルの摩耗やぶれ、めっきのばらつきに対応するために必要です。

Solder Mask Expansion

-

Rule – このビアのソルダーマスク拡張を、該当するSolder Mask Expansion設計ルールで定義された値に従わせるにはこれを選択します。

-

Top

-

Tented – ソルダーマスク拡張設計ルール内のソルダーマスク設定を上書きし、このビアのトップレイヤー上のソルダーマスクに開口を設けない(つまりテント処理する)場合はチェックします。このオプションを無効にすると、このビアにはソルダーマスク拡張ルールまたは特定の拡張値が適用されます。

-

Bottom

-

Tented – ソルダーマスク拡張設計ルール内のソルダーマスク設定を上書きし、このビアのボトムレイヤー上のソルダーマスクに開口を設けない(つまりテント処理する)場合はチェックします。このオプションを無効にすると、このビアにはソルダーマスク拡張ルールまたは特定の拡張値が適用されます。

-

Manual – 該当する設計ルールを上書きし、このビアのソルダーマスク拡張値を指定するにはこれを選択します。

-

Top – トップレイヤーのソルダーマスク拡張値を入力します。値はメートル法またはヤード・ポンド法のいずれでも入力できます。現在のデフォルトと異なる単位で値を入力する場合は、単位を含めてください。デフォルト単位(メートル法またはヤード・ポンド法)は、Board モードの Properties パネル内、Other 領域の Units 設定によって決まります(デザインスペースでオブジェクトが何も選択されていないときにアクセス可能)。単位が指定されていない場合は、このデフォルト単位が使用されます。このフィールドは、Tented が有効になっていない場合にのみ使用できます。

-

Tented – ソルダーマスク拡張のデザインルールにあるソルダーマスク設定を上書きし、このビアのトップレイヤーでソルダーマスクに開口を設けず、テント処理された状態にしたい場合にチェックします。このオプションを無効にすると、このビアにはソルダーマスク拡張ルールまたは個別の拡張値が適用されます。

-

Bottom – ボトムレイヤーのソルダーマスク拡張値を入力します。値はメートル法またはヤード・ポンド法のいずれでも入力できます。現在のデフォルトと異なる単位で値を入力する場合は、単位を含めてください。デフォルト単位(メートル法またはヤード・ポンド法)は、Board モードの Properties パネル内、Other 領域の Units 設定によって決まります(デザインスペースでオブジェクトが何も選択されていないときにアクセス可能)。単位が指定されていない場合は、このデフォルト単位が使用されます。このフィールドは、この領域の右側にある

アイコンが

アイコンが  に設定されており、かつ Tented オプションが有効になっていない場合にのみ使用できます。アイコンが

に設定されており、かつ Tented オプションが有効になっていない場合にのみ使用できます。アイコンが  状態で、かつ Tented オプションが有効になっていない場合、ボトムレイヤーのソルダーマスク拡張値はトップレイヤーと同じになります。

状態で、かつ Tented オプションが有効になっていない場合、ボトムレイヤーのソルダーマスク拡張値はトップレイヤーと同じになります。

-

Tented – ソルダーマスク拡張のデザインルールにあるソルダーマスク設定を上書きし、このビアのボトムレイヤーでソルダーマスクに開口を設けず、テント処理された状態にしたい場合にチェックします。このオプションを無効にすると、このビアにはソルダーマスク拡張ルールまたは個別の拡張値が適用されます。

-

From Hole Edge – 有効にすると、ソルダーマスク開口は穴のサイズに追従します。そのため、マスクはビアサイズに依存せず、穴サイズを基準にスケーリングされます。また、ビアの拡張マスク開口サイズは、穴サイズの変更にも追従します。

ビアタイプと機能

-

IPC 4761 Via Type – ドロップダウンを使用して、IPC 4761 規格に従ったビアタイプ Design Guide for Protection of Printed Board Via Structures を選択します。

-

Grid – IPC 4761 Via Type ドロップダウンで

None 以外のビアタイプを選択すると表示されます。選択したビアタイプに応じて利用可能な機能について、基板の Side を選択し、Material を入力します。

プロパティでビアタイプが IPC-4761 に設定されたビアを PCB 設計に配置すると、新しい種類のメカニカルレイヤーおよびコンポーネントレイヤーペアが対応する図形とともに自動的に設計へ追加されます。

IPC-4761 ビアタイプ用のメカニカルレイヤーは自動的に設計へ追加されます。例として、Top Tenting レイヤーがデザインスペースに表示されています。

これらのレイヤーは、PCB 印刷出力、Gerber / Gerber X2、ODB++、および IPC-2581 出力で使用できます。

テストポイント

Fabrication/Assembly – これらのオプションを使用すると、製造テストおよび/または組立テストでテストポイント位置として使用するビアを指定できます。このビアをトップレイヤーのテストポイントとして定義するには Top を有効にします。このビアをボトムレイヤーのテストポイントとして定義するには Bottom を有効にします。

パッドおよびビアのサーマルリリーフ

Properties パネルの Pad Stack / Via Stack 領域にある Thermal Relief フィールドには、現在適用されているサーマルリリーフ設定の概要が表示されます。たとえば、Relief, 15mil, 10mil, 4, 90 は次のことを意味します。

-

サーマルリリーフ接続が適用されている。

-

エアギャップ幅が 15mil である。

-

サーマルリリーフ導体の幅が 10mil である。

-

サーマルリリーフ導体の回転角が 90 度である。

Thermal Relief フィールド内のチェックボックスが無効の場合、パッドおよびビアのポリゴンサーマルリリーフは rules-driven、つまり適用される Polygon Connect Style design rules によって定義されます。個々のパッドについては、必要なレイヤーに対して関連する Thermal Relief オプションを有効にすることで、サーマルリリーフ設定をカスタマイズできます。この場合、サーマルリリーフは custom と見なされます。詳細は Defining Custom Thermal Reliefs を参照してください。

ソルダーマスクおよびペーストマスクの拡張

ソルダーマスクは、各パッド/ビア位置の Solder Mask レイヤー上に自動的に作成されます。ソルダーマスクはネガティブ定義であり、配置されたオブジェクトが Solder Mask レイヤー上の開口を定義します。ペーストマスクは、各パッド位置の Paste Mask レイヤー上に自動的に作成されます。マスクレイヤー上に作成される形状はパッド/ビア形状であり、PCB エディターで設定された Solder Mask Expansion および Paste Mask Expansion デザインルール、または Properties パネルで指定された量だけ拡張または縮小されます。

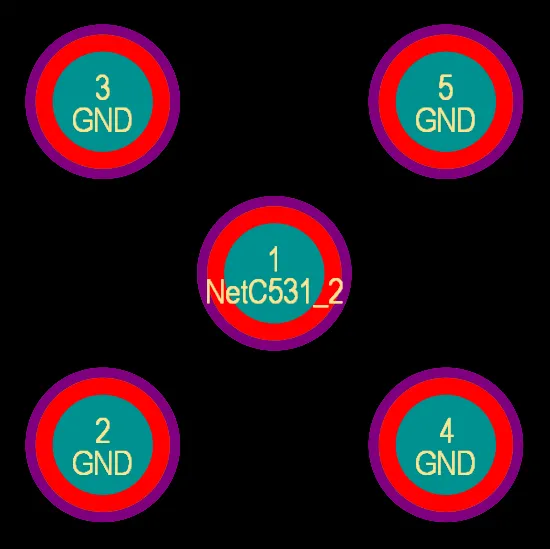

ソルダーマスクを表示したパッド。

パッドまたはビアを編集すると、ソルダーマスク拡張およびペーストマスク拡張の設定が、それぞれ Properties パネルの Pad Stack 領域および Solder Mask Expansion 領域に表示されます。これらの設定はパッド/ビアごとの局所的な拡張要件を制御するために用意されていますが、通常は必要ありません。一般には、PCB エディターで適切なデザインルールを定義して、ペーストマスクおよびソルダーマスクの要件を制御するほうが簡単です。デザインルールを使用すると、まず 1 つのルールで基板上のすべてのコンポーネントの拡張を設定し、必要に応じて、基板上で使用される特定のフットプリントタイプのすべてのインスタンスや、特定のコンポーネント上の特定のパッドなど、特定の状況を対象とする別のルールを追加できます。

デザインルールでマスク拡張を設定するには:

-

Properties パネルの Pad Stack 領域で、Rule Expansion オプションが Shape として選択されていることを確認します(パッドの場合)。または/および、Properties パネルの Solder Mask Expansion 領域で Rule オプションが選択されていることを確認します(ビアの場合)。

-

PCB エディターで、メインメニューから Design » Rules を選択し、PCB Rules and Constraints Editor dialog の Mask カテゴリのデザインルールを確認します。これらのルールは、フットプリントが PCB に配置されたときに適用されます。

拡張デザインルールを上書きし、マスク拡張をパッド/ビア属性として指定するには、Properties パネルの Pad Stack 領域で Manual Expansion を Shape として選択し(パッドの場合)、または/および Properties パネルの Solder Mask Expansion 領域で Manual を選択し(ビアの場合)、必要な値を入力します。

スルーホールパッドのペーストマスクレイヤーは、Draftsman ドキュメント、および Gerber、Gerber X2、ODB++、IPC-2581、PCB 印刷出力でサポートされています。

パッドについては、あらかじめ定義された標準マスク形状セットから手動で選択することも、独自のカスタム形状を作成することもできます –

learn more。

パッドおよびビアのテント処理

パッドおよびビアの部分的または完全なテント処理は、Solder Mask Expansion に適切な値を定義することで実現できます。この拡張制約は、Properties パネルでオブジェクトごとに定義することも、適切な Solder Mask Expansion デザインルールを定義することでも設定できます。拡張値を適切に設定することで、次のことが可能になります。

-

パッド/ビアを部分的にテント処理するには – ランド領域のみを覆う場合、マスクがパッド/ビアの穴の直前まで閉じるように、Expansion に負の値を設定します。

-

パッド/ビアを完全にテント処理するには – ランドと穴の両方を覆う場合、Expansion にパッド/ビア半径以上の負の値を設定します。

-

単一レイヤー上のすべてのパッド/ビアをテント処理するには、適切な Expansion 値を設定し、Solder Mask Expansion ルールのスコープ(Full Query)が必要なレイヤー上のすべてのパッド/ビアを対象にしていることを確認します。

-

異なるビアサイズが定義されている設計内のすべてのパッド/ビアを完全にテント処理するには、最大のパッド/ビア半径以上の負の値を Expansion に設定します。個々のパッド/ビアをテント処理する場合は、適用されるデザインルールで定義された拡張に従うか、ルールを上書きして対象の個々のパッド/ビアに指定した拡張を直接適用するオプションを利用できます。

テストポイント

Related page: 基板上でのテストポイントの割り当て

このソフトウェアはテストポイントを完全にサポートしており、パッド(スルーホールまたは SMD)およびビアを、製造テストおよび/または組立テストで使用するテストポイント位置として指定できます。パッド/ビアをテストポイントとして指定するには、関連するテストポイントプロパティを設定します。つまり、それが製造テスト用か組立テスト用か、また基板のどちら側でテストポイントとして使用するかを指定します。これらのプロパティは、Properties panel の Testpoint 領域にあります。

プロセスを効率化し、テストポイントのプロパティを手動で設定する必要を軽減するために、ソフトウェアには、定義された設計ルールに基づいて Testpoint Manager(Tools » Testpoint Manager)を使用し、テストポイントを自動的に割り当てる方法が用意されています。いずれの場合も、この自動割り当てにより、該当するパッド/ビアに関連するテストポイントのプロパティが設定されます。

Pad の詳細

Pad のデジグネータ

各 Pad には、最大 20 文字の英数字からなるデジグネータ(通常はコンポーネントのピン番号を表す)を付ける必要があります。最初の Pad のデジグネータが数字で終わっている場合、配置時に Pad デジグネータは自動的に 1 ずつ増加します。配置前に、最初の Pad のデジグネータを Properties パネルから変更してください。

アルファベットでの増分、たとえば 1A、1B、または 1 以外の数値増分を実現するには、Paste Array ボタンを Paste Special dialog(Edit » Paste Special)で押して開く Setup Paste Array dialog を使用します。

Paste Array 機能

Pad をクリップボードにコピーする前にそのデジグネータを設定しておくことで、Setup Paste Array ダイアログを使用して、Pad 配置時にデジグネータの連番を自動適用できます。Setup Paste Array ダイアログの Text Increment フィールドを使用すると、次の Pad デジグネータのシーケンスを配置できます。

-

数値(1、3、5)

-

アルファベット(A、B、C)

-

英数字の組み合わせ(A1 A2、 1A 1B、A1 B1、または 1A 2A など)

数値で増分するには、Text Increment フィールドに増やしたい量を設定します。アルファベットで増分するには、Text Increment フィールドに、スキップしたい文字数を表すアルファベットの文字を設定します。たとえば、最初の Pad のデジグネータが 1A の場合、デジグネータを 1 ずつ増やすには、このフィールドを A(アルファベットの最初の文字)に設定します。フィールドを C(アルファベットの 3 番目の文字)に設定すると、デジグネータは 1A、1D(A の 3 文字後)、1G… のようになります。

ジャンパ接続

ジャンパ接続は、PCB 上でプリミティブによって物理的に配線されていないコンポーネント Pad 間の電気的接続を定義します。これは特に単層基板で有用で、1 つの物理層上のトラックをまたぐためにワイヤを使用する場合に役立ちます。

コンポーネント内の Pad には、Properties パネル内から Jumper 値を設定できます。同じ Jumper と電気ネットを共有する Pad は、それらの間に物理的な接続はなくても正当な接続が存在することをシステムに伝えます。

ジャンパ接続は、PCB Editor では曲線の接続線として表示されます。Design Rules Checker は、ジャンパ接続を未配線ネットとして報告しません。

Via の詳細

Via プロパティの定義

各 Via タイプの層をまたぐ要件(Z プレーン)は the Via Types tab of the Layer Stack Manager で定義されますが、Via のサイズプロパティは次のいずれかによって定義されます。

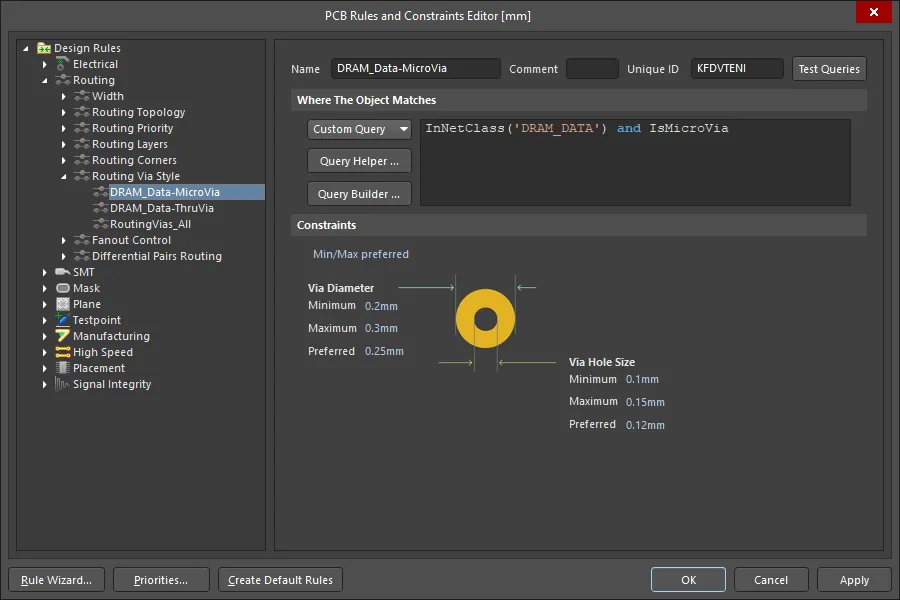

Routing Via Style 設計ルールの設定

Main page: PCB 設計ルールの定義、スコープ設定、および管理

インタラクティブルーティング、ActiveRouting、または自動配線中に配置される Via のサイズプロパティは、適用される Routing Via Style 設計ルールによって制御されます。設計ルールで Via を対象指定しやすくするために、ルールスコープ(Where the Object Matches)で使用できる Via 関連のクエリキーワード群が用意されています。これらについては 以下で詳しく説明します。

配線中にレイヤ変更を行うと、ソフトウェアはそのレイヤ変更の開始層と終了層を確認し、Layer Stack Manager から許可された Via Type を選択します。次に、最も優先度の高い適用可能な Routing Via Style 設計ルールを特定し、そのルールの Constraints セクションにある Via サイズ設定を、これから配置される Via に適用します。

たとえば、DRAM_DATA ネットのセットについて、TopLayer - S2 のレイヤ遷移および S2 - S3 のレイヤ遷移には µVia が必要で、それ以外のすべてのレイヤ遷移にはドリル加工されたスルーホール Via が必要になる場合があります(しかもこれは他のネットに必要な Via とも異なります)。これは、これらの DRAM_DATA ネットを対象とする 2 つの Routing Via Style 設計ルールを作成することで対応できます。適切な µVia 設計ルールの例を以下に示します。画像の上にカーソルを置くと、スルーホール設計ルールが表示されます。

設計ルールは、特定の種類の Via に適用されるようスコープ設定できます。

Via が空き領域に配置される場合、配置中にソフトウェアが Routing Via Style 設計ルールを適用することはできません。この場合は、デフォルトの Via が配置されます。

Query Keywords

Routing Via Style 設計ルールのスコープ設定を簡単にするために、次の Via 関連クエリキーワードを使用できます。

| Via Type Query |

Returns |

| IsVia |

Via Type に関係なく、すべての Via オブジェクト。 |

| IsThruVia |

トップレイヤからボトムレイヤまで貫通するすべての Via。 |

| IsBlindVia |

表層から内部層で終わる、µVia ではないすべての Via。 |

| IsBuriedVia |

内部層から別の内部層へ接続する、µVia ではないすべての Via。 |

| IsMicroVia |

µVia オプションが有効で、隣接層を接続するすべての Via。 |

| IsSkipVia |

µVia オプションが有効で、2 層をまたぐすべての Via。 |

使用可能な Via 関連キーワードを見つけるには、Query Helper の Mask 機能を使用してください。リスト内でクエリキーワードを選択した状態で F1 を押すと、そのキーワードのヘルプが表示されます。

インタラクティブルーティング中の Via 配置

インタラクティブルーティング中にレイヤを変更すると、ソフトウェアは自動的に Via を挿入します。選択される Via は、次の要素によって決まります。

-

レイヤ変更でまたぐ層に対して使用可能な Via Type。

-

そのレイヤ変更で選択された Via Type に適用される Routing Via Style 設計ルール。

インタラクティブルーティング中にレイヤを変更するには、次の操作を行います。

-

テンキーの * キーを押して、次の信号レイヤへ進みます。

-

Ctrl+Shift+WheelRoll の組み合わせを使用して、レイヤを上下に移動します。

L1 から L4 へのレイヤ変更時に配置されるスタックド µVia。Properties パネルの Interactive Routing モードには、配置される Via Type が表示されます。6 を押すと使用可能な Via スタックを順に切り替え、8 を押すと使用可能な Via スタックの一覧を表示します。

インタラクティブルーティング中に配置される Via の制御

-

配線レイヤを変更すると、ソフトウェアはそのレイヤスパンに最も適した Via Type を自動的に選択します。

-

使用可能な Via Type/組み合わせ(Via スタック)が複数ある場合は、6 ショートカットキーを押して、そのレイヤ変更で使用可能なすべての Via スタックをインタラクティブに順送りできます。8 ショートカットを押すと一覧が表示されます。Via スタックは、µVia を使用、Skip µVia を使用、Blind via を使用、Thruhole via を使用、の順で提示されます。レイヤ変更が 1 層を超え、適切な Via Type が定義されている場合は、スタックド Via を配置できます。提案される Via Type は、ステータスバーおよび Heads Up 表示に詳細が示されます。たとえば、上の画像に示すように [µVia 1:2, µVia 2:3, µVia 3:4] のように表示されます。

-

最後に使用した Via スタックは、次に配線するネットのデフォルトとして保持されます。このデフォルト Via スタックは、現在の編集セッション中のみ保持されます。

-

Via のサイズプロパティは、適用される Routing Via Style design rule によって指定されます。適切な Routing Via Style 設計ルールを定義するための方針については、前述しています。

-

レイヤ変更の実行中に Via サイズをインタラクティブに変更するには、4 ショートカットを押します。これにより Via Size モード(Rule Minimum、Rule Preferred、Rule Maximum、User Choice)が順に切り替わります。現在の Via-Size モードは、Heads Up 表示とステータスバーに表示されます(上の画像参照)。User Choice が選択されている場合は、Shift+V を押して Choose Via Sizes dialog を開き、希望する Via サイズを選択します。ダイアログに表示される使用可能な Via サイズの一覧は、設計内ですでに使用されている Via の一覧から取得されます。これらは PCB パネルの Pad and Via Templates mode で確認できます。

適用される Routing Via Style design rule で Template preferred モードが使用されている場合、4 ショートカットを使用すると、有効な Via テンプレートを順に切り替えられます。

-

提案される Via Type の側面図は、上記のように Properties パネルに表示されます。

-

Via を配置して同じレイヤで配線を続けるには、2 ショートカットを押します。

-

Via を配置してこの接続の配線を一時停止するには、テンキーの / ショートカットを押します。

-

配線中のネットを内部電源プレーンに接続する場合は、適切な電源プレーンに接続する Via を配置するために、テンキーの / キーを押します。これは Any Angle モードを除くすべてのトラック配置モードで機能します。

-

配線中に Shift+F1 を押すと、コマンド実行中に使用できるすべてのショートカットのメニューが表示されます。

スタックド Via の操作

-

連続した接続を形成するスタックドビアは、単一のビアであるかのように扱うことができ、click and drag をスタック上で行うと、接続された配線とともにすべて移動できます。

-

最上位のビアを選択するには 1 回クリックします。マウスを動かさなければ、その後のシングルクリックでスタック内の他の各ビアが順に選択されます。

Preferences ダイアログの PCB Editor – General page で Display popup selection dialog オプションが有効になっている場合、ビアのスタックをクリックすると選択ポップアップが開き、必要なビアを選択できます。

-

Ctrl+Click and drag を使用すると、選択したビアのみを接続された配線とともに移動できます。

-

スタック内のすべてのビアを選択するには、1 回クリックして 1 つ選択し、次に Tab を押して、そのスタック内のすべてのビアを含むように選択範囲を拡張します。

ビア表示の設定

ビアの操作を支援するために、さまざまな表示機能が用意されています。

ビアの色

ビアの色は View Configuration panel で設定します。ビアの銅リングは、Layers セクションの現在の Multi-Layer 設定で表示されます。ビアホールの色は、System Colors セクションの Via Holes 設定で表示されます。また、必要な設定の  を切り替えることで、ホールの表示を無効にすることもできます。

を切り替えることで、ホールの表示を無効にすることもできます。

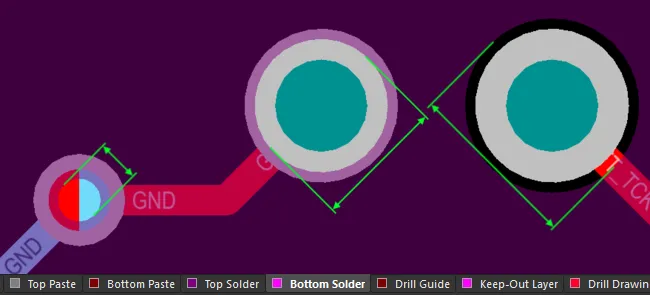

最初の画像にはスルーホールビアが表示されています。2 番目の画像のビアはブラインドビアで、ホールは開始層と終了層の色で表示されています。

ビアとソルダーマスク

PCB エディタにおけるレイヤーのデフォルト表示では、常に Multi-Layer が最前面のレイヤーとして表示されます。そのため、特にパッドやビアで負のマスク拡張が使用されている場合、ソルダーマスクレイヤーの内容がマルチレイヤーオブジェクトの下に隠れて見えなくなるため、ソルダーマスクレイヤーの内容を正確に確認しにくくなることがあります。これは、Preferences ダイアログの PCB Editor – Display ページでレイヤーの描画順序を変更することで改善できます。現在のレイヤーが最前面に描画されるように設定してください。

レイヤーの描画順序を変更して Current Layer を最前面に表示するようにすると、Top Solder を現在のレイヤーにした際に、下の画像に示すようにマスク開口が正確に表示されます。緑の矢印は、左側のビアのソルダーマスク開口サイズ、中央のマスク開口が縮小されたパッド、右側の開口が拡張されたパッドを示しています。

ソルダーマスク開口を確認できるように表示設定を構成します。

スタックドビアの表示

スタックドビアがある場合、表示される番号はスタック内のすべてのビアの開始層と終了層です。下の画像にカーソルを合わせるとビアが 3D で表示されます。画像右側には 3 つのビアのスタックがあります。

ビア内にまたがるレイヤーを表示できます。カーソルを合わせるとビアが 3D で表示されます。

ビア内にまたがるレイヤーを表示できます。カーソルを合わせるとビアが 3D で表示されます。

その他のビア表示設定

ビアのネット名と、ビアのスパン内のレイヤー番号を表示するには、View Configuration panel の View Options タブにある Additional Options 領域で、それぞれ Via Nets および Via Span オプションを有効にします。

パッドおよびビアホールの参照

PCB panel’s Hole Size Editor モードでは、3 つの主要領域が次の内容を反映するように変化します(上から順に)。

-

ホールタイプとそのステータスに対する一般的なフィルタリング。これには、基板に現在定義されているレイヤードリルペアのサブセクションも含まれます。

-

Unique Holes サイズと形状によって決定されるグループに整理された項目。

-

各ホールオブジェクトグループを構成する個々の Pads/Vias 。

パネルの各セクションには、ホールタイプ、スタイル、およびステータスに対して累積的に適用されたフィルタリングが表示されます。

ホールのグループは、パネルの Unique Holes 領域で、適切な列セルに値を入力することで一括編集できます。Hole Size 列では、数値を入力してパッドおよびビアの現在のホールサイズを変更できます。

一致する 6 つのホールスタイルの選択グループに対してホールサイズを編集しています。

必要に応じて、ホールに対応する Hole Length、Hole Type、および Plated の各項目も変更できます。

一致する 6 つのホールスタイルの選択グループに対してホールタイプを変更しています。

選択したホールグループに属する個々のパッド/ビアオブジェクトは、PCB panel の下部 Pad/Via セクションに一覧表示されます。リスト内のオブジェクトを右クリックして Properties を選択するか(または項目を直接ダブルクリックする)、そのプリミティブに対応する Properties panel の関連モードを開くと、そのプロパティを表示および編集できます。

PCB の現在のドリルシンボルデータで PCB panel の Hole Size Editor モードを更新するには、このモードのパネル領域内で右クリックし、Refresh コマンドを選択します。

ドリルシンボルデータは、PCB ドキュメントの保存時、およびこのデータを含む出力の生成時に自動的に更新されます。

パフォーマンス向上のため、ドリルシンボルデータは PCB panel では自動更新されません。Advanced Settings dialog で PCB.LiveDrillSymbols オプションが無効になっている場合は、ドリルシンボルデータを手動で更新できます。

バックドリルのサポート

Hole Size Editor mode の PCB panel は、バックドリル対象のパッドやビアを確認するためにも使用できます。バックドリルのレイヤーペアは、Layer Pairs リスト内で [BD] というテキストが追加されて表示されます。

バックドリルのホールサイズを選択すると、オブジェクトの Kind は Backdrill として表示されます。この機能を使用すると、バックドリルされたホールをすばやく見つけて確認できます。なお、バックドリル設定はこのパネルでは編集できません。

バックドリルレポート

すべてのバックドリルイベントのレポートを生成するには、Unique Holes リスト内で右クリックし、コンテキストメニューから Backdrill Report を選択します。

このレポートには、位置、ドリルサイズ、ドリル深さを含む各バックドリルイベントの詳細が記載されます。

カウンターホールのサポート

Hole Size Editor mode の PCB panel は、カウンターホール機能が有効なパッドを確認するためにも使用できます。PCB 設計で、片側または両側に対してカウンターホール(座ぐり/皿もみ)機能が有効なパッドオブジェクトがある場合、対応する Counterholes Top および/または Counterholes Bottom グループが Layer Pairs リストに表示されます。Unique Holes 領域では、Counterhole Depth 列および Counterhole Angle 列を表示できます。なお、カウンターホール設定はこのパネルでは編集できません。

設計内のカウンターホールに関する情報は、PCB panel の Hole Size Editor mode に表示されます。