Aby przeprowadzić skuteczną analizę integralności sygnału (Signal Integrity) projektu i uzyskać dokładne wyniki, przed uruchomieniem analizy należy wykonać poniższe czynności.

-

Chociaż każdą sieć można przescreenować w celu uzyskania danych o sieci i impedancji, nie wszystkie sieci można analizować pod kątem cech integralności sygnału (napięcie i czas). Aby pomyślnie przescreenować wszystkie cechy, sieć musi zawierać co najmniej jeden układ scalony (IC) z pinem wyjściowym i nie może zawierać innych komponentów. Rezystory, kondensatory i indukcyjności, na przykład, nie dostarczą samodzielnie wyników symulacji, ponieważ nie mają pinu wyjściowego, który zapewniałby źródło wymuszające. Należy zauważyć, że gdy przescreenowywane są sieci dwukierunkowe, symulowane są oba kierunki, a wyświetlany jest wynik dla najgorszego przypadku.

-

Powiązany typ modelu Signal Integrity dla każdego komponentu musi być poprawny. Osiąga się to poprzez okno dialogowe Signal Integrity Model Assignments albo przez ręczne ustawienie właściwego wpisu w polu Type w oknie dialogowym Signal Integrity Model, podczas edycji modelu Signal Integrity powiązanego z komponentem umieszczonym w źródłowym dokumencie schematu. Jeśli ten wpis nie jest zdefiniowany, okno dialogowe Signal Integrity Model Assignments spróbuje odgadnąć typ komponentu na podstawie jego charakterystyk. Jeśli ten wpis nie jest zdefiniowany, zostanie przyjęty typ Integrated Circuit. Więcej informacji: Adding SI Models Using the Signal Integrity Model Assignments Dialog.

-

Muszą istnieć reguły projektowe Supply Nets. Zwykle powinny być co najmniej dwie reguły: jedna dla sieci zasilania i jedna dla sieci masy. Ich zakres może dotyczyć sieci (net) lub klasy sieci (net class). Sieci zasilania nie mogą być analizowane w Signal Integrity. Więcej informacji: Signal Integrity Design Rules in Schematic lub Signal Integrity Design Rules in PCB.

-

Można skonfigurować regułę projektową Signal Stimulus. Reguła bodźca (stimulus) jest potrzebna tylko wtedy, gdy chcesz nadpisać bodziec domyślny, więc zazwyczaj nie jest wymagana.

-

Stos warstw PCB musi być poprawnie skonfigurowany. Signal Integrity Analyzer wymaga ciągłych płaszczyzn zasilania. Płaszczyzny dzielone (split planes) nie są obsługiwane, więc używana jest sieć przypisana do płaszczyzny. Jeśli płaszczyzny nie są obecne, są one zakładane, dlatego znacznie lepiej jest je dodać i odpowiednio skonfigurować. Grubość wszystkich warstw, rdzeni (cores) i prepregów również musi być poprawnie ustawiona dla płytki. Użyj polecenia Design » Layer Stack Manager, aby skonfigurować stos warstw w edytorze PCB. Podczas uruchamiania Signal Integrity w trybie „schematic only” używana jest domyślna płytka dwuwarstwowa z dwiema wewnętrznymi płaszczyznami. Jeśli potrzebna jest większa kontrola, możesz utworzyć pusty PCB z odpowiednio skonfigurowanym stosem warstw. Więcej informacji na stronie Defining the Layer Stack .

Charakterystyki sygnału, takie jak poziom napięcia, są określane przez model przypisany do pinu wyjściowego w testowanej sieci. Modele pinów są przypisywane w ramach procesu przypisywania modeli do komponentu, a te przypisania na poziomie komponentu mogą zostać zachowane poprzez aktualizację schematu. Pojedynczy model pinu można także nadpisać, na przykład przez dwukrotne kliknięcie pinu w panelu Signal Integrity – zwróć uwagę, że takie ponowne przypisania na poziomie pinu nie są zachowywane pomiędzy sesjami edycji.

Adding SI Models Using the Signal Integrity Model Assignments Dialog

Najprostszym sposobem dodania modeli integralności sygnału do projektu jest użycie okna dialogowego Signal Integrity Model Assignments.

-

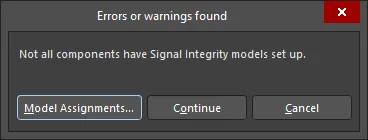

Wybierz Tools » Signal Integrity z menu. Jeśli dopiero zaczynasz pracę z integralnością sygnału w projekcie i są komponenty, które nie mają dołączonych modeli integralności sygnału, okno dialogowe Errors or warnings found poprosi o skonfigurowanie przypisań modeli za pomocą okna dialogowego Signal Integrity Model Assignments.

Okno dialogowe Errors or warnings found

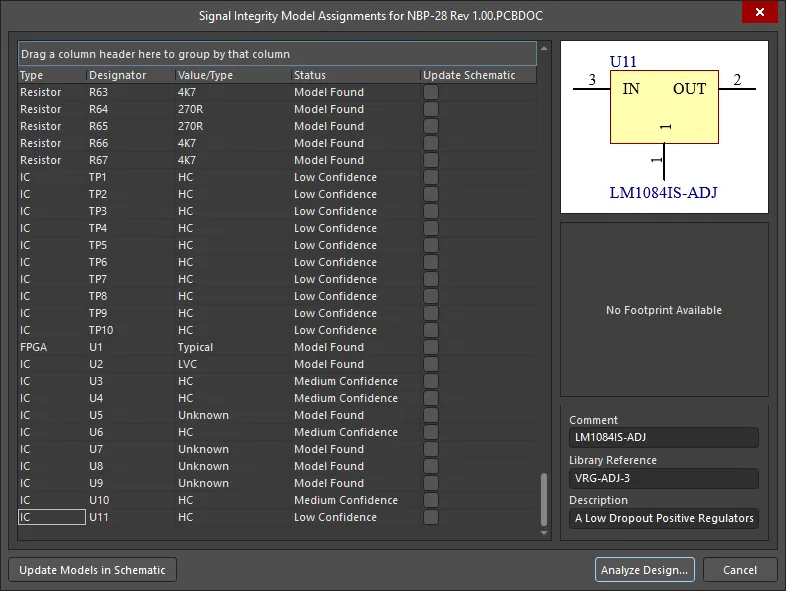

Okno dialogowe Signal Integrity Model Assignments

Alternatywnie, jeśli kliknięto Continue i panel Signal Integrity jest widoczny, można w dowolnym momencie wejść do okna dialogowego Signal Integrity Model Assignments, klikając przycisk Model Assignments w panelu. Zwróć uwagę, że spowoduje to wyczyszczenie i ponowne przeliczenie wszystkich wyników, ponieważ wszelkie zmiany w przypisaniach modeli unieważniają istniejące wyniki.

Jeśli modele zostały już skonfigurowane dla wszystkich komponentów, zostanie wyświetlone okno dialogowe SI Setup Options. Więcej informacji: Configuring the SI Setup Options .

-

Jeśli klikniesz Model Assignments w oknie dialogowym Errors or warnings found, zostanie wyświetlone okno dialogowe Signal Integrity Model Assignments.

Po uruchomieniu okno dialogowe Signal Integrity Models Assignment próbuje dokonać „wyedukowanych” przypuszczeń co do wymaganego modelu integralności sygnału dla każdego komponentu, który nie zawiera modelu integralności sygnału. Wszystkie komponenty, w tym te z już zdefiniowanymi modelami (oraz informacjami o modelu), będą wyświetlane w oknie dialogowym Signal Integrity Models Assignment . Każdemu komponentowi zostanie przypisany status opisany w poniższej tabeli.

| Status |

Definicja |

| No match |

Okno dialogowe Signal Integrity Model Assignments nie było w stanie znaleźć żadnych cech łączących ten komponent z określonym typem. Najprawdopodobniej będzie wymagał modyfikacji przez użytkownika, aby został poprawnie skonfigurowany. |

| Low confidence |

Okno dialogowe Signal Integrity Model Assignments wybrało typ dla tego komponentu, ale nie było mocnych przesłanek. |

| Medium confidence |

Okno dialogowe Signal Integrity Model Assignments wybrało typ dla tego komponentu i ma rozsądną pewność co do tego przypuszczenia. |

| High confidence |

Okno dialogowe Signal Integrity Model Assignments wybrało typ dla tego komponentu i pasuje on do większości cech zwykle kojarzonych z tym typem komponentu. |

| Model found |

Znaleziono istniejący model dla tego komponentu. |

| User modified |

Komponent zmieni status na ten, gdy użytkownik zmodyfikuje go względem początkowego przypuszczenia okna dialogowego Signal Integrity Model Assignments. |

| Model added |

Ten status jest używany, gdy użytkownik użył okna dialogowego Signal Integrity Model Assignments do zmodyfikowania dokumentu schematu w celu zapisania nowego modelu. |

Modifying Component Models using the Signal Integrity Model Assignments Dialog

-

Wybierz komponent, którego model chcesz zmodyfikować.

-

Wybierz poprawny typ. Dla Signal Integrity istnieje siedem typów komponentów – resistor, capacitor, inductor, diode, BJT, connector oraz IC. Typ każdego komponentu można wybrać z listy rozwijanej w kolumnie Type lub z menu pod prawym przyciskiem myszy.

-

Ustaw wartość dla rezystora, kondensatora lub indukcyjności. Jeśli to możliwe, okno dialogowe Signal Integrity Model Assignments spróbuje umieścić w tej kolumnie poprawną wartość komponentu na podstawie pola komentarza oraz parametrów komponentu. Jeśli wymaga to modyfikacji (lub wartość nie jest obecna), należy to zrobić na tym etapie. Szczególny przypadek tablic elementów (np. tablic rezystorów) jest obsługiwany w osobnym oknie dialogowym, dostępnym po kliknięciu w kolumnie (zob. Manually Adding Signal Integrity Models to Components po więcej szczegółów).

-

Jeśli komponent jest układem IC, wybór typu technologii jest istotny, ponieważ determinuje charakterystyki modeli pinów używanych w analizie. Można go wybrać z listy rozwijanej w kolumnie Value/Type lub z menu pod prawym przyciskiem myszy (Change Technology).

-

Na koniec może być konieczne podanie większej ilości szczegółów, niż pozwala na to okno dialogowe Signal Integrity Model Assignments, na przykład dla modeli IBIS. Można to zrobić, wybierając Advanced z menu pod prawym przyciskiem myszy. Więcej informacji o tym procesie: Manually Adding Signal Integrity Models to Components.

Zapisywanie modeli

Po wybraniu modeli dla dowolnych (lub wszystkich) komponentów dokumenty schematu można zaktualizować, aby trwale zapisać te informacje.

-

Zaznacz kolumnę Update Schematic w oknie dialogowym Signal Integrity Model Assignments dla wszystkich komponentów, które mają zostać zaktualizowane. Następnie kliknij przycisk Update Models in Schematic.

-

Wszystkie nowe modele Signal Integrity (lub zmodyfikowane istniejące) dla każdego wybranego komponentu zostaną dodane do dokumentów schematu. Dokumenty schematu będzie trzeba później zapisać.

Nie jest konieczne zapisywanie modeli, aby kontynuować proces analizy Signal Integrity. Jeśli modele nie zostaną zapisane, analiza zostanie przeprowadzona z wszystkimi modelami skonfigurowanymi tak, jak są aktualnie pokazane w oknie dialogowym Signal Integrity Model Assignments. Jednak przy następnym użyciu narzędzia Signal Integrity wszelkie zmiany zostaną utracone.

Manually Adding Signal Integrity Models to Components

Aby dodać model Signal Integrity do komponentu na schemacie:

-

Dla komponentu umieszczonego w edytorze schematu – wybierz komponent i otwórz panel Properties.

-

Dla komponentu edytowanego w edytorze symboli schematu – uaktywnij wymagany komponent, wybierając jego wpis w panelu SCH Library, i otwórz panel Properties.

Kliknij przycisk Add w obszarze Parameters panelu Properties i wybierz Signal Integrity. Zostanie otwarte okno dialogowe Signal Integrity Model.

Skonfiguruj model i kliknij OK.

Konfigurowanie elementów pasywnych

Podczas konfigurowania elementów takich jak rezystory i kondensatory zwykle wystarczy wprowadzić typ i wartość. Wartość można wprowadzić w polu Value i ustawić jako parametr dla całego komponentu.

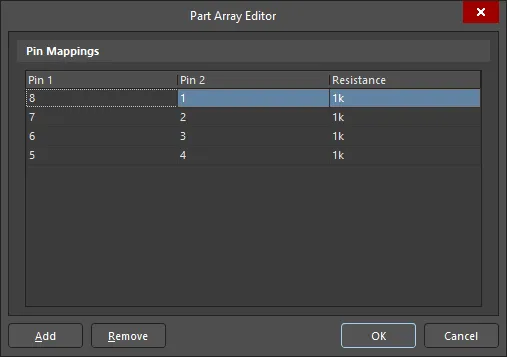

Obsługiwane są również komponenty takie jak tablice rezystorów. Można to osiągnąć, wybierając typ komponentu, a następnie klikając przycisk Setup Part Array w oknie dialogowym Signal Integrity Model. Okno dialogowe Part Array Editor umożliwia skonfigurowanie połączeń między pinami oraz wartości/modelu dla tych połączeń.

Okno dialogowe Part Array Editor

Konfigurowanie układu IC

Istnieje kilka alternatyw podczas konfigurowania modelu typu IC.

Importowanie plików IBIS

Inną ważną opcją jest możliwość importowania plików IBIS.

-

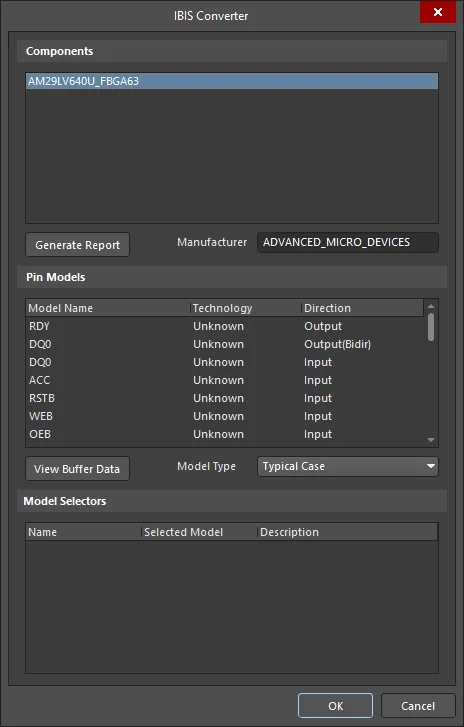

Aby użyć pliku IBIS (Input/Output Buffer Information) do określenia charakterystyk wejściowych i wyjściowych modelu układu scalonego, kliknij przycisk Import IBIS w oknie dialogowym Signal Integrity Model. Wybierz plik IBIS w oknie dialogowym Open IBIS File i kliknij Open. Zostanie wyświetlone okno dialogowe IBIS Converter.

Okno dialogowe IBIS Converter

-

Wybierz wymagany komponent zawarty w pliku IBIS. Altium Designer odczyta plik IBIS i zaimportuje modele pinów z pliku IBIS do biblioteki zainstalowanych modeli pinów. Jeśli zostanie znaleziony zduplikowany model, pojawi się pytanie, czy chcesz nadpisać istniejący model. Dodatkowo wszystkie piny komponentu otrzymają przypisany odpowiedni model pinu zgodnie z definicją w pliku IBIS.

-

Automatycznie zostanie wygenerowany raport informujący, które piny zostały przypisane pomyślnie, a które nie. Dalsza personalizacja jest możliwa poprzez ręczne wybranie modeli dla odpowiednich pinów, jak opisano powyżej.

-

Kliknij OK, aby zakończyć importowanie informacji IBIS i wrócić do okna dialogowego Signal Integrity Model.

Edycja modeli pinów

Można dodać lub edytować istniejący model pinu, określając różne charakterystyki elektryczne tego pinu. Zwróć uwagę, że jest to dostępne również dla innych typów, takich jak tranzystory BJT, złącza i diody.

-

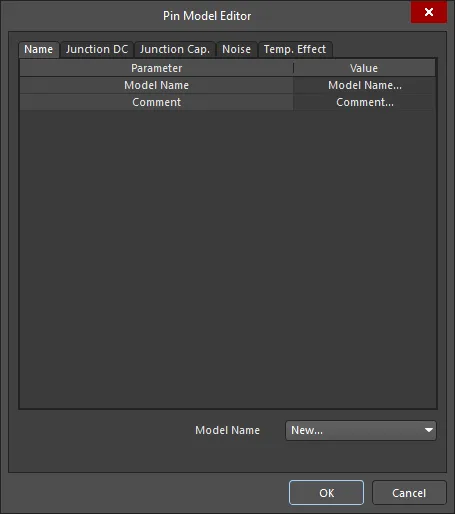

Aby modyfikować modele pinów, kliknij przycisk Add/Edit Model w oknie dialogowym Signal Integrity Model, jeśli ten przycisk jest dostępny dla danego typu. Zostanie wyświetlone okno dialogowe Pin Model Editor.

Okno dialogowe Pin Model Editor

-

Kliknij New na liście rozwijanej dla Model Name.

-

Wprowadź niezbędne zmiany i kliknij OK.

-

Jeśli jest to nowy model pinu, będzie on teraz dostępny do wyboru na pinach w tym (i innych) komponentach.

Praca z edytorem implementacji modelu IBIS

Aby wspierać narzędzia firm trzecich, które wymagają dedykowanych modeli IBIS do symulacji integralności sygnału i nie mogą używać własnego formatu modelu integralności sygnału Altium Designer (określanego jako SI Macro Models), Altium Designer zawiera dedykowany edytor implementacji modelu IBIS, umożliwiający dołączenie modelu IBIS do komponentu schematowego. Możesz więc:

-

Zaimportować modele pinów IBIS do pinów komponentu podczas analizy integralności sygnału (aby zostały zapisane jako Altium Designer SI Macro Models), jak opisano powyżej (zob. Importowanie plików IBIS), albo

-

Dołączyć model IBIS do komponentu schematowego, jak opisano poniżej.

Ta funkcja obsługuje wszystkie wersje specyfikacji modelu IBIS, do wersji 4.0 włącznie.

Aby dodać model IBIS do komponentu schematowego:

-

Dla wstawionego komponentu w edytorze schematu – wybierz komponent i otwórz panel Properties.

-

Dla komponentu edytowanego w edytorze symboli schematowych – uaktywnij wymagany komponent, wybierając jego wpis w panelu SCH Library, i otwórz panel Properties.

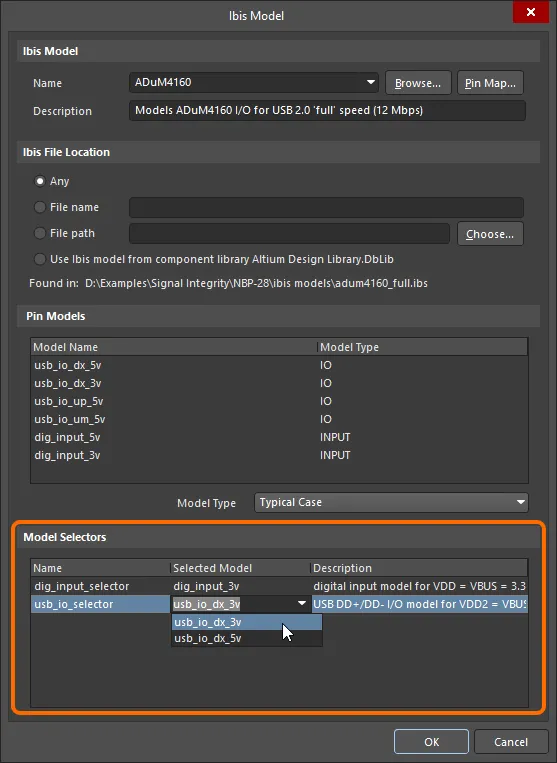

Kliknij przycisk Add w obszarze Parameters panelu Properties i wybierz Ibis Model. Zostanie otwarte okno dialogowe IBIS Model .

Dla komponentu schematowego można zdefiniować dowolną liczbę łączy modeli IBIS, ale w danym momencie aktywny może być tylko jeden model.

Model IBIS

Podaj nazwę modelu – dokładnie tak, jak występuje w pliku .ibs – oraz nadaj łączu modelu sensowną nazwę, być może opisującą, co reprezentuje implementacja w tej domenie.

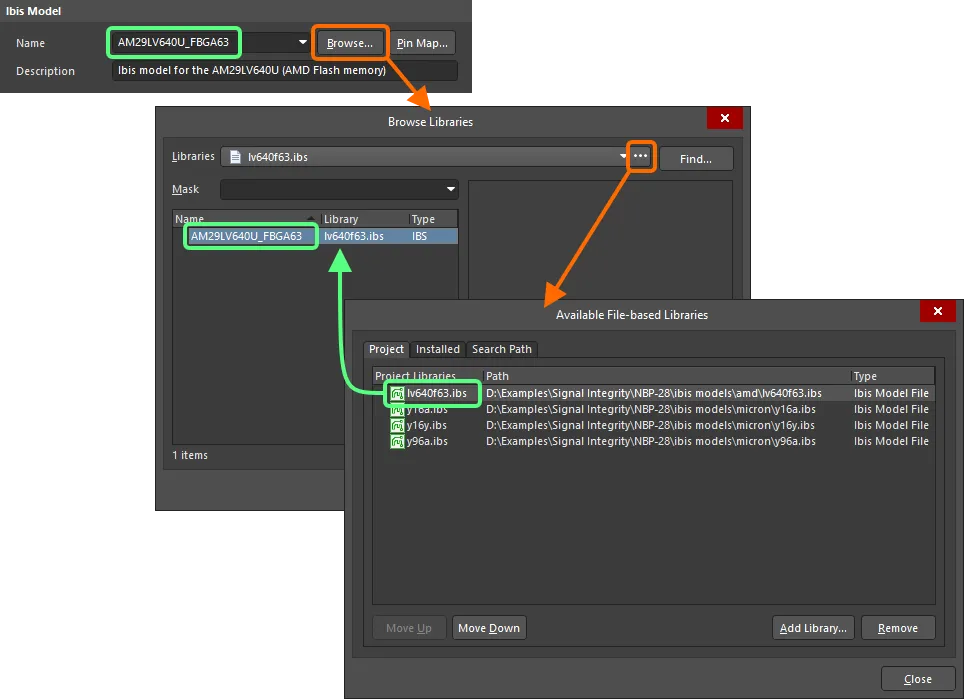

Alternatywnie, a zwłaszcza jeśli nie masz pewności co do nazwy, użyj przycisku Browse , aby uzyskać dostęp do okna dialogowego Browse Libraries . Użyj tego okna dialogowego, aby przeglądać pliki modeli IBIS we wszystkich aktualnie dostępnych bibliotekach. Skorzystaj z funkcji Find w tym oknie dialogowym, jeśli wymagane pliki modeli nie są częścią aktualnie dostępnych bibliotek.

Podaj nazwę modelu bezpośrednio lub wyszukaj ją.

Podczas przeglądania pliku IBIS lista rozwijana Name pokaże wszystkie modele, według nazwy, zdefiniowane w tym pliku. Po prostu wybierz wymagany.

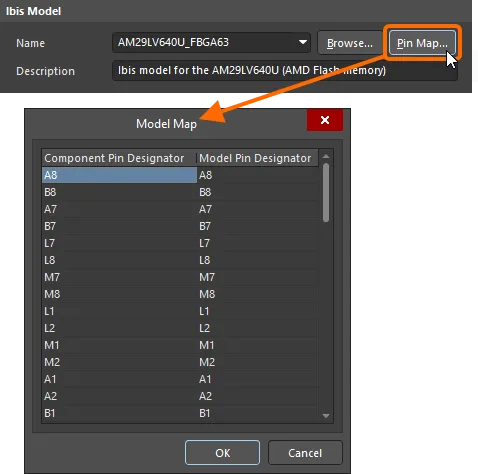

Mapowanie pinów komponentu schematowego na piny modelu IBIS jest definiowane w oknie dialogowym Model Map , do którego przechodzi się, klikając przycisk Pin Map .

Zweryfikuj mapowanie pinów komponentu do modelu w oknie dialogowym Model Map .

Lokalizacja pliku IBIS

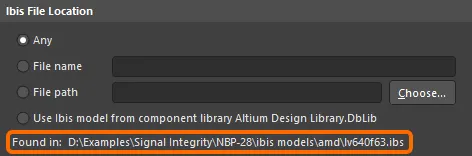

W tym obszarze okna dialogowego IBIS Model dostępne są opcje określające, w jaki sposób oprogramowanie ma zlokalizować model – pod warunkiem, że nazwa modelu jest zdefiniowana:

-

Any – do wyszukania modelu używane są wszystkie Available Libraries (biblioteki projektu, biblioteki zainstalowane oraz biblioteki znalezione wzdłuż zdefiniowanych ścieżek wyszukiwania).

-

File name – wprowadź pełną nazwę pliku, w którym znajduje się model (np.

lv640f63.ibs). Do wyszukania modelu używane są wszystkie Available Libraries. Jeśli nie zostanie tam znaleziony, zostanie sprawdzona domyślna ścieżka biblioteki (pole Library Path na stronie System – Default Locations okna dialogowego Preferences ), aby ustalić, czy wskazany plik można tam odnaleźć.

-

File path – wprowadź pełną ścieżkę/nazwę pliku. Kliknij przycisk Choose , aby przejść do pliku. Ta opcja zawsze znajdzie model, ponieważ jest jawna (oczywiście pod warunkiem, że plik pozostanie w tym katalogu!).

-

Integrated/Database Library – po umieszczeniu, jeśli komponent został wstawiony z biblioteki zintegrowanej lub bazy danych, model może zostać pobrany bezpośrednio z tej samej biblioteki, pod warunkiem że biblioteka należy do zestawu Available Libraries.

Jeśli model zostanie pomyślnie zlokalizowany, zostanie pokazana informacja, gdzie go znaleziono.

Określ, jak znaleźć model IBIS.

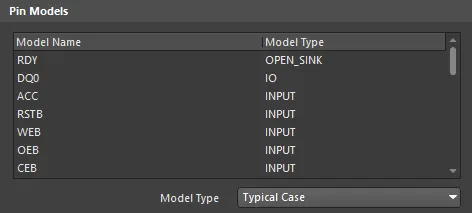

Modele pinów

Ten obszar okna dialogowego prezentuje listę tylko do odczytu modeli pinów zdefiniowanych dla wybranego modelu IBIS. Możesz jednak zmienić Model Type z domyślnego Typical Case na Strong Case lub Weak Case .

Modele pinów dla wybranego modelu IBIS.

Selektory modeli

Obszar Model Selectors okna dialogowego zostanie wypełniony, jeśli wybrany model IBIS zawiera selektory modeli. Pozwala to wybrać, którego modelu użyć (np. pin może mieć modele dla różnych poziomów napięcia: 3,3 V, 5 V itd.).

Przykładowy model IBIS ze zdefiniowanymi selektorami modeli.

Reguły projektowe integralności sygnału na schemacie

Reguły projektowe specyficzne dla PCB dotyczące integralności sygnału mogą być definiowane na schemacie, jeśli zostaną dodane jako parametry.

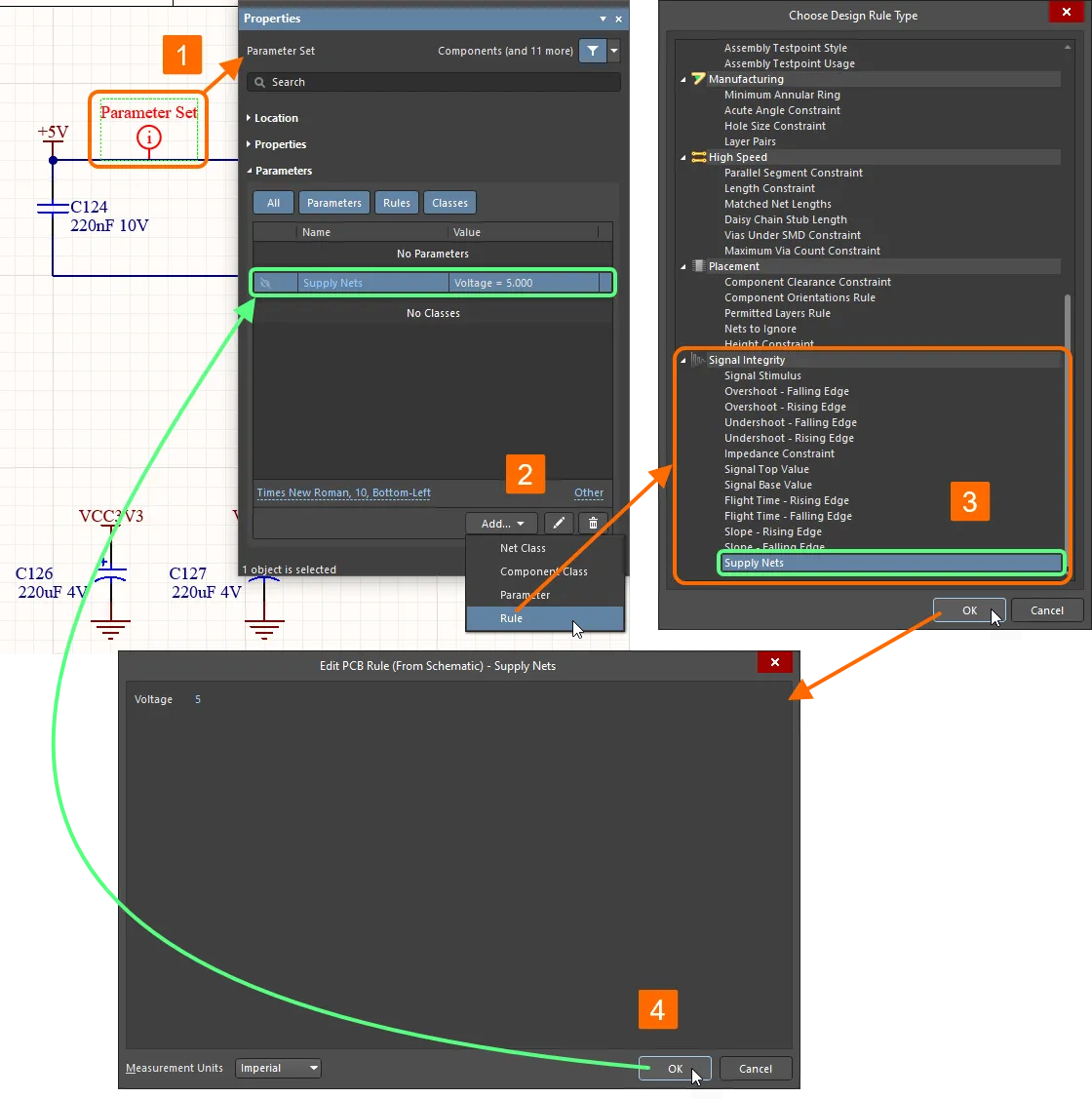

Reguła projektowa Supply Nets

Na potrzeby analizy integralności sygnału należy dodać regułę PCB identyfikującą sieci zasilania oraz ich napięcie, używając dyrektywy Parameter Set directive. Aby dodać regułę projektową supply nets na schemacie:

-

Umieść dyrektywę Parameter Set (Place » Directive » Parameter Set) na odpowiedniej sieci.

-

Gdy umieszczona dyrektywa jest zaznaczona, kliknij przycisk Add w obszarze Parameters panelu Properties i wybierz Rule z menu rozwijanego.

-

Zostanie otwarte okno dialogowe Choose Design Rule Type, w którym można wybrać typ reguły. Przewiń w dół do reguł Signal Integrity i wybierz Supply Nets, a następnie kliknij OK.

-

Zostanie wyświetlone okno dialogowe Edit PCB Rule (From Schematic) - Supply Nets. Wprowadź napięcie dla tej sieci zasilania i kliknij OK. Wpis reguły zostanie wyświetlony w panelu Properties.

Reguły projektowe integralności sygnału można dodawać bezpośrednio na schematach, używając dyrektyw Parameter Set.

Po przeniesieniu projektu do układu PCB reguła jest dodawana do reguł projektowych PCB (dostępnych do podglądu i edycji w PCB Editor w oknie dialogowym PCB Rules and Constraints Editor, otwieranym poleceniem Design » Rules).

Zwróć uwagę, że w edytorze schematów zakres reguły (zestaw obiektów, do których reguła będzie stosowana) jest definiowany przez miejsce dodania parametru, np. na przewodzie lub pinie. W PCB Editor zakres reguły jest definiowany w samej regule.

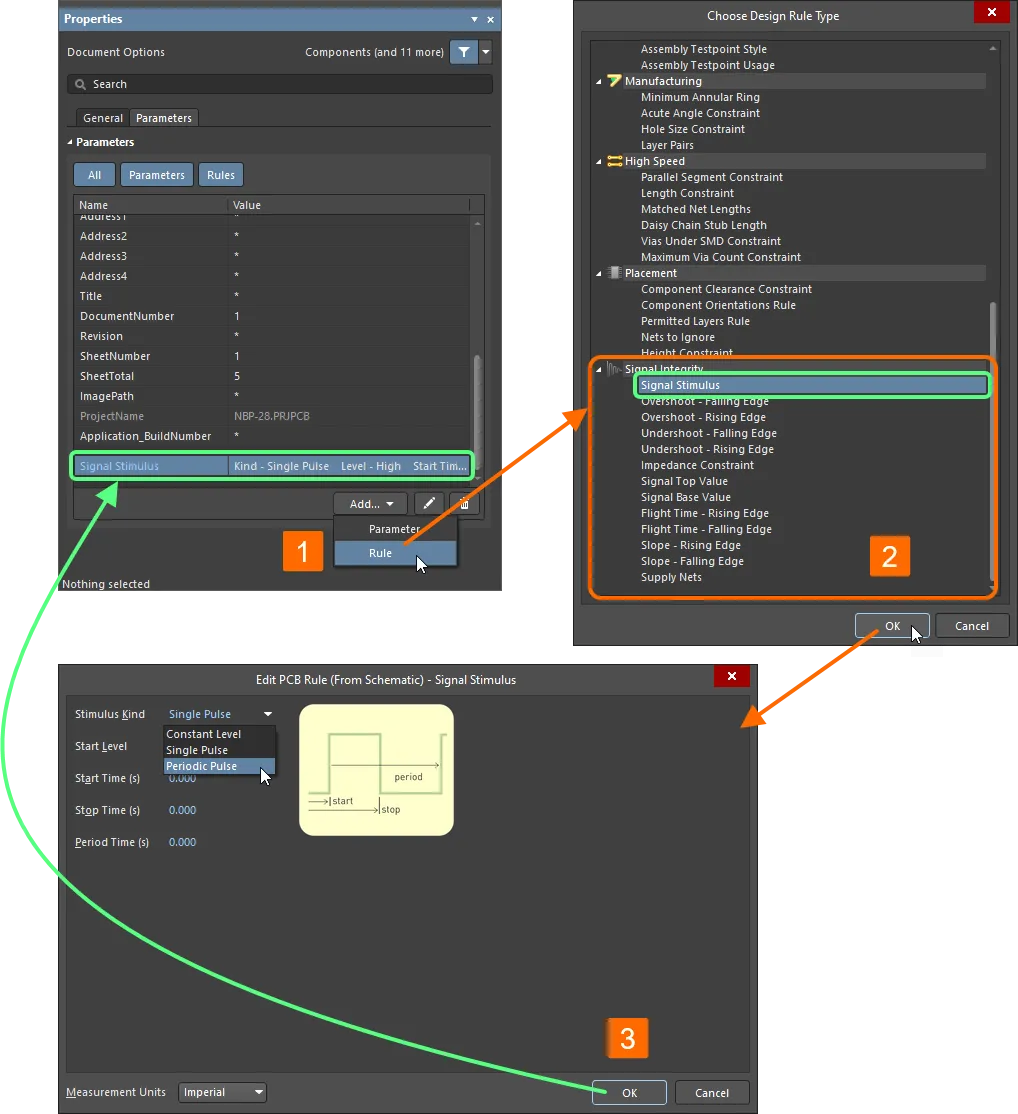

Reguła projektowa Signal Stimulus

Inną regułą projektową, którą można skonfigurować z poziomu edytora schematów, jest reguła Signal Stimulus. Po uruchomieniu tej reguły bodziec jest wstrzykiwany na każdym pinie wyjściowym w analizowanej sieci. Wymaga to reguły projektowej o zakresie „all”, więc musisz utworzyć parametr arkusza dla tej reguły. Jeśli nie skonfigurujesz tej reguły, zostaną użyte domyślne opcje reguły.

-

Gdy na arkuszu schematu nie jest zaznaczony żaden obiekt, otwórz panel Properties. Na karcie Parameters panelu kliknij przycisk Add i wybierz Rule z menu rozwijanego.

-

Otworzy się okno dialogowe Choose Design Rule Type, w którym można wybrać typ reguły. Przewiń w dół do reguł Signal Integrity i wybierz Supply Nets, a następnie kliknij OK.

-

Zostanie wyświetlone okno dialogowe Edit PCB Rule (From Schematic) - Signal Stimulus. Wybierz rodzaj bodźca, poziom początkowy oraz czasy, a następnie kliknij OK. Wpis reguły zostanie wyświetlony na liście w panelu Properties.

Regułę projektową Signal Integrity można dodać jako parametr arkusza schematu.

Reguły projektowe Signal Integrity w PCB

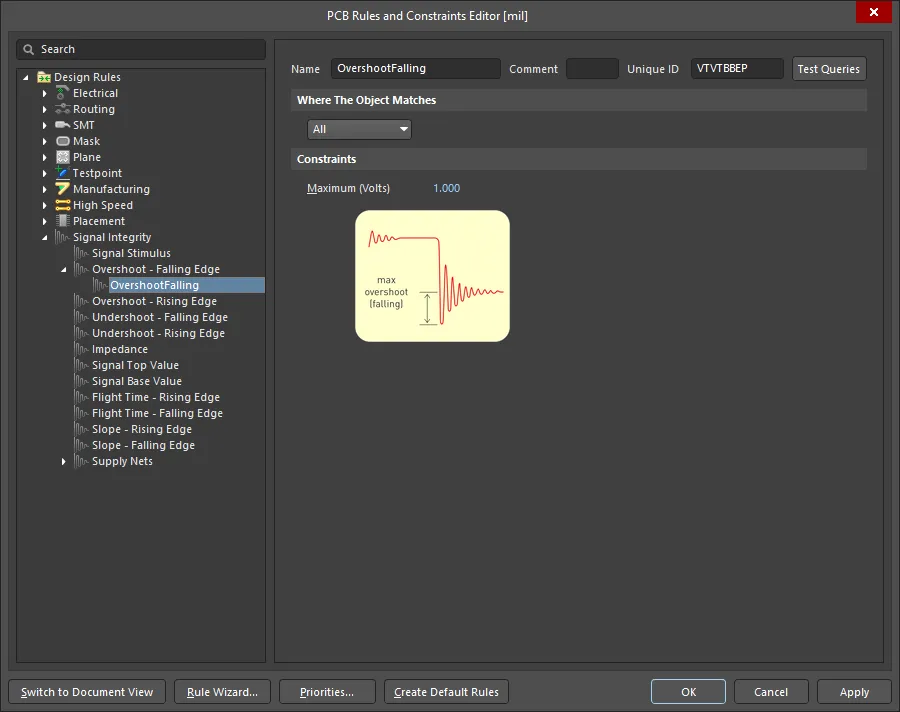

Parametry Signal Integrity, takie jak wymagania dotyczące przeregulowania (overshoot), niedoregulowania (undershoot), impedancji oraz nachylenia sygnału, można określić jako standardowe reguły projektowe PCB. Wybierz Design » Rules w PCB Editor, aby uzyskać dostęp do okna dialogowego PCB Rules and Constraints Editor, w którym można skonfigurować te reguły. Reguły te można również skonfigurować za pomocą parametrów w edytorze schematów i pojawią się one w oknie dialogowym PCB Rules and Constraint Editor po przeniesieniu projektu do układu PCB.

Okno dialogowe PCB Rules and Constraint Editor podczas przeglądania reguły projektowej Overshoot - Falling Edge

Reguły te mają dwa zastosowania. Pierwsze to uruchamianie standardowych kontroli DRC w PCB – płytkę można sprawdzić względem tych reguł za pomocą standardowej analizy przesiewowej. Drugie zastosowanie dotyczy panelu Signal Integrity. Reguły te można skonfigurować i włączyć jako testy, a panel będzie graficznie pokazywał, które sieci nie przeszły których testów.

Gdy projekt jest przygotowany, skonfiguruj i uruchom analizę integralności sygnału.