PDN Analyzer (by CST)

Rozszerzenie PDN Analyzer powered by CST® (Computer Simulation Technology) integruje się bezpośrednio z Altium Designer, umożliwiając symulację i analizę PI-DC dla bieżącego projektu PCB. Ponieważ PDN Analyzer działa wewnątrz Altium Designer, nie ma potrzeby ręcznego importu/eksportu danych, konwersji ani uruchamiania osobnych aplikacji – wystarczy uruchomić PDN Analyzer z edytora schematu lub PCB, ustawić wymagane parametry testu i uruchomić symulację. Wyniki są prezentowane głównie w postaci modelowania 2D/3D miedzi na płytce, co pozwala szybko ocenić rezultaty oraz przeprowadzać eksploracyjne testy typu „co jeśli” dla projektu układu PCB.

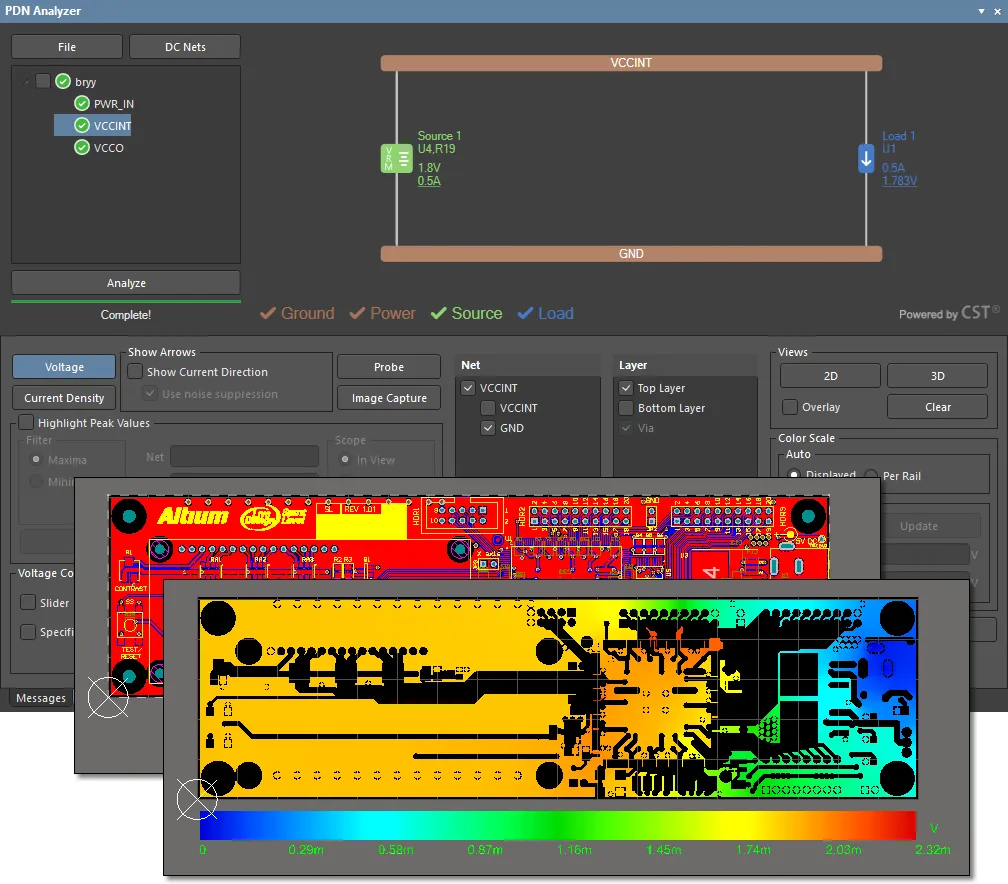

Interfejs PDN Analyzer pokazany na przykładzie PCB Altium Designer Spirit Level oraz wyniki symulacji spadku napięcia PI-DC dla powrotu sieci GND na warstwie Top dla zasilania VCCINT.

Uzyskiwanie dostępu do funkcji PDN Analyzer

Aby uzyskać dostęp do funkcji PDN Analyzer w Altium Designer, należy zainstalować rozszerzenie PDN Analyzer software extension . To rozszerzenie można instalować lub usuwać ręcznie.

Aby uzyskać więcej informacji o zarządzaniu rozszerzeniami, zapoznaj się z Extending Your Installation stroną (Altium Designer Develop, Altium Designer Agile, Altium Designer).

Aby uzyskać dostęp do funkcjonalności, musisz również posiadać ważną subskrypcję PDN Analyzer.

Podstawy Power Integrity

W istocie problem PI-DC (czyli „IR drop”) jest dość prosty: rezystancja zawarta w kształtach zasilania na płytce (ścieżki, poligony, pola, itp.) powoduje zużycie mocy i spadek napięcia, odbierając je poszczególnym obciążeniom. Jak można się spodziewać, problemy IR rosną na złożoności wraz z liczbą obciążeń na danym zasilaniu, poprzez wzajemne oddziaływanie w miedzianych ścieżkach zasilania i masy.

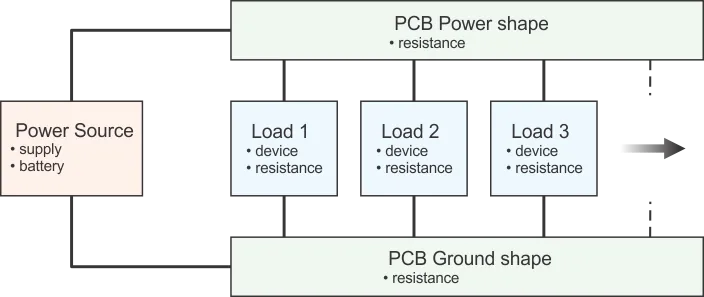

Rysunek 1: Podstawowy schemat blokowy kształtów zasilania i masy oraz przyłożonych obciążeń.

Rysunek 1 (powyżej) przedstawia prosty schemat blokowy źródła zasilania układu oraz jego kształtów zasilania i masy (ścieżek i pól), które dostarczają energię do różnych obciążeń (pamięci, mikrokontrolerów itp.). Zwróć uwagę, że wszystkie obciążenia są podłączone do tych samych kształtów zasilania i masy i polegają na nich, aby otrzymać swoje napięcie(a) pracy. Zwykle zakładamy, że te kształty zasilania i masy mają rezystancję 0Ω, co niekoniecznie jest prawdą, a takie założenie może powodować problemy. Ponieważ często występują stosunkowo duże prądy, nawet niewielkie rezystancje w kształtach zasilania i masy mogą powodować znaczące straty mocy i spadki napięcia.

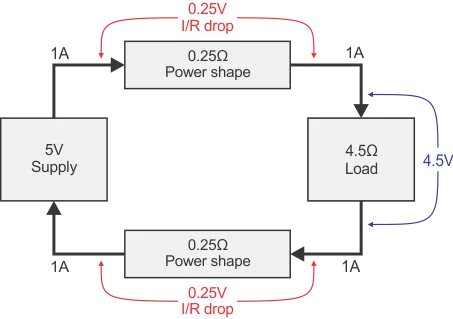

Rysunek 2: Efekty „IR Drop”

Rysunek 2 pokazuje przykład problemów, które mogą się pojawić, jeśli rezystancja kształtów zasilania i masy nie zostanie właściwie uwzględniona. Mimo że każdy kształt ma stosunkowo małą rezystancję wynoszącą tylko 0,25Ω, spowodowały one spadek napięcia na obciążeniu z 5V do 4,5V. Projektant musi być świadomy tego spadku i upewnić się, że można go zaakceptować, albo zmienić projekt, aby go zmniejszyć, tak by finalny projekt nie zawiódł w warunkach eksploatacji.

Problem wydaje się jednak łatwy do rozwiązania – wystarczy wykonać kształty zasilania i masy na tyle krótkie lub na tyle duże, aby reprezentowały pomijalną rezystancję, korzystając z następującej zależności: R = ρ * L/A, gdzie:

-

Rto całkowita rezystancja kształtu (ścieżki lub pola) -

ρto rezystywność materiału użytego dla kształtu (zwykle miedź,ρ ≈ 1.7µΩ-cm) -

Lto długość kształtu -

Ato pole przekroju poprzecznego kształtu (szerokośćxgrubość)

Mówiąc prosto: jeśli wykonasz kształty zasilania i masy jako krótkie, grube i szerokie, zminimalizujesz ich rezystancję.

Trudność polega jednak na tym, że zbyt duże kształty zajmują cenną przestrzeń trasowania i mogą ograniczać ilość miejsca dla innych kształtów napięć. Projekt z prawidłowo dobranymi kształtami zasilania i masy będzie bardziej kompaktowy i będzie wymagał mniejszej liczby warstw niż projekt, który arbitralnie stosuje zbyt duże pola lub ścieżki. Celem analizy PI-DC jest poinformowanie projektanta, że kształty zasilania i masy w projekcie płytki są wystarczające, ale nie przesadnie duże.

Kolejną kwestią związaną z IR drop jest fakt, że ilość zużytej mocy wynosi I2R – więc niewielki wzrost prądu płynącego przez rezystancję powoduje duży wzrost strat mocy. Może to objawiać się problemami termicznymi, gdy projekt znacząco się nagrzewa, ponieważ kształty zasilania i/lub masy nie są wystarczająco duże, aby przenieść przepływający przez nie prąd. Zapewnienie bardzo małego IR drop w kształtach zasilania i masy minimalizuje straty mocy w tych kształtach.

W skrajnym przypadku, jeśli kształt jest wystarczająco rezystywny (bardzo wąski i długi) i płynie przez niego odpowiednio duży prąd, taki kształt staje się w praktyce „bezpiecznikiem”, topiąc miedź i powodując awarię projektu – a potencjalnie także sytuację niebezpieczną. Norma IPC-2152 dotycząca obciążalności prądowej PCB odnosi się do tego zagadnienia, ale opiera się na pesymistycznych założeniach (np. brak pobliskiej, dobrze przewodzącej cieplnie miedzi, która pomaga odprowadzać ciepło), a projektanci często stosują tę specyfikację w najbardziej konserwatywny sposób, np. dopuszczając jedynie minimalny wzrost temperatury. Choć PI-DC nie może zastąpić normy IPC-2152 jako wytycznej dla zagadnień termicznych, może dostarczyć cennych informacji o tym, jak bezpiecznie zoptymalizować projekt, analizując spadki napięcia i gęstości prądu w systemie dystrybucji zasilania. Projekt zoptymalizowany pod kątem najniższej gęstości prądu i najmniejszego spadku napięcia między źródłami a wszystkimi obciążeniami będzie również generował mniej ciepła i będzie mniej narażony na problemy termiczne.

Kolejny aspekt, który obejmuje analiza PI-DC, to liczba przelotek używanych do dostarczania zasilania. Problem jest bardzo podobny do właściwego doboru rozmiarów miedzianych kształtów: jeśli przelotek jest za mało, napięcie jest tracone, a moc marnowana na skutek IR drop; jeśli przelotek jest za dużo, marnuje się cenną przestrzeń trasowania. W szczególności, jeśli dla danej ścieżki napięciowej użyje się zbyt wielu przelotek, przechodzą one przez kształty na innych warstwach i zmniejszają ich przekrój miedzi, powodując problemy dla tych innych napięć. Podobnie jak w przypadku prawidłowego wymiarowania kształtów, analiza napięcia w punktach obciążenia pozwala dobrać właściwy rozmiar i/lub liczbę przelotek.

Na koniec, istotną zaletą jest symulowanie finalnego projektu dokładnie tak, jak wygląda on fizycznie, aby upewnić się, że jest zoptymalizowany. Symulacja PI-DC stanowi końcową weryfikację, czy złącza i stabilizatory są dobrane właściwie, na wypadek gdyby w trakcie procesu projektowego dodano lub usunięto obciążenia.

W przypadku braku wiarygodnych danych o spadkach napięcia w różnych kształtach zasilania, kształtach masy i przelotkach na PCB, projektant jest zmuszony do zachowawczości, stosując nadmiernie duże pola, szerokości ścieżek i liczbę przelotek, co zużywa cenną przestrzeń projektową oraz zwiększa liczbę warstw i gabaryty projektu. Altium PDN Analyzer dostarcza dokładnych informacji o przydatności dystrybucji zasilania DC w projekcie w łatwy i bezpośredni sposób, umożliwiając projektantom tworzenie możliwie najbardziej efektywnych rozwiązań dystrybucji zasilania.

Wyniki nadają się nie tylko do końcowej weryfikacji projektu, ale mogą być również wykorzystane na etapie planowania, aby z wyprzedzeniem jak najefektywniej zaprojektować dostarczanie zasilania. PI-DC jest nieocenionym narzędziem w osiąganiu możliwie najbardziej wydajnej i odpornej sieci zasilania, a PDN Analyzer sprawia, że uruchomienie procesu symulacji i analizy jest proste, intuicyjne i efektywne.

Oprócz tych i innych zalet, które PDN Analyzer wnosi do Twoich projektów PCB, zapewnia on także następujące korzyści:

- Niezawodność produktu: Pomaga zapewnić prawidłowe działanie poszczególnych zasilaczy w projekcie pod względem ustalonych poziomów napięć, stabilności napięcia oraz nagrzewania/uszkodzeń ścieżek.

- Ulepszony układ PCB: Dostarcza informacji, które można wykorzystać do jak najefektywniejszego użycia przestrzeni płytki, oraz umożliwia łatwą identyfikację i korektę problematycznych obszarów o wysokiej gęstości prądu.

- Wiedza: Koniec z poleganiem na podejściu „na oko” lub przybliżonych obliczeniach przy rozważaniu prowadzenia ścieżek prądu stałego.

Symulacja PDN Analyzer

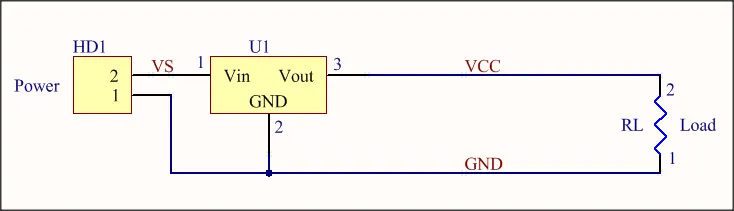

W swojej najbardziej podstawowej postaci układ płytki poddawany analizie PI-DC może składać się ze źródła w postaci stabilizatora napięcia i jego obciążenia, połączonych miedzianymi obszarami o różnych kształtach i szerokościach ścieżek.

Przykładowy obwód bazowy źródła zasilania i obciążenia.

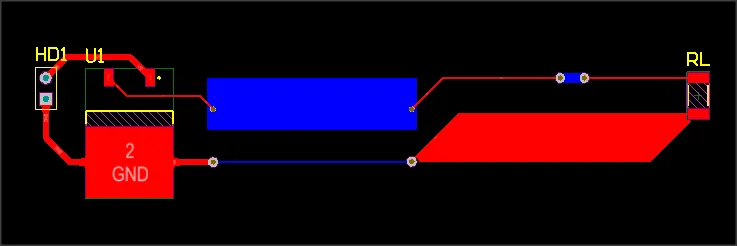

Układ PCB obwodu bazowego, z zakresem miedzianych kształtów i ścieżek połączonych warstwami i przelotkami.

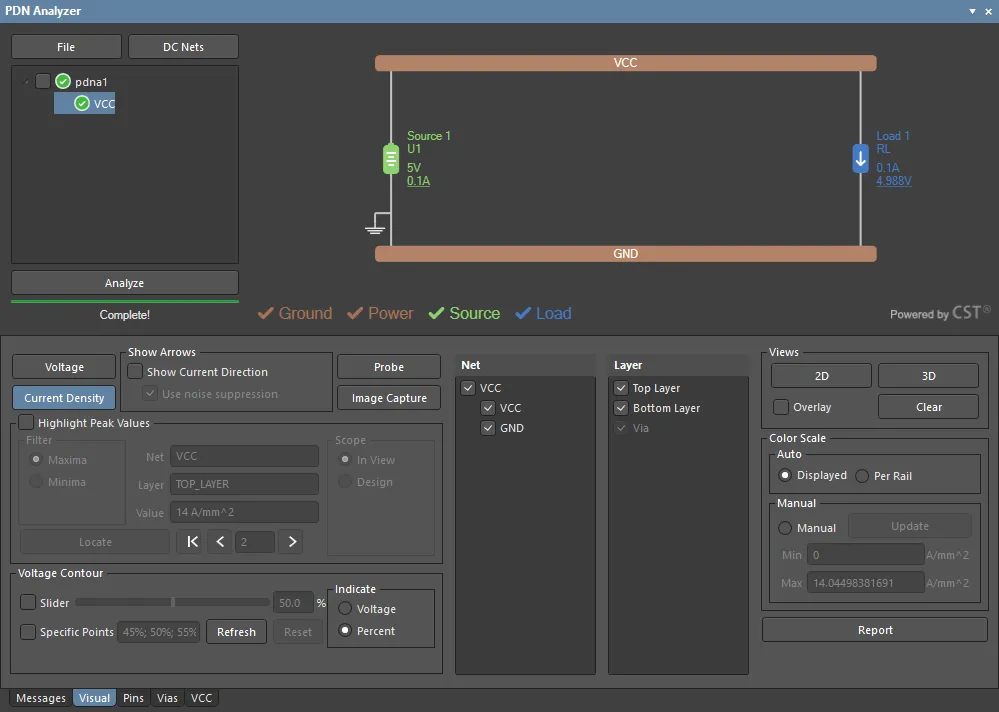

Interfejs panelu PDN Analyzer (Tools » PDN Analyzer) wizualnie odwzorowuje sieć obwodu od źródła zasilania do obciążenia, uwzględniając rzeczywiste ścieżki zasilania i masy – podobnie jak pokazano w powyższym obwodzie oraz w koncepcyjnym schemacie blokowym (Rys. 1). Aplikacja automatycznie wyodrębnia wszystkie informacje fizyczne i elektryczne (netlistę, elementy i kształty warstw itp.) z aktualnie aktywnego projektu PCB, co dostarcza danych dla silnika symulacji PI-DC.

Interfejs panelu PDN Analyzer pokazujący konfigurację symulacji PI dla obwodu bazowego i układu płytki.

Tutaj źródłem napięcia jest wyjście U1 (5V między wyprowadzeniami 3 i 2), a obciążeniem jest zadany prąd płynący przez RL (0,1A). Po wprowadzeniu parametrów początkowych w interfejsie (napięcia i prądy źródła/obciążenia itp.) i uruchomieniu symulacji, wynikowe dane analityczne są graficznie modelowane w edytorze PCB jako renderowany obraz 2D lub 3D.

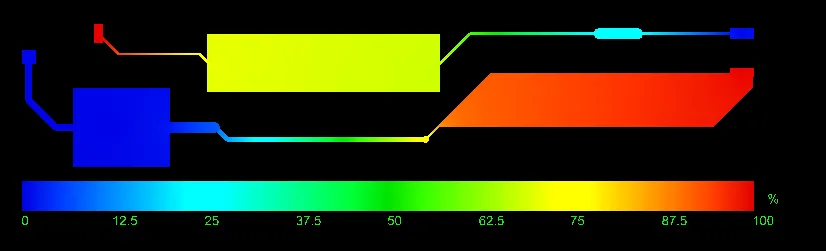

Wyniki symulacji spadku napięcia dla miedzi sieci PWR i GND na płytce (U1 do RL oraz RL do U1).

Wyniki symulacji spadku napięcia dla miedzi sieci PWR i GND na płytce (U1 do RL oraz RL do U1).

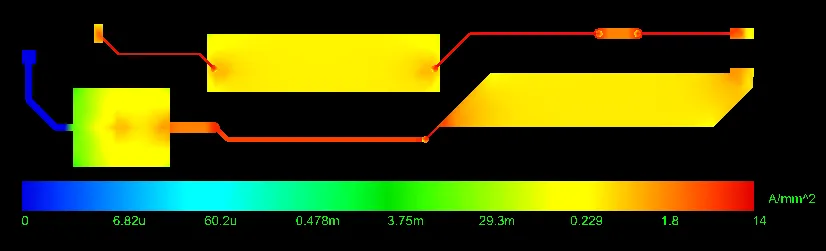

Symulację PI w PDN Analyzer można skonfigurować tak, aby wyświetlała wyniki dla Napięcia (spadek IR, obraz powyżej) lub Gęstości prądu (obraz poniżej) dla wszystkich odpowiednich warstw płytki.

Mapa gęstości prądu dla obu sieci PWR i GND (U1 do RL).

► Zobacz przewodnik z przykładem PDN Analyzer, aby uzyskać pełny opis korzystania z PDN Analyzer oraz interpretacji jego wyników.

Tłumaczenie SI

Tłumaczenie SI