Afin d’exécuter une analyse d’intégrité du signal réussie sur la conception et d’obtenir des résultats précis, les opérations suivantes doivent être effectuées avant de lancer l’analyse.

-

Bien que chaque net puisse être examiné afin de fournir des données sur le net et l’impédance, tous les nets ne peuvent pas être analysés du point de vue des caractéristiques d’intégrité du signal (tension et temporisation). Pour qu’un examen couvre correctement toutes les caractéristiques, un net doit contenir au moins un CI avec une broche de sortie et aucun autre composant. Les résistances, condensateurs et inductances, par exemple, ne fourniront pas à eux seuls de résultats de simulation en raison de l’absence de broche de sortie pouvant servir de source d’excitation. Il convient de noter que lorsque des nets bidirectionnels sont examinés, les deux sens sont simulés et le résultat du pire cas est affiché.

-

Le type de modèle Signal Integrity associé à chaque composant doit être correct. Cela s’effectue via la boîte de dialogue Signal Integrity Model Assignments ou en définissant manuellement l’entrée correcte pour le champ Type dans la boîte de dialogue Signal Integrity Model, lors de l’édition du modèle Signal Integrity associé au composant placé sur le document source schématique. Si cette entrée n’est pas définie, la boîte de dialogue Signal Integrity Model Assignments tentera de deviner le type du composant en fonction de ses caractéristiques. Si cette entrée n’est pas définie, le type Circuit intégré sera supposé. Pour plus d’informations, voir Adding SI Models Using the Signal Integrity Model Assignments Dialog.

-

Il doit exister des règles de conception Supply Nets. En général, il devrait y avoir au moins deux règles, une pour les nets d’alimentation et une pour les nets de masse. Leur portée peut être soit net, soit classe de nets. Les nets d’alimentation ne peuvent pas être analysés dans Signal Integrity. Pour plus d’informations, voir Signal Integrity Design Rules in Schematic ou Signal Integrity Design Rules in PCB.

-

Une règle de conception Signal Stimulus peut être définie. Vous n’avez besoin d’une règle de stimulus que si vous souhaitez remplacer le stimulus par défaut ; cela n’est donc généralement pas nécessaire.

-

L’empilement des couches du PCB doit être correctement configuré. L’analyseur Signal Integrity nécessite des plans d’alimentation continus. Les plans scindés ne sont pas pris en charge ; le net affecté au plan est donc utilisé. S’ils ne sont pas présents, ils sont supposés exister ; il est donc préférable de les ajouter et de les configurer correctement. L’épaisseur de toutes les couches, âmes et préimprégnés doit également être correctement définie pour la carte. Utilisez la commande Design » Layer Stack Manager pour configurer l’empilement des couches dans l’éditeur PCB. Lors de l’exécution de Signal Integrity en mode schématique uniquement, une carte par défaut à deux couches avec deux plans internes est utilisée. Vous pouvez créer un PCB vierge avec un empilement de couches configuré si un contrôle plus fin est nécessaire. Reportez-vous à la page Defining the Layer Stack pour en savoir plus.

Les caractéristiques d’un signal, telles que le niveau de tension, sont déterminées par le modèle affecté à la broche de sortie dans le net testé. Les modèles de broches sont affectés dans le cadre du processus d’affectation du modèle de composant, et ces affectations de modèles au niveau composant peuvent être conservées en mettant à jour le schéma. Un modèle de broche individuel peut également être remplacé, par exemple en double-cliquant sur une broche dans le panneau Signal Integrity – notez que ces réaffectations au niveau broche ne sont pas conservées entre les sessions d’édition.

Adding SI Models Using the Signal Integrity Model Assignments Dialog

La manière la plus simple d’ajouter des modèles d’intégrité du signal à votre conception consiste à utiliser la boîte de dialogue Signal Integrity Model Assignments.

-

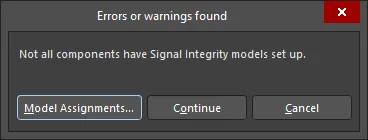

Sélectionnez Tools » Signal Integrity dans les menus. Si vous débutez tout juste avec l’intégrité du signal sur un projet et que certains composants n’ont pas de modèles d’intégrité du signal associés, la boîte de dialogue Errors or warnings found vous invitera à configurer les affectations de modèles à l’aide de la boîte de dialogue Signal Integrity Model Assignments.

La boîte de dialogue Errors or warnings found

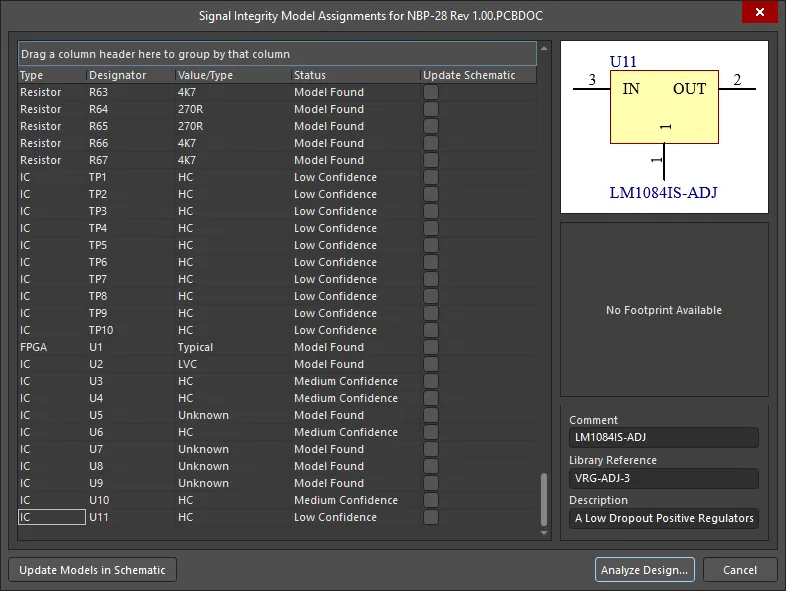

La boîte de dialogue Signal Integrity Model Assignments

Sinon, si vous avez cliqué sur Continue et que le panneau Signal Integrity est visible, vous pouvez accéder à tout moment à la boîte de dialogue Signal Integrity Model Assignments en cliquant sur le bouton Model Assignments dans le panneau. Notez que cela effacera tous les résultats et les recalculera, car toute modification des affectations de modèles invalide les résultats existants.

Si des modèles ont déjà été configurés pour tous les composants, la boîte de dialogue SI Setup Options s’affichera. Voir Configuring the SI Setup Options pour plus d’informations.

-

Si vous cliquez sur Model Assignments dans la boîte de dialogue Errors or warnings found, la boîte de dialogue Signal Integrity Model Assignments s’affiche.

Lorsqu’elle est exécutée, la boîte de dialogue Signal Integrity Models Assignment tente de faire des suppositions éclairées quant au modèle d’intégrité du signal nécessaire pour chaque composant ne contenant pas de modèle d’intégrité du signal. Tous les composants, y compris ceux pour lesquels des modèles sont déjà définis (ainsi que les informations de modèle), seront affichés dans la boîte de dialogue Signal Integrity Models Assignment . Un statut sera attribué à chaque composant, comme décrit dans le tableau suivant.

| Statut |

Définition |

| Aucune correspondance |

La boîte de dialogue Signal Integrity Model Assignments n’a trouvé aucune caractéristique reliant ce composant à un type particulier. Une modification par l’utilisateur sera probablement nécessaire pour le configurer correctement. |

| Faible confiance |

La boîte de dialogue Signal Integrity Model Assignments a sélectionné un type pour ce composant, mais les éléments probants étaient faibles. |

| Confiance moyenne |

La boîte de dialogue Signal Integrity Model Assignments a sélectionné un type pour ce composant et le niveau de confiance dans cette estimation est raisonnable. |

| Confiance élevée |

La boîte de dialogue Signal Integrity Model Assignments a sélectionné un type pour ce composant et celui-ci correspond à la plupart des caractéristiques généralement associées à ce type de composant. |

| Modèle trouvé |

Un modèle existant a été trouvé pour ce composant. |

| Modifié par l’utilisateur |

Un composant passe à ce statut dès que l’utilisateur l’a modifié par rapport à l’estimation initiale de la boîte de dialogue Signal Integrity Model Assignments. |

| Modèle ajouté |

Ce statut est utilisé lorsque l’utilisateur a utilisé la boîte de dialogue Signal Integrity Model Assignments pour modifier le document schématique afin d’enregistrer le nouveau modèle. |

Modifying Component Models using the Signal Integrity Model Assignments Dialog

-

Sélectionnez le composant dont vous souhaitez modifier le modèle.

-

Sélectionnez le type correct. Il existe sept types de composants pour Signal Integrity – résistance, condensateur, inductance, diode, BJT, connecteur et CI. Le type de chaque composant peut être sélectionné via une liste déroulante dans la colonne Type ou via le menu contextuel.

-

Définissez la valeur d’une résistance, d’un condensateur ou d’une inductance. Si possible, la boîte de dialogue Signal Integrity Model Assignments tentera de placer la valeur correcte du composant dans cette colonne en se basant sur le champ de commentaire et les paramètres du composant. Si cela nécessite une modification (ou si la valeur n’est pas présente), cela doit être fait à ce stade. Le cas particulier des réseaux de composants (tels que les réseaux de résistances) est traité via une boîte de dialogue distincte accessible en cliquant dans la colonne (voir Manually Adding Signal Integrity Models to Components pour plus de détails).

-

Si le composant est un CI, le choix du type de technologie est important, car il déterminera les caractéristiques des modèles de broches utilisés dans l’analyse. Cela peut être sélectionné via la liste déroulante de la colonne Value/Type ou via le menu contextuel (Change Technology).

-

Enfin, il peut être nécessaire de spécifier davantage de détails que ce que permet la boîte de dialogue Signal Integrity Model Assignments, comme pour les modèles IBIS. Cela peut être réalisé en sélectionnant Advanced dans le menu contextuel. Voir Manually Adding Signal Integrity Models to Components pour plus de détails sur ce processus.

Enregistrement des modèles

Une fois les modèles choisis pour tout ou partie des composants, les documents schématiques peuvent être mis à jour afin de stocker ces informations de manière permanente.

-

Cochez la colonne Update Schematic dans la boîte de dialogue Signal Integrity Model Assignments pour tous les composants à mettre à jour. Cliquez ensuite sur le bouton Update Models in Schematic.

-

Tous les nouveaux modèles Signal Integrity (ou les modèles existants modifiés) pour chaque composant sélectionné seront ajoutés aux documents schématiques. Les documents schématiques devront être enregistrés ultérieurement.

Il n’est pas nécessaire d’enregistrer les modèles pour poursuivre le processus d’analyse Signal Integrity. Si les modèles ne sont pas enregistrés, l’analyse se poursuivra avec tous les modèles configurés tels qu’ils sont actuellement affichés dans la boîte de dialogue Signal Integrity Model Assignments. Toutefois, lors de la prochaine utilisation de l’outil Signal Integrity, toutes les modifications auront été perdues.

Ajout manuel de modèles Signal Integrity aux composants

Pour ajouter un modèle Signal Integrity à un composant schématique :

-

Pour un composant placé dans l’éditeur de schéma – sélectionnez le composant et ouvrez le panneau Properties.

-

Pour un composant en cours d’édition dans l’éditeur de symboles schématiques – activez le composant requis en sélectionnant son entrée dans le panneau SCH Library et ouvrez le panneau Properties.

Cliquez sur le bouton Add dans la zone Parameters du panneau Properties et sélectionnez Signal Integrity. La boîte de dialogue Signal Integrity Model s’ouvrira.

Configurez votre modèle et cliquez sur OK.

Configuration des composants passifs

Lors de la configuration de composants tels que les résistances et les condensateurs, il suffit généralement de saisir un type et une valeur. La valeur peut être saisie dans le champ Value et définie comme paramètre pour l’ensemble du composant.

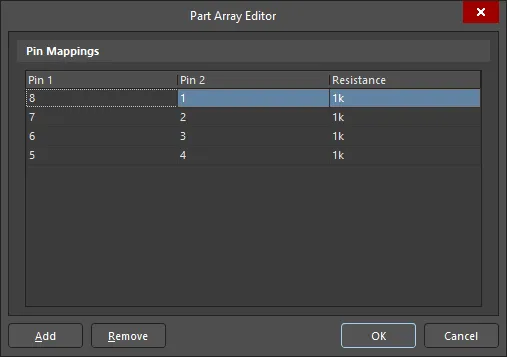

La prise en charge de composants tels que les réseaux de résistances est également disponible. Pour cela, après avoir sélectionné le type de composant, cliquez sur le bouton Setup Part Array dans la boîte de dialogue Signal Integrity Model. La boîte de dialogue Part Array Editor permet de configurer les connexions entre les broches ainsi que la valeur/le modèle de ces connexions.

La boîte de dialogue Part Array Editor

Configuration d’un CI

Il existe plusieurs possibilités lors de la configuration d’un modèle de type CI.

-

Après avoir sélectionné le type (CI), il suffit de sélectionner un type de technologie. Cela garantit que, lors de la simulation de ce composant, les modèles de broches appropriés à cette technologie seront utilisés. La liste complète des technologies disponibles figure dans la section repliable ci-dessous.

Types de technologies disponibles

| Type de technologie |

Description |

| ABT |

Technologie CMOS bipolaire avancée |

| AC |

CMOS avancé |

| ACT |

CMOS avancé avec entrées TTL |

| AHC |

CMOS avancé haute vitesse |

| AHC_50 |

CMOS avancé haute vitesse 5,0 V |

| AHCT |

CMOS avancé haute vitesse avec entrées TTL |

| AHCT_50 |

CMOS avancé haute vitesse 5,0 V avec entrées TTL |

| ALS |

Schottky avancé basse consommation |

| ALVC |

CMOS avancé basse tension |

| AS |

Schottky avancé |

| BCT |

Technologie CMOS bipolaire |

| BTL |

Logique de transceiver de fond de panier/Futurebus+ |

| CMOS |

CMOS |

| F |

FAST |

| FCT |

Technologie CMOS FAST |

| GTL |

Logique de transceiver Gunning |

| GTL_LVT |

Logique de transceiver Gunning basse tension |

| HC |

CMOS haute vitesse |

| HCT |

CMOS haute vitesse avec entrées TTL |

| HLL |

CMOS haute vitesse basse consommation basse tension |

| LS |

Schottky basse consommation |

| LV |

CMOS haute vitesse basse tension |

| LVC |

CMOS basse tension |

| LVT |

Technologie BiCMOS basse tension |

| S |

Schottky |

| STD_TTL |

TTL standard |

| TTL |

TTL |

-

Si un contrôle plus fin est nécessaire, il est possible d’assigner des technologies spécifiques ou des modèles de broche à des broches individuelles. Cela peut être fait en sélectionnant dans les listes déroulantes des broches de la liste des broches au bas de la boîte de dialogue Signal Integrity Model. Notez que toute modification effectuée ici remplacera la technologie de base du composant.

Importation de fichiers IBIS

Une autre option importante est la possibilité d’importer des fichiers IBIS.

-

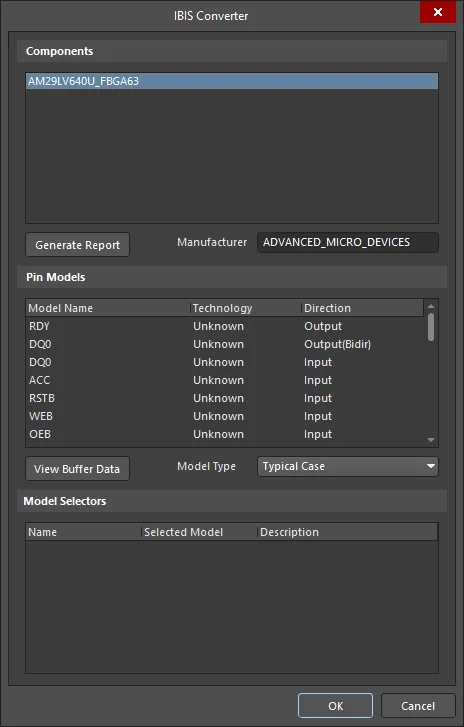

Pour utiliser un fichier IBIS (Input/Output Buffer Information) afin de spécifier les caractéristiques d’entrée et de sortie d’un modèle de CI, cliquez sur le bouton Import IBIS dans la boîte de dialogue Signal Integrity Model. Sélectionnez le fichier IBIS dans la boîte de dialogue Open IBIS File et cliquez sur Open. La boîte de dialogue IBIS Converter s’affiche.

La boîte de dialogue IBIS Converter

-

Sélectionnez le composant requis contenu dans le fichier IBIS. Altium Designer lira le fichier IBIS et importera les modèles de broche du fichier IBIS dans la bibliothèque des modèles de broche installés. Si un modèle en double est trouvé, il vous sera demandé si vous souhaitez remplacer le modèle existant. De plus, toutes les broches du composant se verront attribuer le modèle de broche approprié tel que spécifié dans le fichier IBIS.

-

Un rapport sera automatiquement généré indiquant quelles broches ont été assignées avec succès et lesquelles ne l’ont pas été. Une personnalisation supplémentaire est possible en sélectionnant manuellement les modèles pour les broches appropriées comme décrit ci-dessus.

-

Cliquez sur OK pour terminer l’importation des informations IBIS et revenir à la boîte de dialogue Signal Integrity Model.

Modification des modèles de broche

Il est possible d’ajouter ou de modifier un modèle de broche existant en spécifiant diverses caractéristiques électriques de cette broche. Notez que cela est également disponible pour d’autres types tels que les BJT, les connecteurs et les diodes.

-

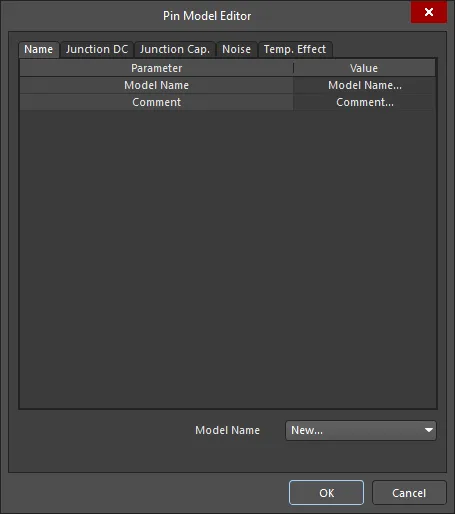

Pour modifier les modèles de broche, cliquez sur le bouton Add/Edit Model dans la boîte de dialogue Signal Integrity Model si ce bouton est disponible pour ce type. La boîte de dialogue Pin Model Editor s’affiche.

La boîte de dialogue Pin Model Editor

-

Cliquez sur New dans la liste déroulante de Model Name.

-

Effectuez les modifications nécessaires et cliquez sur OK.

-

S’il s’agit d’un nouveau modèle de broche, ce modèle sera désormais disponible pour être sélectionné sur les broches de ce composant (et d’autres composants).

Utilisation de l’éditeur d’implémentation de modèle IBIS

Pour prendre en charge les outils tiers qui nécessitent des modèles IBIS dédiés pour leurs simulations d’intégrité du signal et ne peuvent pas utiliser le propre format de modèle d’intégrité du signal d’Altium Designer (appelé SI Macro Models), Altium Designer intègre un éditeur dédié d’implémentation de modèle IBIS, permettant d’attacher le modèle IBIS au composant schématique. Vous pouvez donc soit :

-

Importer les modèles de broche IBIS dans les broches du composant pendant l’analyse d’intégrité du signal (pour qu’ils soient stockés en tant que SI Macro Models d’Altium Designer) comme décrit ci-dessus (voir Importation de fichiers IBIS), ou

-

Attacher le modèle IBIS au composant schématique, comme décrit ci-dessous.

Cette fonctionnalité prend en charge toutes les versions de la spécification de modèle IBIS, jusqu’à la version 4.0 incluse.

Pour ajouter un modèle IBIS à un composant schématique :

-

Pour un composant placé dans l’éditeur de schéma – sélectionnez le composant et ouvrez le panneau Properties.

-

Pour un composant en cours de modification dans l’éditeur de symbole schématique – activez le composant requis en sélectionnant son entrée dans le panneau SCH Library et ouvrez le panneau Properties.

Cliquez sur le bouton Add dans la région Parameters du panneau Properties et sélectionnez Ibis Model. La boîte de dialogue IBIS Model s’ouvrira.

Un nombre quelconque de liens de modèle IBIS peut être défini pour un composant schématique, mais un seul peut être le modèle actif à un instant donné.

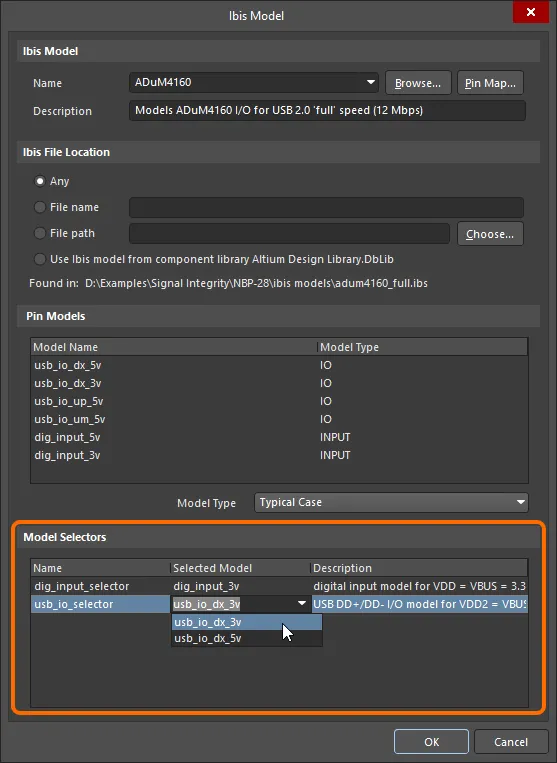

Modèle IBIS

Spécifiez le nom du modèle – exactement tel qu’il apparaît dans le fichier .ibs – et donnez au lien de modèle un nom explicite, décrivant peut-être ce que représente l’implémentation dans ce domaine.

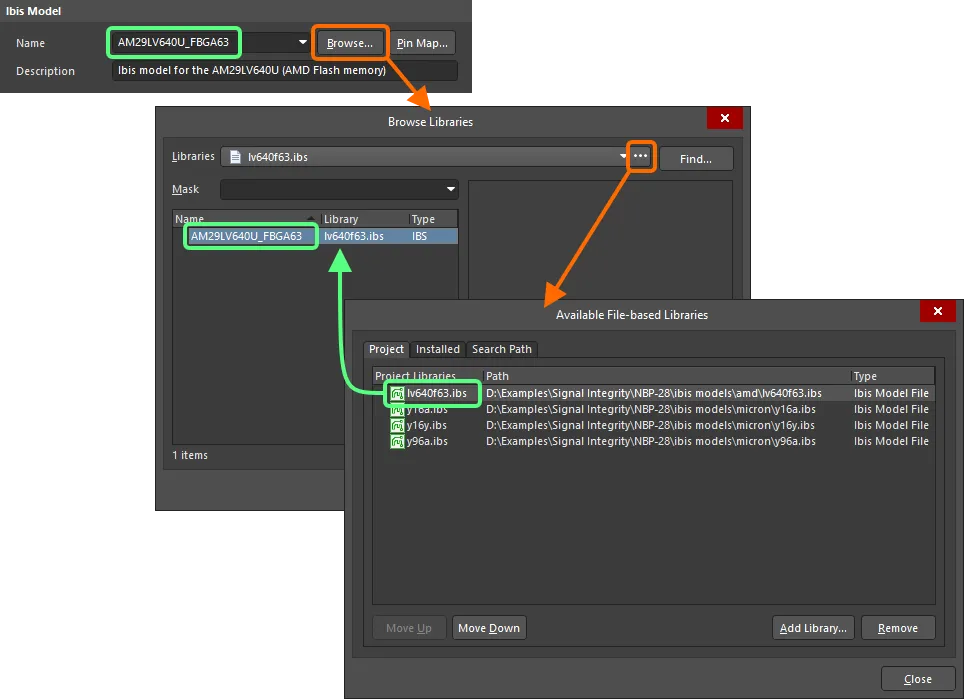

Sinon, et surtout si vous n’êtes pas sûr du nom, utilisez le bouton Browse pour accéder à la boîte de dialogue Browse Libraries . Utilisez cette boîte de dialogue pour parcourir les fichiers de modèle IBIS dans toutes les bibliothèques disponibles. Utilisez la fonctionnalité Find de cette boîte de dialogue si les fichiers de modèle requis ne font pas partie des bibliothèques actuellement disponibles.

Spécifiez directement le nom du modèle ou recherchez-le.

Lors de la recherche d’un fichier IBIS, la liste déroulante Nom présentera tous les modèles, par nom, définis dans ce fichier. Sélectionnez simplement celui requis.

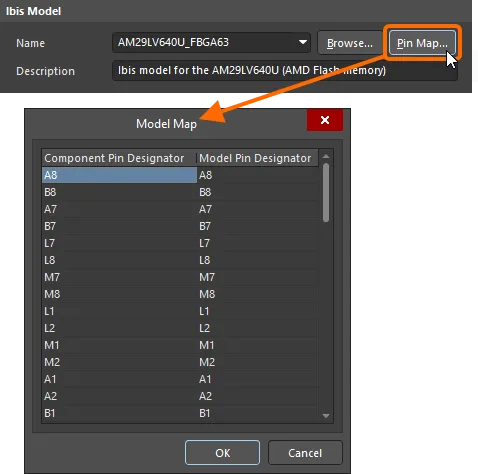

Le mappage des broches du composant schématique vers les broches du modèle IBIS est défini dans la boîte de dialogue Model Map , accessible en cliquant sur le bouton Pin Map .

Vérifiez le mappage des broches composant-modèle dans la boîte de dialogue Model Map .

Emplacement du fichier IBIS

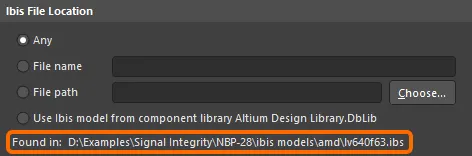

Des options sont disponibles dans cette région de la boîte de dialogue IBIS Model pour spécifier comment le logiciel doit localiser le modèle – à condition que le nom du modèle soit défini :

-

Any – toutes les bibliothèques disponibles (bibliothèques de projet, bibliothèques installées et bibliothèques trouvées le long des chemins de recherche définis) sont utilisées pour rechercher le modèle.

-

File name – saisissez le nom complet du fichier dans lequel réside le modèle (par ex.,

lv640f63.ibs). Toutes les bibliothèques disponibles sont utilisées pour rechercher le modèle. S’il n’est pas trouvé ici, le chemin de bibliothèque par défaut (le champ Library Path sur la page System – Default Locations de la boîte de dialogue Preferences ) sera interrogé pour voir si le fichier nommé peut y être trouvé.

-

File path – saisissez le chemin/nom complet du fichier. Cliquez sur le bouton Choose pour rechercher le fichier. Cette option trouvera toujours le modèle, puisqu’elle est explicite (à condition bien sûr que le fichier reste dans ce répertoire !).

-

Integrated/Database Library – après placement, si le composant est placé à partir d’une bibliothèque intégrée ou d’une base de données, le modèle peut être obtenu directement à partir de cette même bibliothèque, à condition que la bibliothèque fasse partie de l’ensemble des bibliothèques disponibles.

Si le modèle est localisé avec succès, une indication de l’endroit où il a été trouvé sera présentée.

Spécifiez comment trouver le modèle IBIS.

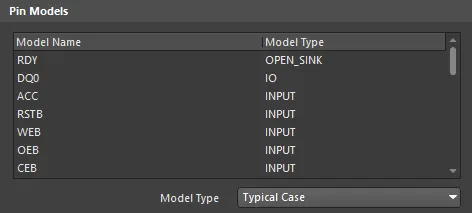

Modèles de broche

Cette région de la boîte de dialogue présente une liste en lecture seule des modèles de broche définis pour le modèle IBIS choisi. Vous pouvez toutefois modifier le Model Type de la valeur par défaut Typical Case, vers Strong Case ou Weak Case respectivement.

Modèles de broche pour le modèle IBIS choisi.

Sélecteurs de modèle

La région Model Selectors de la boîte de dialogue sera renseignée si le modèle IBIS choisi contient des sélecteurs de modèle. Cela vous permet de choisir quel modèle utiliser (par ex., une broche peut avoir des modèles pour différents niveaux de tension : 3,3 V, 5 V, etc.).

Exemple de modèle IBIS avec sélecteurs de modèle définis.

Règles de conception d’intégrité du signal dans le schéma

Des règles de conception spécifiques au PCB pour l’intégrité du signal peuvent être définies dans le schéma si elles sont ajoutées en tant que paramètres.

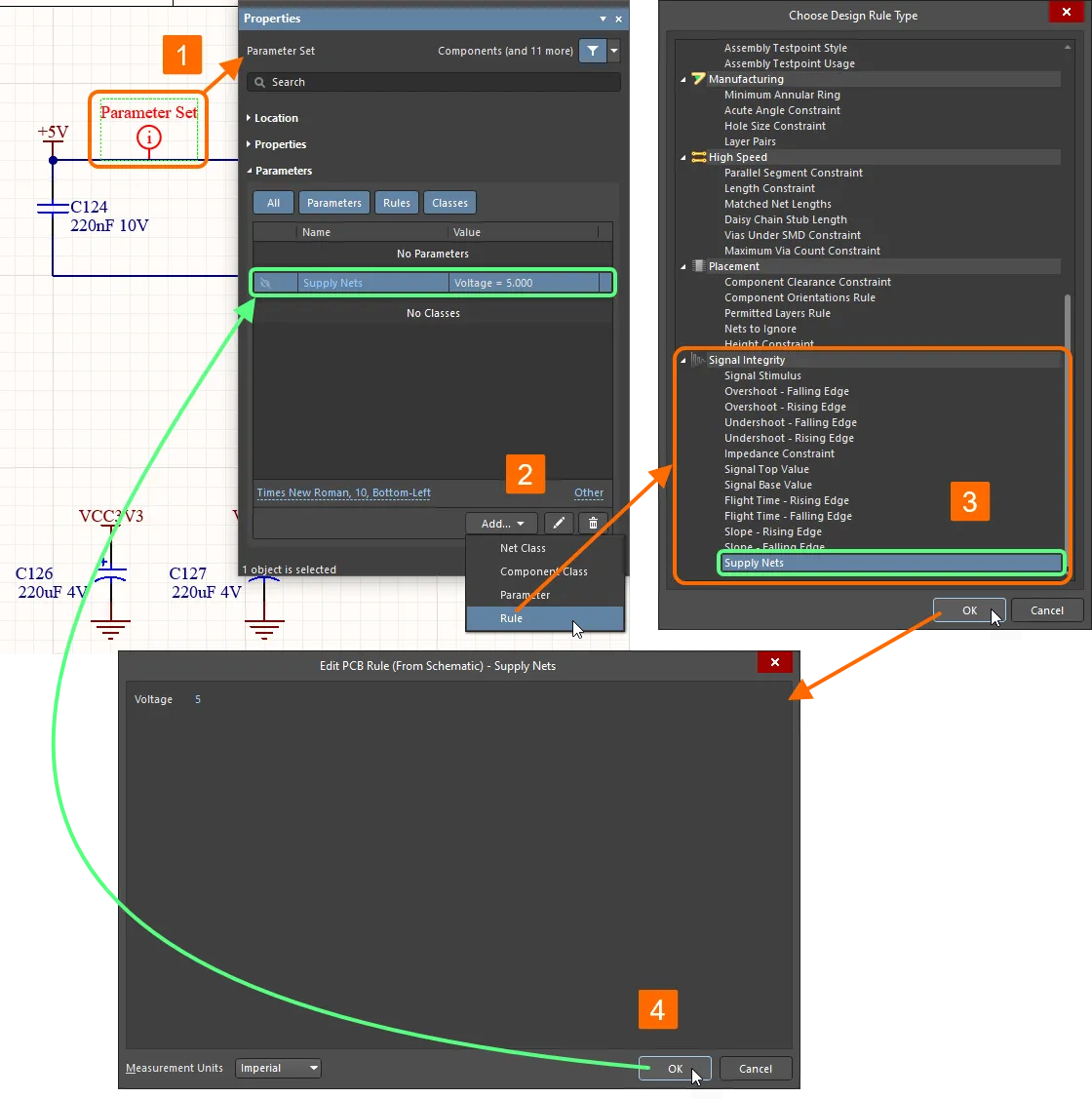

Règle de conception des réseaux d’alimentation

Pour l’analyse d’intégrité du signal, une règle PCB doit être ajoutée pour identifier les réseaux d’alimentation et leur tension à l’aide de la directive Parameter Set. Pour ajouter la règle de conception des réseaux d’alimentation dans le schéma :

-

Placez la directive Parameter Set (Place » Directive » Parameter Set) sur le réseau approprié.

-

Lorsque la directive placée est sélectionnée, cliquez sur le bouton Add dans la région Parameters du panneau Properties et sélectionnez Rule dans le menu déroulant.

-

La boîte de dialogue Choose Design Rule Type s’ouvrira, où le type de règle peut être choisi. Faites défiler jusqu’aux règles Signal Integrity et sélectionnez Supply Nets puis cliquez sur OK.

-

La boîte de dialogue Edit PCB Rule (From Schematic) - Supply Nets s’affiche. Saisissez la tension pour ce réseau d’alimentation et cliquez sur OK. L’entrée de règle sera listée dans le panneau Properties.

Les règles de conception d’intégrité du signal peuvent être ajoutées directement dans les schémas à l’aide des directives Parameter Set.

Après le transfert de la conception vers le routage PCB, la règle est ajoutée aux règles de conception du PCB (consultables et modifiables dans l’éditeur PCB à partir de la boîte de dialogue PCB Rules and Constraints Editor, accessible à l’aide de la commande Design » Rules).

Notez que, dans l’éditeur de schéma, la portée de la règle (l’ensemble des objets ciblés par la règle) est définie par l’endroit où le paramètre est ajouté, par exemple sur un fil ou une broche. Dans l’éditeur PCB, la portée d’une règle est définie dans la règle elle-même.

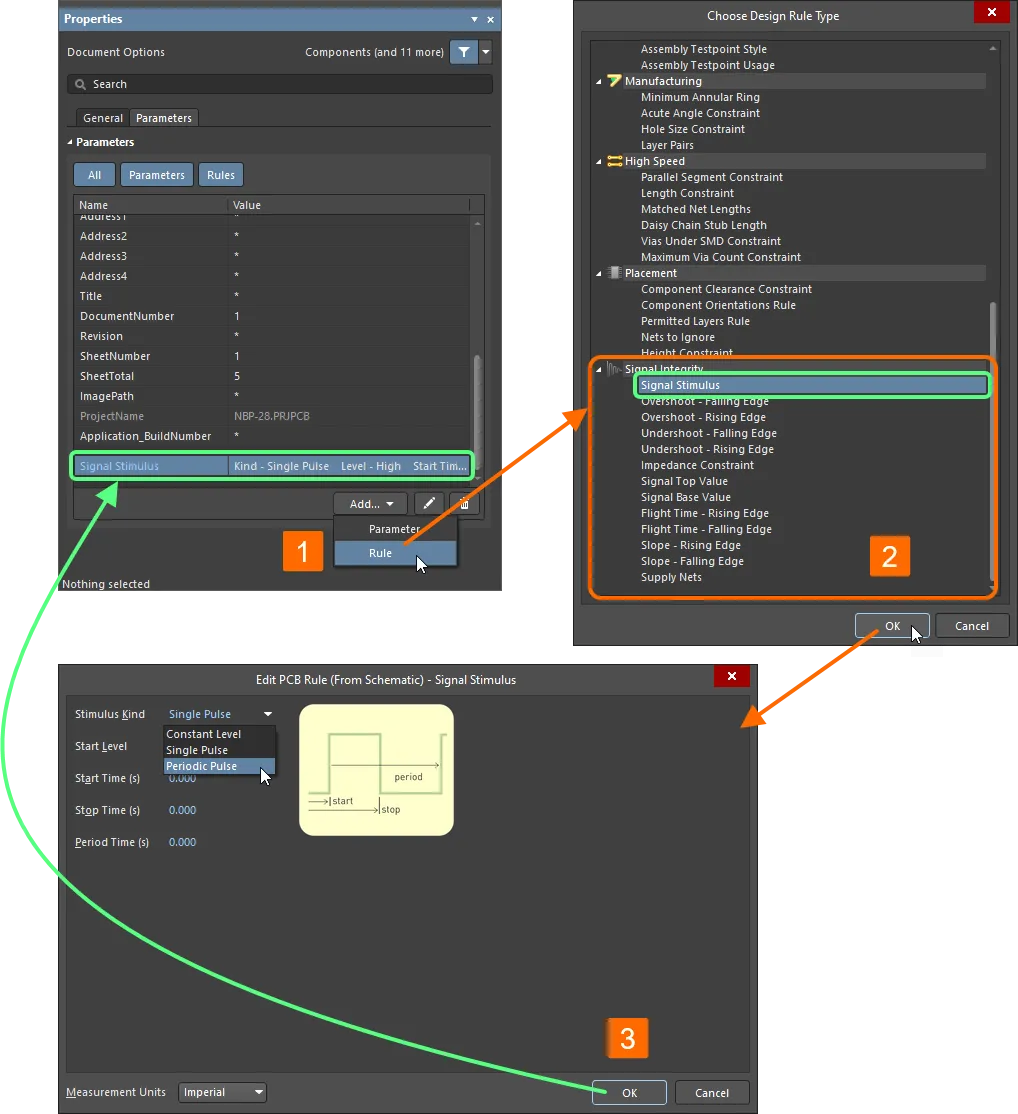

Règle de conception Signal Stimulus

L’autre règle de conception pouvant être configurée depuis l’éditeur de schéma est la règle Signal Stimulus. Lorsque cette règle est exécutée, le stimulus est injecté sur chaque broche de sortie du net analysé. Cela nécessite une règle de conception utilisant une portée définie sur « all » ; vous devez donc créer un paramètre de feuille pour cette règle. Si vous ne configurez pas cette règle, les options de règle par défaut sont utilisées.

-

Lorsqu’aucun objet n’est sélectionné dans la feuille de schéma, ouvrez le panneau Properties. Dans l’onglet Parameters du panneau, cliquez sur le bouton Add et sélectionnez Rule dans le menu déroulant.

-

La boîte de dialogue Choose Design Rule Type s’ouvre, dans laquelle le type de règle peut être choisi. Faites défiler jusqu’aux règles Signal Integrity et sélectionnez Supply Nets, puis cliquez sur OK.

-

La boîte de dialogue Edit PCB Rule (From Schematic) - Signal Stimulus s’affiche. Choisissez le type de stimulus, le niveau de départ et les temps, puis cliquez sur OK. L’entrée de règle sera répertoriée dans le panneau Properties.

Une règle de conception d’intégrité du signal peut être ajoutée comme paramètre de feuille de schéma.

Règles de conception d’intégrité du signal dans le PCB

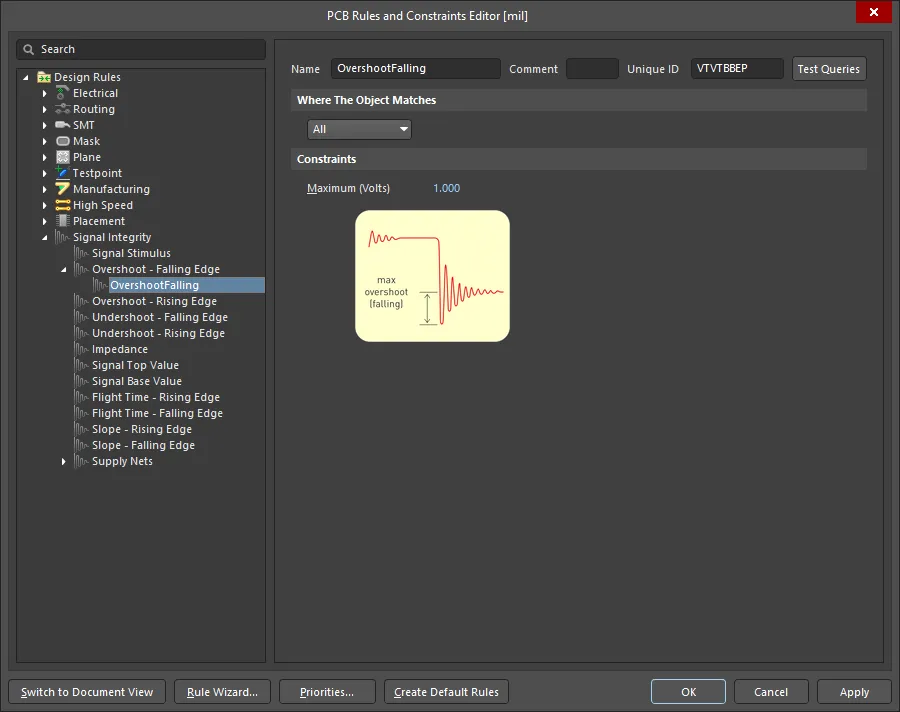

Les paramètres d’intégrité du signal, tels que le dépassement positif, le dépassement négatif, l’impédance et les exigences de pente du signal, peuvent être spécifiés comme règles de conception PCB standard. Sélectionnez Design » Rules dans l’éditeur PCB pour accéder à la boîte de dialogue PCB Rules and Constraints Editor, dans laquelle vous pouvez configurer ces règles. Vous pouvez également configurer ces règles à l’aide de paramètres dans l’éditeur de schéma ; elles apparaîtront alors dans la boîte de dialogue PCB Rules and Constraint Editor après le transfert de la conception vers le routage PCB.

Boîte de dialogue PCB Rules and Constraint Editor lors de la consultation d’une règle de conception Overshoot - Falling Edge

Ces règles ont deux objectifs. Le premier est lors de l’exécution des vérifications DRC standard dans le PCB : la carte peut être vérifiée par rapport à ces règles à l’aide de l’analyse de contrôle standard. Le second usage de ces règles intervient lors de l’utilisation du panneau Signal Integrity. Ces règles peuvent être configurées et activées comme tests, et le panneau affichera graphiquement quels nets ont échoué à quels tests.

Lorsque la conception est prête, configurez et exécutez l’analyse d’intégrité du signal.