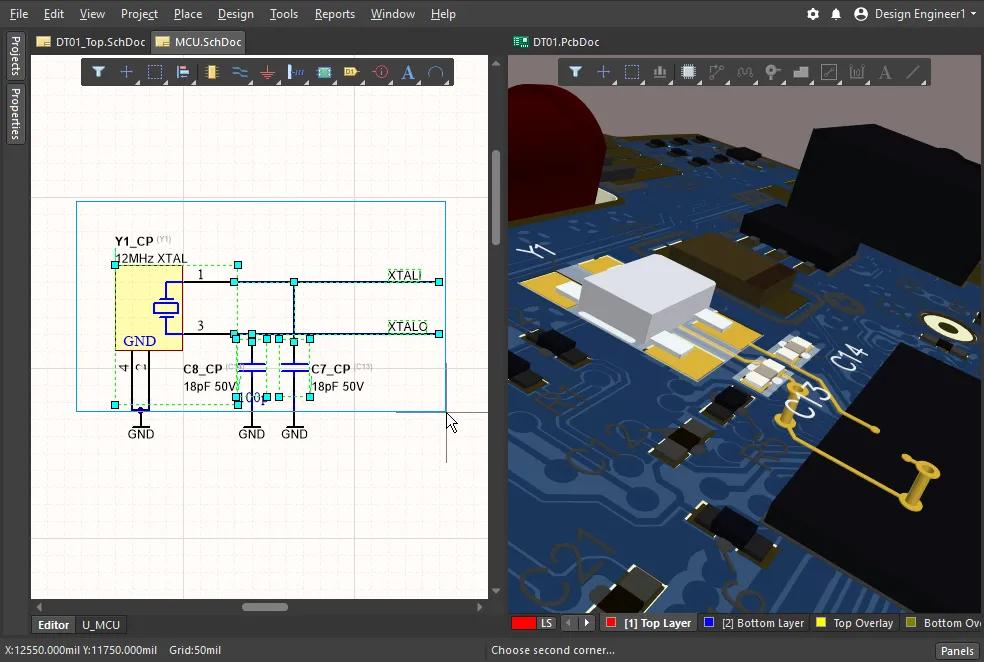

正是元器件以及它们彼此之间的连接方式,构成了你独特的电子电路。在原理图中,你通过将元器件引脚相互连接来创建设计的逻辑表示; 而在设计印制电路板时,你需要放置实际的物理元器件,并通过布线建立相同的连通关系。

物理与逻辑连通性

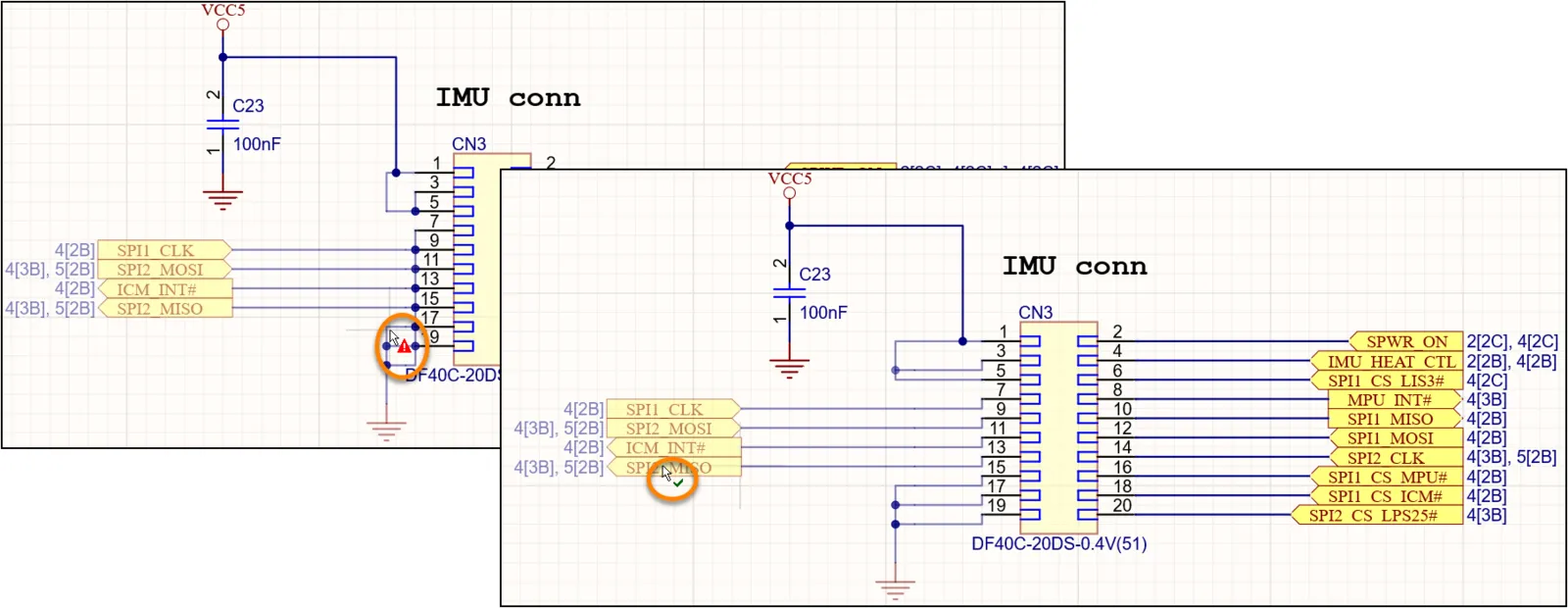

在原理图中,你可以通过从一个元器件画一根导线到另一个元器件来创建这种连通性——这称为物理连通性。

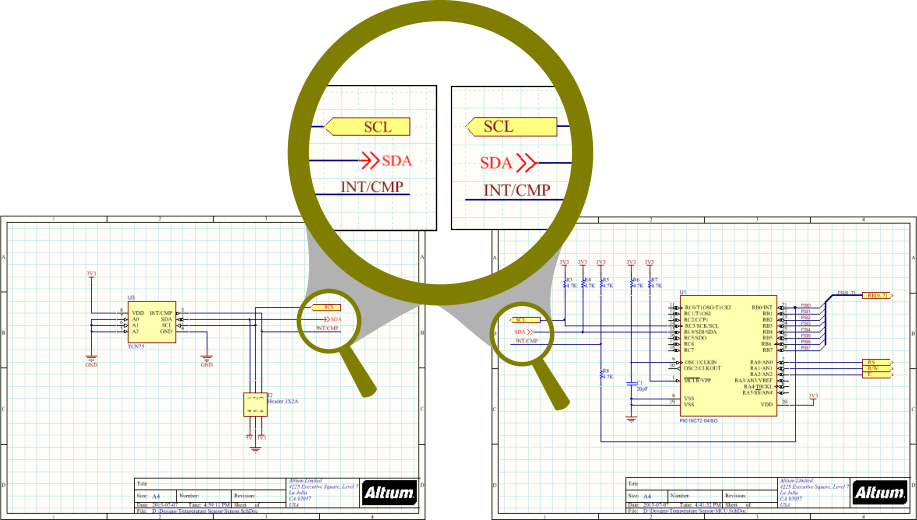

你也可以通过放置一小段导线,并在每个元器件引脚上放置一个网络标号(Net Label)来将一个引脚连接到另一个引脚。软件会识别这两段网络并将它们连接起来,形成一个单一网络。这种连通性称为逻辑连通性。

物理连通性便于用户在研究电路时沿着每一根导线追踪连接关系,但导线过多会导致原理图变得密集且杂乱。另一方面,网络标号可以减少布线数量,但用户必须在图纸上查找所有可能的连接点。作为设计者,你可以自由决定哪种连通模型最适合你的设计,也可以混合使用两种技术。

放置导线以创建物理连通性,或使用网络标号以创建逻辑连通性。

除了在 within 原理图页内创建逻辑连通性之外,还有一些对象可用于在 between 原理图页之间创建逻辑连通性。具体如何创建这种连通性取决于你如何组织原理图: 是采用平面设计,还是采用分层设计。更多内容见下文。

有多种不同的网络标识符可用于在不同图纸之间建立连接。

Connectivity Insight

Altium Designer Connectivity Insight 功能(Design Insight 功能的一部分)可即时显示项目内的连接关系视图。它以文档树的形式呈现,并可选显示原理图预览;可选择的元素提供了一种快速且直观的方式,用于在项目的连通结构中导航。

在其 默认设置状态 下,Connectivity Insight 功能会显示:

-

当光标悬停在原理图连通对象(导线、端口等)上时,显示相关的网络连接信息。

-

当在对象上使用 Alt+Double-click 时,显示基于树的连通性预览地图。

在此能力基础上,还有一个功能:将鼠标悬停在属于某个信号网络的对象上,然后按下 Ctrl+Alt。这会打开一个可选择的树状视图。单击树中所需的图纸即可快速跳转到该文档。

可在 Preferences dialog 的 System - Design Insight page 中,通过勾选/取消勾选 Document Tree entry 的 Mouse Hover 选项来启用/禁用该功能。

在所有原理图中,也可以通过在选择网络时按住 Alt 键并单击导线(Alt+Click)来高亮显示整个设计中的网络连通性。

要为电路中选定点选择所有电气相连的对象,你可以使用主菜单中的

Edit » Select » Connection 命令,或在

Active Bar 上使用

Select Connection 命令。单击你希望选中其电气连接对象的某个对象后,所有与该对象电气相连的对象都会被选中,同时会应用过滤以将图纸上的其他对象变暗显示。

用于创建连通性的对象

原理图编辑器包含以下用于创建连通性的对象。总体而言,这些对象被称为 net identifiers。

-

不同类型但同名的网络标识符不会自动彼此连接。这取决于网络命名选项的配置方式。下文将讨论这些选项。

-

注意:由网络标识符定义的网络名称不区分大小写。例如,如果两根导线分别添加了网络标号 abc 和 ABC,它们将被分配到同一个网络 abc (如果项目的 Net Identifier Scope 允许这样做)。

-

避免在网络名称末尾使用撇号('),因为该字符在 query language 中是一个功能运算符,因此可能会因为该字符后还期望有另一个参数而导致错误。

Net Label

网络标号用于标识并在电气上连接原理图中的不同点。

摘要

原理图元器件引脚之间的电气连通性可以通过在这些引脚之间放置导线来创建。这称为物理连通性,因为引脚是通过 physically 导线连接的。也可以通过使用合适的网络标识符(例如网络标号)以逻辑方式创建连通性。网络标号除了为网络提供便于人理解的标识外,还允许你在不实际用导线把它们连在一起的情况下连接电路中的各个点。

可用性

在原理图编辑器中,网络标号仅可通过以下方式放置:

-

从主菜单选择 Place » Net Label 。

-

在设计空间顶部的 Active Bar 上的图形对象下拉菜单中,单击 Net Label 按钮( )。 (单击并按住 Active Bar 按钮可访问其他相关命令。某个命令一旦被使用,它将成为 Active Bar 该分区的最上方条目。)

)。 (单击并按住 Active Bar 按钮可访问其他相关命令。某个命令一旦被使用,它将成为 Active Bar 该分区的最上方条目。)

-

在设计空间中右键单击,然后从上下文菜单选择 Place » Net Label 。

-

单击 Wiring toolbar 上的  按钮。

按钮。

放置

启动命令后,光标将变为十字准星,你将进入网络标号放置模式,并且会有一个网络标号随光标浮动:

-

按 Tab 打开 Properties panel 的 Net Label 模式,并选中 Net Name 字段以便编辑;输入新的网络名称。

-

将网络标号定位,使其左下角接触到你希望为其赋名的对象,然后单击或按 Enter 放置网络标号。

-

继续放置更多网络标号,或右键单击/按 Esc 退出放置模式。

在放置过程中,当网络标号仍悬浮在光标上且其中心点尚未锚定之前,可执行的其他操作包括:

-

按下 Tab 键可暂停放置,并访问 Net Label mode(位于 Properties panel 中),可在其中即时更改其属性。单击设计空间暂停按钮叠加层(

)以继续放置。

)以继续放置。

-

按 X 或 Y 键可沿 X 轴或 Y 轴翻转网络标号。

-

按下 Spacebar 可将网络标号逆时针旋转,或按 Shift+Spacebar 进行顺时针旋转。旋转以 90° 为增量。

放置时的注意事项:

-

网络标号的电气热点在左下角,因此,该角必须must接触导线、总线或信号线束,才能形成有效连接。

-

如果在放置网络标号之前输入其 Net property,且输入的值以数字结尾,则后续每个网络标号都会自动递增该数字值。此行为可在 Preferences dialog 的 Schematic – General 页面上的 Auto-Increment During Placement 选项中配置。对于网络标号,仅 Primary 字段适用;当对象具有多个字段(例如 Pin)时,Secondary 字段才适用。

图形化编辑

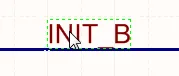

网络标号可通过所谓的 in-place editing 进行图形化编辑。要就地编辑网络标号字符串,单击一次进行选择,稍作停顿,然后第二次单击以进入编辑模式。

|

单击一次以选择该字符串。 |

|

停顿一下,然后第二次单击以进入就地编辑模式。 |

|

字符串已被选中,可输入替换字符串。 |

编辑完成后,按 Enter 或单击字符串以外区域以退出就地编辑模式。

备注

-

网络标号在单个原理图页内创建逻辑连通性;它们不会在原理图页之间创建连通性。要实现跨页连接,必须使用 Ports。

-

要对网络标号取反(在顶部加横线),可使用以下方法之一:

-

在网络名中的每个字符后添加反斜杠字符(例如

E\N\A\B\L\E)。

-

在 Preferences dialog 的 Schematic - Graphical Editing 页面上启用 Single '\' Negation 选项,然后在网络名开头添加一个反斜杠字符(例如

\ENABLE)。

-

当多个独立网络组成一条总线时,其命名方式有特定要求。更多信息请参阅 Bus 页面。

-

不同类型的网络标识符即使同名也不会自动互连。例如,名为

AGND 的网络标号不会自动连接到名为 AGND 的电源端口;必须放置一根导线将它们连接起来。

Net Label Properties

位置

-

(X/Y)

-

X (第一个字段)- 对象参考点相对于当前设计空间原点的当前 X(水平)坐标。编辑以更改对象的 X 位置。数值可用公制或英制输入;当输入的单位不是当前默认单位时,请在数值中包含单位。

-

Y (第二个字段)- 对象参考点相对于当前原点的当前 Y(垂直)坐标。编辑以更改对象的 Y 位置。数值可用公制或英制输入;当输入的单位不是当前默认单位时,请在数值中包含单位。

-

Rotation - 使用下拉列表选择旋转角度。

属性

-

Net Name - 使用下拉列表选择网络名称,或直接输入名称。

-

Font - 使用控件选择所需的字体、字号、颜色,以及是否加粗、斜体等属性(如需要)。

-

Justification - 通过单击与所需对齐方式对应的箭头来选择对齐方式,或单击圆点以居中。

Off Sheet Connector

Off Sheet Connector 用于在原理图页之间创建连接。

概述

Off Sheet Connector 是一种电气设计图元。Off Sheet Connector 用于在多个原理图页之间连接网络,这些原理图页都从同一个父级 sheet symbol 派生。

可用性

在 Schematic Editor 中,Off Sheet Connector 仅可通过以下方式放置:

-

从主菜单中选择 Place » Off Sheet Connector 。

-

在 Active Bar 上找到并使用 Off Sheet Connector 命令( )。

)。

-

在设计空间中右键单击,然后从上下文菜单中选择 Place » Off Sheet Connector 。

放置

启动命令后,光标将变为十字准星,并进入 Off Sheet Connector 放置模式,此时一个 Off Sheet Connector 将悬浮在光标上:

-

按 Tab 打开 Properties panel 的 Off Sheet Connector mode,其中 Net Name 已选中并可编辑;输入新的网络名称。

-

定位 Off Sheet Connector,使其电气热点(由光标握持的一端)接触要连接的导线,然后单击或按 Enter 以完成放置。

-

继续放置更多 Off Sheet Connector,或右键单击或按 Esc 退出放置模式。

在放置过程中,当 Off Sheet Connector 仍悬浮在光标上时,可执行的其他操作包括:

-

按下 Tab 键可暂停放置,并访问 Off Sheet Connector mode(位于 Properties panel 中),可在其中即时更改其属性。单击工作区暂停按钮叠加层(

)以继续放置。

)以继续放置。

-

按 X 或 Y 键可沿 X 轴或 Y 轴翻转 Off Sheet Connector。

-

按下 Spacebar 可将 Off Sheet Connector 逆时针旋转,或按 Shift+Spacebar 进行顺时针旋转。旋转以 90° 为增量。

如果在放置 Off Sheet Connector 之前输入其 Net 属性,且输入的值以数字结尾,则后续每个 Off Sheet Connector 都会自动递增该数字值。此行为可在 Preferences dialog 的 Schematic – General 页面上的 Auto-Increment During Placement 选项中配置。对于 Off Sheet Connector,仅 Primary 字段适用;当对象具有多个字段(例如 Pin)时,Secondary 字段才适用。

请注意,Cross Reference 功能可用于识别互连的 ports、sheet entries 和 off sheet connectors 的位置。了解更多关于在设计中 adding Cross References 的信息。

图形化编辑

Off Sheet Connector 可通过所谓的 in-place editing 进行图形化编辑。要就地编辑 Off Sheet Connector 字符串,单击一次进行选择,稍作停顿,然后第二次单击以进入编辑模式。

单击一次以选择该字符串。

单击一次以选择该字符串。

停顿一下,然后第二次单击以进入就地编辑模式。

停顿一下,然后第二次单击以进入就地编辑模式。

字符串已被选中,可输入替换字符串。

字符串已被选中,可输入替换字符串。

Off Sheet Connector 可进行就地编辑。

编辑完成后,按 Enter 或单击字符串以外区域以退出就地编辑模式。

Off Sheet Connector 没有独立的字体属性;它们使用放置所在原理图页的 Document Font 属性(也称为 System Font)。在图纸边框内双击,以在 Properties panel 中编辑 Document Options(包括字体)。

备注

-

需要牢记的是,尽管在某些情况下 Off Sheet Connector 与细分的 sheet symbol 可能很有用,但它们确实存在限制。它们无法正确自动形成 component classes;如果你选择使用它们,则需要在 PCB 中手动重新创建这些类。

-

要在两张或更多图纸之间成功连接某个特定网络,每张图纸上的 Off Sheet Connector 必须分配到同一个网络。

-

Port Cross-References 不能应用于 Off Sheet Connector,因此在可能的情况下应使用 Ports 。

Off Sheet Connector Properties

位置

-

(X/Y)

-

X (第一个字段)- 对象参考点相对于当前工作区原点的当前 X(水平)坐标。编辑此项可更改对象的 X 位置。该值可使用公制或英制输入;当输入的值单位不是当前默认单位时,请在输入时包含单位。

-

Y (第二个字段)- 对象参考点相对于当前原点的当前 Y(垂直)坐标。编辑此项可更改对象的 Y 位置。该值可使用公制或英制输入;当输入的值单位不是当前默认单位时,请在输入时包含单位。

-

Rotation - 使用下拉列表选择旋转角度。可选项为:

0 Degrees、 90 Degrees、 180 Degrees 和 270 Degrees。

属性

常规(网络)

显示分配给跨页连接器的网络属性。按需更新。

在向对象添加指令后,Power Net 和 High Speed 字段将变为可用。

参数(网络)

-

Selection buttons - 单击所需对象以在网格中显示。

-

Add - 使用下拉列表添加所需对象,然后定义其值。

在向对象添加指令后,Add 按钮将变为可用。

如果在放置跨页连接器之前就输入其 Net 属性,并且输入的值以数字结尾,则后续每个跨页连接器都会自动递增该数字值。此行为可在

Preferences dialog 的

Schematic – General 页面上的

Auto-Increment During Placement 选项中进行配置。对于跨页连接器,仅

Primary 字段适用;当对象具有多个字段(例如引脚)时,才适用

Secondary 字段。

请注意,

Cross Reference 功能会识别互连的

Ports 的位置,以及互连跨页连接器的位置网格引用。对于这两类原理图连接对象,现有的

Reports » Port Cross Reference » Add To Project 命令会基于目标图纸名称和位置网格引用添加一个交叉引用参数。

Power Port

已放置的 Power Port

已放置的 Power Port

概述

电源端口(Power Port)是一种电气设计基元。它是一种特殊的原理图对象,用于定义电源或地网络。电源端口使您能够在设计中的任意位置方便地标注电源网络,然后将其连接到引脚或导线。同名的电源网络会在整个设计中自动连接,但以下两种情况除外:

-

如果在层次化设计中,Power Port 被明确布线连接到 Port 对象(即在设置了 Net Identifier Scope 为 Hierarchical 的设计中,或在顶层图纸包含 sheet entry 且将 的 Net Identifier Scope 设置为 Automatic 的设计中),则该电源网络将变为放置所在图纸的本地网络 – 图纸之外的网络连接必须通过 Port/Sheet Entry 组合的布线来定义(了解更多)。

-

如果将 Net Identifier Scope 设置为 Strict Hierarchical。这会将所有电源网络设置为在每张图纸内本地化。了解更多关于 设置网络标识符作用域。

可用性

可通过以下方式在原理图编辑器中放置电源端口:

-

从主菜单单击 Place » Power Port 。

-

单击 Wiring 工具栏上的  按钮,放置条形(bar-style)电源端口,并预先分配到

按钮,放置条形(bar-style)电源端口,并预先分配到 VCC 网络。

-

单击 Wiring 工具栏上的  按钮,放置电源地(power ground)样式的电源端口,并预先分配到

按钮,放置电源地(power ground)样式的电源端口,并预先分配到 GND 网络。

-

在 Active Bar 的电源端口下拉列表中选择命令。

-

单击 Utilities 工具栏上的  按钮,打开下拉列表以提供一组电源端口命令,其中包括多种样式以及若干预先分配网络的电源端口。

按钮,打开下拉列表以提供一组电源端口命令,其中包括多种样式以及若干预先分配网络的电源端口。

-

在设计空间中右键单击,然后从上下文菜单中选择 Place » Power Port 。

放置

启动命令后,光标将变为十字准线,并进入电源端口放置模式。电源端口符号将随光标浮动显示。

-

定位对象后单击或按 Enter 以完成放置。

-

继续放置更多电源端口,或右键单击/按 Esc 退出放置模式。

在放置过程中(电源端口仍随光标浮动时)还可执行以下附加操作:

-

按 Tab 键暂停放置,并从 Properties panel 的 Power Port mode 中访问其属性,以便即时更改。单击设计空间中的暂停按钮叠加层(

)以继续放置。

)以继续放置。

-

按 Alt 键将移动方向约束为水平或垂直轴,具体取决于初始移动方向。

-

按 Spacebar 可将电源端口逆时针旋转,或按 Shift+Spacebar 顺时针旋转。旋转以 90° 为增量。

-

按 X 或 Y 键可沿 X 轴或 Y 轴镜像电源端口。

图形化编辑

此编辑方式允许您在设计空间中直接选择已放置的电源端口对象,并以图形方式更改其位置。电源端口的尺寸和形状是固定的。因此,当选中电源端口对象时不会提供编辑手柄:

选中的 Power Port

选中的 Power Port

-

在虚线框内任意位置单击并拖动,以按需重新定位电源端口。拖动时,可旋转电源端口(Spacebar/Shift+Spacebar)或镜像(按 X 或 Y 键沿 X 轴或 Y 轴翻转)。

-

电源端口对象所分配的网络可通过就地编辑 来修改,方法如下:

-

单击一次电源端口以选中它。

-

再次单击一次(或按 Enter)进入就地编辑模式。两次单击之间应留出足够时间,以确保软件不会将两次单击解释为一次双击(双击会打开 Properties panel)。

-

要结束就地文本编辑,请按 Enter 或使用鼠标在电源端口之外单击。

Power Port 样式

电源端口提供以下图形样式,可通过在 Properties panel 中编辑对象的 Style 属性来设置。

为电源端口选择的图形符号并不决定其分配到的网络。必须显式设置网络名称。

|

箭头

|

|

横杠

|

|

圆形

|

|

接地

|

|

GOST 箭头

|

|

GOST 横杠

|

|

GOST 接地

|

|

GOST 电源地

|

|

电源地

|

|

信号地

|

|

波形

|

与 GOST 相关的样式可让您符合由欧亚标准化、计量与认证理事会(EASC)维护的区域标准(GOST)。独联体(CIS)各地的设计人员都遵循这些标准。

注释

Power Port Properties

位置

-

(X/Y)

-

X (第一个字段)- 对象参考点相对于当前设计空间原点的当前 X(水平)坐标。编辑以更改对象的 X 位置。该值可用公制或英制输入;当输入的单位不是当前默认单位时,请带上单位。

-

Y (第二个字段)- 对象参考点相对于当前原点的当前 Y(垂直)坐标。编辑以更改对象的 Y 位置。该值可用公制或英制输入; 当输入的单位不是当前默认单位时,请带上单位。

-

Rotation - 使用下拉列表选择旋转角度。

属性

-

Name - 电源端口的名称。使用“眼睛”图标 显示/隐藏名称。

-

Style - 使用下拉列表选择电源对象的样式。预览图会根据您的选择更新。单击颜色框以选择颜色。

-

当通过使用 Import Wizard 导入 OrCAD 设计时,在生成的原理图文档中支持自定义电源端口。此类电源端口将与原始设计具有相同的图形,并且其 Style 属性的值为 Custom。了解更多关于 从 OrCAD 导入设计。

-

当通过使用 Import Wizard 导入 xDX Designer 设计时,在生成的原理图文档中支持自定义电源端口连接器。此类电源端口连接器将与原始设计具有相同的图形,并且其 Style 属性的值为 Custom。了解更多关于 从 xDX Designer 或 DxDesigner 导入设计。

-

Font - 如有需要,使用控件选择所需的字体、字号、颜色以及加粗、斜体等属性。

常规(网络)

显示分配给电源端口的网络属性。按需更新。

在向对象添加指令后,Power Net 和 High Speed 字段将变为可用。

参数(网络)

-

Selection buttons - 单击所需对象以在网格中显示。

-

Add - 使用下拉列表添加所需对象,然后定义其值。

在向对象添加指令后,Add 按钮将变为可用。

Wire

导线用于在原理图中创建电气连通性。

导线用于在原理图中创建电气连通性。

摘要

导线是一种折线(polyline)电气设计基本对象,用于在原理图上的各点之间形成电气连接。它类似于物理导线。

可用性

在原理图编辑器中,导线只能通过以下方式放置:

-

从主菜单中选择 Place » Wire。

-

在设计空间顶部的 Active Bar 下拉列表中单击“导线”按钮(

)。(单击并按住 Active Bar 按钮可访问其他相关命令。某个命令一旦使用过,它将成为该 Active Bar 区域中的最上层项目。)

)。(单击并按住 Active Bar 按钮可访问其他相关命令。某个命令一旦使用过,它将成为该 Active Bar 区域中的最上层项目。)

-

单击 Wiring 工具栏上的

按钮。

按钮。

-

在设计空间中右键单击,然后从上下文菜单中选择 Place » Wire 命令。

-

使用 Ctrl+W 快捷键。

放置

启动命令后,光标将变为十字准星,进入导线放置模式。放置通过执行以下操作序列完成:

-

单击或按 Enter 以锚定导线的起点。

-

移动光标,然后单击或按 Enter 以锚定一系列顶点,从而定义导线的形状。

-

放置最后一个顶点后,右键单击或按 Esc 以完成导线放置。

-

继续放置更多导线对象,或右键单击/按 Esc 退出放置模式。

-

使用 Backspace 或 Delete 键移除最后放置的导线段。

放置模式

放置导线时,有三种“手动”放置模式,其中两种具有 Start 和 End 子模式。该模式指定放置导线时如何生成拐角,以及导线可放置的角度。在放置过程中:

-

按 Shift+Spacebar 在各模式间循环切换。

-

在 90 Degree 或 45 Degree 模式(称为真正的正交模式)下,按 Spacebar 在 Start 与 End 子模式间循环切换。

-

放置过程中,当前放置模式会显示在状态栏中。您可以在导线放置期间随时更改模式。

-

在 Any Angle 以外的模式中,连接到光标的线段是 look-ahead 线段。您实际正在放置的线段位于该前瞻线段之前。

45 度模式

45 度模式

90 度模式

90 度模式

任意角度模式

任意角度模式

自动布线模式

自动布线模式

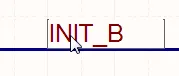

此外还有一种 Auto Wire 模式,可使用 Point to Point Router 从上一段的末端快速布线到光标单击的位置。布线路径会在避开图纸上已放置对象的同时,尽可能高效。放置导线时,按 Shift+Space 在放置模式间轮换。进入 Auto Wire 放置模式后,按 Tab。在此模式下按 Tab 可在 Point to Point Router Options 对话框中配置适用选项。

Point to Point Router Options 对话框

-

Time Out After (s) - 超时设置可防止在尝试计算路径时耗费无限长的时间。输入所需的秒数;默认值为 3。

-

Avoid cutting wires - 用于避免让新导线跨越大量现有导线。 在刻度的 L 端,导线放置不会对现有导线进行区分;在刻度的 H 端,导线放置会避开现有导线。将标记从刻度一端拖到另一端,或拖到中间任意所需位置。

引导布线

原理图具有可定义的电气网格,可轻松定义对象之间的电气连接。当您放置导线时,如果导线落入另一个电气对象的电气网格范围内,光标将吸附到该固定对象,并出现一个热点(蓝色十字)。

热点会引导您到可建立有效连接的位置,并自动将光标吸附到电气连接点。

电气网格可在 Document Options 模式下的 Properties 面板Properties 的 General 选项卡中定义。建议将电气网格设置得略小于当前捕捉网格,否则可能会难以将电气对象以相隔一个捕捉网格的距离进行定位。

吸附范围(即一个对象在多远的距离内会以电气方式吸附到另一个电气对象的热点)可在

General 部分的

Snap Distance 字段中定义,该字段位于

Properties panel(当图纸上未选中任何对象时)。建议将此“对象吸附”范围设置得略小于当前吸附网格,否则很难将电气对象以相隔一个吸附网格的距离进行放置。对象吸附可通过

Shift+E 键盘快捷键切换开/关,或通过启用/禁用

Properties 面板中的

Snap 选项(位于

Snap Distance 字段上方)来控制。

图形化编辑

此编辑方法允许你在设计空间中直接选择已放置的导线对象,并以图形方式更改其尺寸和/或形状。

当选中导线对象时,可使用以下编辑手柄。

已选中的导线,准备进行图形化编辑。

已选中的导线,准备进行图形化编辑。

-

单击并拖动 A 以重新定位导线的端点。

-

单击并拖动 B 以移动导线的顶点。端点将保持锚定不动。

-

在导线段上单击并拖动以 grab 该线段并重新定位。端点和其他顶点将保持锚定不动。

-

在顶点处右键单击,然后选择 Edit Wire Vertex n 命令,以打开 Wire 对话框,并选中

nth 顶点的条目以便编辑。根据需要编辑该顶点和/或导线的其他属性。更多信息请参阅 Wire Properties 部分。

-

在顶点上单击并按住,然后在键盘上按 Delete 以删除该顶点。

要移动整根导线,请在未选中的导线上单击并按住,然后移动到新位置。

关于拖动的信息

-

拖动过程中会使用热点来直观指示将在哪些位置创建自动结点。

-

拖动结束后,会移除不必要/冗余的自动结点。

新建自动结点的指示

根据受影响的布线情况,执行拖动操作可能会在新位置创建自动结点。为对这些新结点实例的位置提供可视化反馈,会使用热点。在 Preferences dialog 的 Schematic - Compiler 页面上的 Auto-Junctions 区域中,为导线和总线启用这些热点并设置其颜色。

选择与移除

选中导线后,单击某一线段可单独选中该线段。这种导线“子选择”会通过相关编辑手柄变为红色来区分。

单个线段子选择。

单个线段子选择。

随后可使用 SCH List panel 直接编辑该线段关联的顶点,任何更改都会立即显示在原理图上。

你也可以按一下 Delete 键来删除所选导线段。你可以删除跨不同导线的多个线段——确保每个线段都已被选中(对后续每个线段按 Shift+Click 两次,将其纳入整体线段选择)。自动结点也会被纳入考虑——允许你仅删除到该结点为止的一段导线(并且如果该结点否则只会与另外两段导线相连,则也会一并删除该结点)。

以 T 形结点为例,它由三段导线和一个结点构成——删除其中一段导线将导致该结点被删除。剩余的两段导线将合并为单一线段。

自动结点

导线中的 T 形结点会通过结点(编译器生成结点)自动连接。如果在 Preferences dialog 的 Schematic - General 页面启用了 Break Wires At Autojunctions 选项,则在插入自动结点的位置,现有导线段会被断开为两段。例如,在创建 T 形结点时,垂直的导线段会被断开为两段,分别位于结点两侧。若禁用 Break Wires At Autojunctions 选项,则导线段在结点处将保持不断开。

Wire Properties

常规(网络)

显示分配给该导线的网络属性。

将光标悬停在已放置的导线上,会以工具提示显示其 Net Name 和 Physical Name。

顶点

-

Width - 使用下拉列表选择所需线宽。单击颜色框为对象选择所需颜色。

-

Vertices Grid - 以以下形式列出当前为该对象定义的所有顶点:

-

Index - 顶点的分配索引(不可编辑)。

-

X - 顶点的 X(水平)坐标。单击可编辑。

-

Y - 顶点的 Y(垂直)坐标。单击可编辑。

-

Add - 单击以添加新顶点。新顶点将添加在当前聚焦的顶点条目下方,并且初始 X、Y 坐标与聚焦条目相同。单击

以删除当前选中的顶点。

以删除当前选中的顶点。

参数(网络)

-

Selection buttons - 单击所需对象以在网格中显示。

-

Add - 使用下拉列表添加所需对象,然后定义其值。

在对象上添加指令后,Add 按钮将可用。

Compiler Generated Junction

原理图编译器会在每个 T 形结点处自动添加结点,以完成电气连接。

概述

结点是一种电气设计基元,是原理图图纸上用于连接相交导线(或总线、或信号线束)的小圆形对象。编译器生成结点是指当两条导线/总线/信号线束以 T 形方式连接,或当导线/总线/信号线束以正交方式连接到引脚、电源端口或其他电气对象时,由自动结点功能自动放置的结点。

可用性

此类结点由原理图编辑器的自动结点功能自动放置。因此,它不是用户可访问并手动放置的设计对象。

放置

在布线过程中只要出现 T 形结点,就会自动放置编译器生成结点,例如两条导线/总线/信号线束以 T 形相交,或导线/总线/信号线束以正交方式穿过器件引脚端点或其他电气对象(如 Power Port)的端点。

如果在 Preferences dialog 的 Schematic - General 页面启用了 Break Wires At Autojunctions 选项,则在插入自动结点的位置,现有导线/总线/信号线束线段会被断开为两段。例如,在创建 T 形结点时,垂直的导线/总线/信号线束线段会被断开为两段,分别位于结点两侧。若禁用该选项,则导线/总线/信号线束线段在结点处将保持不断开。

编辑

编译器生成结点无法以常规方式编辑(通过对话框或在原理图图纸上进行图形化编辑)。编译器生成结点的显示属性在 Schematic - Compiler 页面上的 Preferences dialog 中配置,如下图所示。请注意,禁用编译器生成结点的显示并不会断开该结点处的电气连接。

在 Preferences dialog 中配置编译器生成结点(自动结点)的显示选项。

在 Preferences dialog 中配置编译器生成结点(自动结点)的显示选项。

新建自动结点的指示

根据受影响的布线情况,执行拖动操作可能会在新位置创建自动结点。为对这些新结点实例的位置提供可视化反馈,会使用热点。启用这些热点的使用,并指定其颜色——针对导线和总线——也属于首选项设置的一部分。

控制拖动操作期间对预测自动结点的显示。

控制拖动操作期间对预测自动结点的显示。

示例:显示拖动操作导致预测产生的新自动结点。

连通性变化的可视化指示

拖动元件时,可能会不小心拖得过远或偏离路径,从而产生非预期的自动结点,并可能对电路连通性造成致命更改。为在拖动过程中及时以图形方式指示连通性状态,会使用两个图标:

- OK - 拖动操作不会改变电路的连通性。

- OK - 拖动操作不会改变电路的连通性。

- Alert - 拖动操作正在导致电路的连通性发生变化。

- Alert - 拖动操作正在导致电路的连通性发生变化。

拖动时,适用的图标会显示在光标附近。

此功能要求在 Preferences dialog 的 Schematic - Compiler 页面中 Auto-Junctions 区域启用 Display When Dragging 选项。

将警示符号显示在光标附近(而不是显示在连通性发生变化的位置)的好处在于:即使变化发生在当前工作区可视范围之外的电路区域,你也能获得针对该变化的可视化警告。

提供可视化警告,提示拖动操作将导致连通性发生变化。

转换交叉结点

你可以快速将一个四向结点(由导线或总线对象创建)转换为两个相邻的三向结点。为此,从主菜单中选择 Tools » Convert » Convert Cross Junctions 命令。启动命令后,将出现 Junctions Conversion 对话框。使用该对话框来确定转换的范围(当前文档、工程文档或所有打开的原理图文档),以及是考虑所有可能的四向结点,还是仅考虑目标文档中与所选导线/总线相关联的结点。按需配置好转换选项后,在对话框中单击 OK 即可执行转换。

当基于所选对象进行转换时,你必须选择进入该四向结点的所有导线(或总线)线段。

Junctions Conversion 对话框

Junctions Conversion 对话框的选项/控件

范围

-

Sheet Scope - 选择以下选项之一以确定更新范围:

-

Current Document - 仅更新活动原理图文档,并应用其当前模板的更改。

-

Project Documents - 更新活动原理图文档以及活动工程中的所有其他原理图文档,并应用各自当前模板的更改。当前处于关闭状态的原理图将被打开。

-

Open Documents - 更新活动原理图文档以及所有其他已打开的原理图文档(不论其所属工程),并应用各自当前模板的更改。

-

Selection - 使用下拉列表选择范围内所需的对象:

-

Selected Objects - 仅选择在从 Sheet Scope 选定的图纸中已被选中的对象。

-

All Objects - 选择从 Sheet Scope 选定的图纸中的所有对象。

选项

-

Miter Size - 输入一个值以定义斜接(miter)的尺寸。

设计结构如何影响连通性

Related page: 多图纸与层次化设计

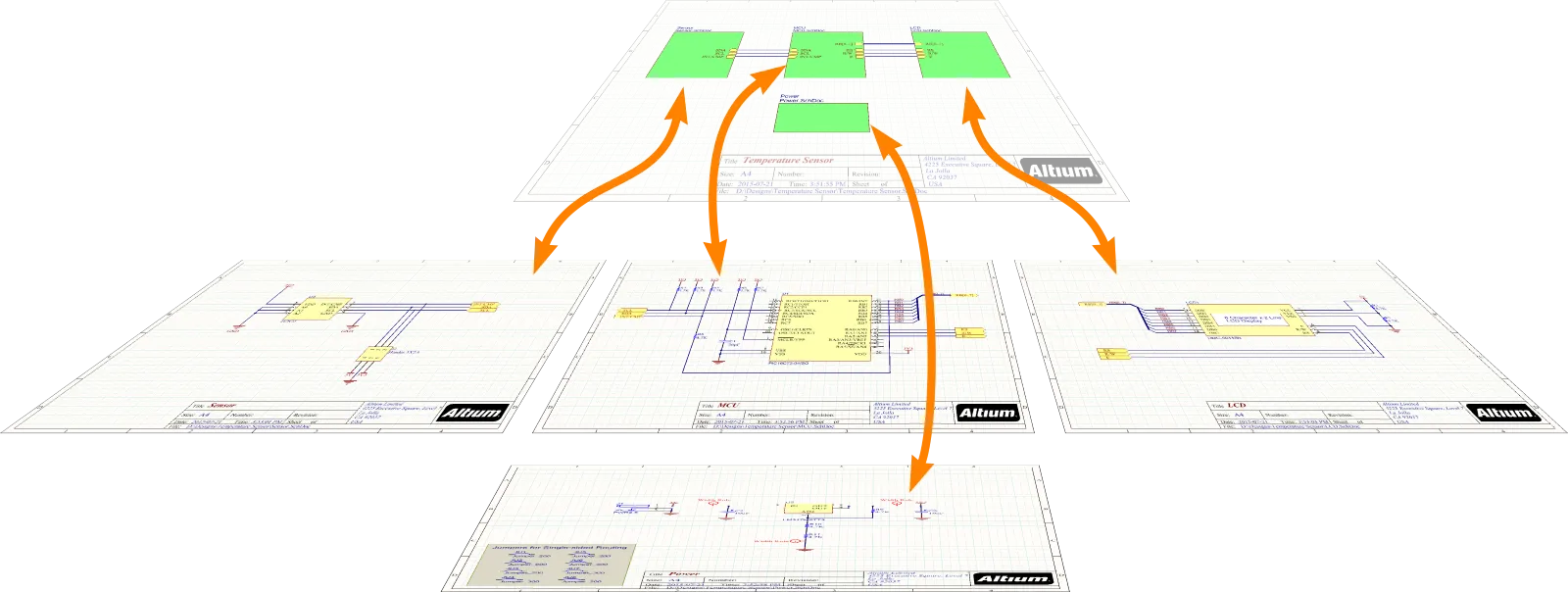

如果设计无法放在单张原理图图纸上,可以分布到多张图纸上。多图纸原理图中组织与创建连通性有两种截然不同的模型:一种是扁平(flat)设计,可将其视为一张很大的原理图被切分成若干较小的图纸;另一种是层次化(hierarchical)设计,其中各图纸以“祖父-父-子”式结构相互链接。

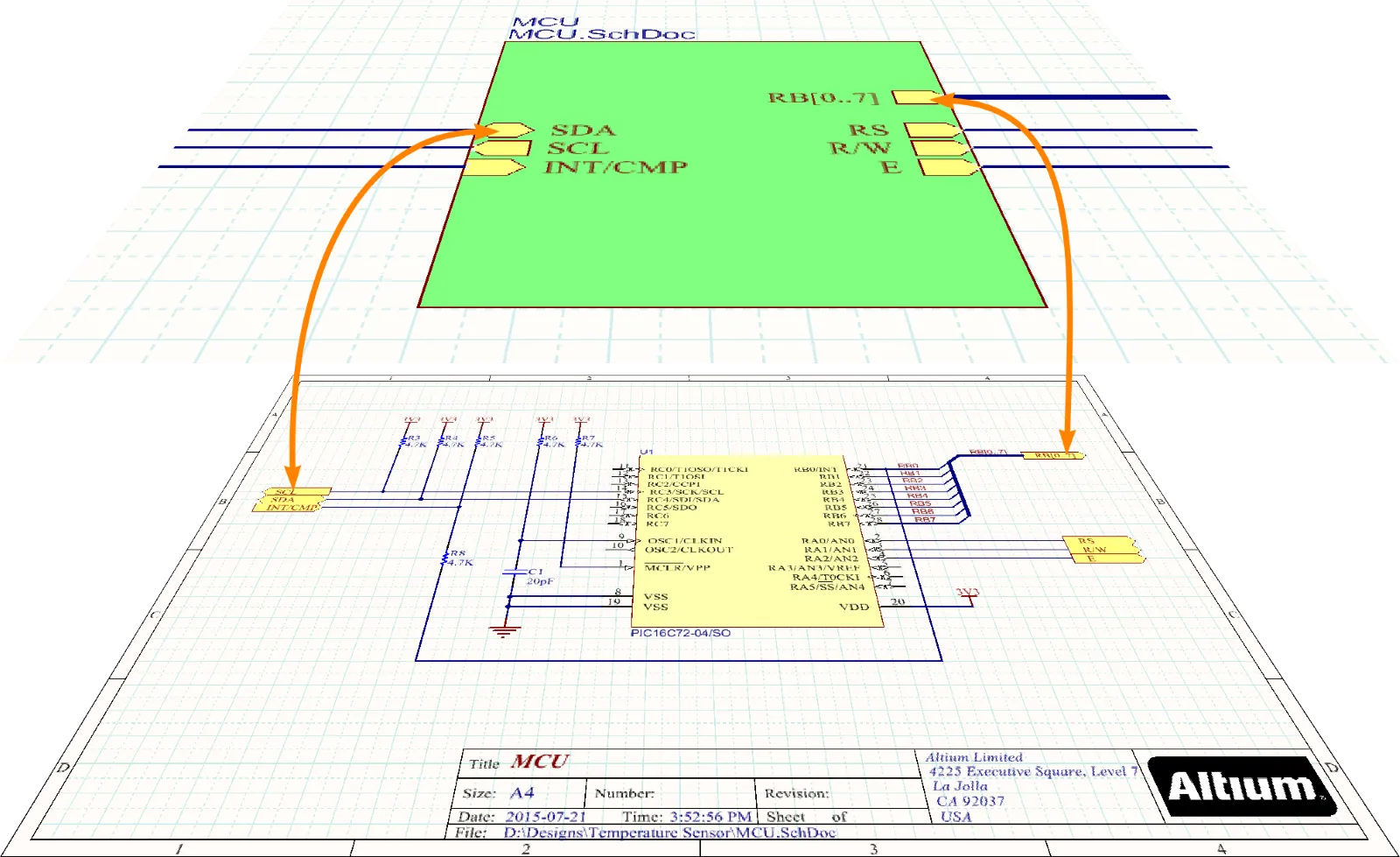

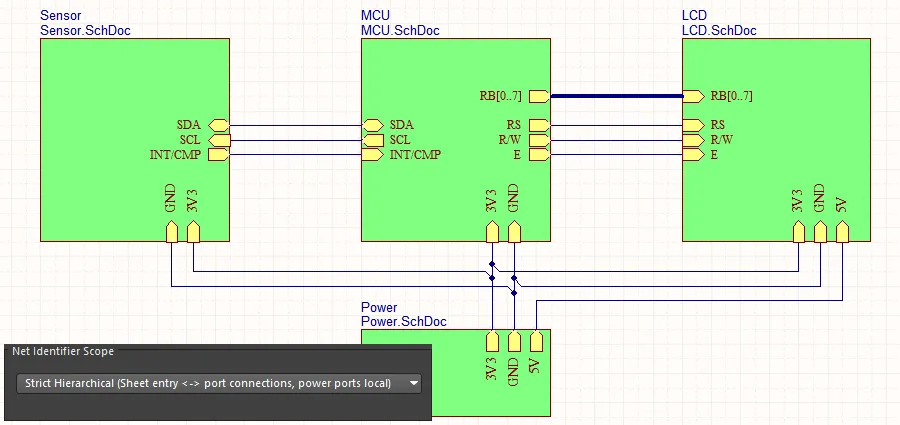

多图纸设计通过在父图纸上放置一个 Sheet Symbol 来实现,该符号代表并链接到子图纸,如下图所示。

Sheet Symbol 表示(并链接到)更低层级的图纸。在扁平设计中,该结构只能有一层深度;在层次化设计中,深度没有限制。

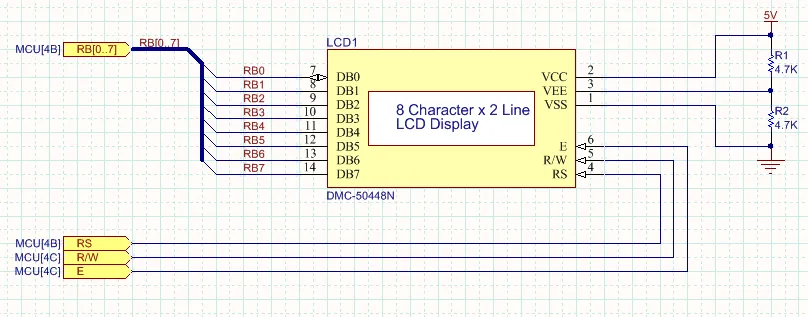

扁平设计

Related page: 多图纸与层次化设计

当连通性直接从一张图纸创建到另一张图纸时,该设计称为扁平设计。它不会通过父图纸上的 Sheet Symbol。在扁平设计中,Sheet Symbol 仅用于表示(并引用)子图纸。由于不存在层级结构,设计中的所有图纸在 Projects panel 中显示在同一层级。下面两张图都展示了扁平设计。

扁平设计更容易创建。扁平设计可以包含一张顶层图纸,并为每张子图纸放置一个 Sheet Symbol,但这不是必需的,因为该顶层图纸不用于创建跨图纸连通性。对于只有两三张原理图图纸的小型设计,你可能会认为顶层图纸并无额外价值。当图纸数量增多时,顶层图纸可以通过图纸上逻辑块(Sheet Symbol)的排列方式,帮助读者理解电路设计的功能。

同一设计:不含顶层图纸(左)与包含顶层图纸(右)的展示——两者都是扁平设计示例。

在扁平设计中,图纸之间的连接可通过 Ports、Offsheet Connectors、Power Ports 和 Net Labels 来创建,如上图放大镜所示。推荐的方法是在 within 每张图纸上使用 Net Labels,并使用 Ports 来连接 between 图纸。Ports 比 Off-Sheet Connectors 提供更多功能,包括可添加 Port Cross References,它会在每个端口旁添加一个 SheetName[GridReference],引用另一张图纸上的匹配端口,如下图所示。

扁平设计中的图纸数量没有限制。

每个 Port 旁都添加了 Port Cross References,指示匹配 Port 的目标图纸与网格参考位置。

当连通性直接从一张图纸到另一张图纸时,设计即为扁平。该连通行为由 设置 Net Identifier Scope 为 Automatic、Flat 或 Global 来定义。注意:如果你选择混合使用 Ports 与 Net Labels 来创建跨图纸连通性,则不能使用 Automatic 选项。在这种情况下,你必须手动将 Net Identifier Scope 设置为 Global。

层次化设计

Main page: 多图纸与层次化设计

当跨图纸连通性从 Sheet Symbol 向下连接到该 Sheet Symbol 所引用的子图纸时,该设计称为层次化设计。在网络(net)层面,连通性在该 Sheet Symbol 中的 Sheet Entry 与子图纸上与该 sheet entry 同名的 Port 之间创建。这种连通性也称为垂直连通性(vertical connectivity),因为所创建的跨图纸连通性仅在父图纸与其子图纸之间上下传递。

在层次化设计中,网络层面的连通性从父图纸上的 Sheet Entry 向下连接到子图纸上匹配的 Port。

层次化设计有两大主要优势。

-

第一是能够通过原理图图纸的结构组织方式,并将其作为逻辑块(Sheet Symbol)呈现,从而向读者展示设计的功能。顶层原理图将设计呈现为一组高层功能块,块的排列反映了整体电路传统的从左到右、从输入到输出的流程。这些块在需要时还可以进一步拆分为更小的块,使得承载元器件的最低层级原理图结构相对简单、元器件数量较少。由于每张图纸都相对简单,图纸尺寸可以保持较小,这在打印原理图时是一个很大的优势。

-

另一个主要优势是:在层次化设计中通常更容易追踪信号,因为读者只需将父图纸上的 Sheet Entry 与子图纸上的 Port 匹配起来,然后即可在每张图纸内部沿着布线追踪信号。

构建层次化设计需要额外工作。Sheet Symbol 需要 Sheet Entries,并且顶层图纸必须布线以在不同 Sheet Symbol 之间传递信号。软件包含用于帮助保持 Sheet Entries 与子图纸 Ports 同步的工具(对所有 Sheet Symbols 使用 Design » Synchronize Sheet Entries and Ports,或在某个 Sheet Symbol 上右键然后选择 Sheet Symbol Actions » Synchronize Sheet Entries and Ports 以仅针对单个 Sheet Symbol)。它还包含用于将较大设计拆分为小块的工具(Edit » Refactor » Move Selected Subcircuit to Different Sheet)。要了解更多关于这些重构与重整工具的信息,请参阅 Design Refactoring 页面。

层次化设计可以具有任意深度,并包含任意数量的原理图图纸。

当跨图纸连通性仅在父图纸上的 Sheet Entries 与子图纸上匹配的 Ports 之间建立时,设计即为层次化。该连通行为由 设置 Net Identifier Scope 为 Automatic、Hierarchical 或 Strict Hierarchical 来定义。

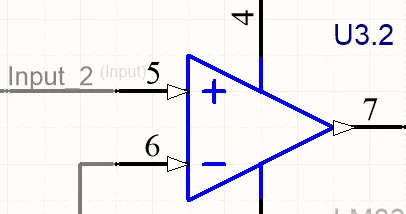

多通道设计

Main article: 创建多通道设计

电子设计中包含重复的电路段并不少见。它可能是一个立体声功放,或一个 64 通道调音台。这类设计可由一组称为 multi-channel design 的功能完整支持。在多通道设计中,你只需捕获一次重复电路,然后通过以下方式指示软件重复它:放置多个都引用同一子原理图的 Sheet Symbol,或配置单个 Sheet Symbol,使其将所引用的子原理图按所需次数重复。编译后的设计会在计算机内存中展开,所有器件与连通性都会按 user-defined naming scheme 的要求重复相应次数。

左侧有四个 Sheet Symbol,全部引用同一个子页(PortIO.SchDoc)。右侧通过 Repeat keyword 将 InputChannel.SchDoc 重复了八次。

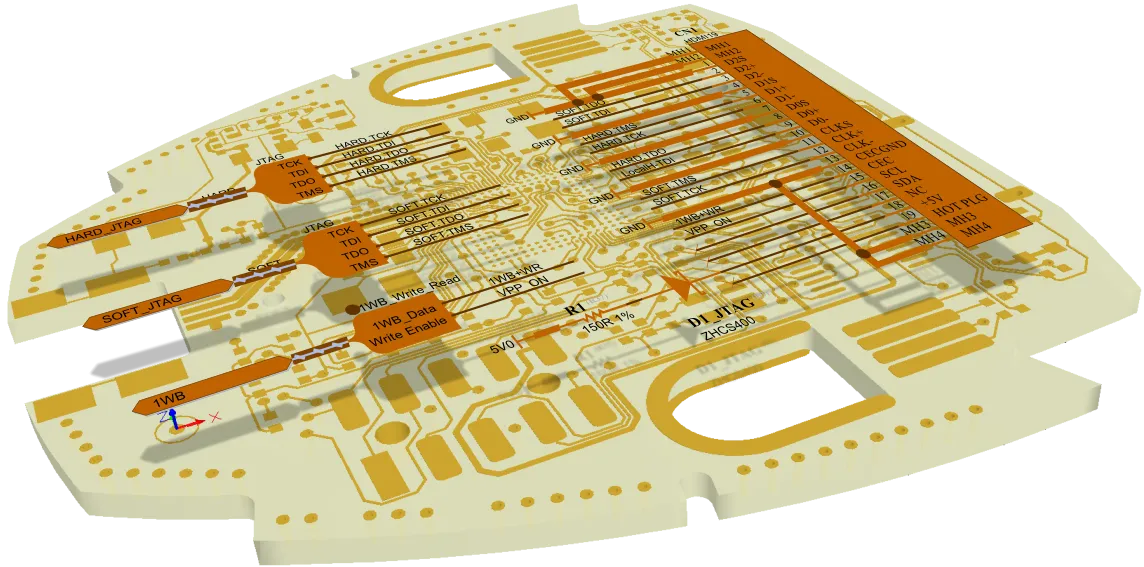

你所捕获的逻辑设计实际上从不会被扁平化;它始终保持为多通道原理图。当你将其传输到 PCB 布局时,物理器件与网络会按所需次数展开,并且你可以完整使用 Working Between the Schematic and the Board 中提供的交叉探测与交叉选择工具。PCB 编辑器中还有一个工具,可将某一通道的器件摆放与布线复制到所有其他通道,并能轻松移动与重新定向整个通道。更多关于多通道设计的内容,请参阅 multi-channel design 文档。

多通道设计必须是层次化的,因为软件使用这种结构模型在内存中实例化各个通道。

对于多通道设计,将 Net Identifier Scope 设置为 Automatic、Hierarchical 或 Strict Hierarchical。

器件与网络的复制由软件根据在 Project Options dialog 的 Multi-Channel 选项卡中选择的命名方案来解析。

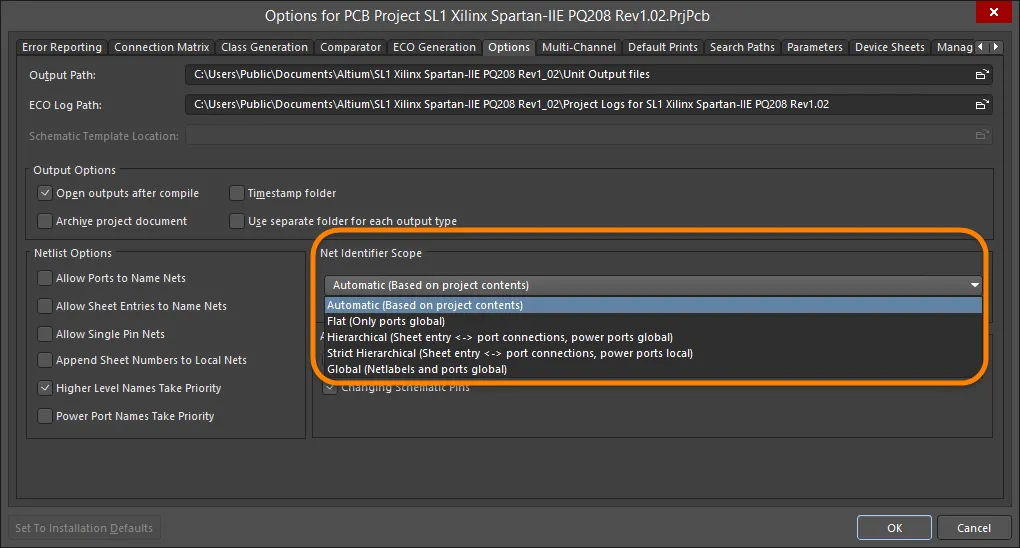

设置 Net Identifier Scope

Dialog page: Project 的选项

软件使用当前的 Net Identifier Scope 设置来确定在原理图各页之间如何建立连通性。Net Identifier Scope 在 Project Options dialog 的 Options 选项卡中配置(Project » Project Options)。

选择适合你设计结构的 Net Identifier Scope 模式。

下图展示了 Global、Flat 和 Hierarchical 选项的行为。

展示三种主要模式(Global、Flat、Hierarchical)各自如何创建连通性的简单示例。

除上述三个选项外,还有一个 Automatic 选项。通常更建议将 Net Identifier Scope 保持为 Automatic。软件会根据图纸结构以及 Ports 和 Sheet Entries 的存在/缺失,自动在三种选项中选择最合适的一种。

当设置为 Automatic 时,软件会基于以下条件自动选择三种主要 net identifier 模式中的一种:

-

如果顶层图纸上存在 sheet entries,则使用

Hierarchical。

-

如果没有 sheet entries 但存在 ports,则使用

Flat。

-

如果既没有 sheet entries 也没有 ports,则使用

Global。

Strict Hierarchical 模式会将所有电源端口本地化到各自的 sheet。在该模式下,你必须使用 Ports 和 Sheet Entries 将所有电源与地网络接到每个子页上。你也可以仅对选定的 sheet 这样做:不使用 Strict Hierarchical 模式,但仍为你想本地化的电源网络放置 Sheet Entry(s) + Port(s)。了解更多请参阅 Power Nets。

网络如何命名

每当你在器件引脚之间放置一根导线,就创建了连通性。设计中的每个网络都会被赋予一个名称。如果你没有放置可用于命名该网络的 net identifier,软件会基于该网络中的某个引脚为其命名,例如下图所示的 NetR7_1 。如果器件位号在某个阶段被更改,这个系统生成的网络名也会随之更改,并且必须在原理图与 PCB 之间传递这些更改以保持同步。

没有 net identifier 的网络会基于网络中的某个引脚被分配一个系统生成的名称。

Net Labels 总是为其所附着的网络命名。默认附着点是 Net Label 的左下角,移动时会以一个小十字标示。

对于其他 net identifiers,如果在 Project Options dialog 的 Options 选项卡的 Netlist Options 区域启用了相应选项,它们也会为网络命名。

不同类型的 net identifiers 不会自动彼此连接。例如,一个名为 的 Port 不会连接到一个名为 的 Net Label,即使在 Options dialog 的 Project 中启用了 IntaIntaAllow Ports to Name Nets 选项也是如此。它们必须通过导线连接。下图给出了示例。

同一网络上的多个 Net Identifier

在同一张原理图 sheet 内,你不能在同一网络上放置多个名称不同的 Net Label。验证时会检测到这种情况并标记为错误。不过,如果该网络出现在不同的 sheet 上,那么在不同 sheet 上为该网络放置多个 net identifier 是合法的吗。

这种能力允许你:

-

在层次结构的不同层级更改网络名称,以更好地反映它在该 sheet 上的功能。

-

复用子原理图 sheet,而无需在其上重命名网络。

默认设置是假定不允许多个 net identifiers。如果在验证期间检测到,将给出警告。如果你的设计确实需要它们,你需要执行以下之一:

-

在 Project Options dialog 的 Error Reporting 选项卡中更改

Nets with multiple names 错误检查的设置;或

-

通过放置 No ERC Marker 来抑制特定警告:在每条警告上放置标记,然后在 Properties panel 的 No ERC mode 中选择 Specific Violations 来定义要抑制的错误。注意:No ERC 标记可以通过在 Messages panel 中右键单击列出的警告,或在原理图 sheet 上右键单击标示违规的彩色波浪线来放置。选中 No ERC 标记后,可在 Properties panel 中更改其形状与颜色。

控制网络命名的选项

Dialog page: Project Options

最终,每个网络在 PCB 上只能有一个名称(除非你通过 Net Tie intentionally connecting two nets,否则一个 PCB net 不能有两个名称)。软件会自动将具有多个名称的网络解析为项目中唯一的一个名称,但这可能不是你期望的名称。在 Project Options dialog 的 Options 选项卡的 Netlist Options 区域中提供了多种选项,用于控制名称如何被选取。关于各选项的更多细节,请参阅 Project Options dialog 页面。

设置这些选项的一个良好方法是启用 Allow Ports to Name Nets 和 Higher Level Names Take Priority 选项。再结合在每张 sheet 上对重要网络合理使用 Net Labels,以确保所有重要网络(包括跨 sheet 的网络)都被命名,并且高层原理图中分配的名称会用于低层原理图。

当启用了多个网络命名选项时,网络命名的优先级如下:

-

如果 Power Port Names Take Priority 选项关闭,则顺序为:Net Labels、Power Ports、Ports、Pins。

-

如果 Power Port Names Take Priority 选项开启,则顺序为:Power Ports、Net Labels、Ports、Pins。

两个独立网络却具有相同名称

另一个可能出现的网络命名问题是:在不同原理图 sheet 上使用了相同的网络名来标注不同的网络。验证时会由 Duplicate Nets 错误检查检测到这种情况。在存在该问题时,你无法将设计传输到 PCB。设计传输期间,这两个独立网络会被合并为一个 PCB net。

可通过在 Project Options dialog 的 Options 选项卡中启用 Append Sheet Numbers to Local Nets 选项来解决。启用后,所有本地网络的名称都会附加 SheetNumber 参数的值,如下图所示。

由于网络标号 Input 已在多个 sheet 上使用,因此启用了 Append Sheet Numbers to Local Net 选项以防止 Duplicate Nets 错误。

其效果可通过单击编译后的 sheet 选项卡(右图)看到,注意网络名后附加了 _2。

Append Sheet Numbers to Local Nets 选项只有在每张原理图页都被分配了唯一的 SheetNumber 时才会生效。SheetNumber 参数是在每张原理图页的 Properties 面板中 Document Options mode 的 Parameters 选项卡上设置的 。作为手动为每张原理图页分配唯一编号的替代方案,可以运行 Tools » Annotation » Number Schematic Sheets 命令,它会打开 Sheet Numbering for Project 对话框。该对话框可用于为所有页面分配唯一的 SheetNumbers(每张页一个简单的数值)以及 DocumentNumbers(通常用于公司内部的文档编号) 。

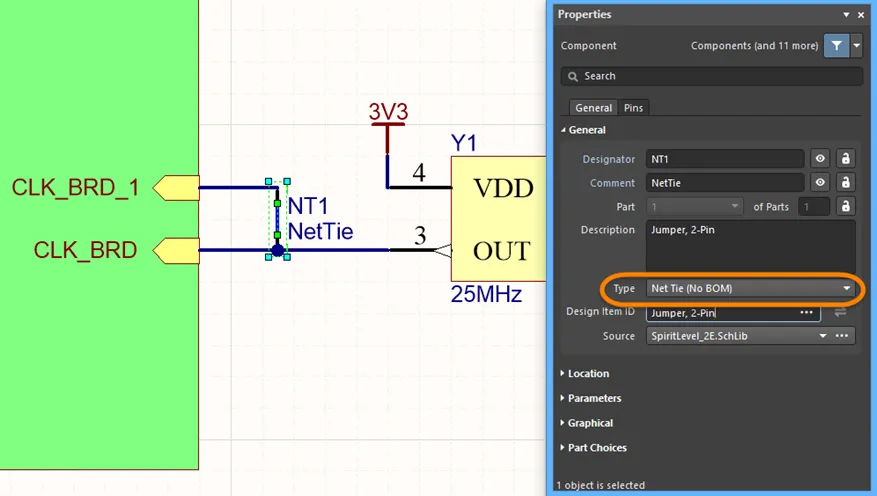

有意连接两个网络

在某些情况下,你需要有意将两个不同的网络连接在一起。这并不是一个简单的命名问题,而是出于设计要求需要将两个网络短接。例如,你可能需要以可控的方式将模拟地(Analog ground)与数字地(Digital ground)连接起来。

这可以通过使用 Net Tie 元件将两个网络连接起来实现。Net Tie 元件本质上就是一个受控的短路,让你能够决定网络在板上连接的位置。在原理图中,Net Tie 元件有两个或更多引脚,每个引脚连接到需要短接的其中一个网络。该元件的 Component Type 属性被设置为 Net Tie,如下所示。

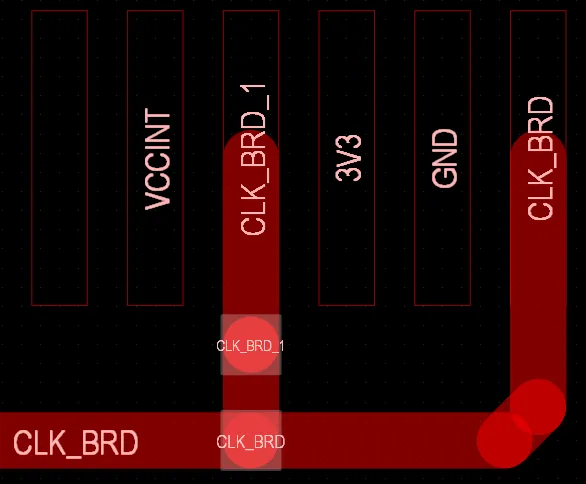

在原理图中使用 Net Tie 元件将单一路时钟布线到两个 FPGA 时钟引脚的示例。

请注意,这些引脚在原理图上并没有 not 相互连线(也就是说在原理图上并未短接),但它们会在 PCB 封装内部 are 连接在一起。

在 PCB 端,该封装具有与原理图符号引脚数量相同的焊盘,并且焊盘之间有铜连接。在下面的示例图中,这是通过用一段走线连接两个方形焊盘来实现的。这是在 PCB 库编辑器中的封装内部完成的。PCB 的 Component Type 属性同样被设置为 Net Tie。

软件会自动忽略在 Net Tie PCB 元件内部创建的短路,因此不会产生 DRC 错误。

PCB 上的同一个 Net Tie 元件;Net Tie 封装中的焊盘(已选中)通过一段走线短接。

当使用 Net Tie 元件连接两个不同网络时,每个网络在整个原理图以及 PCB 上都会保留各自的名称。

-

在创建 Net Tie 符号和封装时,有两种 Net Tie Component Type 模式:一种是将 Net Tie 包含在 BOM 中(例如 Net Tie 是一个短接跳线时),另一种是将其从 BOM 中排除(当 Net Tie 仅仅是一段铜连接时)——请选择所需的 Component Type。

-

在板上对 Net Tie 进行布线时,可以使用任意布线模式从 Net Tie 焊盘引出 away 进行布线。要对 into Net Tie 焊盘进行布线,你必须切换到 Ignore Obstacle 模式。

► Net Tie 元件布线演示

电源网络

这些设置的默认行为是假定电源网络是全局的,也就是说你希望它们在每一张原理图页上都可用。要访问某个电源网络,请放置一个带有所需网络名的 Power Port,然后将元件连线到该电源端口。当设计被编译时,项目中所有页面上连接到每个电源网络的引脚都会互相连接起来。

决定电源端口连接到哪个网络的是网络名,而不是符号的 Style——图中高亮的三个电源端口都连接到 GND 电源网络。

将电源网络本地化——全局方式

如前所述,在层次化设计中,可以通过为 Net Identifier Scope 选择 Strict Hierarchical 选项,将电源网络本地化到每张原理图页。该方法会将每一张页上的所有电源网络都本地化,因此必须使用与信号网络相同的方法手动将它们连线在一起。如果没有连线,对于每张原理图页上存在的每个电源网络都会出现一个 Duplicate Net Name 错误。你还需要调整 Connection Matrix 设置,以允许 Port 与 Power Port 连接。

如果 Net Identifier Scope 被设置为 Strict Hierarchical, 每个电源网络都必须连线到其使用到的每一张页面。

在页面之间连接已本地化的电源网络

在层次化设计中,连接已本地化的电源网络的方法与其他网络相同:从子页上的 port 连接到父页 sheet symbol 上的 sheet entry。注意:对于电源网络,该技术只支持单个电源网络,不支持将多个电源网络打包成总线( )的情况。

)的情况。

如果你正在创建多通道设计,并希望使用 Repeat 语句(如下所示)为每个通道提供唯一、独立的电源网络,这是受支持的,因为你只是通过 sheet entry-port 组合向每个通道传递一个网络。只要设计仅尝试通过每个 sheet entry-port 组合将单个电源网络从父级传递到子级,就能正确生成网表。

在多通道设计中,只要本地化电源网络在层次结构中以上下传递的“单个网络”形式传输,而不是以总线形式传输,就可以分发到每个通道。

在多通道设计中,只要本地化电源网络在层次结构中以上下传递的“单个网络”形式传输,而不是以总线形式传输,就可以分发到每个通道。

如果你更倾向于将多个电源网络打包成总线并通过设计层次结构传递该总线,那么这些网络必须是标准网络,不能使用电源端口进行连接。

将电源网络本地化——单独方式

在层次化设计中,某个特定电源网络 (即:在 Net Identifier Scope 被设置为 Hierarchical 的设计中,或在顶层页包含 sheet entries 且 的 Net Identifier Scope 被设置为 Automatic 的设计中——更多信息请参阅 Setting the Net Identifier Scope) 也可以通过将 Power Port 连接到该原理图页上的 Port,从而在特定页面上 单独本地化。

这里 3V3 电源网络仅对这一张页进行了本地化,因此也必须在父页上手动连线。GND 和 5V 网络仍然保持为全局电源网络。

电源网络与隐藏电源引脚

较旧版本的 Altium 设计软件包含用于支持隐藏原理图元件引脚的功能与选项。当设计只有一个电源网络和一个地网络时,这个功能很有用:通过隐藏这些电源引脚,所有器件上的电源引脚就能自动连接到各自的网络。它在多分部件(multi-part)元件上最为常用,使你无需在原理图上显示这些元件的电源引脚。

如今,电子设计通常具有多个电源与地网络。这些网络不再只是简单地连到相应的电源引脚;电源传输如今已成为成功板级设计的关键环节。

随着 power delivery networks 的设计方式发生变化,隐藏元件引脚并让软件自动连接它们的需求已经大幅下降,以至于大多数设计人员都反对这种做法。因此,软件不再支持将引脚定义为隐藏并预先分配其网络名。采用这种设计方式的旧项目在最新版本的 Altium 设计软件中打开时,仍然可以正确生成网表。

动态编译

Related page: 验证你的设计项目

当你用导线连接两个引脚时,你是在表达设计意图,而不是创建一个实际的网络。网络要到项目编译后才会创建。编译不仅会提取元件及其连接方式的细节,还会提取详细的元件与设计参数信息。项目的编译模型被称为统一数据模型(Unified Data Model)。

通过动态编译,设计数据模型会在每次用户操作后进行增量更新——从而形成所谓的动态数据模型(Dynamic Data Model,DDM)。不需要手动编译项目,全部由系统自动完成。借助动态编译,设计连通性模型会在每次用户操作后增量更新。对于一个设计项目,自动编译过程执行三项功能:

-

实例化设计层次结构。

-

建立所有设计页面之间的网络连通性。

-

构建设计的内部动态数据模型(DDM)。

这确保任何设计更改都会立即反映在 Navigator 以及 Projects panel 中。

为了检查 DDM 与编译器设置之间的逻辑、电气以及绘图错误,你必须验证项目。可通过主菜单选择 Project » Validate Project 命令访问该功能,或在 Projects 面板中对项目条目右键,并从上下文菜单中选择 Validate Project 命令。

编译器检测到的任何违规项都会以警告和/或错误的形式列在 Messages 面板中。编译器在检查源文档违规项时,会使用 Project Options dialog 的 Error Reporting 与 Connection Matrix 选项卡中定义的选项(视项目类型而定)。

动态数据模型

软件的一个基本要素是统一数据模型(Unified Data Model,UDM)。通过动态编译的自动实例化,会创建一个单一、连贯的模型,并将其置于设计流程的核心。模型中的数据可被软件内的各类编辑器和服务(包括原理图与 PCB)访问与操作。UDM 并非为不同的设计领域分别使用独立的数据存储,而是被构建为能够容纳设计各方面的全部信息,包括元器件及其互连关系。这个位于设计流程中心的单一、连贯模型,是动态设计编译的结果。这意味着从打开项目的那一刻起,统一数据模型就已可用,并且不应需要额外的手动编译——这才是真正的动态数据模型(Dynamic Data Model,DDM)。因此,模型会在每次用户操作后进行增量更新(编译)。你可以在原理图设计中自由放置、连线、重新排列、重命名、添加以及删除内容。

PCB 设计编译过程由原理图与 PCB 编辑器之外的代码进行管理。这种方式有多项优势,其中最大的一点是:设计的统一数据模型独立于各自的原理图与 PCB 编辑器之外。UDM 包含对设计中每个元器件的详细描述,以及它们彼此之间如何连接。

软件负责管理跨原理图与 PCB 的互连数据。

由于编译是动态的,以下位置与操作在设计编译方面不需要任何额外的手动操作:

-

Navigator 和 Projects 面板

-

ActiveBOM

-

执行 ECO

-

交叉探测(Cross-probing)

-

网络颜色高亮

-

引脚互换(Pin swapping)

-

元器件交叉引用

要在动态编译后刷新项目视图和 Navigator 面板,请在 Projects 与 Navigator 面板的右键菜单中使用 Refresh 命令。要在动态编译后自动刷新项目视图和 Navigator 面板,请在 Advanced Settings dialog 中启用 Schematic.DynamicCompiler.Navigator.Autorefresh 选项。

放置一个 compile mask,用于 hide 设计中尚未准备好进行错误检查或传输到 PCB 编辑器的部分。当你准备就绪时,点击控件折叠该遮罩,使电路显露出来,从而被纳入编译过程与设计传输。

Compile mask 属于一类称为 design directives 的对象。使用它们可向原理图添加设计级指令(direction),例如:指定网络类成员关系、标识编译器应忽略某个特定违规的位置、标识一组网络为差分对等。将鼠标悬停在图片上可查看 compile mask 的演示。

那么你如何与统一数据模型交互,例如在设计中追踪一条网络?你可以通过 Navigator 面板来完成。

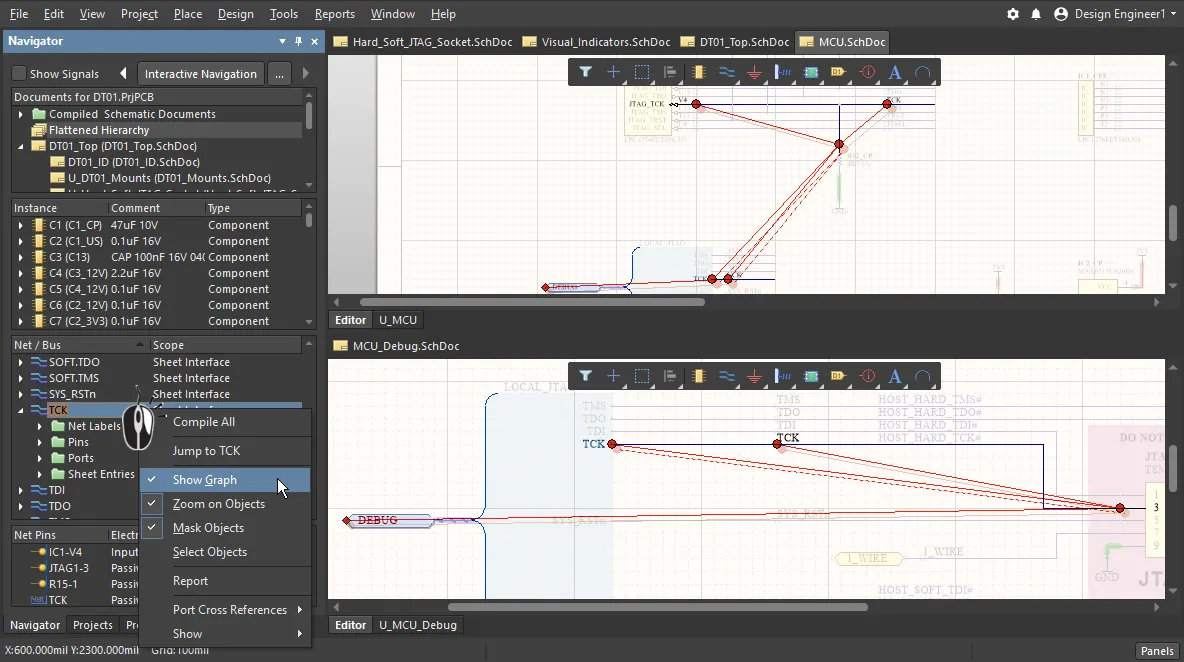

检查连通性

Panel page: Navigator panel

如果设计规模很大并分布在许多图纸上,就会难以跟踪并验证设计中的连通性。为帮助完成这一过程,你可以使用 Navigator panel 。该面板提供整个已编译设计的视图。

使用该面板的基本方法是:

-

通过点击面板顶部的

按钮打开 Preferences 对话框并启用你偏好的 Highlight Methods,以设置浏览行为。或者,在面板中右键单击感兴趣的对象,并使用菜单选项配置导航行为,如下图所示。

按钮打开 Preferences 对话框并启用你偏好的 Highlight Methods,以设置浏览行为。或者,在面板中右键单击感兴趣的对象,并使用菜单选项配置导航行为,如下图所示。

-

在面板的 Documents for 区域设置浏览范围;要浏览整个设计请选择

Flattened Hierarchy。

-

在列表的 Instance 部分单击某个元器件即可跳转到该元器件;展开元器件以定位或跳转到某个引脚。

-

在 Net /Bus 部分单击某条网络或总线即可跳转到该网络或总线。

-

按住 Alt 键并单击,可在原理图与 PCB 上同时跳转到该对象。

在 Navigator 面板中单击元器件或网络即可定位该元器件或网络,并在设计中追踪连通性。右键可访问显示选项。将光标悬停在图片上可显示同时导航到原理图与 PCB 上的某个元器件(在 Navigator 面板中单击时按住 Alt 以包含 PCB 对象)。

在板上导航元器件

除了可从 Navigator 面板定位原理图与 PCB 上的元器件(若按住 Alt)之外,你还可以直接从原理图在 PCB 上导航引脚/元器件/网络/总线/线束(harness)。

例如,当你单击以在原理图上定位某个元器件时,也可以同时在 PCB 上定位同一个元器件。

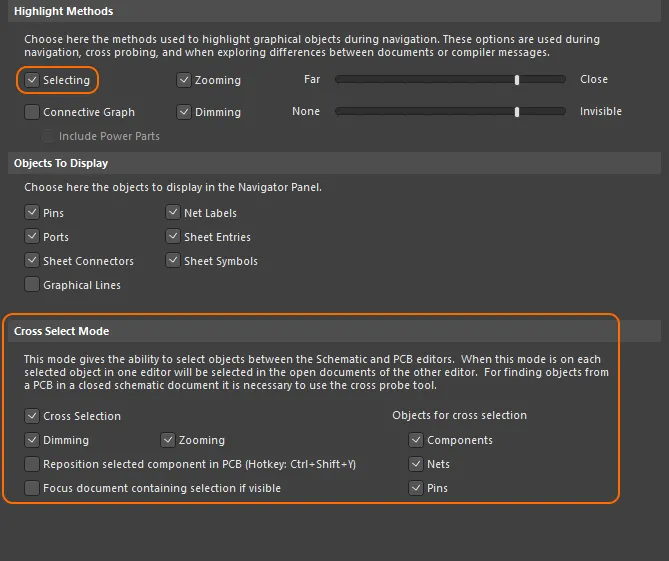

操作方法:

-

在 Highlight Methods 中启用 Selecting 选项,并在 Preferences 对话框的 System - Navigation 页面中,于 Cross Select Mode 区域启用你偏好的选项。

-

在原理图与 PCB 编辑器中都启用交叉选择(Cross Selection,Tools » Cross Select Mode)。

这些选项用于配置导航与交叉选择行为。

现在,当你在原理图上选择引脚/元器件/网络/总线/线束时,这些对象也会在 PCB 上被选中,如下图所示。

在原理图上选择元器件与网络时,这些对象也会在 PCB 上被选中。交叉选择同样支持从 PCB 到原理图。

在项目结构中搜索元器件与网络

在面板中浏览结构以找到感兴趣的元器件或网络,然后双击该对象以在项目的原理图文档中显示该对象的实例。使用 Preferences 对话框的 System - Navigation 页面上的选项来指定对象高亮行为(缩放、变暗、选择等)。

在设计空间中右键单击并选择 Clear Filter 选项,以移除原理图或 PCB 编辑器中的对象高亮/选择。

项目对象导航也可在 Navigator panel 中使用,该面板提供设计对象及其关联数据的详细层级结构。System - Navigation 首选项设置决定 Project 与 Navigator 面板的对象高亮行为。

连接高亮

连通性导航选项会显示在 Projects 面板中所选对象的连接关系。在面板的对象层级列表中双击某个条目(例如 Net),即可在原理图中高亮其互连关系。

预览功能由 Preferences 对话框的 System – Navigation 页面中 Highlight Methods 区域的 Connectivity Graph 选项启用。勾选额外的 Include Power Parts 选项,还可查看与所选对象相关联的电源对象的连通性。

全局网络高亮

在整个设计中,可通过在选择网络时按住 Alt 键并单击一段导线(Alt+Click)来在所有原理图中高亮该网络的连通性。该网络在原理图中的所有实例都会被高亮,其他对象会变暗,从而通过一个简单动作直观显示信号/电源在设计中的传播路径。

在空白处单击可清除网络高亮,其行为由 Preferences 对话框的 System - Navigation page 上的 Highlight Methods 设置决定。注意,取消勾选 Dimming 选项将禁用网络高亮功能。

交叉探测与交叉选择

除了能够在两个编辑器之间进行选择(交叉选择)之外,Altium Designer 还支持交叉探测(Cross Probing)。交叉探测有两种模式:连续模式(停留在源编辑器)与跳转模式(跳转到目标编辑器)。你也可以从各种面板与对话框进行交叉探测,例如 Messages 面板与 Engineering Change Order 对话框。要了解更多,请参阅 Cross Probing and Selecting 页面。

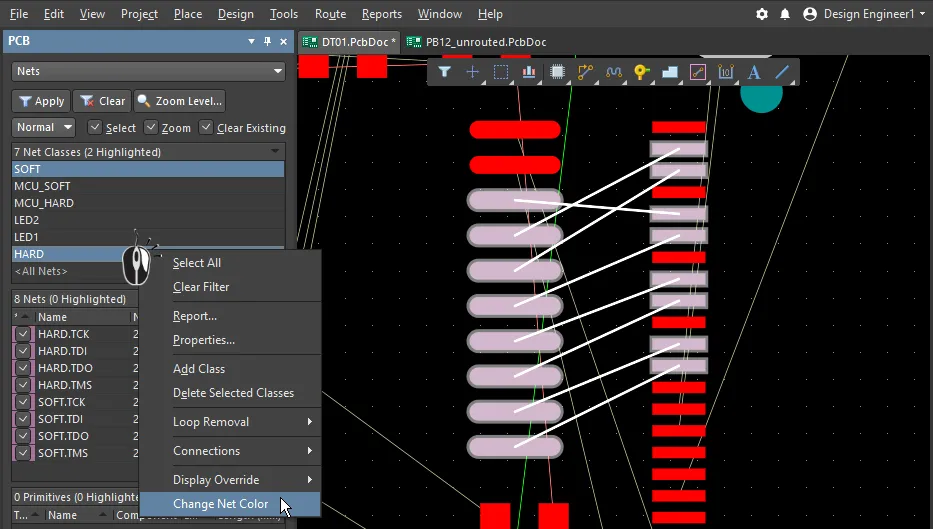

配置网络颜色

Main page: 为网络应用颜色

为提高原理图可读性,并让在 PCB 编辑器中处理网络与布线更容易,可以为原理图导线以及 PCB 网络与走线应用颜色。

在原理图编辑器中,可使用 View » Set Net Colors 子菜单中的命令为网络或总线应用高亮颜色,如下图所示。 这些颜色可随时通过 Update PCB 命令传输到 PCB 编辑器。

在 PCB 编辑器中,Connection Lines 的默认颜色与可见性在 PCB View Configuration panel 的 System Colors 区域中配置。注意:该默认颜色会在创建网络时(从原理图初次传输设计期间)应用;如果更改此选项,现有连接线的颜色不会改变。

在 PCB 编辑器中,每条网络所应用的颜色会显示在 PCB 面板的 Nets mode 中。请查看网络名称旁复选框后面的颜色,如下图右下角所示。

颜色始终会应用到未布线的网络(连接线)上。要在已布线的网络上显示颜色,请在 PCB 面板中勾选网络名称旁的复选框,并在 Preferences 对话框的 Board Insight Color Overrides 页面中配置显示选项。在下图中,覆盖颜色的 Base Pattern 设置为 Solid,Zoom Out Behavior 设置为 Override Color Dominates。

原理图中应用的网络颜色会通过 Update PCB 命令传递到 PCB。请配置 PCB Color Override 功能,以控制它们在板上的显示方式。

原理图中应用的网络颜色会通过 Update PCB 命令传递到 PCB。请配置 PCB Color Override 功能,以控制它们在板上的显示方式。

按下 F5 可在原理图与 PCB 编辑器中切换 Net Color Override 功能的开启/关闭。你可能还需要执行一次屏幕刷新(End)。

更改 PCB 网络的颜色

并非总能将原理图布线的颜色应用并传递到 PCB。在这种情况下,仍然可以在 PCB 编辑器中对连接线和走线应用颜色。要在设计已传递后更改某个网络的颜色,请在 PCB 面板的 Nets 模式下双击网络名称。单个网络的颜色可在 Edit Net dialog 中编辑。

要更改多个网络的颜色,请使用 PCB 面板的 Nets 模式:

-

使用标准的 Windows 多选方式(Shift+click 或 Ctrl+click)选择多个网络类或多个单独网络。

-

在选中的对象上右键,从上下文菜单中选择 Change Net Color 命令,为所选网络分配新颜色。

-

再次右键并选择 Display Override » Selected On,为所选网络启用颜色覆盖功能。

通过更改网络连接线的颜色并启用显示覆盖功能,可提升网络的可见性。

AI 翻译

AI 翻译