PCB エディターはルール駆動型の設計環境であり、基板の完全性を確保するためにチェックできるさまざまな種類の設計制約を定義できます。オンライン DRC 機能は、作業中に有効化されているルールを監視し、検出された設計違反を即座に強調表示します。あるいは、バッチ DRC を実行して、設計がルールに準拠しているかをテストし、有効なルールと検出された違反の詳細を記載したレポートを生成することもできます。

このチュートリアルの前半では、電気的クリアランス、配線幅、配線ビア スタイルなど、いくつかの設計制約を確認して設定しました。これらに加えて、新しい基板を作成したときに自動的に定義される設計ルールがほかにも多数あります。

設計ルールチェック(DRC)の設定と実行

Main page: DRC の設定と実行

設計ルールチェック(DRC)を実行することで、設計内の違反がチェックされます。オンライン DRC とバッチ DRC はどちらも、メイン メニューから Tools » Design Rule Check コマンドを選択して開く Design Rule Checker ダイアログで設定します。

設計ルールチェックは、ダイアログ下部の  ボタンをクリックして実行します。DRC が実行されると、Messages パネルが開き、検出されたすべての違反が一覧表示されます。ダイアログで Create Report File オプションが有効になっている場合は、Design Rule Verification Report が別のドキュメント タブで開きます。このレポートには、チェック対象として有効になっているルール、検出された違反数、および各違反の詳細が記載されます。

ボタンをクリックして実行します。DRC が実行されると、Messages パネルが開き、検出されたすべての違反が一覧表示されます。ダイアログで Create Report File オプションが有効になっている場合は、Design Rule Verification Report が別のドキュメント タブで開きます。このレポートには、チェック対象として有効になっているルール、検出された違反数、および各違反の詳細が記載されます。

-

メイン メニューから Tools » Design Rule Check コマンドを選択して、Design Rule Checker ダイアログを開きます。

-

ダイアログの Report Options ページで、Create Report File オプションが有効になっていることを確認します。

-

ダイアログの Rules To Check ページで、グリッド領域内を右クリックし、Batch DRC - Used On エントリを選択します。

-

テストポイント ルールのバッチ DRC を無効にします。これを行うには、ツリー内の Testpoint セクションを選択し、このカテゴリ内の 4 つのルール タイプについて Batch チェックボックスをオフにします。

-

ダイアログ下部の  ボタンをクリックして DRC を実行します。Design Rule Checker ダイアログが閉じ、レポートが開きます。これには少なくとも次の内容が含まれます。

ボタンをクリックして DRC を実行します。Design Rule Checker ダイアログが閉じ、レポートが開きます。これには少なくとも次の内容が含まれます。

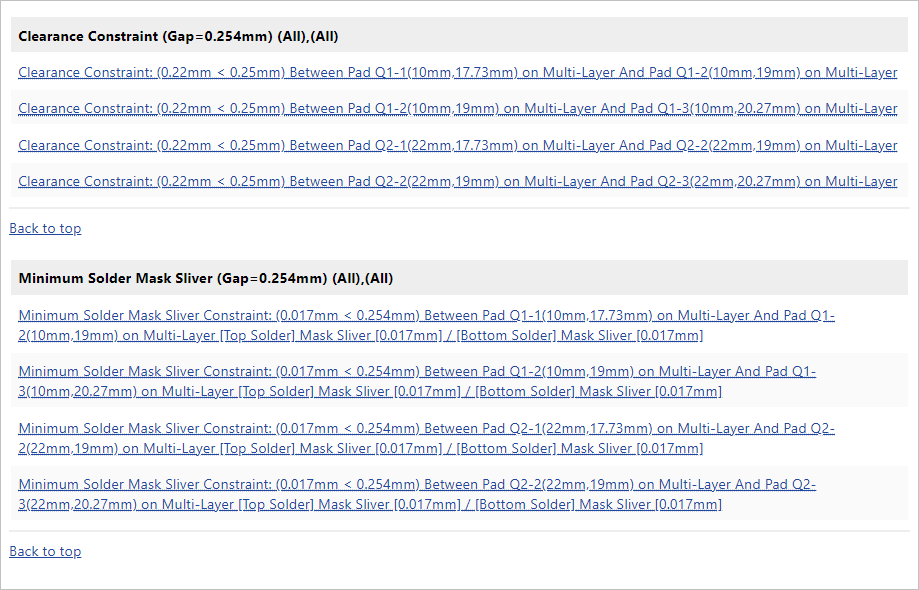

レポートの上部セクションには、チェック対象として有効になっているルールと、検出された違反数が記載されます。ルールをクリックすると、その違反箇所へジャンプして確認できます。

レポートの下部セクションには、違反している各ルールと、それに続く問題のあるオブジェクトの一覧が表示されます。違反エントリをクリックすると、PCB 上のそのオブジェクトへジャンプできます。

検出された違反は、開いた Messages パネルにも一覧表示されます。

違反の特定と解決

Main page: 設計違反の調査と解決

設計者として、PCB 上で違反箇所を特定し、その状態と実際にどの程度ルールを満たしていないかを把握し、最も適切な解決方法を見つける必要があります。

違反の特定と解決に関する注意事項

-

Altium Designer には、設計ルール違反を表示するための 2 つの方法があります。

以下にクリアランス違反の例を示します。上記 2 つの方法の両方を使って違反を示しています。問題のあるパッドはパターン表示で強調されます。また、白い矢印と <0.25mm テキストによっても違反が示されており、このギャップが制約で許可されている最小値 0.25 mm を下回っていることがわかります。

-

違反を特定するには、レポート ファイルの下部セクションにある個別の違反を示すリンクをクリックするか、Messages パネル内のエントリをダブルクリックします。

-

レポートおよび Messages パネル内の違反エントリには、違反がどの程度ルールを満たしていないかの詳細も含まれます。実際の値は、指定された制約値とともに表示されます(例: 0.017mm < 0.254mm)。

クリアランス違反の解決

このチュートリアル設計では、トランジスタ フットプリントのパッド間にクリアランス制約違反が 4 件あります。これらの違反を解決する方法は 2 つあります。

0.25 mm のクリアランスはかなり余裕があり、実際のクリアランスもこの値(0.22 mm)にかなり近いため、この場合は、より小さいクリアランスを許可するようにルールを設定するのが適切です。この解決策がこの状況で許容できるのは、スルーホール パッドを持つほかの唯一の部品がコネクタであり、そのパッド間隔が 1 mm あるためです。もしそうでない場合は、ソルダー マスク拡張ルールで行ったように、トランジスタ パッドだけを対象とする 2 つ目のクリアランス制約を追加するのが最善の解決策です。

-

デザイン スペース上部の PCB ドキュメント タブをクリックして、アクティブ ドキュメントにします。

-

メイン メニューから Design » Constraint Manager コマンドを選択して Constraint Manager を開きます。

-

Constraint Manager の Clearances ビューで、クリアランス マトリクス内の All Nets / All Nets セルをクリックします。

-

下部のグリッド領域で TH Pad – to – TH Pad の値を 0.22 mm に変更します。これを行うには、セルをクリックして 0.22 と入力し、Enter を押します。

-

Constraint Manager で変更を保存します(File » Save to PCB)。

最小ソルダー マスク スリバー違反の解決

ソルダー マスクは、基板の外表面に塗布される薄いラッカー状の層で、銅箔を保護し絶縁する被覆を提供します。部品や配線を銅箔にはんだ付けできるように、マスクには開口部が設けられます。PCB エディターでソルダー マスク層上のオブジェクトとして表示されるのは、この開口部です(ソルダー マスク層はネガティブ定義である点に注意してください。つまり、表示されているオブジェクトが実際のソルダー マスクでは穴になります)。

製造時には、ソルダー マスクはさまざまな方法で塗布されます。最も低コストな方法は、マスクを通して基板表面にシルクスクリーン印刷する方法です。層の位置合わせのずれに対応するため、マスク開口部は通常パッドより大きく作られます。これは、デフォルトの設計ルールで使用されている 4 mil(約 0.1 mm)の拡張値に反映されています。

はんだマスクの適用には、より高品質なレイヤー位置合わせと、より正確な形状定義を実現できる別の手法もあります。これらの手法を使用する場合、はんだマスクの拡張量はより小さく、場合によってはゼロにすることもできます。マスク開口を小さくすると、はんだマスクの細片やシルクとはんだマスクのクリアランス違反が発生する可能性を低減できます。

はんだマスク細片違反。紫色は各パッド周囲のはんだマスク拡張を表します。

最小はんだマスク細片違反の詳細を確認するには、はんだマスクの表示を有効にする必要があります。レイヤーの表示/非表示は View Configuration パネルで設定します。

このようなはんだマスクの問題は、完成基板の製造に使用される加工技術を考慮せずに解決することはできません。

たとえば、これが高価値製品向けの複雑な多層基板であれば、高品質なはんだマスク技術が採用される可能性が高く、その場合は小さい、あるいはゼロのはんだマスク拡張が可能です。しかし、このチュートリアルの基板のようなシンプルな両面基板は、低コスト製品として製造される可能性が高く、低コストのはんだマスク技術を使用する必要があります。つまり、基板全体のはんだマスク拡張を減らしてはんだマスク細片違反を解消するのは、適切な解決策ではありません。

PCB設計の多くの側面と同様に、解決策は影響を最小限に抑えるよう、的を絞って慎重にトレードオフを行うことにあります。

この違反を解消するには、次の方法があります。

これは、部品に関する知識、および使用予定の製造技術と実装技術を踏まえて行う設計判断です。マスク開口を広げてトランジスタのパッド間のマスク細片を完全になくすと、それらのパッド間に半田ブリッジが発生する可能性が高くなります。一方、マスク開口を小さくすると細片は残りますが、それが許容されるかどうかは状況によります。また、マスクとパッドの位置ずれの問題が生じる可能性もあります。

このチュートリアルでは、2番目と3番目の方法を組み合わせて使用します。つまり、この基板で使用している設定に適した値まで最小細片幅を小さくし、さらにトランジスタのパッドに対してのみマスク拡張を小さくします。

-

最初の手順は、許容される細片幅を小さくすることです。Constraint Manager 上部の対応するボタンをクリックして、All Rules ビューを開きます。

-

左側のツリーで、Manufacturing カテゴリ内の Solder Mask Sliver ルールタイプを見つけて選択し、メイングリッド領域で既存の MinimumSolderMaskSliver というルールを選択します。

-

このような設計では、パッド間隔 0.22 mm(約 8.7 mil)と同じ値であれば許容できます。ルールの制約領域で、Minimum Solder Mask Sliver の値を 0.22 に編集します。

-

次の手順では、トランジスタ専用のマスク拡張ルールを追加し、マスク拡張をゼロにします。これにより、はんだマスクの開口はパッドと同じサイズになり、パッド間のはんだマスク細片の幅はパッド間隔(0.22 mm)と等しくなります。左側ツリーの Mask カテゴリにある Solder Mask Expansion ルールタイプをクリックして、このタイプの既存ルールを表示します。SolderMaskExpansion というルールが 1 つあり、拡張値 0.1016 mm(4 mil)を指定しているはずです。

違反しているのはトランジスタのパッドだけなので、この値は編集しません。代わりに、新しいルールを作成します。

-

新しい Solder Mask Expansion ルールを追加するには、メイングリッド領域の空いている場所を右クリックし、コンテキストメニューから Add Custom Rule を選択します。SolderMaskExpansion_1 という新しいルールが作成されます。

-

メイングリッド領域で新しいルール名をダブルクリックし、名前を SolderMaskExpansion_Transistor に変更します。

-

ルールをクリックして、Constraint Manager 下部にその設定を表示します。

-

新しいルールの適用範囲を定義します。適用範囲クエリは Query Builder 機能を使用して作成できます。Object Match フィールドの横にある  ボタンをクリックし、Open Query Builder コマンドを選択します。開いた Building Query from Board ダイアログで、Condition Type / Operator 列のドロップダウンから Associated with Footprint を選択し、次に Condition Value 列のドロップダウンから ONSC-TO-92-3-29-11 を選択します。ダイアログで OK をクリックすると、クエリ

ボタンをクリックし、Open Query Builder コマンドを選択します。開いた Building Query from Board ダイアログで、Condition Type / Operator 列のドロップダウンから Associated with Footprint を選択し、次に Condition Value 列のドロップダウンから ONSC-TO-92-3-29-11 を選択します。ダイアログで OK をクリックすると、クエリ HasFootprint('ONSC-TO-92-3-29-11') が Object Match フィールドに表示されます。

❯ ❮

Javascript ID: Tutorial_CM_SolderMaskExpansion_New_Query_AD25_2

|

-

0 を Expansion top と Expansion bottom の値に設定します。

-

Constraint Manager で変更を保存します(File » Save to PCB)。

-

デザインスペース上部のタブを右クリックし、コンテキストメニューから Close Multivibrator.PcbDoc [Constraints] コマンドを選択して Constraint Manager を閉じます。

-

Projects パネルで PCB ドキュメントのエントリを右クリックし、コンテキストメニューから Save を選択して、PCB ドキュメントをローカルに保存します。

違反解消後にデザインルールチェックを実行する

次に、すべての違反が解消されたことを確認するため、DRC を再実行します。

出力を生成する前に、必ずクリーンな Design Rule Verification Report であることを確認してください。

-

Design Rule Checker ダイアログを開き(Tools » Design Rule Check)、Report Options ページで Create Report File オプションが有効になっていることを確認します。

-

ボタンをクリックします。

ボタンをクリックします。

-

新しいレポートが生成され、別のドキュメントタブで開きます。ルール違反が含まれていないことを確認してください。

違反がある場合はそれらを解消し、再度レポートを生成します。

-

生成された DRC レポートをプロジェクトから削除します。このレポートは設計リリース処理中に生成されます。これを行うには、Projects パネルの Generated\Documents エントリの下にあるレポートファイルを見つけて右クリックし、Remove from Project コマンドを選択します。開いた Remove from project ダイアログで、Delete file オプションを選択します。

-

現在開いているすべてのドキュメントを閉じます。これを行うには、デザインスペース上部のドキュメントタブを右クリックし、コンテキストメニューから Close All Documents コマンドを選択します。

-

Projects パネルのプロジェクトエントリの横にある Save to Server コントロールをクリックし、開いた Save to Server ダイアログの Comment フィールドに意味のあるコメント(例: PCB design complete)を入力して、OK ボタンをクリックし、プロジェクトを Workspace に保存します。

よくできました。これで PCB が制約に適合していることを確認できたので、PCB 図面を作成 する準備が整いました。