Setting Up & Running a DRC

Altium Essentials: PCB Design Rule Checks

This content is part of the official Altium Professional Training Program. For full courses, materials and certification, visit Altium Training.

DRC の設定

デザインルールチェックの設定は、PCB ドキュメントから Tools » Design Rule Check コマンドを使用して開く Design Rule Checker ダイアログで行います。

Design Rule Checker ダイアログには、PCB エディターのパフォーマンス向上のために一部の Online DRC チェックを無効にした既定設定が表示されます。関連するオプションを使用して、Online DRC および/または Batch DRC のチェック対象に含めるデザインルールタイプを指定します。

ダイアログ左側のフォルダーツリーペインには、チェック可能な各デザインルールカテゴリが Rules To Check フォルダの下に一覧表示されます。この最上位フォルダをクリックすると、チェック可能なすべてのルールタイプがダイアログ右側に表示されます。あるいは、その下の特定カテゴリをクリックすると、そのカテゴリに関連付けられたデザインルールタイプのみが表示されます。チェックしたい各ルールタイプについて、このダイアログで Online(利用可能な場合)および/または Batch Mode チェックを有効/無効にします。

Online DRC の使用

Online Design Rule Checking はバックグラウンドでリアルタイムに動作し、デザインルール違反を通知し、または自動的に防止します。これは、基板を interactively routing している際に、クリアランス、幅、平行セグメントの違反を即座に強調表示できるため、特に便利です。ルールを Online DRC の対象にするには、次の 3 つの要件を満たす必要があります。

-

ルールが有効になっていること。これは、PCB Rules and Constraints Editor dialog でそのルールの Enabled オプションがチェックされていることを確認するか、PCB Rules and Violations panel でそのルールの On オプションがチェックされていることを確認することで設定できます。

Online DRC で監視したいデザインルールが、実際に設計で使用できるよう有効になっていることを確認してください。

Online DRC で監視したいデザインルールが、実際に設計で使用できるよう有効になっていることを確認してください。

-

ルールタイプが Design Rule Checker ダイアログでオンラインチェック用に有効になっていること。

ルールタイプが Online DRC 用に有効になっていることを確認してください。

ルールタイプが Online DRC 用に有効になっていることを確認してください。

-

Online DRC 機能自体がオンになっていること。これは、Preferences ダイアログの PCB Editor - General page にある Online DRC オプションを有効にすることで設定します。

Online DRC 機能が有効になっていることを確認してください。

Online DRC 機能が有効になっていることを確認してください。

オンラインチェック用に有効化された適用可能なデザインルールに違反しているオブジェクトが見つかった場合、それらは定義済みの violation display options に従って設計空間内でハイライト表示されます。

Batch DRC の使用

Online DRC は新しい違反、つまり機能を有効にした後に作成された違反しか検出しませんが、Batch DRC では基板設計プロセス中の任意のタイミングで手動チェックを実行できます。そのため、優れた設計者は Online DRC の価値を理解している一方で、基板設計は Batch DRC で始まり、Batch DRC で終えるべきことも理解しています。

必要に応じて、Design Rule Checker ダイアログでバッチチェック用のルールタイプを有効にします(Configuring the DRC セクションを参照)。Batch DRC の実行時には、レポートファイルを生成する機能を含むさまざまな追加オプションを利用できます。これらのオプションには、ダイアログのフォルダーツリーペインで Report Options フォルダをクリックしてアクセスします。主な 2 つのオプション(以下の画像で強調表示)は次のとおりです。

-

Create Report File - このオプションを有効にすると、基板に対して Batch DRC を実行した後にレポートが生成されます。生成されるレポートに PCB Health Check Monitor によって検出された問題も含めるには、Report PCB Health Issues サブオプションを有効にします。

レポートは HTML 形式で、ファイル名は

Design Rule Check - <PCBDocumentName>.htmlになります。Batch DRC プロセスの完了後、自動的にアクティブドキュメントとして開かれます。 -

Create Violations - このオプションを有効にすると、違反が定義済みの violation display options に従って設計空間内でハイライト表示されます。このオプションは、違反を PCB Rules And Violations panel の Violations 領域に一覧表示するためにも必要です。

Batch DRC の実行および DRC レポート生成に関するオプションへのアクセス。

Batch DRC の実行および DRC レポート生成に関するオプションへのアクセス。

その他の利用可能なオプションは次のとおりです。

-

Sub-Net Details – Un-Routed Net ルールが定義されている場合、このオプションを有効にすると DRC レポートにサブネットの詳細が含まれます。

-

Verify Shorting Copper – このオプションを有効にすると、設計で使用されている Net Tie コンポーネント内の短絡用銅箔の完全性を検証します。このチェックでは、コンポーネント内に未接続の銅箔がないかを確認します(これは、あるパッドが他のパッドを正しく短絡していないことを示します)。

-

Report Drilled SMT Pads – このオプションを有効にすると、誤って穴あけされた SMT(Surface Mount Technology)パッドを DRC レポートに含めます。

-

Report Multilayer Pads with 0 size Hole – このオプションを有効にすると、設計内で見つかった無効なマルチレイヤーパッドを含めます。無効なマルチレイヤーパッドとは、穴サイズがゼロで、そうでなければ SMT パッドになるものを指します。

-

Stop when n violations found – このフィールドでは、Batch DRC プロセスを停止する前に検出できる違反の最大数を指定します(既定値 =

500)。報告される違反数を制限することは、チェックプロセスを管理しやすく保つための重要な戦略です。 -

Report Broken Planes – このオプションを有効にすると、バッチルールチェック処理で broken plane を検出して報告します。broken plane は、ネットに接続されているプレーン領域の一部が、プレーンの残り部分から電気的に切り離されたときに発生します。たとえば、分割プレーンをまたいで配置されたコネクタが、そのプレーンに接続されていない場合に発生することがあります。ピン周囲のボイドがつながってプレーン銅箔を完全に横切り、結果としてプレーンが 2 つに分断されます。

-

Report Dead Copper larger than – このオプションを有効にすると、バッチルールチェック処理で、指定した面積より大きい dead copper 領域を検出して報告します。dead copper とは、ネットへの接続がなく、かつ元の親プレーンからも電気的に切り離された銅箔領域を指します。たとえば、プレーンに接続されていないコネクタのピン間隔が狭い場合、ピン周囲のボイドがつながってプレーン銅箔の一部をプレーンの残り部分から孤立させることがあります。関連フィールドを使用して、許容される dead copper の最大面積を指定します。これを超えるとルール違反と見なされます(既定値 =

100 sq. mils)。 -

Report Starved Thermals with less than n% available copper – このオプションを有効にすると、バッチルールチェック処理で、指定した割合より大きい「starved」なサーマル接続を検索してレポートします。サーマルとは、平面銅箔への熱伝導を低減するために、その周囲にサーマルリリーフの「切り欠き」を設けたプレーンへの接続です。プレーンに接続する銅スポークの表面積がボイド領域によって減少すると、サーマルは「starved」状態になることがあります。このオプションでは、サーマルに侵入するボイド領域に対して、スポークだけでなくサーマル自体の表面積もチェックします。関連フィールドを使用して、接続銅箔として最低限残っていなければならない許容最小割合の値を指定してください。これを下回るとルール違反と見なされます(デフォルト =

50%)。 -

Run Design Rule Check – このボタンをクリックすると、Batch チェック用に有効化されたルールと、この種のチェック用に定義された追加オプションに従って Batch DRC を実行します。

バッチモード DRC は、ダイアログ左下の Run Design Rule Check ボタンをクリックすると開始されます。必要に応じて、DRC レポートが作成され、(そのように設定されている場合は)メイン設計ウィンドウのアクティブドキュメントとして自動的に開かれます。レポートには、Design Rule Checker dialog で指定された、テストされた各ルールが一覧表示されます。設計内に存在しないルールはテストされません。

DRC レポート

Design Rule Checker dialog で Create Report File オプションを有効にすると、Batch DRC の実行時に DRC レポートが生成されます。Preferences dialog の PCB Editor - Reports page にあるオプションを使用して、レポート形式や、生成後にレポートを自動表示するかどうかを指定できます。

Batch DRC プロセスの一部として DRC レポートを生成します。

サポートされる形式は次のとおりです。

-

TXT – Design Rule Check - <PCBDocumentName>.drc ファイルを生成します。

-

HTML – Design Rule Check - <PCBDocumentName>.html ファイルを生成します。

-

XML – <PCBDocumentName>.xml ファイルを生成します。

レポートには、Design Rule Checker dialog で指定された、バッチチェック処理中にテストされた各ルールが一覧表示されます。検出された各違反については、レイヤー、ネット名、コンポーネントデジグネータ、パッド番号などの参照情報、およびオブジェクトの位置を含む完全な詳細が記載されます。

違反表示オプション

指定した設計ルールに対して設計をチェックすること自体は一つの作業ですが、それらのルールの 1 つ以上に違反した場合はどうなるでしょうか。設計中に Online DRC を実行する場合でも、手動で Batch DRC を実行する場合でも、そのようなルール違反がどこで発生しているかを視覚的に示す必要があります。PCB Editor には、違反箇所を明確かつ視覚的に示す強力な違反表示オプションが用意されています。

カスタム違反グラフィックス

Online および/または Batch 設計ルールチェックに含めることができるほとんどの設計ルールには、対応するカスタム違反グラフィックスがあります。これらは特定のルールに違反したときに設計空間内に表示されます。これらのグラフィックスにより、DRC 表示はより視覚的に整理されたものになります。特定の設計ルールに違反した場合、対応するカスタム違反グラフィックス(該当する場合)は、その違反に関係するレイヤーにのみ描画されます。

場合によっては、このグラフィックは違反がどこで発生しているかだけでなく、その理由も示します。つまり、ルールに定義された制約値を表示し、問題のあるプリミティブがその値を下回っているか上回っているかを示します。

幅ルール違反および最小アニュラリングルール違反に使用されるカスタムグラフィックスの例。

幅ルール違反および最小アニュラリングルール違反に使用されるカスタムグラフィックスの例。

Net Antennae、Short-Circuit、Un-Routed Net、Room Definition、Layer Pairs、Vias Under SMD ルールの違反を表すために使用されるその他のグラフィックスは、表示すべき定義可能な制約値がないため、グラフィックのみとなります。

カスタム違反グラフィックスの追加例。左から右へ: Net Antennae 違反、Short-Circuit 違反、Un-Routed Net 違反。

カスタム違反グラフィックスの追加例。左から右へ: Net Antennae 違反、Short-Circuit 違反、Un-Routed Net 違反。

違反オーバーレイ

カスタム違反グラフィックスに加えて、設定して使用できる違反「オーバーレイ」も用意されています。このオーバーレイは設計プリミティブの上に描画されます。プリミティブ上に表示するパターンは、複数のスタイルから選択できます。

DRC 違反を表示する際、カスタム違反グラフィックスの代替として違反オーバーレイを使用します。

DRC 違反を表示する際、カスタム違反グラフィックスの代替として違反オーバーレイを使用します。

これら 2 種類の違反表示を組み合わせて使用すると、違反の「粗い」表示と「詳細な」表示を提供できるため便利です。ズームアウト時には違反オーバーレイで違反箇所を示し、その後ズームインして、対応するカスタム違反グラフィックによる詳細を確認できます。

違反表示設定の構成

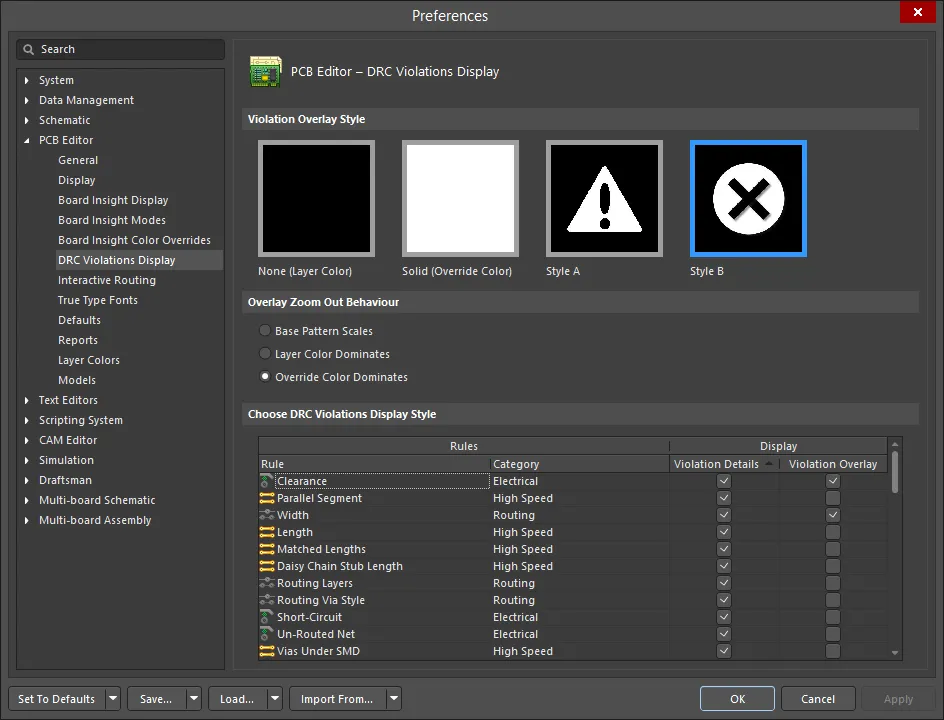

カスタム違反グラフィックスおよび/または定義済みの違反オーバーレイを使用して DRC 違反をどのように表示するかは、Preferences dialog の PCB Editor - DRC Violations Display page で指定します。

ソフトウェア設定の一部として、カスタムグラフィックスおよび/または定義済みの違反オーバーレイを使用して、設計空間内で DRC 違反をどのように表示するかを構成します。

利用可能なオプションでは、次のことができます。

-

Violation Overlay Style を使用して違反オーバーレイのスタイルを選択します。エラーマーカーは次の 4 つの方法のいずれかで表示できます。クリックして希望のスタイルを選択してください。

-

None (Layer Color) - エラーマーカーはレイヤーカラーで表示されるため、見えません。

-

Solid (Override Color) - エラーマーカーは Error Marker レイヤーカラーで表示されます。

-

Style A - エラーマーカーは警告三角形として表示されます。

-

Style B - エラーマーカーは中央に十字の入ったドットとして表示されます。

-

-

Overlay Zoom Out Behavior を使用して、ズームアウト時の違反オーバーレイ表示動作を決定します。ズームアウトすると、エラーマーカーは次のように動作します。

-

Base Pattern Scales - エラーマーカーはズームレベルに関係なくスケーリングされます(マーカーの種類は上で選択した Violation Overlay Style によって決まります)。

-

Layer Color Dominates - ズームアウトすると、エラーマーカーはレイヤーカラーの単色領域になります。

-

Override Color Dominates - ズームアウトすると、エラーマーカーは Error Marker レイヤーカラーの単色領域になります。

-

-

Choose DRC Violations Display Style 領域で、ルールごとに使用する表示スタイルを選択します。あるルールタイプに対して Violation Details オプションを有効にすると、そのルールの DRC 違反を対応するカスタム違反グラフィックスで表示します。Violation Overlay オプションを有効にすると、指定したオーバーレイスタイルを使用して違反を表示します。デフォルトでは、すべてのルールタイプに対して Violation Details 表示スタイルが有効であり、Violation Overlay Style 表示は Clearance、Width、Component Clearance ルールに対してのみ有効です。

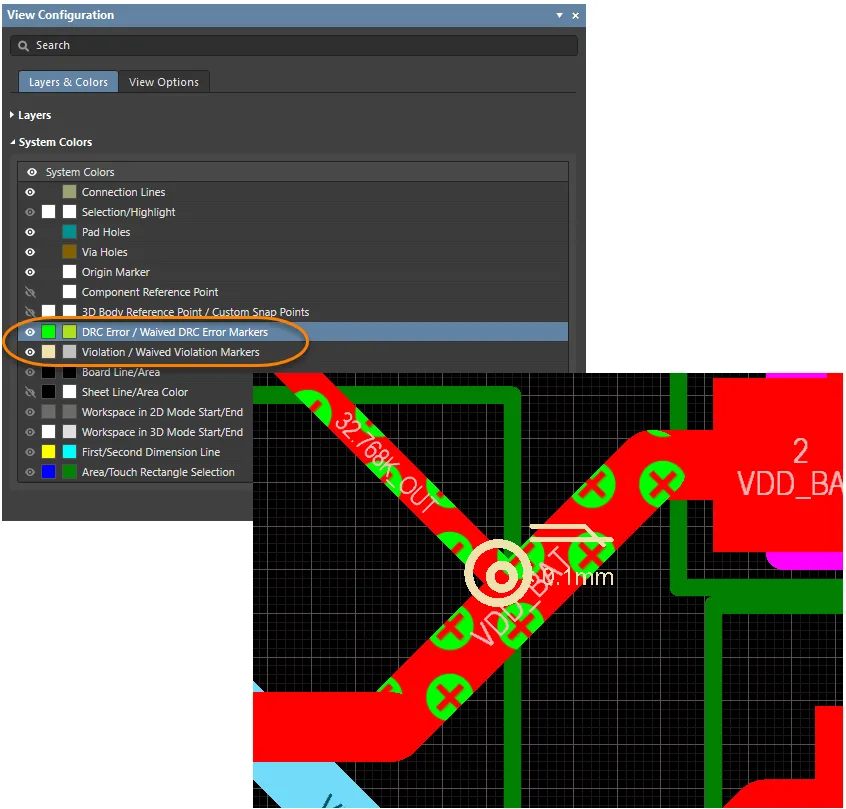

違反カラーの定義

設計空間でルール違反を表示する際の柔軟性をさらに高めるために、2つの違反表示タイプ、すなわち violation details(カスタム違反グラフィックス)と violation overlay には、それぞれ個別に関連付けられたシステムカラーが用意されています。これにより、異なる明確な色を使って両者を区別できます。色の割り当ては、System ColorsView Configuration panel の Layers & Colors タブにある section で行います。

-

Violation Details – Violation Markers システムカラーを使用します(この表示スタイルで免除された違反には、Waived Violation Markers システムカラーを使用します)。

-

Violation Overlay – DRC Error Markers システムカラーを使用します(この表示スタイルで免除された違反には、Waived DRC Error Markers システムカラーを使用します)。

2つの違反表示タイプに対して異なる色設定を指定し、必要に応じてそれぞれの表示を有効/無効にできます。

2つの違反表示タイプに対して異なる色設定を指定し、必要に応じてそれぞれの表示を有効/無効にできます。

AI で翻訳

AI で翻訳