Чтобы успешно выполнить анализ целостности сигналов (Signal Integrity) проекта и получить точные результаты, перед запуском анализа необходимо выполнить следующее.

-

Хотя каждую цепь (net) можно просканировать, чтобы получить данные по цепи и импедансу, не все цепи можно анализировать на характеристики целостности сигналов (напряжение и временные параметры). Чтобы успешно выполнить скрининг по всем характеристикам, цепь должна содержать как минимум одну микросхему (IC) с выходным выводом и не содержать других компонентов. Например, резисторы, конденсаторы и индуктивности сами по себе не дадут результатов моделирования, поскольку у них нет выходного вывода, который мог бы выступать в роли источника возбуждения. Следует отметить, что при скрининге двунаправленных цепей моделирование выполняется в обоих направлениях, и отображается результат для наихудшего случая.

-

Связанный тип модели Signal Integrity для каждого компонента должен быть задан корректно. Это выполняется через диалог Signal Integrity Model Assignments или вручную — установкой правильного значения в поле Type в диалоге Signal Integrity Model при редактировании модели Signal Integrity, связанной с компонентом, размещённым на исходном документе схемы. Если это значение не задано, диалог Signal Integrity Model Assignments попытается определить тип компонента на основе его характеристик. Если это значение не задано, будет предполагаться тип Integrated Circuit. Дополнительные сведения см. в Adding SI Models Using the Signal Integrity Model Assignments Dialog.

-

Должны быть заданы правила проектирования Supply Nets. Как правило, должно быть как минимум два правила: одно для цепей питания и одно для цепей земли. Область действия (scope) для них может быть задана либо как net, либо как net class. Цепи питания не могут анализироваться в Signal Integrity. Дополнительные сведения см. в Signal Integrity Design Rules in Schematic или Signal Integrity Design Rules in PCB.

-

Можно настроить правило проектирования Signal Stimulus. Правило возбуждения требуется только если вы хотите переопределить стимул по умолчанию, поэтому обычно оно не нужно.

-

Стек слоёв (layer stack) для PCB должен быть настроен корректно. Signal Integrity Analyzer требует непрерывных плоскостей питания. Разделённые плоскости (split planes) не поддерживаются, поэтому используется цепь, назначенная плоскости. Если плоскости отсутствуют, они считаются присутствующими по умолчанию, поэтому гораздо лучше добавить их и настроить должным образом. Толщина всех слоёв, сердечников (cores) и препрега (prepreg) также должна быть корректно задана для платы. Используйте команду Design » Layer Stack Manager, чтобы настроить стек слоёв в редакторе PCB. При запуске Signal Integrity в режиме «только схема» используется плата по умолчанию: два сигнальных слоя и две внутренние плоскости. При необходимости более точного контроля можно создать пустую PCB с настроенным стеком слоёв. Подробнее см. на странице Defining the Layer Stack .

Характеристики сигнала, например уровень напряжения, определяются моделью, назначенной выходному выводу в тестируемой цепи. Модели выводов назначаются в рамках процесса назначения моделей компонентам, и эти назначения на уровне компонента можно сохранить, обновив схему. Отдельную модель вывода также можно переопределить, например, двойным щелчком по выводу в панели Signal Integrity — обратите внимание, что такие переназначения на уровне вывода не сохраняются между сеансами редактирования.

Adding SI Models Using the Signal Integrity Model Assignments Dialog

Самый простой способ добавить модели целостности сигналов в проект — использовать диалог Signal Integrity Model Assignments.

-

Выберите Tools » Signal Integrity в меню. Если вы только начинаете работу с целостностью сигналов в проекте и есть компоненты, к которым не прикреплены модели целостности сигналов, диалог Errors or warnings found предложит настроить назначения моделей с помощью диалога Signal Integrity Model Assignments.

Диалог Errors or warnings found

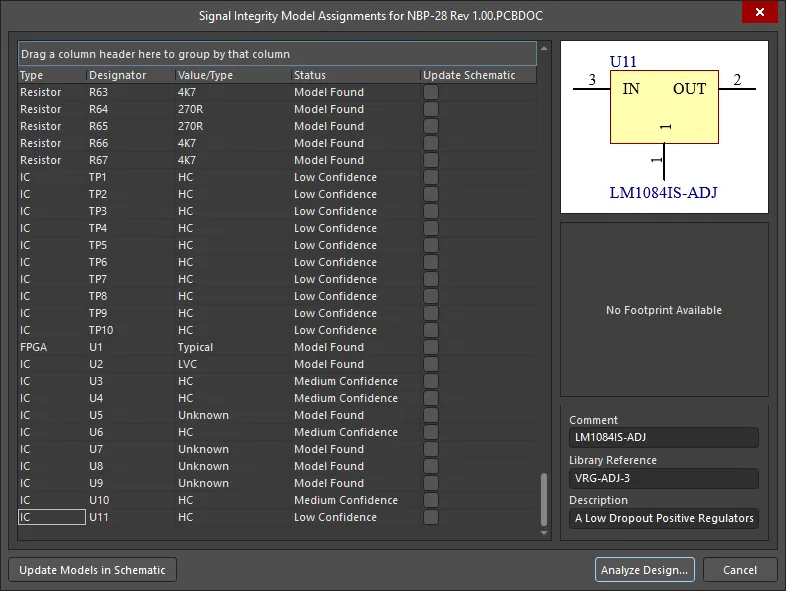

Диалог Signal Integrity Model Assignments

Либо, если вы нажали Continue и панель Signal Integrity видима, можно в любой момент открыть диалог Signal Integrity Model Assignments, нажав кнопку Model Assignments в панели. Учтите, что это приведёт к очистке всех результатов и их пересчёту, поскольку любые изменения назначений моделей делают существующие результаты недействительными.

Если модели уже настроены для всех компонентов, откроется диалог SI Setup Options. Дополнительные сведения см. в Configuring the SI Setup Options .

-

Если нажать Model Assignments в диалоге Errors or warnings found, откроется диалог Signal Integrity Model Assignments.

При запуске диалог Signal Integrity Models Assignment пытается сделать обоснованные предположения о том, какая модель целостности сигналов требуется для каждого компонента, у которого нет модели целостности сигналов. Все компоненты, включая те, для которых модели уже определены (и информация о моделях), будут отображены в диалоге Signal Integrity Models Assignment . Каждому компоненту будет присвоен статус, как описано в следующей таблице.

| Статус |

Определение |

| No match |

Диалог Signal Integrity Model Assignments не смог найти характеристики, связывающие этот компонент с определённым типом. Вероятно, потребуется вмешательство пользователя, чтобы настроить его корректно. |

| Low confidence |

Диалог Signal Integrity Model Assignments выбрал тип для этого компонента, но доказательств было недостаточно. |

| Medium confidence |

Диалог Signal Integrity Model Assignments выбрал тип для этого компонента и имеет разумную уверенность в предположении. |

| High confidence |

Диалог Signal Integrity Model Assignments выбрал тип для этого компонента, и он соответствует большинству характеристик, обычно связанных с этим типом компонента. |

| Model found |

Для этого компонента была найдена существующая модель. |

| User modified |

Компонент получит этот статус после того, как пользователь изменит его относительно первоначального предположения диалога Signal Integrity Model Assignments. |

| Model added |

Этот статус используется, когда пользователь применил диалог Signal Integrity Model Assignments для изменения документа схемы, чтобы сохранить новую модель. |

Modifying Component Models using the Signal Integrity Model Assignments Dialog

-

Выберите компонент, для которого нужно изменить модель.

-

Выберите правильный тип. Для Signal Integrity предусмотрено семь типов компонентов: резистор, конденсатор, индуктивность, диод, BJT, разъём и IC. Тип каждого компонента можно выбрать через выпадающий список в столбце Type или через контекстное меню (правый клик).

-

Задайте значение для резистора, конденсатора или индуктивности. Если возможно, диалог Signal Integrity Model Assignments попытается подставить корректное значение компонента в этот столбец на основе поля comment и параметров компонента. Если это требует корректировки (или значение отсутствует), сделайте это на данном этапе. Особый случай массивов элементов (например, резисторных сборок) настраивается через отдельный диалог, который открывается щелчком в столбце (подробнее см. Manually Adding Signal Integrity Models to Components).

-

Если компонент — IC, выбор типа технологии важен, поскольку он определяет характеристики моделей выводов, используемых в анализе. Это можно выбрать через выпадающий список в столбце Value/Type или через контекстное меню (Change Technology).

-

Наконец, может потребоваться указать больше деталей, чем позволяет диалог Signal Integrity Model Assignments, например для моделей IBIS. Это можно сделать, выбрав Advanced в контекстном меню. Подробнее об этом процессе см. Manually Adding Signal Integrity Models to Components.

Сохранение моделей

После выбора моделей для некоторых или всех компонентов документы схемы можно обновить, чтобы постоянно сохранить эту информацию.

-

Отметьте столбец Update Schematic в диалоге Signal Integrity Model Assignments для всех компонентов, которые нужно обновить. Затем нажмите кнопку Update Models in Schematic.

-

Все новые модели Signal Integrity (или изменённые существующие) для каждого выбранного компонента будут добавлены в документы схемы. Позже документы схемы нужно будет сохранить.

Для продолжения процесса анализа Signal Integrity сохранять модели не обязательно. Если модели не сохранены, анализ будет выполнен со всеми моделями, настроенными так, как они в данный момент показаны в диалоге Signal Integrity Model Assignments. Однако при следующем использовании инструмента Signal Integrity все изменения будут потеряны.

Manually Adding Signal Integrity Models to Components

Чтобы добавить модель Signal Integrity к компоненту на схеме:

-

Для размещённого компонента в редакторе схем — выберите компонент и откройте панель Properties.

-

Для компонента, редактируемого в редакторе условных графических обозначений — сделайте нужный компонент активным, выбрав его запись в панели SCH Library, и откройте панель Properties.

Нажмите кнопку Add в области Parameters панели Properties и выберите Signal Integrity. Откроется диалог Signal Integrity Model.

Настройте модель и нажмите OK.

Настройка пассивных компонентов

При настройке таких элементов, как резисторы и конденсаторы, обычно достаточно указать тип и значение. Значение можно ввести в поле Value и задать как параметр для всего компонента.

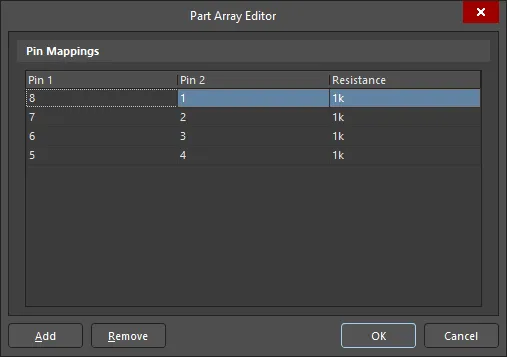

Также поддерживаются компоненты вроде резисторных сборок. Для этого после выбора типа компонента нажмите кнопку Setup Part Array в диалоге Signal Integrity Model. Диалог Part Array Editor позволяет настроить соединения между выводами и значение/модель для этих соединений.

Диалог Part Array Editor

Настройка IC

Существует несколько вариантов настройки модели типа IC.

Импорт файлов IBIS

Ещё одна важная возможность — импорт файлов IBIS.

-

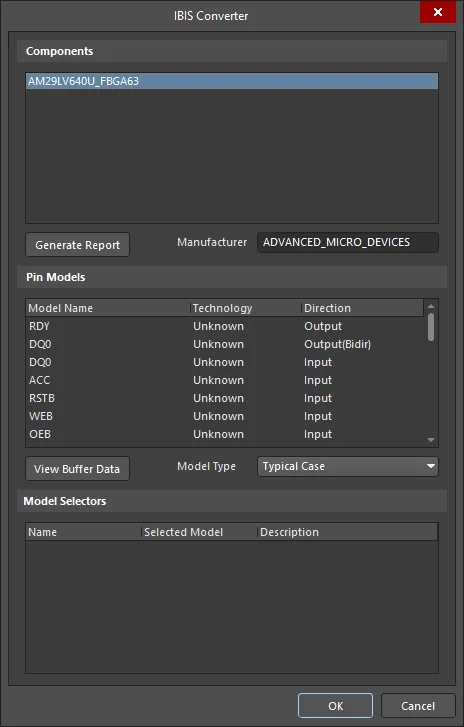

Чтобы использовать файл IBIS (Input/Output Buffer Information) для задания входных и выходных характеристик модели ИС, нажмите кнопку Import IBIS в диалоге Signal Integrity Model. Выберите файл IBIS в диалоге Open IBIS File и нажмите Open. Откроется диалог IBIS Converter.

Диалог IBIS Converter

-

Выберите нужный компонент, содержащийся в файле IBIS. Altium Designer прочитает файл IBIS и импортирует модели выводов из файла IBIS в библиотеку установленных моделей выводов. Если будет обнаружена дублирующаяся модель, вам будет предложено, следует ли переопределить существующую модель. Кроме того, всем выводам компонента будут назначены соответствующие модели выводов согласно данным в файле IBIS.

-

Автоматически будет сформирован отчёт, в котором указано, каким выводам назначение выполнено успешно, а каким — нет. Дополнительная настройка возможна путём ручного выбора моделей для соответствующих выводов, как описано выше.

-

Нажмите OK, чтобы завершить импорт информации IBIS и вернуться в диалог Signal Integrity Model.

Редактирование моделей выводов

Можно добавить или отредактировать существующую модель вывода, задав различные электрические характеристики этого вывода. Обратите внимание: это также доступно для других типов, таких как BJT, разъёмы и диоды.

-

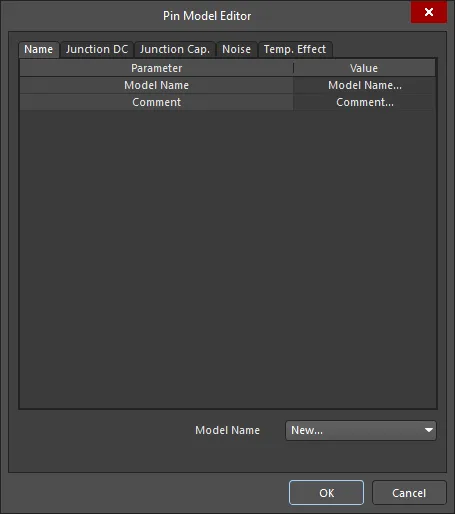

Чтобы изменить модели выводов, нажмите кнопку Add/Edit Model в диалоге Signal Integrity Model, если эта кнопка доступна для данного типа. Откроется диалог Pin Model Editor.

Диалог Pin Model Editor

-

Выберите New в раскрывающемся списке для Model Name.

-

Внесите необходимые изменения и нажмите OK.

-

Если это новая модель вывода, она станет доступной для выбора на выводах в этом (и других) компонентах.

Работа с редактором реализации модели Ibis

Для поддержки сторонних инструментов, которым для моделирования целостности сигналов требуются выделенные модели IBIS и которые не могут использовать собственный формат моделей целостности сигналов Altium Designer (так называемые SI Macro Models), в Altium Designer предусмотрен специализированный редактор реализации модели IBIS, позволяющий прикрепить модель IBIS к компоненту схемы. Таким образом, вы можете либо:

-

Импортировать модели выводов IBIS в выводы компонента во время анализа целостности сигналов (для сохранения в виде Altium Designer SI Macro Models), как описано выше (см. Импорт файлов IBIS), либо

-

Прикрепить модель IBIS к компоненту схемы, как описано ниже.

Эта функция поддерживает все версии спецификации моделей IBIS, вплоть до версии 4.0 включительно.

Чтобы добавить модель IBIS к компоненту схемы:

-

Для размещённого компонента в редакторе схем — выберите компонент и откройте панель Properties.

-

Для компонента, редактируемого в редакторе условных графических обозначений — сделайте нужный компонент активным, выбрав его запись на панели SCH Library, и откройте панель Properties.

Нажмите кнопку Add в области Parameters панели Properties и выберите Ibis Model. Откроется диалог IBIS Model.

Для компонента схемы можно определить любое количество ссылок на модели IBIS, но активной в каждый момент времени может быть только одна.

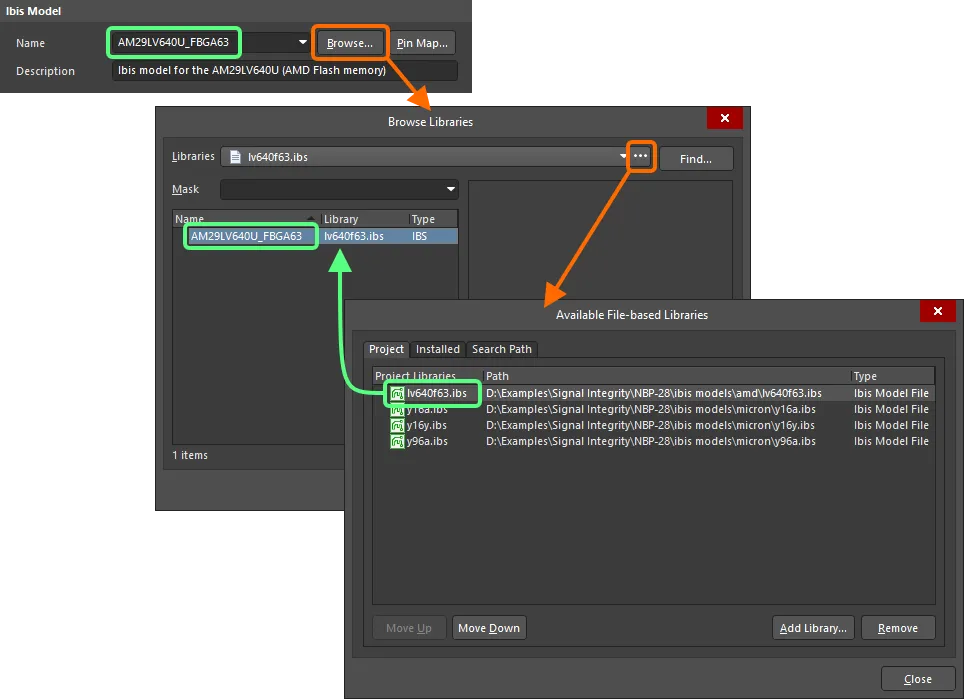

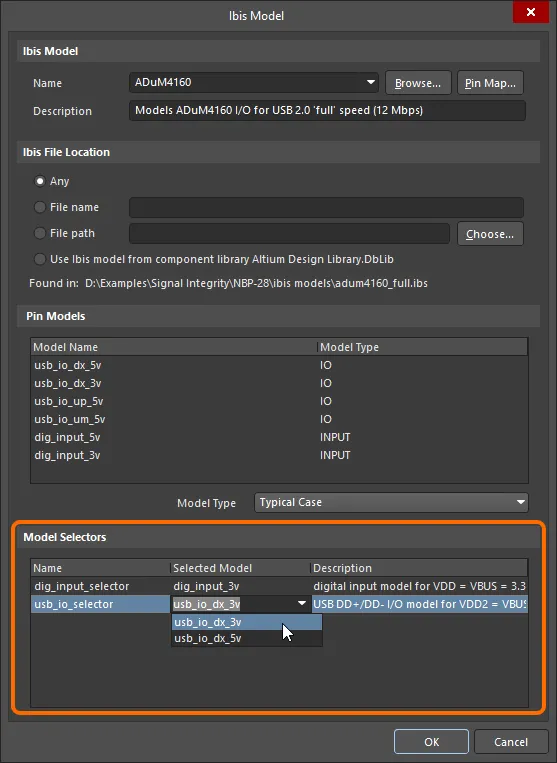

Модель IBIS

Укажите имя модели — точно так, как оно указано в файле .ibs — и задайте ссылке на модель осмысленное имя, возможно описывающее, что представляет реализация в этой области.

Либо, и особенно если вы не уверены в имени, используйте кнопку Browse для доступа к диалогу Browse Libraries. В этом диалоге можно просматривать файлы моделей IBIS во всех доступных библиотеках. Используйте функцию Find в этом диалоге, если нужные файлы моделей не входят в набор доступных библиотек.

Укажите имя модели напрямую или найдите её через просмотр.

При просмотре файла IBIS раскрывающийся список Name покажет все модели, по именам, определённые в этом файле. Просто выберите нужную.

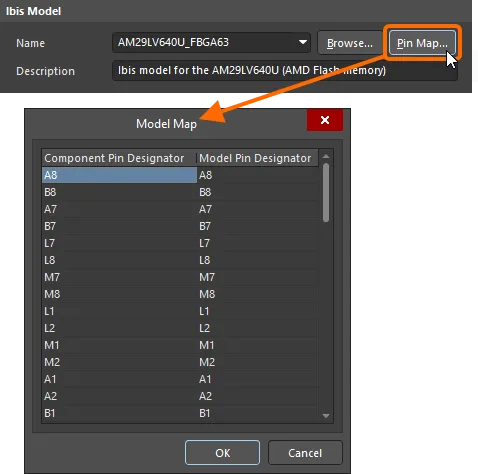

Сопоставление выводов компонента схемы выводам модели IBIS задаётся в диалоге Model Map, который открывается нажатием кнопки Pin Map.

Проверьте сопоставление выводов компонента и модели в диалоге Model Map .

Расположение файла IBIS

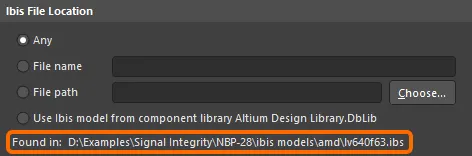

В этой области диалога IBIS Model доступны параметры, позволяющие указать, как программе находить модель — при условии, что имя модели задано:

-

Any — для поиска модели используются все Available Libraries (библиотеки проекта, установленные библиотеки и библиотеки, найденные по заданным путям поиска).

-

File name — введите полное имя файла, в котором находится модель (например,

lv640f63.ibs). Для поиска модели используются все Available Libraries. Если там файл не найден, будет проверен путь к библиотеке по умолчанию (поле Library Path на странице System – Default Locations диалога Preferences ), чтобы выяснить, можно ли найти там указанный файл.

-

File path — введите полный путь/имя файла. Нажмите кнопку Choose для выбора файла. Этот вариант всегда найдёт модель, поскольку путь задан явно (при условии, конечно, что файл остаётся в этом каталоге!).

-

Integrated/Database Library — после размещения, если компонент размещён из интегрированной или базы данных библиотеки, модель может быть получена напрямую из этой же библиотеки, при условии что библиотека входит в набор Available Libraries.

Если модель успешно найдена, будет показано, где именно она была обнаружена.

Укажите, как найти модель IBIS.

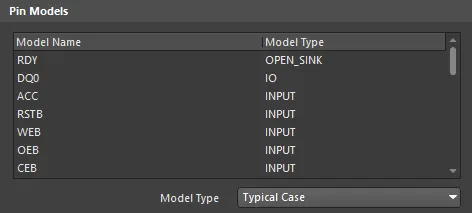

Модели выводов

Эта область диалога содержит список моделей выводов, определённых для выбранной модели IBIS, только для просмотра. Однако вы можете изменить Model Type со значения по умолчанию Typical Case на Strong Case или Weak Case соответственно.

Модели выводов для выбранной модели IBIS.

Селекторы моделей

Область Model Selectors диалога будет заполнена, если выбранная модель IBIS содержит селекторы моделей. Это позволяет выбрать, какую модель использовать (например, у вывода могут быть модели для разных уровней напряжения: 3,3 В, 5 В и т. д.).

Пример модели IBIS с заданными селекторами моделей.

Правила проектирования целостности сигналов на схеме

Специфичные для PCB правила проектирования для целостности сигналов можно задавать на схеме, если добавить их как параметры.

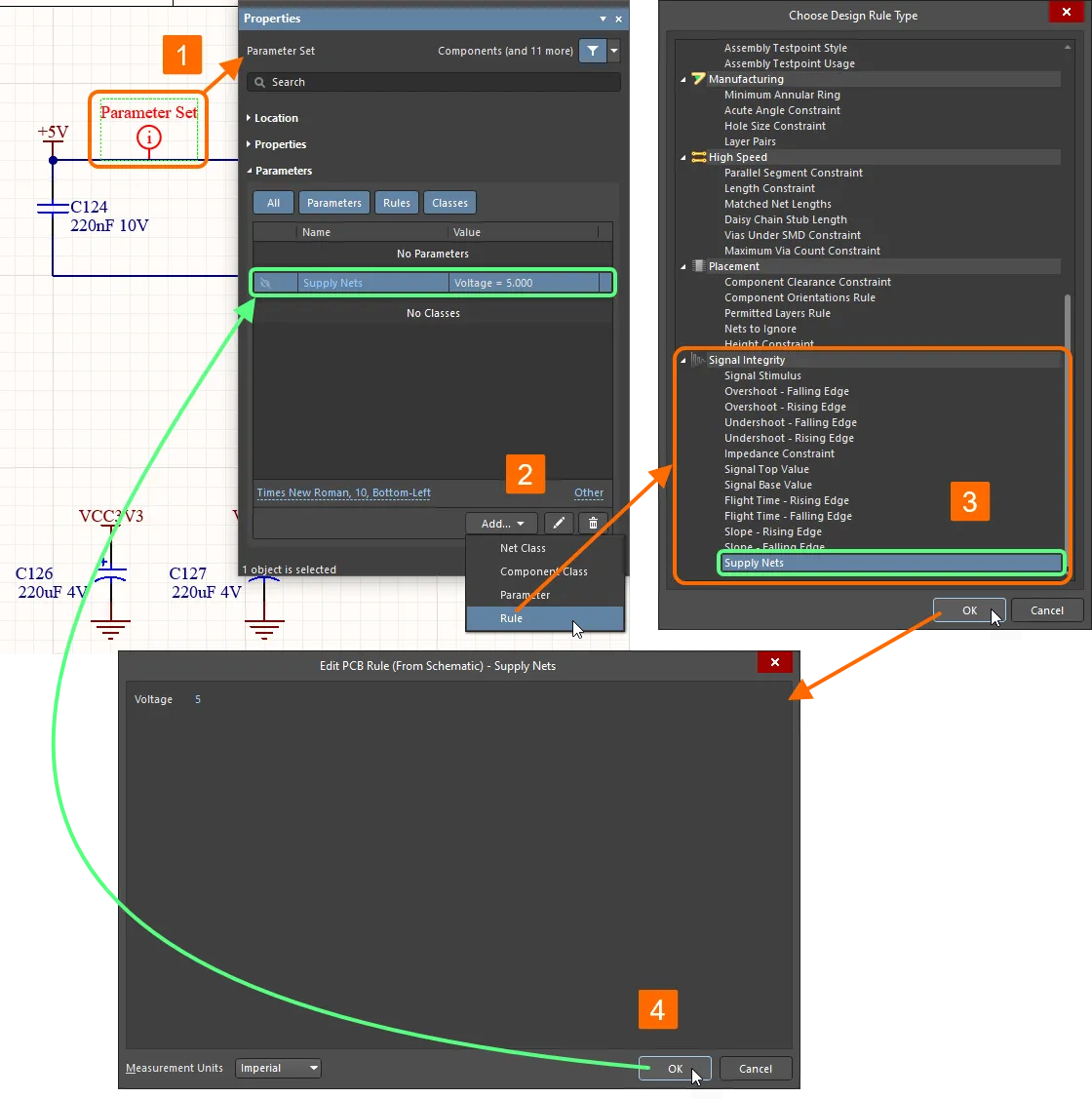

Правило проектирования для цепей питания (Supply Nets)

Для анализа целостности сигналов следует добавить правило PCB, чтобы идентифицировать цепи питания и их напряжение, используя директиву Parameter Set. Чтобы добавить на схеме правило для цепей питания:

-

Разместите директиву Parameter Set (Place » Directive » Parameter Set) на соответствующей цепи.

-

Когда размещённая директива выделена, нажмите кнопку Add в области Parameters панели Properties и выберите Rule в раскрывающемся меню.

-

Откроется диалог Choose Design Rule Type, где можно выбрать тип правила. Прокрутите вниз до правил Signal Integrity и выберите Supply Nets, затем нажмите OK.

-

Откроется диалог Edit PCB Rule (From Schematic) - Supply Nets. Введите напряжение для этой цепи питания и нажмите OK. Запись правила будет отображаться на панели Properties.

Правила проектирования целостности сигналов можно добавлять прямо на схемах с помощью директив Parameter Set.

После переноса проекта в разводку печатной платы правило добавляется в правила проектирования PCB (доступно для просмотра и редактирования в PCB Editor из диалога PCB Rules and Constraints Editor, открываемого командой Design » Rules).

Обратите внимание: в редакторе схем область действия правила (набор объектов, на которые будет распространяться правило) определяется тем, где добавлен параметр, например на проводе или выводе. В PCB Editor область действия правила задается внутри самого правила.

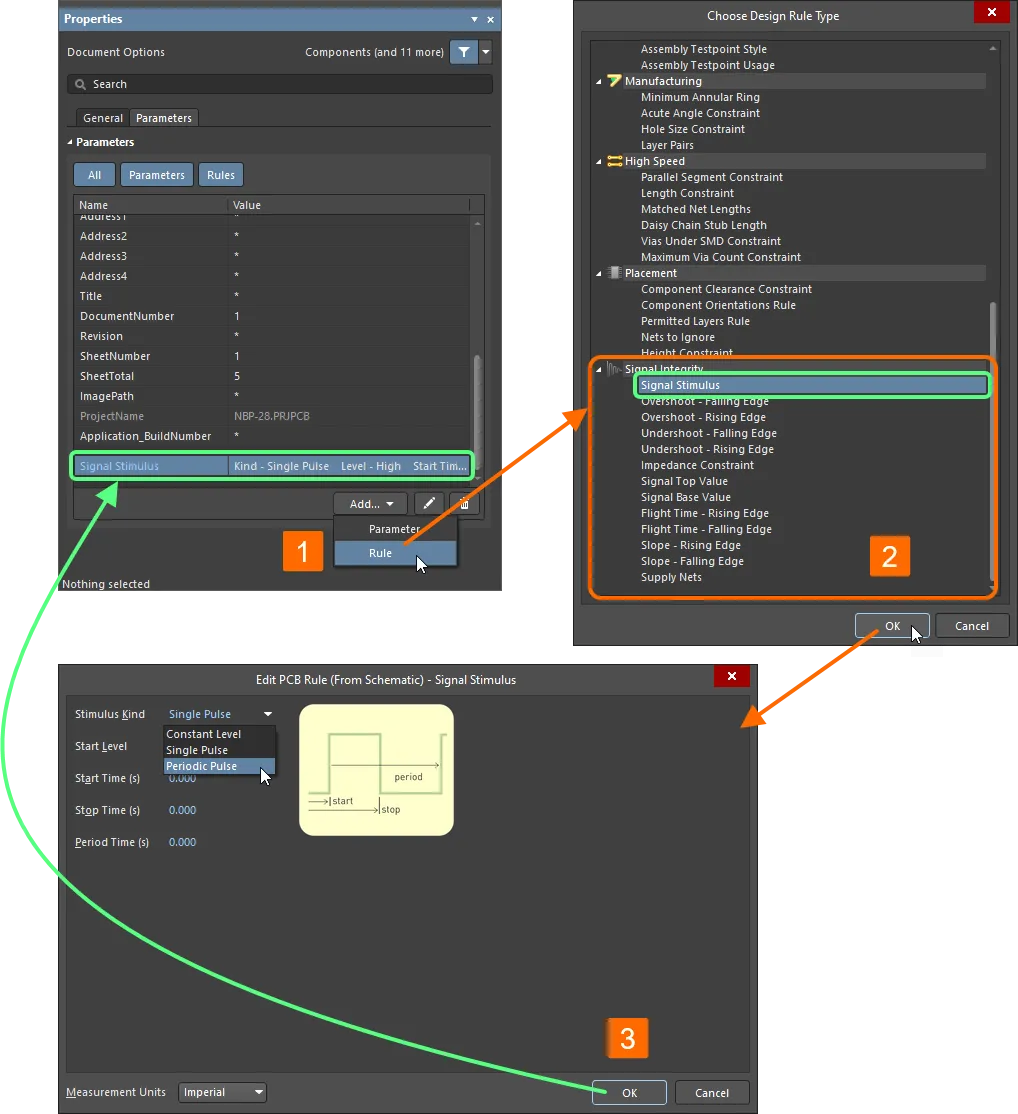

Правило проектирования Signal Stimulus

Другое правило проектирования, которое можно настроить из редактора схем, — это правило Signal Stimulus. При запуске этого правила воздействие (stimulus) вводится в каждый выходной вывод на анализируемой цепи (net). Для этого требуется правило проектирования с областью действия «all», поэтому для этого правила нужно создать параметр листа (sheet parameter). Если вы не настроите это правило, будут использованы параметры правила по умолчанию.

-

Когда на листе схемы не выбран ни один объект, откройте панель Properties. На вкладке Parameters панели нажмите кнопку Add и выберите Rule в раскрывающемся меню.

-

Откроется диалог Choose Design Rule Type, где можно выбрать тип правила. Прокрутите вниз до правил Signal Integrity и выберите Supply Nets, затем нажмите OK.

-

Отобразится диалог Edit PCB Rule (From Schematic) - Signal Stimulus. Выберите тип воздействия (stimulus kind), начальный уровень и времена, затем нажмите OK. Запись правила будет показана в панели Properties.

Правило проектирования Signal Integrity можно добавить как параметр листа схемы.

Правила проектирования Signal Integrity в PCB

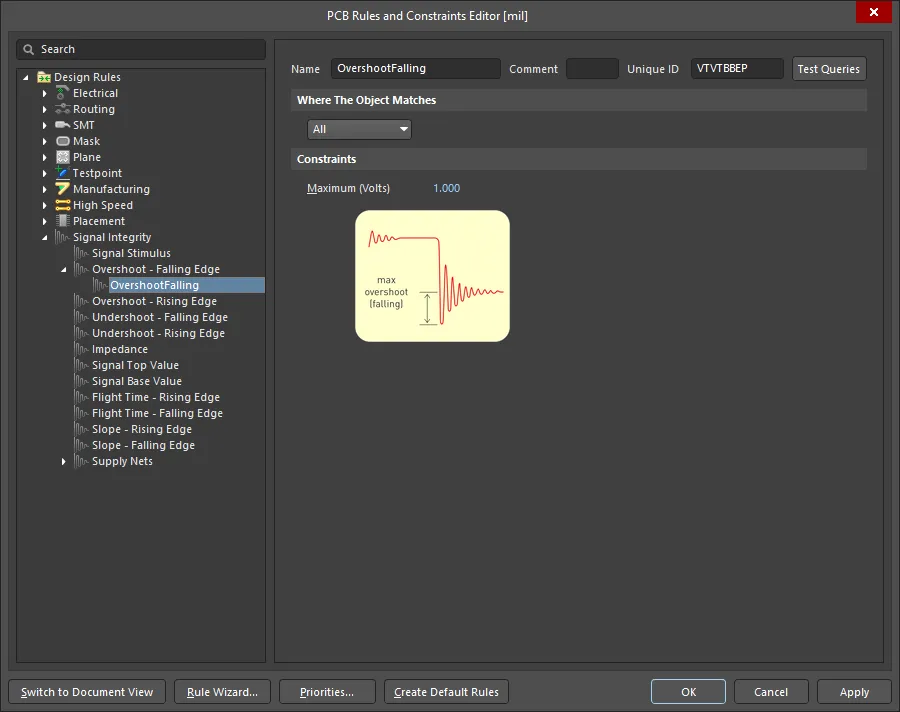

Параметры Signal Integrity, такие как требования к выбросу вверх (overshoot), выбросу вниз (undershoot), импедансу и крутизне фронта сигнала, можно задавать как стандартные правила проектирования PCB. Выберите Design » Rules в PCB Editor, чтобы открыть диалог PCB Rules and Constraints Editor, где можно настроить эти правила. Эти правила также можно настроить с помощью параметров в редакторе схем, и после переноса проекта в разводку PCB они появятся в диалоге PCB Rules and Constraint Editor.

Диалог PCB Rules and Constraint Editor при просмотре правила проектирования Overshoot - Falling Edge

У этих правил две цели. Первая — при запуске стандартных проверок DRC в PCB: плату можно проверить на соответствие этим правилам с помощью стандартного анализа (screening). Второе применение этих правил — при использовании панели Signal Integrity. Эти правила можно настроить и включить как тесты, и панель будет графически показывать, какие цепи (nets) не прошли какие тесты.

Когда проект подготовлен, настройте и запустите анализ целостности сигналов.