설계에 대한 신호 무결성 분석을 성공적으로 실행하고 정확한 결과를 얻으려면 분석을 실행하기 전에 다음을 수행해야 합니다.

-

각 넷을 스크리닝하여 넷 및 임피던스 데이터를 제공할 수 있지만 모든 넷에 대해 신호 무결성 특성(전압 및 타이밍)을 분석할 수 있는 것은 아닙니다. 모든 특성을 성공적으로 스크리닝하려면 넷에 출력 핀이 있고 다른 컴포넌트가 없는 IC가 하나 이상 포함되어 있어야 합니다. 예를 들어 저항기, 커패시터 및 인덕터는 구동 소스를 제공하는 출력 핀이 없기 때문에 자체적으로 시뮬레이션 결과를 제공하지 않습니다. 양방향 네트를 스크리닝할 때는 양방향이 모두 시뮬레이션되고 최악의 결과가 표시된다는 점에 유의해야 합니다.

-

각 컴포넌트의 관련 신호 무결성 모델 유형이 정확해야 합니다. 이는 회로도 소스 문서에 배치된 컴포넌트에 연결된 신호 무결성 모델을 편집할 때 Signal Integrity Model Assignments 대화 상자 또는 Signal Integrity Model 대화 상자에서 Type 필드에 올바른 항목을 수동으로 설정하여 수행할 수 있습니다. 이 항목이 정의되지 않은 경우 Signal Integrity Model Assignments 대화 상자에서 컴포넌트의 특성을 기반으로 컴포넌트의 유형을 추측하려고 시도합니다. 이 항목이 정의되지 않은 경우 집적 회로 유형이 가정됩니다. 자세한 내용은 신호 무결성 모델 할당 대화 상자를 사용하여 SI 모델 추가하기를 참조하세요.

-

Supply Nets design rules이 있어야 합니다. 일반적으로 전원망과 접지망에 대한 규칙이 각각 하나씩, 최소 두 가지 규칙이 있어야 합니다. 이러한 규칙의 범위는 네트 또는 네트 클래스일 수 있습니다. 공급망은 신호 무결성에서 분석할 수 없습니다. 자세한 내용은 회로도의 신호 무결성 설계 규칙 또는 PCB의 신호 무결성 설계 규칙을 참조하세요.

-

신호 자극 설계 규칙을 설정할 수 있습니다. 기본 자극을 재정의하려는 경우에만 자극 규칙이 필요하므로 일반적으로는 필요하지 않습니다.

-

PCB의 레이어 스택을 올바르게 설정해야 합니다. 신호 무결성 분석기에는 continuous power planes이 필요합니다. Split plane은 지원되지 않으므로 Plane에 할당된 Net이 사용됩니다. 없는 경우 가정되므로 추가하고 적절하게 설정하는 것이 훨씬 좋습니다. 모든 레이어, 코어 및 프리프레그의 두께도 보드에 맞게 올바르게 설정해야 합니다. Design » Layer Stack Manager 명령을 사용하여 PCB 에디터에서 레이어 스택을 설정합니다. 신호 무결성을 회로도 전용 모드에서 실행할 때는 내부 Plane이 두 개인 기본 2레이어 보드가 사용됩니다. 더 많은 제어가 필요한 경우 레이어 스택이 설정된 빈 PCB를 생성할 수 있습니다. 자세한 내용은 레이어 스택 정의하기 페이지를 참조하세요.

전압 레벨과 같은 신호의 특성은 테스트 중인 네트워크의 출력 핀에 할당된 모델에 의해 결정됩니다. 핀 모델은 컴포넌트 모델 할당 프로세스의 일부로 할당되며, 이러한 컴포넌트 수준 모델 할당은 회로도를 업데이트하여 유지할 수 있습니다. 예를 들어 Signal Integrity 패널에서 핀을 두 번 클릭하여 개별 핀 모델을 재정의할 수도 있습니다. 이러한 핀 수준 재할당은 편집 세션 간에 유지되지 않는다는 점에 유의하세요.

신호 무결성 모델 할당 대화 상자를 사용하여 SI 모델 추가하기

설계에 신호 무결성 모델을 추가하는 가장 간단한 방법은 Signal Integrity Model Assignments 대화 상자를 사용하는 것입니다.

-

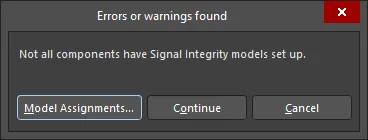

메뉴에서 Tools » Signal Integrity 을 선택합니다. 프로젝트에서 신호 무결성을 막 시작하고 신호 무결성 모델이 첨부되지 않은 컴포넌트가 있는 경우 Errors or warnings found 대화 상자에서 Signal Integrity Model Assignments 대화 상자를 사용하여 모델 할당을 설정하라는 메시지가 표시됩니다.

Errors or warnings found 대화 상자

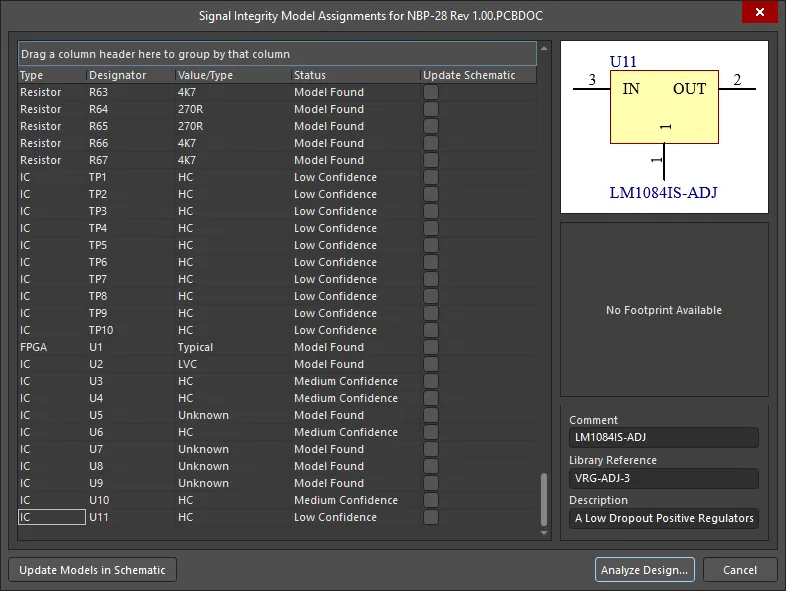

Signal Integrity Model Assignments 대화 상자

또는 Continue 을 클릭하고 Signal Integrity 패널이 표시되는 경우 패널의 Model Assignments 버튼을 클릭하여 언제든지 Signal Integrity Model Assignments 대화 상자로 들어갈 수 있습니다. 이렇게 하면 모델 할당을 변경하면 기존 결과가 모두 무효화되므로 모든 결과가 지워지고 다시 계산됩니다.

모든 컴포넌트에 대해 모델이 이미 설정된 경우 SI Setup Options 대화 상자가 표시됩니다. 자세한 내용은 SI 설정 옵션 구성을 참조하세요.

-

Errors or warnings found 대화 상자에서 Model Assignments 을 클릭하면 Signal Integrity Model Assignments 대화 상자가 표시됩니다.

Signal Integrity Models Assignment 대화 상자를 실행하면 신호 무결성 모델이 없는 각 컴포넌트에 필요한 신호 무결성 모델을 교육적으로 추측하려고 시도합니다. 이미 정의된 모델(및 모델 정보)이 있는 컴포넌트를 포함한 모든 컴포넌트가 Signal Integrity Models Assignment 대화 상자에 표시됩니다. 각 컴포넌트에는 다음 표에 설명된 대로 상태가 할당됩니다.

| 상태 |

정의 |

| 일치하지 않음 |

Signal Integrity Model Assignments 대화 상자에서 이 컴포넌트를 특정 유형에 연결하는 특성을 찾을 수 없습니다. 올바르게 설정하려면 사용자의 수정이 필요할 수 있습니다. |

| 낮은 신뢰도 |

Signal Integrity Model Assignments 대화 상자에서 이 컴포넌트의 유형을 선택했지만 확실한 증거가 없습니다. |

| 중간 신뢰도 |

Signal Integrity Model Assignments 대화 상자에서 이 컴포넌트에 대한 유형을 선택했으며 추측에 대한 적절한 신뢰도가 있습니다. |

| 높은 신뢰도 |

Signal Integrity Model Assignments 대화 상자에서 이 컴포넌트에 대한 유형을 선택했으며 일반적으로 이 유형의 컴포넌트와 관련된 대부분의 특성에 부합합니다. |

| 모델 발견 |

이 컴포넌트에 대한 기존 모델을 찾았습니다. |

| 사용자 수정됨 |

사용자가 Signal Integrity Model Assignments 대화 상자의 초기 추측에서 컴포넌트를 수정하면 이 상태로 변경됩니다. |

| 모델 추가됨 |

이 상태는 사용자가 Signal Integrity Model Assignments 대화 상자를 사용하여 회로도 문서를 수정하여 새 모델을 저장한 경우에 사용됩니다. |

신호 무결성 모델 할당 대화 상자를 사용하여 컴포넌트 모델 수정하기

-

모델을 수정하려는 컴포넌트를 선택합니다.

-

올바른 유형을 선택합니다. 신호 무결성에는 저항, 커패시터, 인덕터, 다이오드, BJT, 커넥터, IC 등 7가지 유형의 컴포넌트가 있습니다. 각 컴포넌트의 유형은 Type 열의 드롭다운 또는 오른쪽 클릭 메뉴를 통해 선택할 수 있습니다.

-

저항, 커패시터 또는 인덕터의 값을 설정합니다. 가능하면 Signal Integrity Model Assignments 대화 상자에서 컴포넌트의 설명 필드와 매개변수를 기반으로 이 열에 컴포넌트에 대한 올바른 값을 입력하려고 시도합니다. 수정이 필요한 경우(또는 없는 경우) 이 시점에서 수정해야 합니다. 부품 배열의 특수한 경우(예: 저항기 배열)는 열을 클릭하여 액세스하는 별도의 대화 상자를 통해 수행됩니다(자세한 내용은 컴포넌트에 신호 무결성 모델 수동 추가하기 참조).

-

컴포넌트가 IC인 경우 기술 유형 선택은 분석에 사용되는 핀 모델의 특성을 결정하므로 중요합니다. 이는 Value/Type 열의 드롭다운 목록을 통해 선택하거나 오른쪽 클릭 메뉴(Change Technology)를 통해 액세스할 수 있습니다.

-

마지막으로, IBIS 모델과 같이 Signal Integrity Model Assignments 대화 상자에서 허용되는 것보다 더 자세한 내용을 지정해야 할 수도 있습니다. 이 경우 오른쪽 클릭 메뉴에서 Advanced 을 선택하면 됩니다. 이 프로세스에 대한 자세한 내용은 컴포넌트에 신호 무결성 모델 수동 추가하기를 참조하세요.

모델 저장

일부 또는 모든 컴포넌트에 대해 모델을 선택하면 회로도 문서를 업데이트하여 이 정보를 영구적으로 저장할 수 있습니다.

-

업데이트할 모든 컴포넌트를 보려면 Signal Integrity Model Assignments 대화 상자에서 Update Schematic 열을 확인합니다. 그런 다음 Update Models in Schematic 버튼을 클릭합니다.

-

선택한 각 컴포넌트에 대한 모든 새 신호 무결성 모델(또는 수정된 기존 모델)이 회로도 문서에 추가됩니다. 회로도 문서는 나중에 저장해야 합니다.

신호 무결성 분석 프로세스를 진행하기 위해 모델을 저장할 필요는 없습니다. 모델을 저장하지 않으면 현재 Signal Integrity Model Assignments 대화 상자에 표시된 대로 구성된 모든 모델로 분석이 진행됩니다. 그러나 다음에 신호 무결성 도구를 사용할 때는 변경 사항이 모두 손실됩니다.

부품 컴포넌트에 수동으로 신호 무결성 모델 추가하기

신호 무결성 모델을 회로도 컴포넌트에 추가하려면 다음과 같이 하세요:

-

회로도 편집기에 배치된 컴포넌트의 경우 - 컴포넌트를 선택하고 Properties 패널을 엽니다.

-

회로도 기호 편집기에서 편집 중인 컴포넌트의 경우 - SCH Library 패널에서 해당 항목을 선택하여 필요한 컴포넌트를 활성화하고 Properties 패널을 엽니다.

Properties 패널의 Parameters 영역에서 Add 버튼을 클릭하고 Signal Integrity 을 선택합니다. Signal Integrity Model 대화 상자가 열립니다.

모델을 설정하고 OK 을 클릭합니다.

Passive 수동소자 컴포넌트 설정하기

저항기 및 커패시터와 같은 부품을 설정할 때는 일반적으로 유형과 값을 입력하는 것으로 충분합니다. 값은 Value 필드에 입력할 수 있으며 전체 컴포넌트에 대한 파라미터로 설정할 수 있습니다.

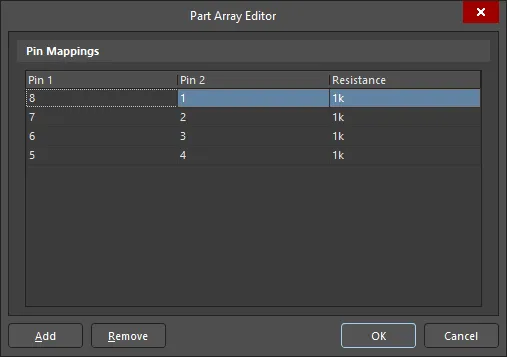

저항 어레이와 같은 컴포넌트에 대한 지원도 있습니다. 컴포넌트 유형을 선택한 후 Signal Integrity Model 대화 상자에서 Setup Part Array 버튼을 클릭하면 됩니다. Part Array Editor 대화 상자에서 핀 간의 연결과 해당 연결에 대한 값/모델을 구성할 수 있습니다.

Part Array Editor 대화 상자

IC 설정하기

IC 유형 모델을 설정할 때 몇 가지 대안이 있습니다.

IBIS 파일 가져오기

또 다른 중요한 옵션은 IBIS 파일을 가져오는 기능입니다.

-

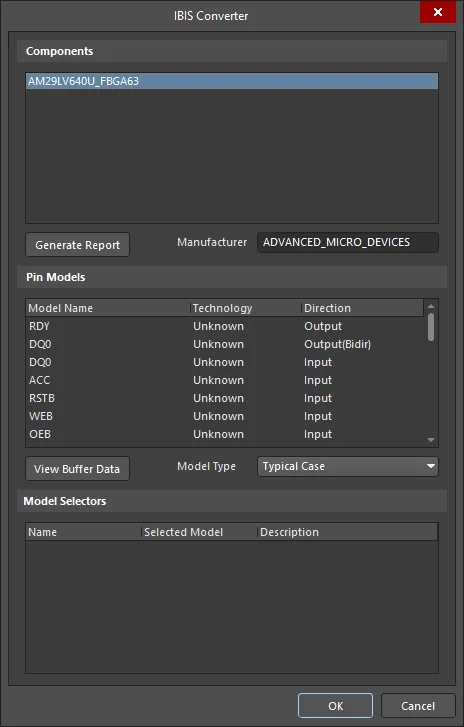

IBIS(입력/출력 버퍼 정보) 파일을 사용하여 IC 모델의 입력 및 출력 특성을 지정하려면 Signal Integrity Model 대화 상자에서 Import IBIS 버튼을 클릭합니다. Open IBIS File 대화 상자에서 IBIS 파일을 선택하고 Open 을 클릭합니다. IBIS Converter 대화 상자가 표시됩니다.

IBIS Converter 대화 상자

-

IBIS 파일에 포함된 필수 컴포넌트를 선택합니다. 알티움 디자이너가 IBIS 파일을 읽고 IBIS 파일에서 설치된 핀 모델 라이브러리로 핀 모델을 가져옵니다. 중복 모델이 발견되면 기존 모델을 재정의할 것인지 묻는 메시지가 표시됩니다. 또한 컴포넌트의 모든 핀에는 IBIS 파일에 지정된 대로 적절한 핀 모델이 할당됩니다.

-

성공적으로 할당된 핀과 실패한 핀이 명시된 보고서가 자동으로 생성됩니다. 위에서 설명한 대로 적절한 핀의 모델을 수동으로 선택하여 추가 사용자 지정이 가능합니다.

-

OK 을 클릭하여 IBIS 정보 가져오기를 완료하고 Signal Integrity Model 대화 상자로 돌아옵니다.

핀 모델 편집

해당 핀의 다양한 전기적 특성을 지정하여 기존 핀 모델을 추가하거나 편집할 수 있습니다. 이 기능은 BJT, 커넥터 및 다이오드와 같은 다른 유형에도 사용할 수 있습니다.

-

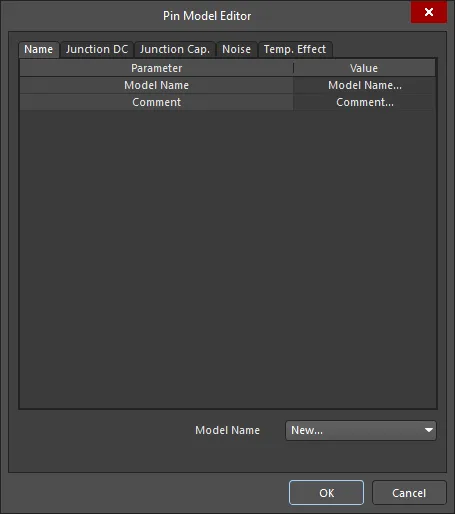

핀 모델을 수정하려면 해당 유형에 이 버튼을 사용할 수 있는 경우 Signal Integrity Model 대화 상자에서 Add/Edit Model 버튼을 클릭합니다. Pin Model Editor 대화 상자가 표시됩니다.

Pin Model Editor 대화 상자

-

Model Name 의 드롭다운 목록에서 New 을 클릭합니다.

-

필요한 사항을 변경하고 OK 을 클릭합니다.

-

새 핀 모델인 경우 이제 이(및 다른) 컴포넌트의 핀에서 해당 모델을 선택할 수 있습니다.

Ibis 모델 구현 에디터로 작업하기

신호 무결성 시뮬레이션을 위해 전용 IBIS 모델이 필요하지만 Altium Designer의 자체 신호 무결성 모델 형식(SI 매크로 모델이라고 함)을 사용할 수 없는 타사 도구를 지원하기 위해 Altium Designer는 전용 IBIS 모델 구현 에디터를 통합하여 IBIS 모델을 회로도 컴포넌트에 첨부할 수 있도록 합니다. 따라서 둘 중 하나를 사용할 수 있습니다:

-

위에서 설명한 대로 신호 무결성 분석 중에, IBIS 핀 모델을 컴포넌트 핀으로 가져오거나(Altium Designer SI 매크로 모델로 저장하기 위해)( IBIS 파일 가져오기 참조)

-

아래 설명된 대로 IBIS 모델을 회로도 컴포넌트에 첨부합니다.

이 기능은 버전 4.0을 포함한 모든 버전의 IBIS 모델 사양을 지원합니다.

회로 컴포넌트에 IBIS 모델을 추가하려면 다음과 같이 하세요:

-

회로도 편집기에 배치된 컴포넌트의 경우 - 컴포넌트를 선택하고 Properties 패널을 엽니다.

-

회로도 기호 편집기에서 편집 중인 컴포넌트의 경우 - SCH Library 패널에서 해당 항목을 선택하여 필요한 컴포넌트를 활성화하고 Properties 패널을 엽니다.

Properties 패널의 Parameters 영역에서 Add 버튼을 클릭하고 Ibis Model 을 선택합니다. IBIS Model 대화 상자가 열립니다.

회로도 컴포넌트에 대해 여러 개의 IBIS 모델 링크를 정의할 수 있지만 주어진 시간에 하나의 모델만 활성 모델이 될 수 있습니다.

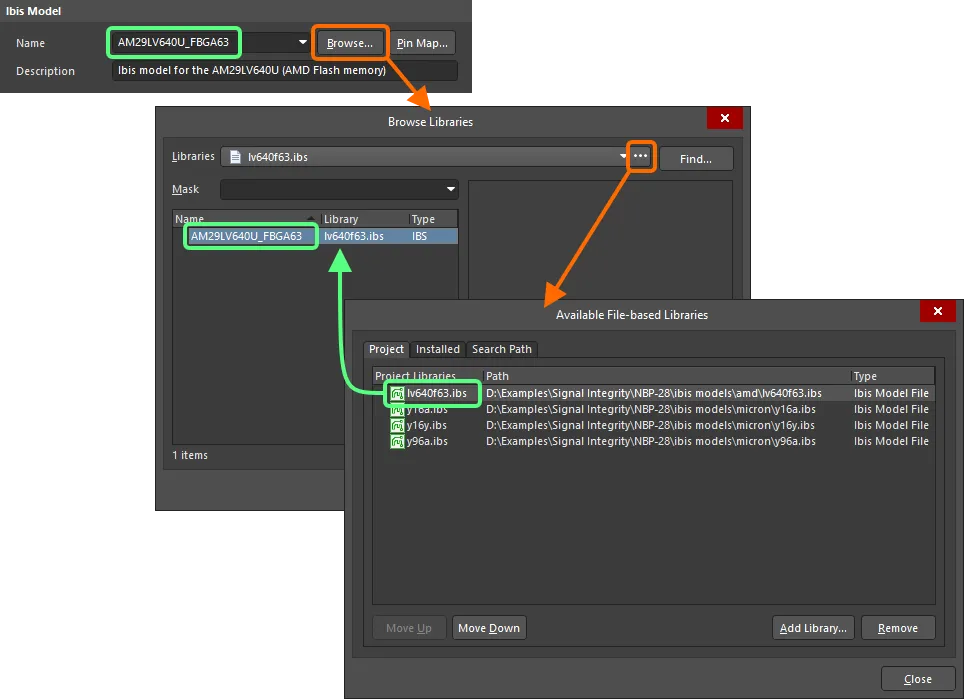

IBIS 모델

모델 이름을 .ibs 파일에 표시된 대로 지정하고 모델 링크에 이 도메인의 구현이 무엇을 나타내는지 설명하는 의미 있는 이름을 지정합니다.

또는 이름을 잘 모르는 경우 Browse 버튼을 사용하여 Browse Libraries 대화 상자에 액세스하세요. 이 대화 상자를 사용하여 현재 사용 가능한 모든 라이브러리에서 IBIS 모델 파일을 찾아볼 수 있습니다. 필요한 모델 파일이 현재 사용 가능한 라이브러리에 없는 경우에는 이 대화 상자의 Find 기능을 사용하세요.

모델 이름을 직접 지정하거나 찾아봅니다.

IBIS 파일을 검색할 때 이름 드롭다운에는 해당 파일에 정의된 모든 모델이 이름별로 표시됩니다. 필요한 모델을 선택하기만 하면 됩니다.

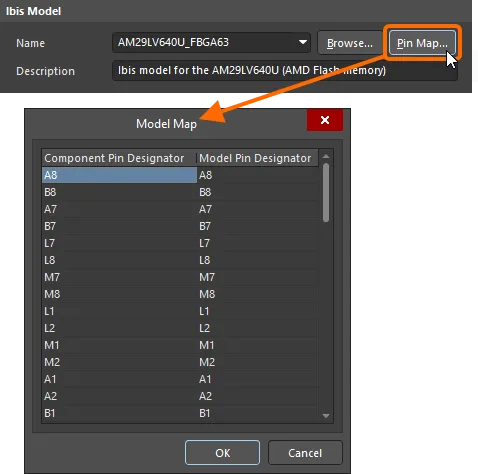

회로도 컴포넌트 핀과 IBIS 모델 핀의 매핑은 Pin Map 버튼을 클릭하여 액세스하는 Model Map 대화 상자에서 정의할 수 있습니다.

모델 맵 대화 상자에서 컴포넌트 간 모델 핀 매핑을 확인합니다.

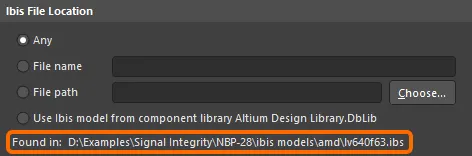

IBIS 파일 위치

모델 이름이 정의되어 있는 경우 IBIS Model 대화 상자의 이 영역에서 소프트웨어가 모델을 찾는 방법을 지정할 수 있는 옵션을 사용할 수 있습니다:

-

Any - 사용 가능한 모든 라이브러리(프로젝트 라이브러리, 설치된 라이브러리 및 정의된 검색 경로를 따라 찾은 라이브러리)가 모델을 찾는 데 사용됩니다.

-

File name - 모델이 있는 전체 파일 이름을 입력합니다(예:

lv640f63.ibs). 사용 가능한 모든 라이브러리는 모델을 찾는 데 사용됩니다. 여기에서 찾을 수 없는 경우 기본 라이브러리 경로( Preferences 대화 상자의 System – Default Locations 페이지에 있는 Library Path 필드)를 조사하여 해당 이름의 파일을 찾을 수 있는지 확인합니다.

-

File path - 파일의 전체 경로/이름을 입력합니다. Choose 버튼을 클릭하여 파일을 찾습니다. 이 옵션은 명시적이기 때문에 항상 모델을 찾을 수 있습니다(물론 파일이 해당 디렉터리에 남아 있는 경우!).

-

Integrated/Database Library - 배치 후 컴포넌트가 통합 또는 데이터베이스 라이브러리에서 배치된 경우 라이브러리가 사용 가능한 라이브러리 세트의 일부인 경우 동일한 라이브러리에서 모델을 직접 소싱할 수 있습니다.

성공적으로 모델을 찾으면 모델을 찾은 위치에 대한 표시가 표시됩니다.

IBIS 모델을 찾는 방법을 지정합니다.

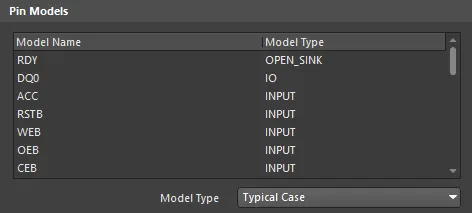

핀 모델

대화 상자의 이 영역에는 선택한 IBIS 모델에 대해 정의된 핀 모델의 보기 전용 목록이 표시됩니다. 그러나 Model Type 을 기본값인 Typical Case 에서 Strong Case 또는 Weak Case 으로 각각 변경할 수 있습니다.

선택한 IBIS 모델의 핀 모델.

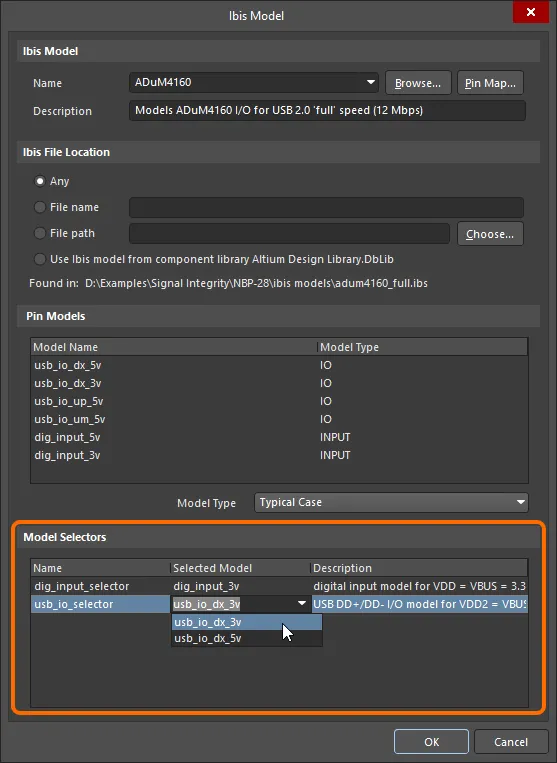

모델 선택기

선택한 IBIS 모델에 모델 선택기가 있는 경우 대화 상자의 Model Selectors 영역이 채워집니다. 이를 통해 사용할 모델을 선택할 수 있습니다(예: 핀에 3.3V, 5V 등 다양한 전압 레벨에 대한 모델이 있을 수 있음).

모델 선택기가 정의된 IBIS 모델 예시.

회로도의 신호 무결성 설계 규칙

신호 무결성에 대한 PCB별 설계 규칙을 파라미터로 추가하면 회로도에 정의할 수 있습니다.

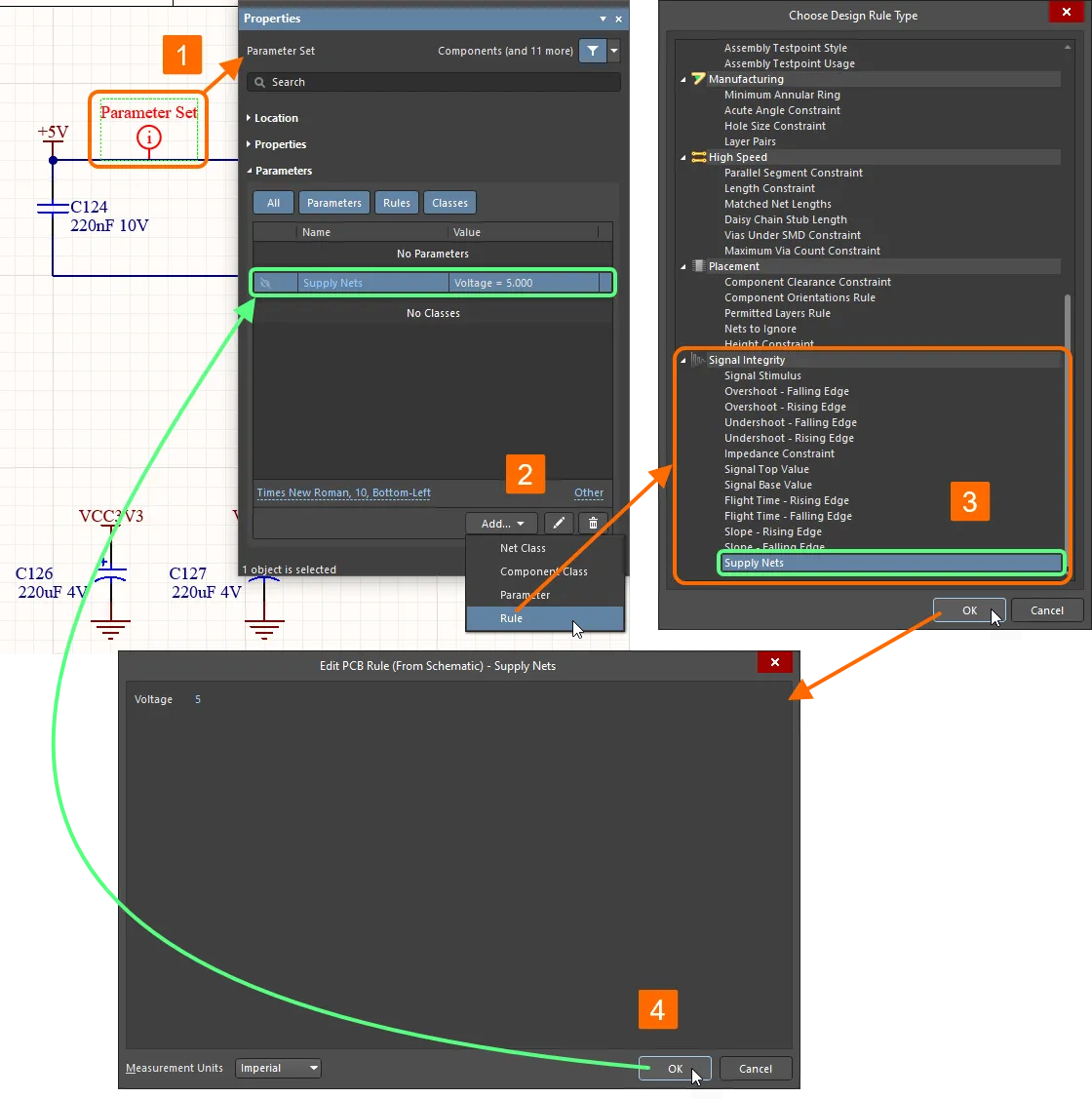

Supply Nets design rules

신호 무결성 분석의 경우 파라미터 세트 지시어를 사용하여 공급망과 해당 전압을 식별하기 위한 PCB 규칙을 추가해야 합니다. 회로도에 Supply Nets design rules을 추가하려면 다음과 같이 하세요:

-

파라미터 세트 지시어(Place » Directive » Parameter Set)를 해당 네트에 배치합니다.

-

배치된 지시문이 선택되면 Properties 패널의 Parameters 영역에서 Add 버튼을 클릭하고 드롭다운 메뉴에서 Rule 을 선택합니다.

-

규칙 유형을 선택할 수 있는 Choose Design Rule Type 대화 상자가 열립니다. Signal Integrity 규칙까지 아래로 스크롤하여 Supply Nets 을 선택한 다음 OK 을 클릭합니다.

-

Edit PCB Rule (From Schematic) - Supply Nets 대화 상자가 표시됩니다. 이 공급망의 전압을 입력하고 OK 을 클릭합니다. 규칙 항목이 Properties 패널에 나열됩니다.

신호 무결성 설계 규칙은 파라미터 세트 지시문을 사용하여 회로도에서 바로 추가할 수 있습니다.

설계를 PCB 레이아웃으로 전송한 후 해당 규칙은 PCB 설계 규칙에 추가됩니다( Design » Rules 명령을 사용하여 액세스하는 PCB Rules and Constraints Editor 대화 상자에서 PCB 편집기에서 보고 편집할 수 있음).

회로도 편집기에서 규칙의 범위(규칙이 대상으로 하는 객체 집합)는 매개변수가 추가된 위치(예: 와이어 또는 핀)에 따라 정의됩니다. PCB 편집기에서 규칙의 범위는 규칙 자체 내에서 정의됩니다.

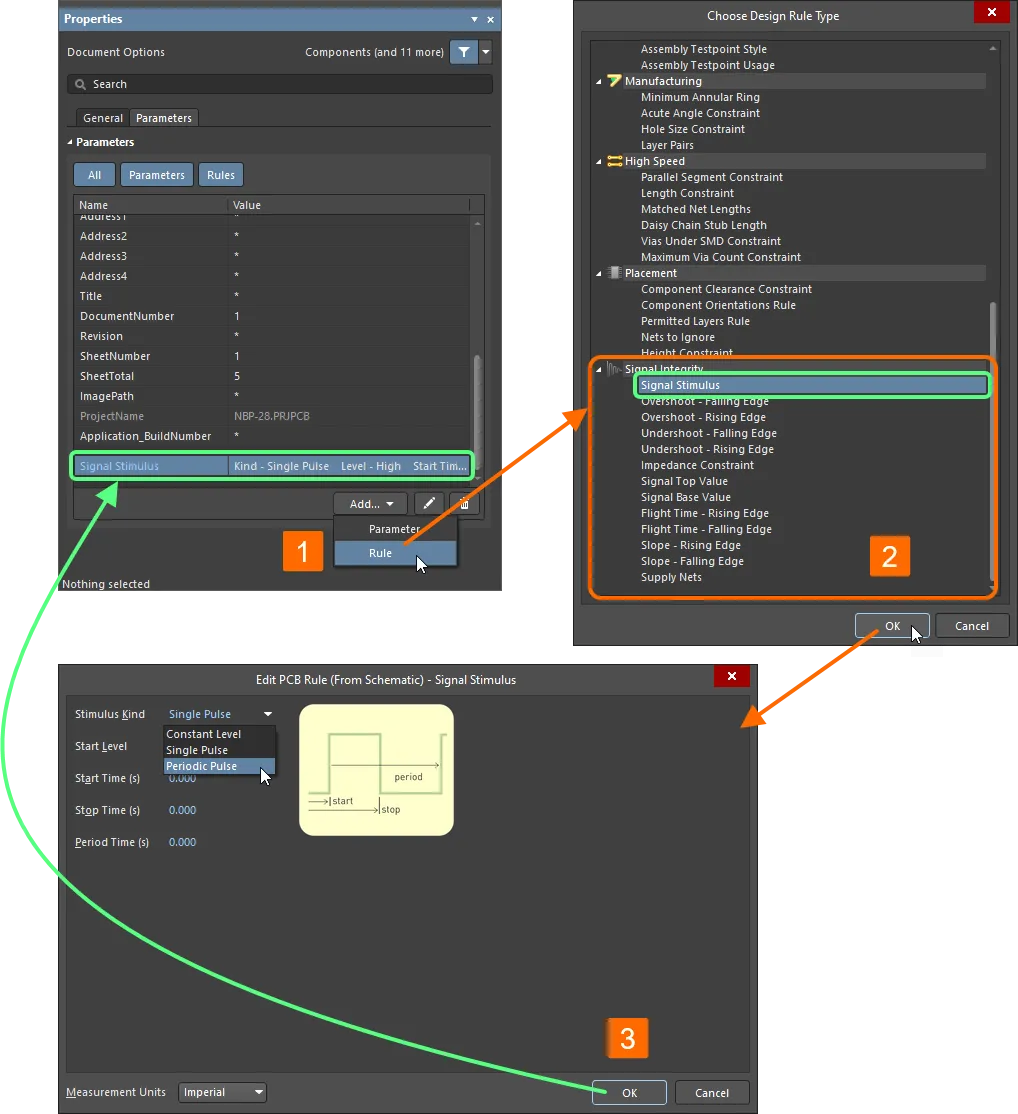

신호 자극 설계 규칙

회로도 편집기 내에서 설정할 수 있는 또 다른 설계 규칙은 신호 자극 규칙입니다. 이 규칙을 실행하면 분석 중인 네트워크의 각 출력 핀에 자극이 주입됩니다. 이를 위해서는 '모두' 범위를 사용하는 설계 규칙이 필요하므로 이 규칙에 대한 시트 매개 변수를 만들어야 합니다. 이 규칙을 설정하지 않으면 기본 규칙 옵션이 사용됩니다.

-

도식 시트에 선택된 객체가 없는 경우 Properties 패널을 엽니다. 패널의 Parameters 탭에서 Add 버튼을 클릭하고 드롭다운 메뉴에서 Rule 을 선택합니다.

-

규칙 유형을 선택할 수 있는 Choose Design Rule Type 대화 상자가 열립니다. Signal Integrity 규칙까지 아래로 스크롤하여 Supply Nets 을 선택한 다음 OK 을 클릭합니다.

-

Edit PCB Rule (From Schematic) - Signal Stimulus 대화 상자가 표시됩니다. 자극 종류, 시작 수준 및 시간을 선택한 다음 OK 을 클릭합니다. 규칙 항목이 Properties 패널에 나열됩니다.

신호 무결성 설계 규칙은 회로도 시트 파라미터로 추가할 수 있습니다.

PCB의 신호 무결성 설계 규칙

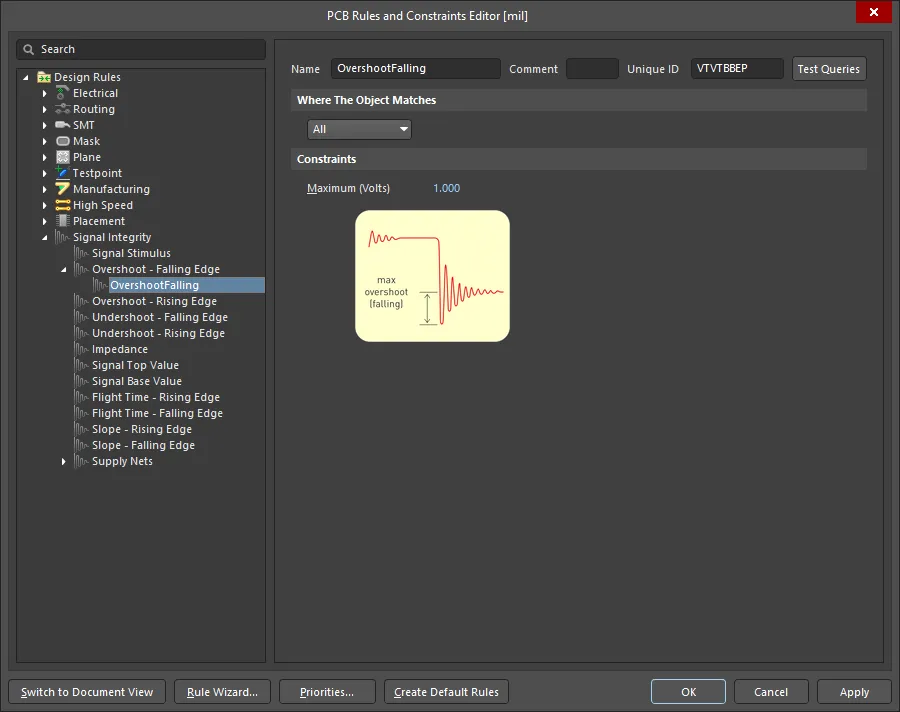

오버슈트, 언더슈트, 임피던스 및 신호 슬로프 요구 사항과 같은 신호 무결성 파라미터를 표준 PCB 설계 규칙으로 지정할 수 있습니다. PCB 에디터에서 Design » Rules 를 선택하면 이러한 규칙을 설정할 수 있는 PCB Rules and Constraints Editor 대화 상자에 액세스할 수 있습니다. 회로도 편집기에서 파라미터를 사용하여 이러한 규칙을 설정할 수도 있으며, 설계를 PCB 레이아웃으로 전송한 후 PCB Rules and Constraint Editor 대화 상자에 나타납니다.

오버슈트 - 폴링 에지 디자인 규칙을 탐색할 때의 PCB Rules and Constraint Editor 대화 상자

이 규칙에는 두 가지 목적이 있습니다. 하나는 PCB 내에서 표준 DRC 검사를 실행할 때입니다. 표준 선별 분석을 사용하여 이러한 규칙에 따라 보드를 검사할 수 있습니다. 이 규칙의 두 번째 용도는 Signal Integrity 패널을 사용할 때입니다. 이러한 규칙은 테스트로 구성하고 활성화할 수 있으며, 패널은 어떤 네트워크가 어떤 테스트에 실패했는지 그래픽으로 표시합니다.

설계가 준비되면 신호 무결성 분석을 구성하고 실행합니다.