Design Directive는 설계 캡처 중 회로도에 배치되는 객체로, 소프트웨어의 다른 부분으로 전달할 지시 사항을 지정하는 방법을 제공합니다. 다양한 Design Directive를 다음 두 가지 방식으로 사용할 수 있습니다:

-

소스 회로도 문서의 자동 컴파일과 관련된 Directive

-

회로도 시트에 정의된 정보를 PCB로 전달하는 데 사용되는 Directive

다음 섹션에서는 이러한 영역과 관련 Directive를 좀 더 자세히 살펴봅니다.

컴파일 관련 Directive

설계는 시간이 지나면서 발전하며 단계적으로 캡처됩니다. 각 단계가 어느 정도 정리되면, 설계의 나머지 부분과 분리해서 해당 단계만 확인하고 싶어지는 경우가 흔합니다. 캡처 과정 중간중간 개별 회로도 문서(또는 전체 프로젝트)를 컴파일하면, 아직 캡처되지 않은 회로나 아직 완성되지 않은 회로 블록 간 인터페이스 배선 때문에 여러 오류 메시지가 발생하는 경우가 많습니다. 이러한 메시지는 실제로 큰 가치가 없고, 중요한 정보 주변에 잡음만 더할 뿐입니다. 이런 컴파일 오류를 가장 빠르고 쉽게 억제하는 방법은 No ERC 또는 Compile Mask Directive를 배치하는 것입니다.

No ERC Directive

No ERC Directive는 회로의 노드에 배치되어, 회로도 프로젝트를 검증할 때 감지되는 모든 Electrical Rule Check 경고 및/또는 오류 위반 조건 보고를 억제합니다. 자세한 내용은 Validating Your Design Project 페이지를 참조하십시오.

Compile Mask Directive

No ERC Directive는 설계 내에서 위반이 발생한 소수의 핀, 포트, 시트 엔트리 또는 넷을 억제하는 데 매우 유용합니다. 하지만 경우에 따라서는 부품을 포함한 설계의 전체 구역을 제거하고 싶을 수도 있습니다. Compile Mask Directive(Place » Directives » Compile Mask command)를 사용하거나 Active Bar의 Directive 드롭다운에서 Compile Mask 버튼( )을 클릭하면, 해당 Directive가 포함하는 설계 영역을 Compiler에서 사실상 숨길 수 있습니다. 이를 통해 아직 완성되지 않아 컴파일 오류를 발생시킬 것이 분명한 회로에 대해 수동으로 오류 검사를 방지할 수 있습니다. 이는 활성 문서나 프로젝트를 컴파일하여 설계의 다른 특정 영역 무결성을 확인해야 하지만, 미완성 설계 부분과 관련된 Compiler 생성 메시지의 '잡음'은 원하지 않을 때 매우 유용합니다.

)을 클릭하면, 해당 Directive가 포함하는 설계 영역을 Compiler에서 사실상 숨길 수 있습니다. 이를 통해 아직 완성되지 않아 컴파일 오류를 발생시킬 것이 분명한 회로에 대해 수동으로 오류 검사를 방지할 수 있습니다. 이는 활성 문서나 프로젝트를 컴파일하여 설계의 다른 특정 영역 무결성을 확인해야 하지만, 미완성 설계 부분과 관련된 Compiler 생성 메시지의 '잡음'은 원하지 않을 때 매우 유용합니다.

이름에서 알 수 있듯이, 이 Directive는 정의된 마스크 경계 completely 안에 있는 모든 객체를 Compiler가 무시하도록 지시합니다. 마스크는 노트나 사각형 객체를 배치하듯이 정확히 같은 방식으로 배치하면 됩니다.

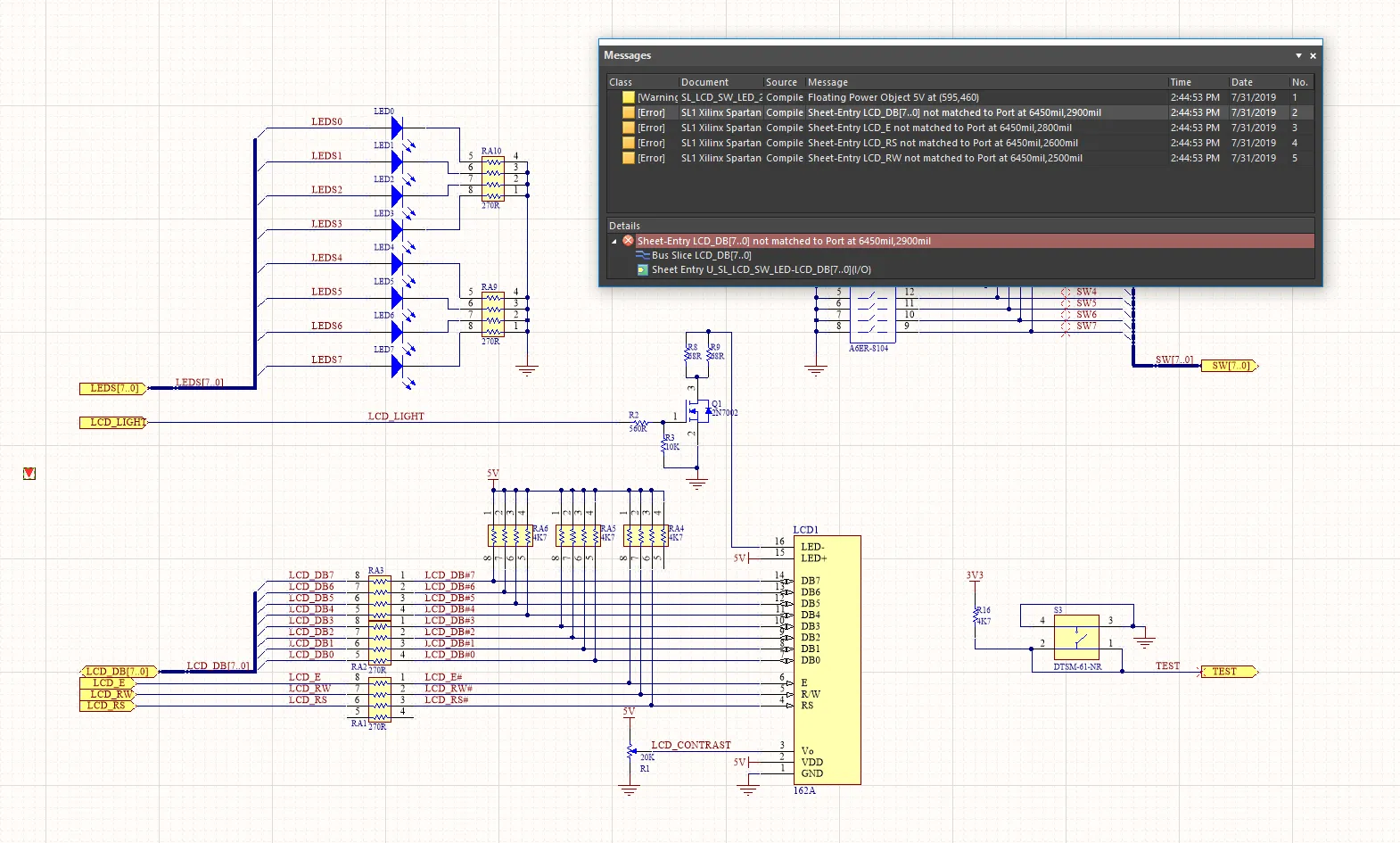

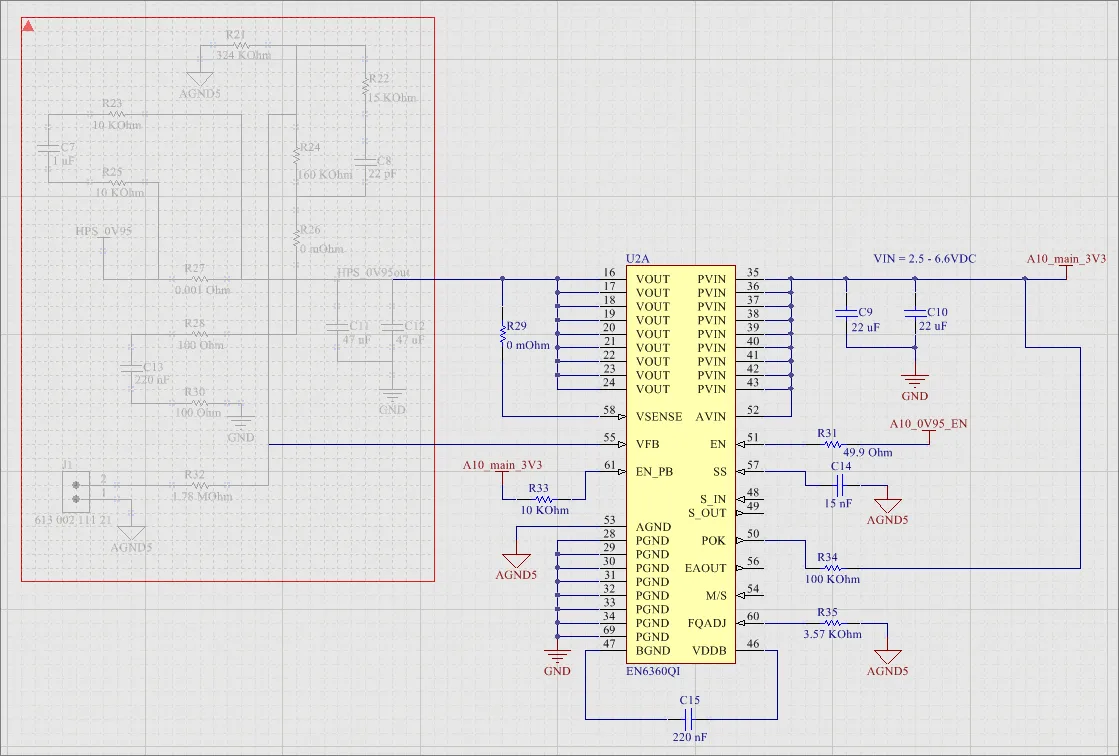

다음 이미지의 예제 회로도를 보면 LCD1 장치로 가는 배선이 아직 완성되지 않았습니다. 이 회로도만 컴파일하면(Project » Validate PCB Project) 불완전한 회로 때문에 수많은 위반 메시지(아래 표시)가 발생합니다. 이미지 위에 마우스를 올려 불완전한 회로 주변에 Compile Mask Directive를 배치했을 때의 효과를 확인해 보십시오. 그러면 이러한 위반은 Compiler에서 무시되고, 회로도에서 완전히 배선된 나머지 회로는 검사됩니다. 실제로 마스킹된 객체, 즉 마스크의 경계 사각형 안에 완전히 포함되는 객체는 회색으로 흐리게 표시됩니다.

이미지 위에 마우스를 올리면, 불완전한 회로로 인한 컴파일러 위반을 숨기기 위해 Compile Mask Directive를 사용할 때의 효과를 볼 수 있습니다.

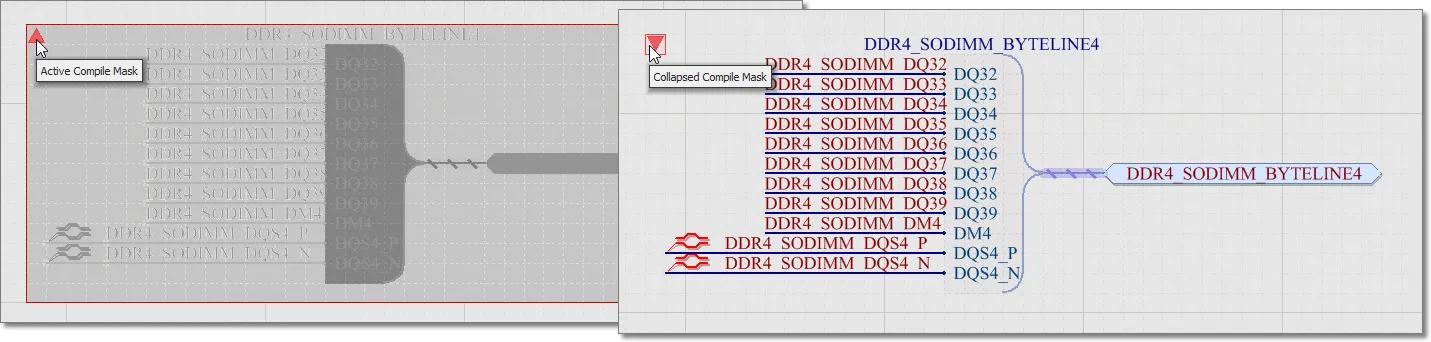

Compile Mask는 확장(전체 프레임) 모드 또는 축소(작은 삼각형) 모드로 표시할 수 있습니다. 이 모드는 각각 마스크가 활성화된 상태와 비활성화된 상태에 대응합니다. 배치된 Compile Mask의 왼쪽 상단 모서리를 클릭하여 표시 모드를 전환할 수 있습니다. 이 기능은 설계 흐름의 일부로 시뮬레이션이 포함되는 경우 특히 유용할 수 있습니다:

자세히 알아보기.

Compile Mask는 회전하거나 X축 또는 Y축을 따라 미러링할 수 있지만, 내부 설계 회로의 방향에는 아무런 영향을 주지 않습니다.

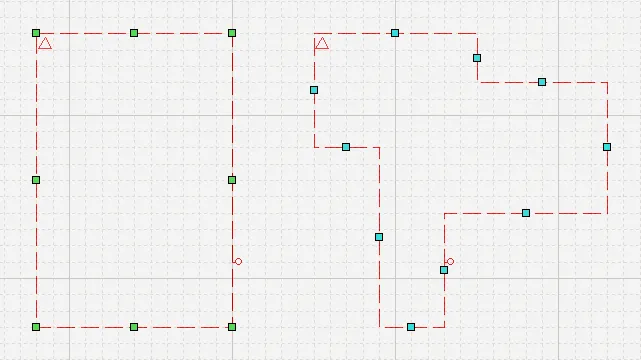

Compile Mask

위 회로도의 왼쪽에 표시된 배치된 Compile Mask.

위 회로도의 왼쪽에 표시된 배치된 Compile Mask.

요약

Compile Mask는 Project » Validate Project command를 사용해 검증을 수행할 때, 자신이 포함하는 설계 영역을 Compiler에서 사실상 숨기는 데 사용되는 Design Directive입니다. 아직 완성되지 않아 검증 오류를 발생시킬 회로에 대해 수동으로 오류 검사를 방지하는 방법을 제공합니다. Compile Mask는 현재 프로젝트를 검증하여 설계의 다른 특정 영역 무결성을 확인해야 하지만, 미완성 설계 부분과 관련된 Compiler 생성 메시지의 혼잡함은 원하지 않는 상황에서 유용합니다.

이름은 'Compile Mask'이지만, 이 Directive는 컴파일 행위 자체와 직접 관련된 것은 아닙니다. 컴파일은 Altium Designer의 Dynamic Compilation 기능에 의해 각 사용자 작업 후 자동으로 수행되기 때문입니다. 대신 Compile Mask는 사용자가 프로젝트 검증을 수동으로 실행할 때 적용됩니다. 이 검증은 컴파일과는 별개의 독립적인 과정이며, 사용자가 직접 시작해야 합니다. 그런 다음 검증은

Project Options dialog의

Error Reporting 및

Connection Matrix 탭에 정의된 설정과 함께 프로젝트 내 회로도 문서의 전기적 오류와 제도 오류를 검사합니다.

사용 가능 위치

Compile Mask는 Schematic Editor에서만 배치할 수 있습니다. Compile Mask를 배치하려면:

-

메인 메뉴에서 Place » Directives » Compile Mask command를 클릭합니다.

-

설계 공간 상단의 Active Bar 에 있는 Directive 드롭다운에서 Compile Mask 버튼(

)을 클릭합니다. 관련된 다른 명령에 접근하려면 Active Bar 버튼을 길게 클릭하십시오. 한 번 사용된 명령은 해당 Active Bar 섹션의 최상단 항목이 됩니다.

)을 클릭합니다. 관련된 다른 명령에 접근하려면 Active Bar 버튼을 길게 클릭하십시오. 한 번 사용된 명령은 해당 Active Bar 섹션의 최상단 항목이 됩니다.

-

회로도 편집기에서 마우스 오른쪽 버튼을 클릭한 다음 Place » Directives » Compile Mask를 클릭합니다.

배치

명령을 실행하면 커서가 십자선으로 바뀌며 Compile Mask 배치 모드임을 나타냅니다. 배치는 다음 순서로 수행합니다:

-

커서를 원하는 위치에 놓은 다음 클릭하거나 Enter를 눌러 마스크의 첫 번째 모서리를 고정합니다.

-

커서를 이동하여 마스크 크기를 조정하고, Compiler에서 숨겨야 하는 설계 영역을 완전히 감싸도록 한 다음 클릭하거나 Enter 를 눌러 대각선 반대편 모서리를 고정하고 마스크 배치를 완료합니다. 마스크 경계 안에 완전히 포함되는 설계 객체는 회색으로 흐리게 표시됩니다.

-

계속해서 추가 Compile Mask를 배치하거나 마우스 오른쪽 버튼을 클릭하거나 Esc를 눌러 배치 모드를 종료합니다.

그래픽 편집

이 편집 방법을 사용하면 설계 공간에서 배치된 Compile Mask 객체를 직접 선택하여 크기, 모양 또는 위치를 그래픽 방식으로 변경할 수 있습니다.

Compile Mask는 활성(전체 프레임) 모드 또는 축소(박스형 삼각형) 모드로 표시할 수 있으며, 이는 각각 마스크가 활성화된 상태와 비활성화된 상태에 대응합니다. 배치된 Compile Mask의 왼쪽 상단 모서리에 있는 ▲ 또는 ▼ 아이콘을 클릭하여 표시 모드를 전환할 수 있습니다.

왼쪽 상단 모서리의 삼각형을 클릭하면 Compile Mask가 축소되고(비활성화됨) 표시됩니다.

왼쪽 상단 모서리의 삼각형을 클릭하면 Compile Mask가 축소되고(비활성화됨) 표시됩니다.

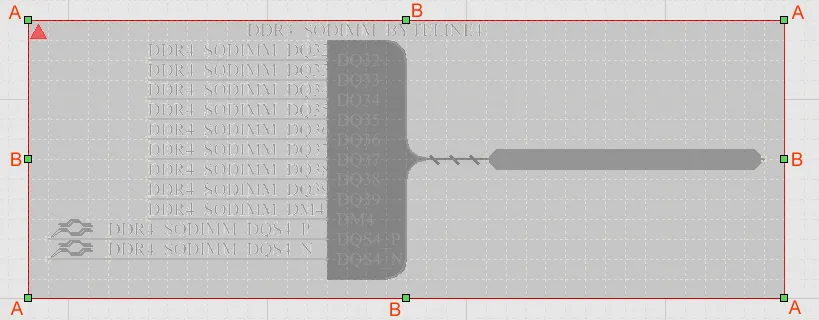

활성(확장) 상태의 Compile Mask 객체를 선택하면 다음 편집 핸들을 사용할 수 있습니다:

선택된 Compile Mask(활성 상태).

선택된 Compile Mask(활성 상태).

-

A를 클릭하고 드래그하여 Compile Mask의 크기를 수직 및 수평 방향으로 동시에 조정합니다.

-

B를 클릭하고 드래그하여 Compile Mask의 크기를 수직 및 수평 방향으로 각각 따로 조정합니다.

-

편집 핸들을 피해 Compile Mask의 아무 곳이나 클릭한 뒤 드래그하여 위치를 변경합니다. 드래그하는 동안 Compile Mask를 회전(Spacebar/Shift+Spacebar)하거나 미러링할 수 있습니다(X 또는 Y 키를 사용하여 각각 X축 또는 Y축 기준으로 미러링).

Compile Mask가 축소된 상태일 때는 새 위치로 드래그하여 위치만 그래픽 방식으로 변경할 수 있습니다.

Locked 속성이 활성화된 객체를 그래픽 방식으로 수정하려고 하면, 편집을 계속할지 확인하는 대화상자가 나타납니다. Preferences dialog의 Schematic – Graphical Editing 페이지에서 Protect Locked Objects 옵션이 활성화되어 있고, 해당 설계 객체의 Locked 옵션도 활성화되어 있으면 그 객체는 선택하거나 그래픽 방식으로 편집할 수 없습니다. 잠긴 객체를 클릭하여 선택한 다음 List panel에서 Locked 속성을 비활성화하거나, 객체를 그래픽 방식으로 편집할 수 있도록 Protect Locked Objects 옵션을 비활성화하십시오.

비그래픽 편집

다음과 같은 비그래픽 편집 방법을 사용할 수 있습니다.

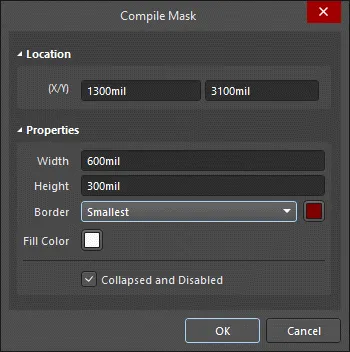

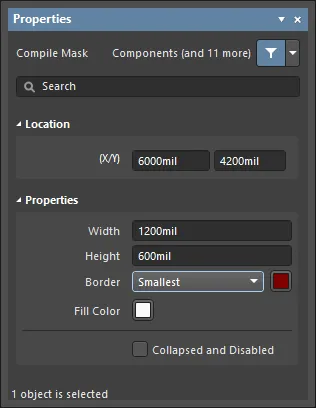

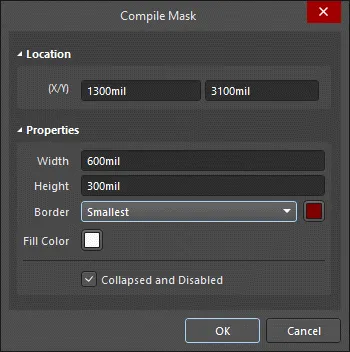

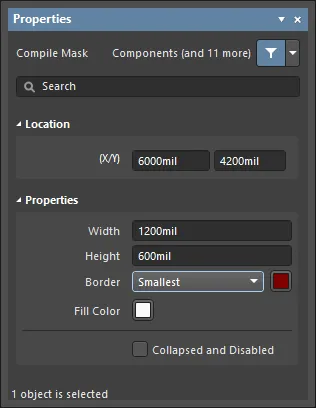

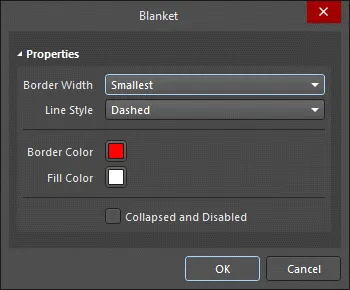

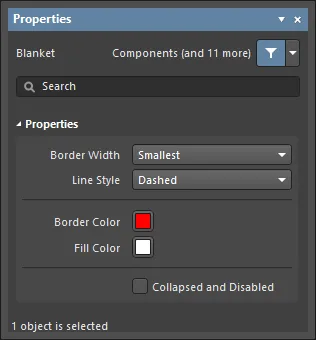

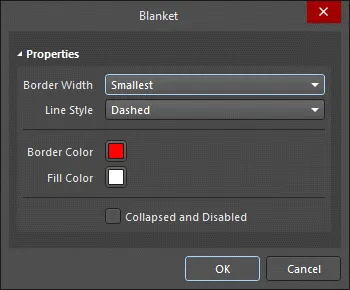

Compile Mask Dialog 또는 Properties Panel을 통한 편집

Panel page: Compile Mask Properties

이 편집 방법은 관련 Compile Mask dialog와 Properties panel 모드를 사용하여 Compile Mask 객체의 속성을 수정합니다.

배치 후에는 다음 방법으로 Compile Mask dialog에 접근할 수 있습니다:

-

배치된 Compile Mask 객체를 더블클릭합니다.

-

Compile Mask 객체를 선택하고 마우스 오른쪽 버튼을 클릭한 다음, 컨텍스트 메뉴에서 Properties를 선택합니다.

배치 중에는 Tab 키를 눌러 Properties panel의 Compile Mask 모드에 접근할 수 있습니다. Compile Mask가 배치되면 모든 옵션이 표시됩니다.

배치 후에는 다음 방법 중 하나로 Properties panel의 Compile Mask 모드에 접근할 수 있습니다:

-

Properties panel이 이미 활성 상태라면 Compile Mask 객체를 선택합니다.

-

Compile Mask 객체를 선택한 후, 설계 공간 오른쪽 하단의 Panels button에서 Properties panel을 선택하거나 메인 메뉴에서 View » Panels » Properties를 선택합니다.

기본값으로

Double Click Runs Interactive Properties 옵션이 비활성화되어 있으면(

Preferences 대화상자의

Schematic - Graphical Editing page에서 설정), 프리미티브를 더블클릭하거나 선택된 프리미티브를 우클릭한 뒤

Properties를 선택하면 대화상자가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면

Properties 패널이 열립니다.

대화상자와 패널의 옵션은 동일하지만, 옵션의 순서와 배치는 약간 다를 수 있습니다.

여러 객체 편집

Properties 패널은 여러 객체 편집을 지원하며, 현재 선택된 모든 객체에서 동일한 속성 설정은 수정할 수 있습니다. 동일한 객체 유형을 여러 개 수동으로 선택하거나, Find Similar Objects dialog, Filter 또는 List 패널을 통해 선택한 경우, 별표(*)로 표시되지 않는 Properties 패널 필드 항목은 선택된 모든 객체에 대해 편집할 수 있습니다.

List 패널을 통한 편집

Panel pages: List Panels, SCH Filter

List 패널은 하나 이상의 문서에 있는 설계 객체 유형을 표 형식으로 표시하여 객체 속성을 빠르게 검토하고 수정할 수 있게 합니다. 적절한 필터링과 함께 사용하면(패널의 Include 옵션을 사용해 객체 유형을 선택하거나, 해당 Filter 패널 또는 Find Similar Objects dialog를 사용하는 방식), 현재 활성 필터 범위에 해당하는 객체만 표시할 수 있습니다. 그러면 나열된 객체의 속성을 List 패널에서 직접 편집할 수 있습니다.

Compile Mask Properties

Schematic Editor 객체 속성은 배치된 객체의 시각적 스타일, 내용 및 동작을 지정하는 정의 가능한 옵션입니다. 각 객체 유형의 속성 설정은 다음과 같이 정의됩니다.

-

Post-placement settings – 모든 Compile Mask 객체 속성은 설계 공간에서 배치된 Compile Mask를 선택했을 때 Compile Mask 대화상자와 Properties 패널에서 편집할 수 있습니다.

대화상자와 패널의 옵션은 동일하지만, 옵션의 순서와 배치는 약간 다를 수 있습니다.

위치

-

(X/Y)

-

X (첫 번째 필드) - 현재 설계 공간 원점을 기준으로 한 객체 기준점의 현재 X(수평) 좌표입니다. 객체의 X 위치를 변경하려면 편집합니다. 값은 미터법 또는 야드파운드법 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 단위를 사용할 경우 단위를 함께 입력해야 합니다.

-

Y (두 번째 필드) - 현재 원점을 기준으로 한 객체 기준점의 현재 Y(수직) 좌표입니다. 객체의 Y 위치를 변경하려면 편집합니다. 값은 미터법 또는 야드파운드법 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 단위를 사용할 경우 단위를 함께 입력해야 합니다.

속성

-

Width - 객체의 너비를 입력합니다.

-

Height - 객체의 높이를 입력합니다.

-

Border - 드롭다운을 사용하여 원하는 테두리를 선택합니다.

-

Fill Color - 색상 상자를 클릭하여 객체에 사용할 원하는 색상을 선택합니다.

-

Collapsed and Disabled - 확인란을 선택하여 객체를 접고 비활성화합니다.

PCB 관련 지시문

통합 설계 환경인 Altium Designer는 보드 레이아웃 전에 PCB 요구사항을 정의할 수 있는 기능을 제공합니다. 이는 회로도 시트에 배치된 객체에 파라미터를 추가하고 지정함으로써 이루어집니다.

컴포넌트, 시트 심볼, 포트 등과 같은 일부 회로도 설계 객체의 경우, 해당 객체의 속성 일부로 관련 파라미터를 추가하면 됩니다. 와이어 및 버스와 같은 넷 객체의 경우에는 와이어나 버스의 속성으로 직접 파라미터를 추가할 수 없습니다. 대신 필요한 정보를 담는 파라미터는 전용 설계 지시문을 사용해 지정합니다.

다음 정보는 지시문을 사용하여 지정할 수 있으며, 설계 동기화 중 적절한 PCB 기반 정의로 전달됩니다.

-

PCB 레이아웃 제약조건

-

차동 페어

-

넷 클래스

회로도 내에 설계 지시문을 포함하면 설계 엔지니어가 명시적인 설계 제약조건을 지정할 수 있으며, 회로도가 설계의 마스터 기록으로 유지되도록 보장합니다. 설계 변경은 회로도 측에서만 수행한 뒤 PCB로 반영할 수 있습니다. 이는 여러 사람이 설계 작업을 하고 있을 때, 특히 서로 다른 지역에 떨어져 있는 경우 매우 중요할 수 있습니다. 이메일이나 전화의 연쇄로 서로 소통하려 하기보다, 설계를 작성하는 사람이 레이아웃 단계에서 특정 제약조건이 실제로 사용되도록 보장할 수 있습니다.

이 기능의 핵심은 Parameter Set directive입니다.

이는 본질적으로 사용자가 정의한 Parameter Set 객체로, 회로도 설계 내의 넷 객체와 연결할 수 있습니다. 연결된 넷에 대해 하나 이상의 설계 제약조건을 정의하려면 와이어, 버스 또는 신호 하니스에 PCB Layout 지시문을 배치합니다. 회로도로부터 PCB를 생성할 때 PCB layout 지시문에 포함된 정보는 관련 PCB 설계 규칙을 만드는 데 사용됩니다. PCB Layout 지시문으로 지정된 정보는 해당 지시문이 연결된 넷(또는 넷 집합)에만 적용됩니다.

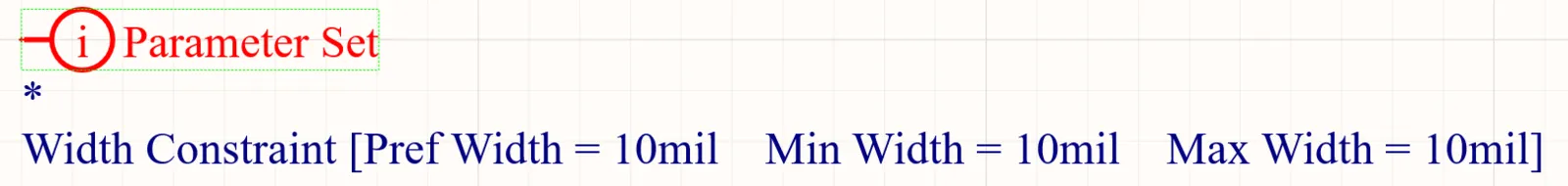

Parameter Set 지시문.

이는 Parameter Set 지시문이 연결된 넷을 대상으로 하는 임의 개수의 파라미터를 담는 컨테이너 역할을 합니다. 파라미터가 없는 기본 Parameter Set 지시문은 배치할 수 있으며(Place » Directives » Parameter Set) 관련 파라미터는 나중에 추가할 수 있습니다. 다음 섹션에서는 이러한 파라미터 기반 지시문 사용 방법을 좀 더 자세히 살펴봅니다. 사용자 정의(Parameter Set) 및 사전 정의(Differential Pair) 파라미터 세트 지시문을 모두 사용할 수 있습니다. 빈 파라미터 세트와 사전 정의된 파라미터 세트의 유일한 차이는 사전 정의된 파라미터 세트에는 아래에서 설명하는 파라미터가 포함된다는 점입니다.

Moving from Directives to the Constraint Manager

원래 설계 요구사항을 정의하는 방식은 회로도 편집기와 PCB 편집기에서 각각 별도로 처리하는 것이었습니다. 즉, 회로도 편집기에서는 Directives로, PCB 편집기에서는 Design Rules로 정의했습니다. 이러한 분리는 설계 요구사항을 정의하기 위한 별도의 편집기인 Constraint Manager의 도입으로 해소되었으며, 이를 통해 설계 프로세스의 어느 단계에서든 요구사항을 구성하고 편집할 수 있게 되었습니다. 하나의 프로젝트에서는 한 가지 방식만 사용할 수 있습니다. 이를 쉽게 확인하는 방법은 Design 메뉴에 Constraint Manager 항목이 있는지 보는 것입니다. 만약 없고(대신 PCB 편집기의 Design 메뉴에 Rules 항목이 있다면) 해당 프로젝트는 이전의 Design Rules 방식을 사용하고 있는 것입니다.

Constraint Manager를 사용하는 경우, parameter set 및 differential pair 지시문으로 정의된 넷 클래스, 차동 페어, 차동 페어 클래스 및 규칙은 회로도에서 PCB를 업데이트할 때 감지되거나 전달되지 not 않습니다. Constraint Manager에서 정의된 넷 클래스, 차동 페어, 차동 페어 클래스 및 규칙만 전달됩니다.

회로도에 배치된 지시문에서 규칙, 넷 클래스, 차동 페어 및 차동 페어 클래스를 가져올 수 있다는 점에 유의하십시오. 이는 회로도에서 접근한 Constraint Manager의 Physical 또는 Electrical 보기의 우클릭 메뉴에서 Import from Directives 명령을 사용하여 수행할 수 있습니다. 자세히 알아보기. 또한 지시문에서 Constraint Manager 로 데이터를 가져오고 해당 변경 사항을 저장한 후에는, 가져온 지시문이 회로도 설계 공간에서 파란색(약간 다른 심볼 포함)으로 구분되어 표시됩니다. 이는 지시문에서 Constraint Manager로의 단방향 전환이 이루어졌음을 나타내며, 파란색 지시문은 읽기 전용 객체가 되어 더 이상 편집할 수 없습니다.

Parameter Set

Parameter Set

요약

파라미터 세트는 회로도 설계 내의 넷 유형 객체와 설계 사양을 연결할 수 있게 해주는 설계 지시문입니다. 예를 들어 파라미터 세트를 사용하여 두 넷이 차동 페어의 구성원임을 선언할 수 있습니다. 소프트웨어는 파라미터 세트 안에 있는 특정 이름의 파라미터 존재 여부를 기준으로 어떤 설계 지시문을 배치하는지 판단합니다.

사용 가능 여부

파라미터 세트는 회로도 편집기에서만 배치할 수 있습니다. 기본(빈) 파라미터 세트 지시문과 사전 정의(Differential Pair) 파라미터 세트 지시문을 모두 사용할 수 있습니다. 빈 파라미터 세트와 사전 정의된 파라미터 세트의 유일한 차이는 사전 정의된 파라미터 세트에는 아래 설명과 같은 파라미터가 포함된다는 점입니다.

해당 명령은 메인 Place 메뉴에서 다음과 같이 접근할 수 있습니다.

| • |

Place » Directives » Parameter Set |

|

| • |

Place » Directives » Differential Pair |

|

배치

파라미터 세트는 다음 대상에 파라미터를 연결하는 데 사용할 수 있습니다.

명령을 실행하면 커서가 십자선으로 바뀌고 설계 지시문 배치 모드로 들어갑니다. 배치는 다음 동작으로 수행합니다.

-

커서를 와이어 또는 다른 넷 객체 위에 놓고 클릭하거나 Enter를 눌러 배치합니다.

-

추가 지시문을 계속 배치하거나, 우클릭 또는 Esc를 눌러 배치 모드를 종료합니다.

배치 중, 즉 파라미터 세트가 아직 커서에 떠 있는 동안 수행할 수 있는 추가 동작은 다음과 같습니다.

-

Tab 키를 눌러 배치를 일시 중지하고 Properties 패널의 Parameter Set mode 에 접근할 수 있으며, 여기서 속성을 즉시 변경할 수 있습니다. 배치를 다시 시작하려면 디자인 공간의 일시 중지 버튼 오버레이( )를 클릭하십시오.

)를 클릭하십시오.

-

초기 이동 방향에 따라 이동 방향을 수평축 또는 수직축으로 제한하려면 Alt 키를 누르십시오.

-

Spacebar를 눌러 아크를 반시계 방향으로 회전하거나, 시계 방향으로 회전하려면 Shift+Spacebar를 누르십시오. 이 작업은 객체를 드래그하는 동안에도 수행할 수 있습니다. 회전은 90° 단위로 이루어집니다.

-

배치 모드에서 X 또는 Y 키를 눌러 파라미터 세트를 X축 또는 Y축을 기준으로 뒤집을 수 있습니다.

배치 중에 속성을 수정할 수는 있지만(

Tab 를 눌러

Properties 패널 표시),

Preferences 대화상자의

Schematic – Defaults page 에서

Permanent 옵션이 활성화되어 있지 않으면 이러한 설정이 이후 배치의 기본값이 된다는 점에 유의하십시오. 이 옵션이 활성화되면 변경 사항은 현재 배치 중인 객체와 동일한 배치 세션 동안 이후에 배치되는 객체에만 영향을 줍니다.

그래픽 편집

이 편집 방법을 사용하면 디자인 공간에서 배치된 파라미터 세트 지시자를 직접 선택하고 위치나 방향을 그래픽으로 변경할 수 있습니다.

디자인 공간에서 파라미터 세트 지시자를 선택하면 지시자 주위에 점선 상자가 표시됩니다. 이 상자는 지시자가 차지하는 영역만 둘러쌉니다. 세트의 각 표시 가능 멤버 파라미터에 대해, 파라미터의 텍스트 필드와 지시자 본체를 연결하는 점선이 표시되어 연관 관계를 나타냅니다.

점선 상자 내부의 아무 곳이나 클릭한 다음 드래그하여 필요에 따라 파라미터 세트를 재배치하십시오. 드래그하는 동안 파라미터 세트는 회전(Spacebar/Shift+Spacebar)하거나 미러링할 수 있습니다(X 또는 Y 키를 눌러 X축 또는 Y축 기준으로 미러링).

파라미터 세트의 텍스트 필드(상위 지시자와 별도로 독립적으로 그래픽 편집 가능)는 Preferences 대화상자의 Schematic – Defaults page 에서 Style 옵션을 변경하여 크기와 관련된 조정만 할 수 있습니다. 따라서 이러한 객체를 선택해도 편집 핸들은 제공되지 않습니다.

점선 상자 내부의 아무 곳이나 클릭한 다음 드래그하여 필요에 따라 텍스트 객체를 재배치하십시오. 드래그하는 동안 텍스트 객체는 회전(Spacebar/Shift+Spacebar)하거나 미러링할 수 있습니다(X 또는 Y 키를 눌러 X축 또는 Y축 기준으로 미러링).

Preferences 대화상자의 Schematic – General page 에서 Enable In-Place Editing 옵션이 활성화되어 있으면, 디자인 공간에서 직접 파라미터 값을 편집할 수 있습니다(규칙으로 추가된 파라미터는 제외). 텍스트 객체를 선택한 다음 한 번 클릭하여 이 기능을 호출하십시오. 필요에 따라 새 값을 입력한 후 텍스트 객체 바깥을 클릭하거나 Enter를 눌러 변경 사항을 적용하십시오.

그래픽으로 수정하려는 객체에 Locked 속성이 활성화되어 있으면, 편집을 계속할지 확인하는 대화상자가 표시됩니다. Preferences 대화상자의 Schematic – Graphical Editing 페이지에서 Protect Locked Objects 옵션이 활성화되어 있고 해당 디자인 객체의 Locked 옵션도 활성화되어 있으면, 그 객체는 선택하거나 그래픽 편집할 수 없습니다. 잠긴 객체를 클릭하여 선택한 다음 List 패널에서 Locked 속성을 비활성화하거나, 객체를 그래픽 편집할 수 있도록 Protect Locked Objects 옵션을 비활성화하십시오.

비그래픽 편집

다음과 같은 비그래픽 편집 방법을 사용할 수 있습니다.

Parameter Set 대화상자 또는 Properties 패널을 통한 편집

Panel page: Parameter Set Properties

이 편집 방법은 연결된 Parameter Set 대화상자와 Properties 패널 모드를 사용하여 파라미터 세트 객체의 속성을 수정합니다.

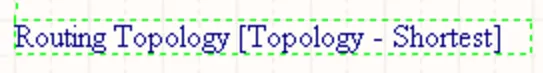

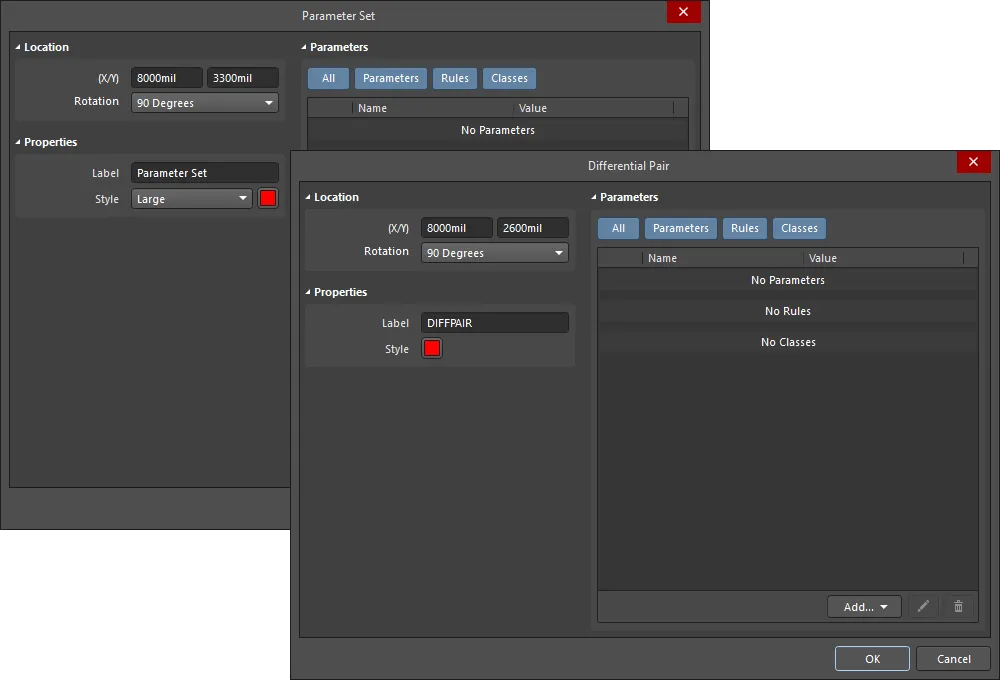

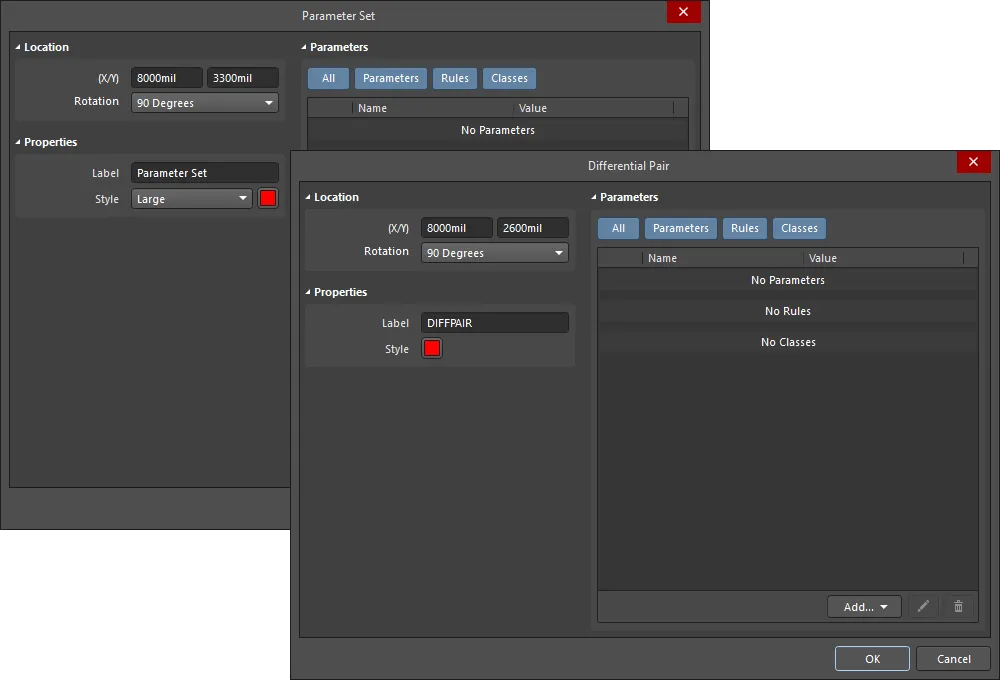

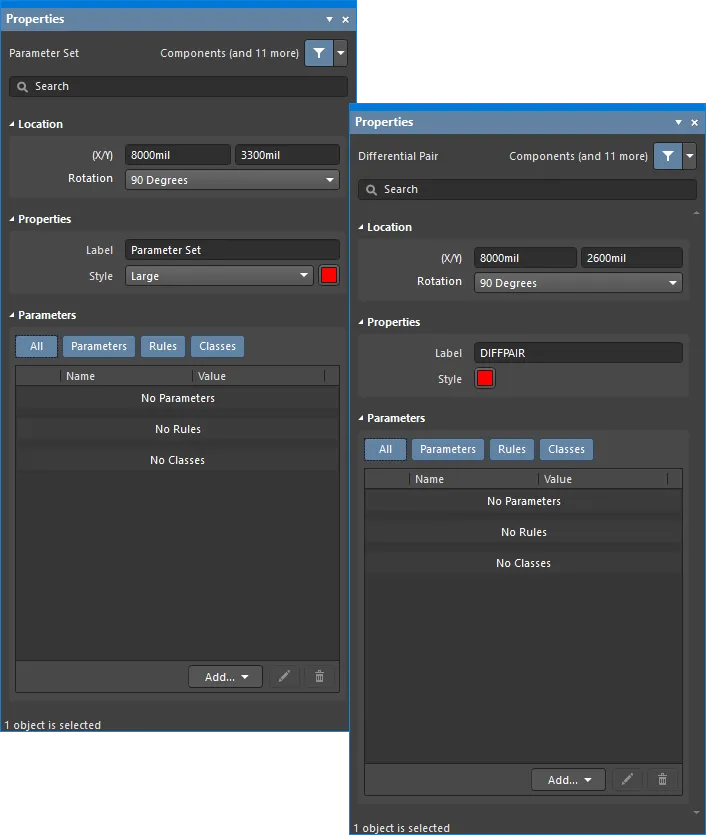

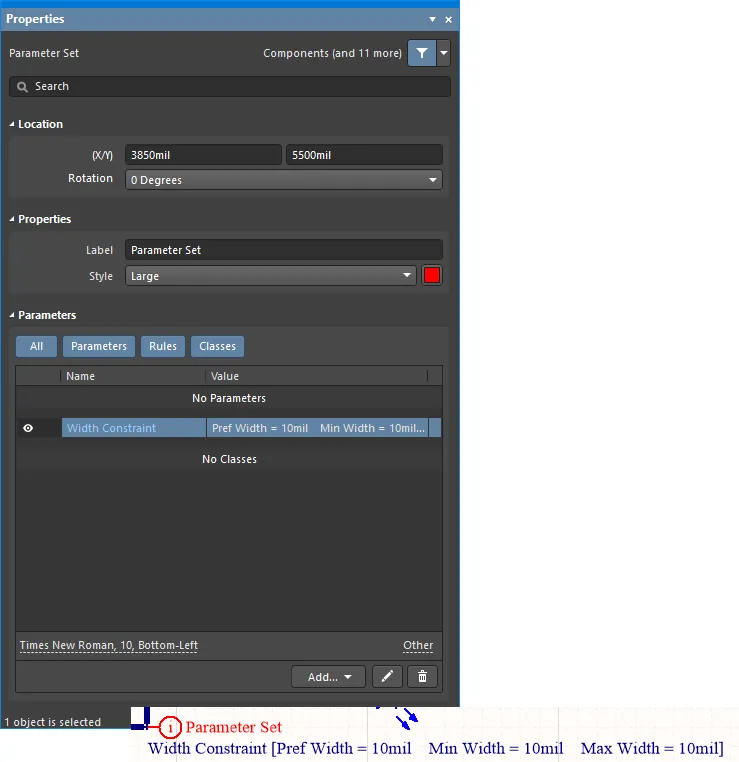

첫 번째 이미지의 Parameter Set dialog 및 두 번째 이미지의 Properties 패널 Parameter Set mode

배치 후에는 다음 방법으로 Parameter Set 대화상자에 접근할 수 있습니다.

-

배치된 파라미터 세트 객체를 더블클릭합니다.

-

커서를 파라미터 세트 객체 위에 놓고 마우스 오른쪽 버튼을 클릭한 다음 컨텍스트 메뉴에서 Properties를 선택합니다.

배치 중에는 Tab 키를 눌러 Properties 패널의 Parameter Set 모드에 접근할 수 있습니다. 파라미터 세트가 배치되면 모든 옵션이 표시됩니다.

배치 후에는 다음 방법 중 하나로 Properties 패널의 Parameter Set 모드에 접근할 수 있습니다.

-

Properties 패널이 이미 활성 상태인 경우, 파라미터 세트 객체를 선택합니다.

-

파라미터 세트 객체를 선택한 후 디자인 공간 오른쪽 하단의 Panels 버튼에서 Properties 패널을 선택하거나, 메인 메뉴에서 View » Panels » Properties를 선택합니다.

Preferences dialog의

Schematic – Graphical Editing page에서

Double Click Runs Interactive Properties 옵션이 비활성화되어 있으면(기본값), 프리미티브를 더블클릭하거나 선택된 프리미티브를 마우스 오른쪽 버튼으로 클릭한 다음

Properties를 선택할 때 대화상자가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면

Properties panel이 열립니다.

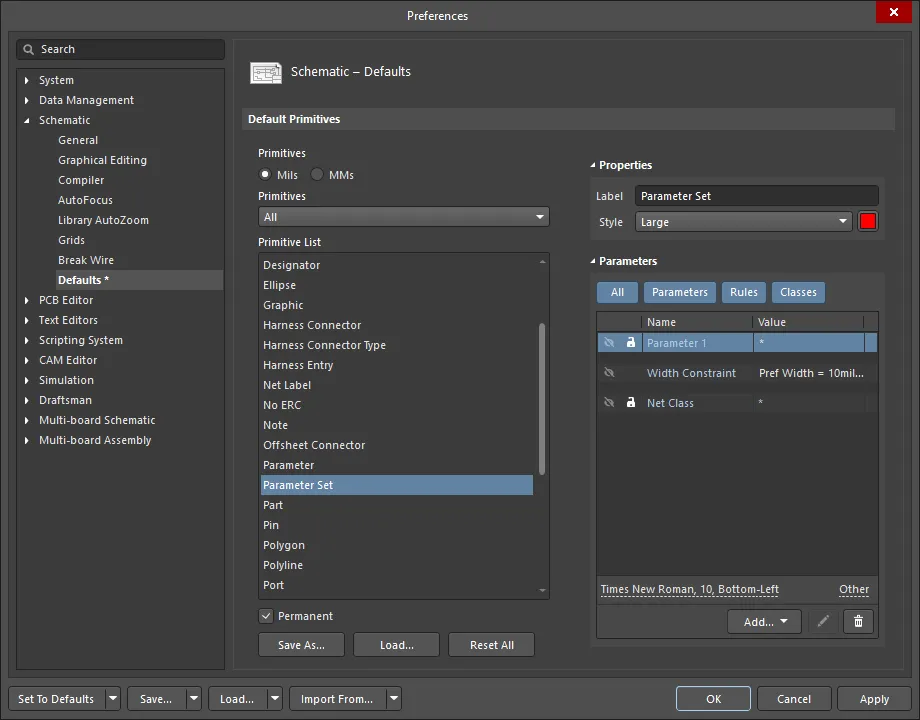

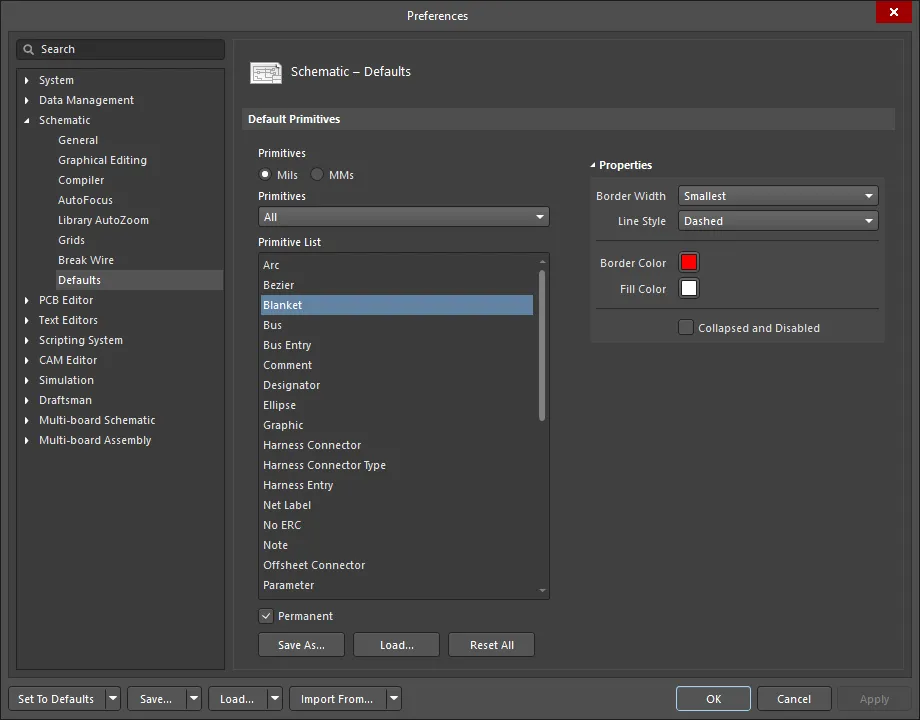

배치 모드에 들어가기 전에도

Preferences 대화상자의

Schematic – Defaults page에서 Parameter Set 속성에 접근할 수 있습니다. 이를 통해 객체의 기본 속성을 변경할 수 있으며, 이후 배치되는 객체에 적용됩니다.

여러 객체 편집

Properties 패널은 여러 객체 편집을 지원하며, 현재 선택된 모든 객체에서 동일한 속성 설정을 수정할 수 있습니다. 동일한 객체 유형 여러 개를 수동으로 선택하거나, Find Similar Objects dialog 또는 Filter 패널이나 List 패널을 통해 선택한 경우, 별표(*)로 표시되지 않는 Properties 패널 필드 항목은 선택된 모든 객체에 대해 편집할 수 있습니다.

List 패널을 통한 편집

Panel pages: List Panels, SCH Filter

List 패널을 사용하면 하나 이상의 문서에 있는 디자인 객체를 표 형식으로 표시할 수 있어 객체 속성을 빠르게 검사하고 수정할 수 있습니다. 적절한 필터링과 함께 사용하면(Filter panel 또는 Find Similar Objects dialog 사용), 현재 활성 필터 범위에 해당하는 객체만 표시할 수 있으므로 여러 디자인 객체를 더 정확하고 효율적으로 대상으로 지정하고 편집할 수 있습니다.

참고

Parameter Set Properties

회로도 편집기 객체 속성은 배치된 객체의 시각적 스타일, 내용 및 동작을 지정하는 정의 가능한 옵션입니다.

각 객체 유형의 속성 설정은 두 가지 방식으로 정의됩니다.

-

Pre-placement settings – 대부분의 Parameter Set 객체 속성, 또는 논리적으로 미리 정의할 수 있는 속성은 Schematic – Defaults page 의 Preferences dialog에서 편집 가능한 기본 설정으로 제공됩니다( 버튼을 디자인 공간 오른쪽 상단에서 클릭하여 접근). Primitive List 에서 객체를 선택하면 오른쪽에 해당 옵션이 표시됩니다.

버튼을 디자인 공간 오른쪽 상단에서 클릭하여 접근). Primitive List 에서 객체를 선택하면 오른쪽에 해당 옵션이 표시됩니다.

-

Post-placement settings – 모든 Parameter Set 객체 속성은 디자인 공간에서 Parameter Set을 선택했을 때 Parameter Set dialogs 및 Properties panel에서 편집할 수 있습니다.

Double Click Runs Interactive Properties 옵션이

Preferences dialog의

Schematic – Graphical Editing page에서 비활성화되어 있으면(기본값), 프리미티브를 더블클릭하거나 선택된 프리미티브를 오른쪽 클릭한 후

Properties를 선택하면 dialog가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면

Properties panel이 열립니다.

dialog와 panel의 옵션은 동일하지만, 옵션의 순서와 배치는 약간 다를 수 있습니다.

아래 속성 목록에서 Preferences dialog의 기본 설정으로 제공되지 않는 옵션은 "Properties panel only"로 표시되어 있습니다.

Location

-

(X/Y)

-

X (첫 번째 필드) – 현재 디자인 공간 원점을 기준으로 한 객체 기준점의 현재 X(수평) 좌표입니다. 객체의 X 위치를 변경하려면 편집합니다. 값은 미터법 또는 영국식 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 단위를 입력할 경우 단위를 함께 포함해야 합니다.

-

Y (두 번째 필드) – 현재 원점을 기준으로 한 객체 기준점의 현재 Y(수직) 좌표입니다. 객체의 Y 위치를 변경하려면 편집합니다. 값은 미터법 또는 영국식 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 단위를 입력할 경우 단위를 함께 포함해야 합니다.

-

Rotation – 드롭다운을 사용하여 회전값을 선택합니다.

Properties

-

Label – parameter set 레이블입니다. 필요하면 편집합니다.

-

Style – 드롭다운을 사용하여 스타일을 선택합니다. 색상 상자를 클릭하면 기본 색상을 선택할 수 있는 드롭다운이 열립니다.

Parameters

-

Grid – 현재 선택된 파라미터와 연결된 파라미터의 Name 및 Value를 나열합니다. 추가한 후에는 Name 및 Value 필드를 편집할 수 있습니다. Value는 해당 필드를 클릭하고 원하는 텍스트를 입력하여 이름을 지정할 수 있습니다. Name 필드는 Properties panel mode의 Parameter Set 객체에서 Ctrl+Click를 사용해야만 변경할 수 있습니다. 이 방법을 사용하면 Properties panel의 Parameter mode가 열리며, 여기서 Name 필드에 원하는 이름을 입력할 수 있습니다. 잠금 아이콘(

)을 사용하여 나열된 파라미터를 잠그거나 잠금 해제합니다. 눈 아이콘을 사용하여 파라미터를 표시하거나 숨깁니다. All 및 개별 파라미터 버튼을 전환하여 이 영역에 모든 파라미터, 개별 파라미터 또는 아무 파라미터도 표시하지 않도록 설정할 수 있습니다. 각 버튼이 회색이면 해당 파라미터는 비활성화되고, 파란색이면 활성화됩니다.

)을 사용하여 나열된 파라미터를 잠그거나 잠금 해제합니다. 눈 아이콘을 사용하여 파라미터를 표시하거나 숨깁니다. All 및 개별 파라미터 버튼을 전환하여 이 영역에 모든 파라미터, 개별 파라미터 또는 아무 파라미터도 표시하지 않도록 설정할 수 있습니다. 각 버튼이 회색이면 해당 파라미터는 비활성화되고, 파란색이면 활성화됩니다.

-

Add – 드롭다운을 사용하여 클래스 유형을 추가합니다.

-

Net Class – 새 net class를 추가하려면 선택합니다.

-

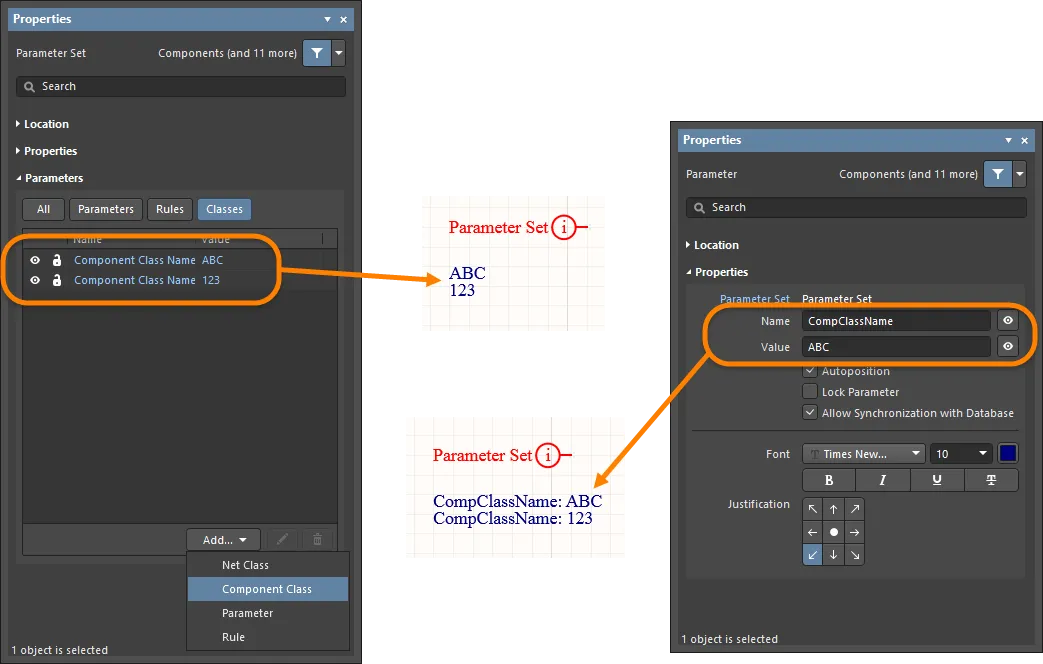

Component Class – 새 component class를 추가하려면 선택합니다. 이 옵션은 Parameter Set dialog 또는 Properties panel의 Parameter Set 반복에서만 사용할 수 있습니다.

새 클래스 Component Class Name를 추가하여 blanket 내 구성요소에 대한 파라미터를 설정할 수 있습니다. Component Class Name 를 구성요소(또는 구성요소 그룹)에 연결하면, 현재 Net Classes에서 수행되는 것과 동일하게 component class, 해당 이름 및 멤버에 대한 정보가 PCB로 전달됩니다.

-

Diff. Pair Net Class – 새 differential pair net class를 추가하려면 선택합니다. 이 옵션은 Parameter Set dialog 또는 Properties panel의 Differential Pair 반복에서만 사용할 수 있습니다.

-

Parameter – 새 파라미터를 추가하려면 선택합니다.

-

Rule – ![]() Choose Design Rule Type dialog 를 열려면 클릭합니다. 여기서 새 규칙을 선택할 수 있습니다. 새 규칙을 선택한 후 OK를 클릭하면 Edit PCB Rule (From Schematic) dialog가 열리고, 필요하면 새 규칙을 편집할 수 있습니다.

Choose Design Rule Type dialog 를 열려면 클릭합니다. 여기서 새 규칙을 선택할 수 있습니다. 새 규칙을 선택한 후 OK를 클릭하면 Edit PCB Rule (From Schematic) dialog가 열리고, 필요하면 새 규칙을 편집할 수 있습니다.

연필( ) 아이콘을 클릭하면 Edit PCB Rule (From Schematic) dialog가 열리고 선택한 항목을 편집할 수 있습니다.

) 아이콘을 클릭하면 Edit PCB Rule (From Schematic) dialog가 열리고 선택한 항목을 편집할 수 있습니다.  를 클릭하면 선택한 항목이 삭제됩니다.

를 클릭하면 선택한 항목이 삭제됩니다.

-

Font Settings – 표시된 글꼴을 클릭하여 글꼴 스타일을 변경합니다. 이 옵션은 net class, differential pair net class, parameter 또는 rule이 추가된 경우에만 사용할 수 있습니다.

-

Other – net class, differential pair net class, parameter 또는 rule이 추가된 경우 클릭하여 추가 옵션을 변경할 수 있는 드롭다운을 엽니다.

-

Show Parameter Name – 활성화하면 파라미터 이름을 표시합니다.

-

Allow Synchronization with Database – 활성화하면 데이터베이스와 동기화합니다.

-

X/Y – X 및 Y 좌표를 입력합니다.

-

Rotation – 드롭다운을 사용하여 회전값을 선택합니다.

-

Autoposition – 체크하면 자동 위치 지정이 활성화됩니다.

Parameter Set Directive 배치

이 유형의 directive는 메인 메뉴에서 Place » Directives » Parameter Set 명령을 선택하거나 디자인 공간 내에서 오른쪽 클릭하여 배치할 수 있습니다. 기본 parameter set directive를 배치할 때는 기존 파라미터가 없습니다. parameter set은 회로도 설계에서 net 유형 객체와 설계 사양을 연결할 수 있게 해주는 설계 directive입니다. 예를 들어 parameter set을 사용하여 두 net이 differential pair의 멤버임을 선언할 수 있습니다. 소프트웨어는 parameter set 안에 있는 특정 이름의 파라미터 존재 여부를 기준으로 어떤 설계 directive를 배치하는지 판단합니다.

사용자 정의 파라미터 directive 외에도, 규칙 기반 파라미터 directive는 파라미터와 연결된 Properties panel mode에서 접근 가능한 Choose Design Rule Type dialog에서 정의됩니다. 접근 방법은 다음과 같습니다.

-

Parameter Set 를 배치하기 전에 Tab를 누르거나, 이미 배치된 Parameter Set directive를 더블클릭하여 Parameter Set mode of the Properties panel을 표시합니다.

-

그런 다음 Properties panel의 Parameter Set mode에 있는 Parameters 섹션에서 Add 버튼을 클릭하고 드롭다운에서 Rule를 선택하여 Choose Design Rule Type dialog에서 규칙을 선택합니다.

규칙의 값을 편집합니다.

Choose Design Rule Type dialog를 사용하여 directive에 규칙 파라미터로 추가할 규칙을 선택합니다. 규칙 유형을 더블클릭하면 관련 Edit PCB Rule (From Schematic) dialog에 접근할 수 있으며, 여기서 해당 규칙의 제약 조건을 정의할 수 있습니다.

Edit PCB Rule (From Schematic) dialog에 표시되는 구체적인 속성은 선택한 설계 규칙에 따라 달라지며, PCB 편집기에서 해당 규칙에 대해 정의되는 속성과 동일합니다.

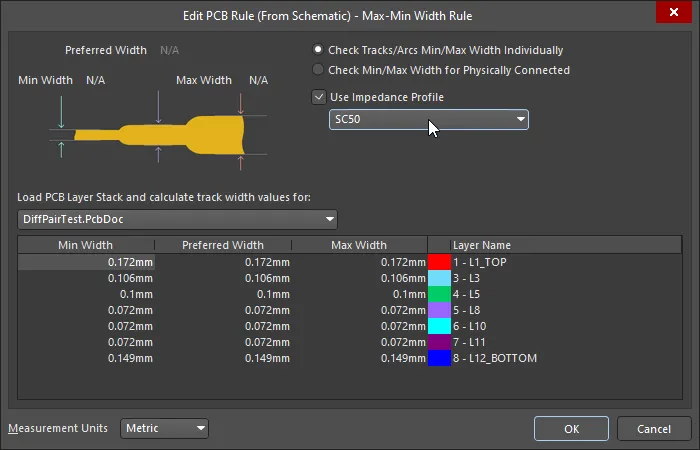

예를 들어, 아래 이미지는 Max-Min Width Rule에 대한 Edit PCB Rule (From Schematic) dialog를 보여주며, 여기서 모든 레이어에 대한 Min/Preferred/Max 설정을 구성하거나, 각 레이어의 폭 설정을 수동으로 정의하거나, Impedance Profile 사용을 선택할 수 있습니다. 임피던스 프로파일을 선택하고 실제 물리적 보드 구조가 이미 PCB 편집기에서 정의되어 있다면, Load the PCB Layer Stack and calculate the track width values할 보드 파일도 선택할 수 있습니다.

PCB가 이미 존재하고 레이어 스택이 정의되어 있다면, 계산된 폭을 회로도에 불러올 수 있습니다.

PCB가 이미 존재하고 레이어 스택이 정의되어 있다면, 계산된 폭을 회로도에 불러올 수 있습니다.

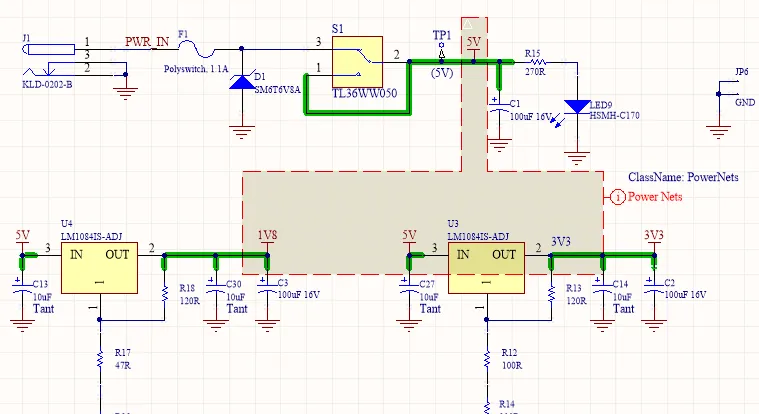

위에 표시된 규칙은 넷 클래스에 적용되었습니다. 이는 넷들을 하나의 클래스로 그룹화하기 위해 PCB Routing Directive가 연결된 Blanket Directive 를 배치한 다음, 해당 클래스에 Max-Min Width Rule을 적용하여 수행되었습니다(이미지 보기![]() ).

).

각 PCB Design Rule 및 제약 조건에 대한 자세한 내용은 여기를 클릭하십시오.

Measurement Units 드롭다운 필드를 사용하여 Metric 또는 Imperial 단위를 선택합니다.

선택한 규칙에 대한 제약 조건 지정.

Parameters 영역의 항목에는 선택한 규칙 유형과 지정된 제약 조건이 함께 표시됩니다. 다음 이미지는 Parameter Set directive에 대해 정의된 폭 제약 규칙 파라미터를 보여 줍니다. 설계 공간 내에서 규칙을 표시하려면 Rules 영역의 가시성( ) 아이콘을 클릭합니다.

) 아이콘을 클릭합니다.

Parameter Set directive를 통해 특정 넷에 대해 정의된 여러 규칙 제약 조건.

동기화 프로세스를 통해 설계가 PCB로 전송되면, directive에 포함된 정보를 기반으로 관련 설계 규칙이 생성됩니다. 생성된 각 규칙의 이름에는 해당 규칙의 출처를 구분하기 위해 Schematic라는 단어가 사용됩니다.

PCB 측에서 생성된 설계 규칙.

여러 파라미터를 동일한 Parameter Set directive에 추가할 수 있으므로 회로도를 더 깔끔하게 유지할 수 있다는 점을 기억하십시오.

Net Class Directives 배치

Net Class directive를 사용하면 회로도에서 사용자 정의 넷 클래스를 생성할 수 있습니다. Net Class directive는 메인 메뉴에서 Place » Directives » Parameter Set 명령을 선택한 다음, 명령 페이지의 팁 #2에 지정된 대로 parameter set을 net class directive로 정의하여 배치할 수 있습니다. 회로도에서 PCB를 생성할 때 Net Class directive의 정보는 PCB에서 해당 Net Class를 생성하는 데 사용됩니다. 넷을 넷 클래스의 멤버로 만들려면 관련 wire, bus 또는 signal harness에 Net Class directive를 연결한 다음 directive의 ClassName 파라미터를 원하는 클래스 이름으로 설정합니다. 이 기능을 사용하려면 the Class Generation tab of the Project Options dialog 에서 Generate Net Classes 옵션(User-Defined Classes용)을 활성화해야 합니다.

넷에 대해 Net Class directive가 정의되어 있으면, 해당 parameter set object에 의해 함께 생성되는 모든 PCB 설계 규칙은 설계가 PCB 편집기로 전송될 때 규칙 범위가 Net Class가 됩니다. 배치된 Parameter Set directive에 클래스를 추가하고 그 값을 필요한 PCB Net Class로 설정하면 해당 directive로부터 Net Class directive를 생성할 수 있습니다.

Net Classes는 PCB 편집기 내에서도 생성할 수 있지만, 넷의 논리적 기능 또는 그룹화는 일반적으로 회로도에서 훨씬 더 명확하므로 그곳에서 프로세스를 구동하는 것이 더 합리적입니다.

동기화 프로세스를 통해 설계가 PCB로 전송되면, directive에 포함된 정보를 기반으로 관련 넷 클래스가 생성됩니다.

Blanket object에 Net Class directive를 연결하면, 해당 blanket이 포함하는 개별 넷들을 멤버로 하는 넷 클래스를 생성할 수 있습니다. PCB Layout directive도 해당 blanket에 연결되어 있으면, PCB Layout directive의 규칙 파라미터는 각 개별 넷이 아니라 그 넷 클래스를 대상으로 합니다. PCB 문서로 변경 사항을 가져올 때, 그 결과 범위가 해당 넷 클래스를 대상으로 설정된 단일 설계 규칙(파라미터당 하나)이 생성됩니다.

Blanket Directives 배치

Parameter Set directives는 연결된 특정 넷만 대상으로 할 수 있지만, Blanket directive와 함께 사용하면 그 범위를 확장하여 blanket 내부의 모든 넷을 포함할 수 있습니다.

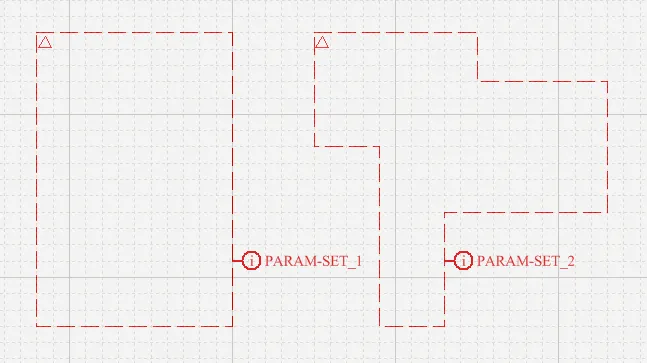

이 유형의 directive는 메인 메뉴에서 Place » Directives » Blanket 명령을 선택하여 배치합니다. blanket을 배치할 때는 단순한 직사각형 형태 또는 다각형 형태를 정의할 수 있습니다. 후자는 시트에서 필요한 넷 객체의 포함 범위를 더 정밀하게 제어할 수 있게 해줍니다.

blanket은 관심 있는 넷을 식별합니다. 해당 넷에 설계 요구사항을 적용하려면 blanket의 가장자리 아무 곳에나 Parameter Set directive를 배치하십시오. Blanket directive 아래의 넷에 둘레 directive를 적용하려면, 해당 넷과 연관된 객체(핀, 포트, 넷 라벨, 전원 포트, wire/bus/harness 세그먼트(양 끝 포함))가 blanket 경계 안에 있어야 합니다. 넷 라벨과 같은 넷 식별자의 경우 hotspot이 blanket 내부에 있어야 한다는 점에 유의하십시오. 멤버 넷이 예상대로 PCB Parameter Set으로 전달되지 않는다면 blanket의 영역을 적절히 조정해 보십시오.

blanket directive가 어떤 넷에 적용되는지 확인하려면

Net Colors 기능을 사용하여 강조 표시합니다.

View » Set Net Colors 메뉴에서 원하는 색상을 선택한 다음 필요한 Blanket directive의 둘레를 클릭합니다. 특정 넷의 강조 표시를 지우려면

View » Set Net Colors » Clear Net Color 명령을 사용한 다음, 색상을 제거하려는 넷을 클릭합니다. 모든 회로도 시트에서 넷 색상을 지우려면

View » Set Net Colors » Clear All Net Colors 명령을 사용합니다.

blanket directive를 사용하여 blanket 내부의 넷에 Parameter Set directive를 적용하는 예.

blanket directive의 사용 예는 다음과 같습니다:

-

blanket object에 Parameter Set directive를 연결하여 해당 blanket이 포함하는 각 개별 넷에 그 규칙 파라미터를 적용합니다.

-

blanket object에 Parameter Set directive를 연결하여 해당 blanket이 포함하는 개별 넷들을 멤버로 하는 Parameter Set을 생성합니다.

-

blanket object에 Differential Pair directive를 연결하여 해당 blanket 범위 내의 차동 넷을 기반으로 differential pair 객체를 생성합니다.

규칙 파라미터를 해당 Blanket이 덮고 있는 각 개별 넷에 적용하려면

Blanket object 에 Parameter Set directive를 연결하십시오. 만약 Parameter Set directive가 해당 Blanket에도 연결되어 있고, 그 Parameter Set에 Net Class 파라미터도 포함되어 있다면, Parameter Set directive의 규칙 파라미터는 각 개별 넷이 아니라 그 넷 클래스에 적용됩니다. PCB 문서로 변경 사항을 가져올 때, 그 결과 범위가 해당 넷 클래스를 대상으로 설정된 단일 설계 규칙(파라미터별)이 생성됩니다.

둘레 perimeter Parameter Set directive를 복사하여 다른 Blanket directive나 개별 와이어, 버스 또는 하니스에 연결할 수도 있습니다. 그러면 동일한 Parameter Set directive와 연관된 추가 넷들이 동일하게 생성된 PCB Net Class에 추가됩니다.

Blanket은 Parameter Set directive와 함께 사용하여 Blanket이 정의한 영역 안에 완전히 포함된 컴포넌트에 대해 컴포넌트 클래스와 파라미터를 적용하는 데에도 사용할 수 있습니다. 이를 위해 Blanket에 연결된 Parameter Set directive의 속성에서 Component Class 및 Parameter 옵션을 Add 버튼 드롭다운에서 사용하십시오. 컴포넌트 클래스와 파라미터 정보는 PCB 업데이트 시 ECO 과정 동안 프로젝트 PCB 문서로 전달됩니다.

Blanket

직사각형 Blanket과 다각형 Blanket - 각각 blanket Directive가 연결된 상태

요약

Blanket은 넷 및/또는 컴포넌트 집합 위에 배치되는 직사각형 또는 다각형 형태의 그룹 Directive 객체입니다. Blanket에 적용된 Directive(Parameter Set object)는 Blanket이 덮는 모든 넷과 컴포넌트에 적용됩니다. Blanket을 배치할 때는 단순한 직사각형 형태 또는 다각형 형태를 정의할 수 있습니다. 후자는 시트에서 필요한 넷 객체의 적용 범위를 더 정밀하게 제어할 수 있게 해줍니다.

Blanket은 다음 조건의 모든 넷에 적용됩니다.

-

Blanket이 정의한 영역 안에 완전히 포함되어 있거나,

-

와이어 / 버스 / 하니스의 연결된 끝점 vertex 중 하나 이상이 Blanket 아래에 있거나,

-

와이어 / 버스 / 하니스에 연결된 넷 라벨이 있고, 그 넷 라벨이 Blanket 아래에 있는 경우.

컴포넌트의 경우, Blanket은 Blanket이 정의한 영역 내의 모든 컴포넌트에 적용됩니다.

Blanket의 둘레에 적용된 Directive(Place » Directive)는 No ERC, Differential Pair 또는 특정 Rule/Class Parameter Set와 같은 것으로, Blanket 객체에 의해 등록된 모든 넷과 컴포넌트에 적용됩니다. Blanket은 disabled and hidden 상태로 설정할 수 있습니다.

사용 가능 위치

Blanket은 schematic editor에서만 배치할 수 있습니다. Blanket을 배치하려면:

-

메인 메뉴에서 Place » Directives » Blanket를 클릭합니다.

-

디자인 공간 상단에 있는 Active Bar 의 directives 드롭다운에서 Blanket 버튼(

)을 클릭합니다. 관련 다른 명령에 접근하려면 Active Bar 버튼을 클릭한 채 유지하십시오. 한 번 사용된 명령은 Active Bar의 해당 섹션 최상단 항목이 됩니다.

)을 클릭합니다. 관련 다른 명령에 접근하려면 Active Bar 버튼을 클릭한 채 유지하십시오. 한 번 사용된 명령은 Active Bar의 해당 섹션 최상단 항목이 됩니다.

-

schematic editor에서 마우스 오른쪽 버튼을 클릭한 다음 Place » Directives » Blanket를 클릭합니다.

배치

직사각형 Blanket을 배치하려면:

-

위에서 설명한 대로 명령을 실행합니다.

-

커서를 위치시킨 다음 클릭하거나 Enter 를 눌러 좌측 상단 모서리를 배치합니다.

-

커서를 위치시킨 다음 클릭하거나 Enter 를 눌러 우측 하단 모서리를 배치합니다.

-

마우스 오른쪽 버튼을 클릭하거나 Enter 를 눌러 배치를 완료합니다.

-

계속해서 다른 Blanket을 배치하거나, 마우스 오른쪽 버튼을 클릭하거나 Esc 를 눌러 배치 모드를 종료합니다.

다각형 형태의 Blanket을 배치하려면:

-

배치 명령을 실행합니다.

-

커서를 위치시킨 다음 클릭하거나 Enter 를 눌러 Blanket의 시작점을 고정합니다.

-

커서를 위치시킨 다음 클릭하거나 Enter 를 눌러 Blanket의 형태를 정의하는 일련의 세그먼트를 고정합니다.

-

마지막 세그먼트를 배치한 후, 마우스 오른쪽 버튼을 클릭하거나 Esc 를 눌러 배치를 완료합니다. 소프트웨어가 시작점과 마지막으로 배치한 세그먼트를 연결하는 데 필요한 세그먼트를 자동으로 추가하여 형태를 완성하므로, 다각형을 직접 '닫을' 필요는 없습니다.

-

계속해서 다른 Blanket을 배치하거나, 마우스 오른쪽 버튼을 클릭하거나 Esc 를 눌러 배치 모드를 종료합니다.

Blanket 세그먼트를 배치하는 동안 수행할 수 있는 추가 작업은 다음과 같습니다.

-

Tab 키를 눌러 배치를 일시 중지하고 Properties panel의 Blanket 모드에 접근하면, 그곳에서 라인 속성을 즉시 변경할 수 있습니다. 디자인 공간의 일시 중지 버튼 오버레이(

)를 클릭하면 배치를 재개합니다.

)를 클릭하면 배치를 재개합니다.

-

확정되지 않은 세그먼트 코너의 방향을 변경하려면 Spacebar 를 누릅니다.

-

Blanket의 다각형 형태를 정의할 때 이전에 확정한 세그먼트를 삭제하려면 Backspace 를 누릅니다. Backspace 를 연속해서 사용하면 이전 세그먼트들이 순서대로 삭제됩니다.

배치 모드는 더 가는 점선으로 표시됩니다. 이는 다각형 형태의 Blanket을 정의할 때 특히 유용합니다. 추가 세그먼트를 확정하기 전에 Blanket의 전체 형태가 어떻게 보일지 확인하는 데 사용하십시오. 복잡하거나 자기 교차하는 다각형 형태는 지원되지 않으며, 소프트웨어가 이러한 형태가 만들어지는 것을 방지합니다.

그래픽 편집

이 편집 방법을 사용하면 디자인 공간에 배치된 Blanket 객체를 직접 선택하여 크기, 형태 또는 위치를 그래픽으로 변경할 수 있습니다. Blanket 객체를 선택하면 다음 편집 핸들을 사용할 수 있습니다.

선택된 직사각형 및 다각형 Blanket과 그래픽 편집 핸들 표시.

선택된 직사각형 및 다각형 Blanket과 그래픽 편집 핸들 표시.

세그먼트 중앙의 편집 핸들을 클릭하여 드래그하면 Blanket의 해당 가장자리를 이동할 수 있습니다.

직사각형 Blanket의 경우, 모서리 편집 핸들을 클릭하여 드래그하면 수직 및 수평 방향으로 동시에 크기를 조정할 수 있습니다.

편집 핸들이 아닌 Blanket 윤곽선의 아무 곳이나 클릭하여 드래그하면 위치를 변경할 수 있습니다. 드래그하는 동안 Blanket을 회전하거나 뒤집을 수도 있습니다.

-

커서 위치를 기준으로 Blanket을 반시계 방향으로 회전하려면 Spacebar 를 누릅니다. Shift+Spacebar는 Blanket을 시계 방향으로 회전합니다. 회전은 90° 단위로 이루어집니다.

-

커서 위치를 기준으로 X축 또는 Y축을 따라 Blanket을 뒤집으려면 X 또는 Y 키를 누릅니다.

다각형 Blanket의 형태를 수정했을 때 복잡하거나 자기 교차하는 형태가 되는 경우, 해당 수정은 허용되지 않습니다.

그래픽으로 수정하려는 객체에

Locked 속성이 활성화되어 있으면, 편집을 계속할지 확인하는 대화상자가 표시됩니다.

Preferences dialog의

Schematic – Graphical Editing page에서

Protect Locked Objects 옵션이 활성화되어 있고, 해당 설계 객체의

Locked 옵션도 활성화되어 있으면, 그 객체는 선택하거나 그래픽으로 편집할 수 없습니다. 잠긴 객체를 클릭하여 선택한 다음

List panel에서

Locked 속성을 비활성화하거나,

Protect Locked Objects 옵션을 비활성화하여 객체를 그래픽으로 편집하십시오.

비그래픽 편집

다음과 같은 비그래픽 편집 방법을 사용할 수 있습니다.

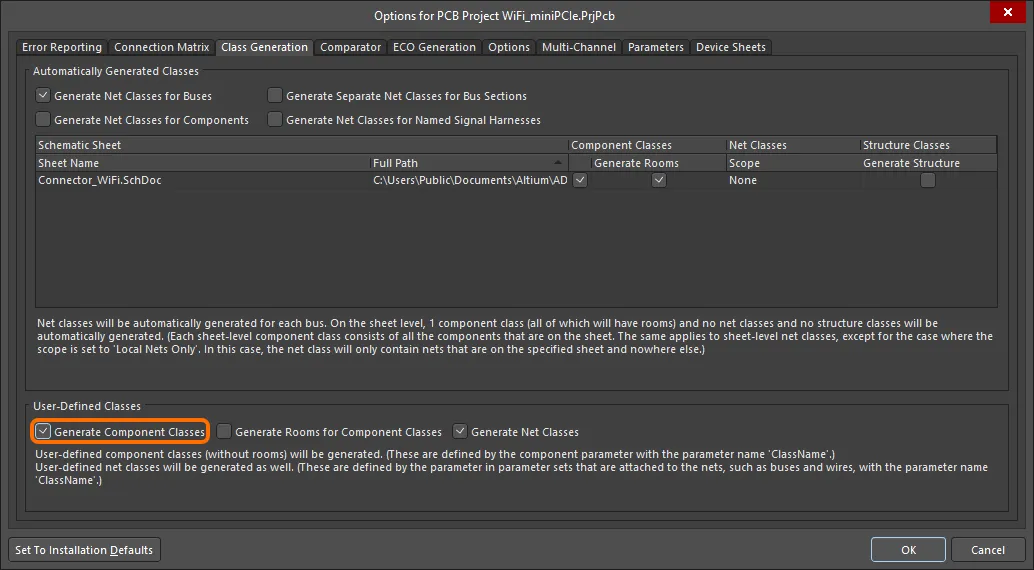

Blanket Dialog 또는 Properties Panel을 통한 편집

Panel page: Blanket 속성

이 편집 방법은 관련 Blanket dialog 모드와 Properties panel 모드를 사용하여 blanket 객체의 속성을 수정합니다.

왼쪽의 Blanket dialog와 오른쪽의 Properties panel의 Blanket 모드

왼쪽의 Blanket dialog와 오른쪽의 Properties panel의 Blanket 모드

배치 후에는 다음 방법으로 Blanket dialog에 접근할 수 있습니다.

-

배치된 blanket 객체를 더블클릭합니다.

-

커서를 blanket 객체 위에 놓고 마우스 오른쪽 버튼을 클릭한 다음 컨텍스트 메뉴에서 Properties를 선택합니다.

배치 중에는 Tab 키를 눌러 Properties panel의 Blanket mode에 접근할 수 있습니다. blanket이 배치되면 모든 옵션이 표시됩니다.

배치 후에는 다음 방법 중 하나로 Properties panel의 Blanket mode에 접근할 수 있습니다.

-

Properties panel이 이미 활성화되어 있는 경우, blanket 객체를 선택합니다.

-

blanket 객체를 선택한 후, 디자인 공간 오른쪽 하단의 Panels button에서 Properties panel을 선택하거나 메인 메뉴에서 View » Panels » Properties를 선택합니다.

Preferences dialog의

Schematic – Graphical Editing page에서

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면(기본값), primitive를 더블클릭하거나 선택된 primitive를 마우스 오른쪽 버튼으로 클릭한 후

Properties를 선택할 때

Properties panel이 열립니다.

Double Click Runs Interactive Properties 옵션이 비활성화되어 있으면 dialog가 열립니다.

dialog와 panel의 옵션은 동일하지만, 옵션의 순서와 배치는 약간 다를 수 있습니다.

여러 객체 편집

Properties 패널은 다중 객체 편집을 지원하며, 현재 선택된 모든 객체에서 동일한 속성 설정은 수정할 수 있습니다. 동일한 객체 유형을 여러 개 수동으로 선택하거나, Find Similar Objects dialog를 통해 선택하거나, Filter 또는 List 패널을 통해 선택한 경우, 별표(*)로 표시되지 않는 Properties 패널 필드 항목은 선택된 모든 객체에 대해 편집할 수 있습니다.

List 패널을 통한 편집

Panel pages: List Panels, SCH Filter

List 패널은 하나 이상의 문서에 있는 설계 객체 유형을 표 형식으로 표시하여 객체 속성을 빠르게 검토하고 수정할 수 있게 합니다. 적절한 필터링과 함께 사용하면, 즉 객체 유형을 선택하거나(패널의 Include 옵션 사용), 해당 Filter 패널 또는 Find Similar Objects dialog를 사용하여 활성 필터 범위에 해당하는 객체만 표시할 수 있습니다. 그런 다음 나열된 객체의 속성을 List 패널에서 직접 편집할 수 있습니다.

필터링 지원

논리 쿼리 식을 사용해 Blanket 객체를 대상으로 지정할 때 특히 유용한 두 가지 키워드를 사용할 수 있습니다. 이 키워드는 Blanket의 속성을 기반으로 대상을 지정하는 다른 키워드들을 보완합니다.

-

Collapsed – 객체가 접혀 있는 상태입니다(Compile Masks를 대상으로 지정할 때도 유용함). 이 키워드는 SCH Functions - Fields category 에서 찾을 수 있으며 Query Helper 사용 시 이용할 수 있습니다.

-

IsBlanket – 객체가 Blanket인지 테스트합니다. 이 키워드는 SCH Functions - Object Type Checks category 에서 찾을 수 있으며 Query Helper 사용 시 이용할 수 있습니다.

필요에 따라 설계 내 Blanket을 대상으로 지정하고 반환하는 쿼리를 위해 논리 식을 작성할 수 있습니다. Blanket을 대상으로 하는 논리 쿼리 식의 예는 다음과 같습니다.

IsBlanket And Collapsed – 현재 접혀 있는 모든 Blanket 객체를 대상으로 지정합니다.

IsBlanket And Not Collapsed – 현재 접혀 있지 않은 모든 Blanket 객체를 대상으로 지정합니다.

Blanket 비활성화

Blanket을 배치한 후에는 왼쪽 상단의 작은 삼각형( )을 클릭하여 일시적으로 비활성화할 수 있습니다. 한 번 클릭하면 Blanket이 비활성화되고 숨겨지며, 다시 클릭하면 재활성화됩니다. 이를 통해 설계에서 Blanket을 완전히 제거하지 않고도 그 영향을 편리하게 제어할 수 있습니다.

)을 클릭하여 일시적으로 비활성화할 수 있습니다. 한 번 클릭하면 Blanket이 비활성화되고 숨겨지며, 다시 클릭하면 재활성화됩니다. 이를 통해 설계에서 Blanket을 완전히 제거하지 않고도 그 영향을 편리하게 제어할 수 있습니다.

Blanket은

Properties panel에서

Collapsed and Disabled 옵션을 활성화하거나,

SCH List panel을 통해 편집할 때

Collapsed 옵션을 활성화하여 비활성화할 수도 있습니다.

Blanket Properties

Schematic Editor 객체 속성은 배치된 객체의 시각적 스타일, 내용 및 동작을 지정하는 정의 가능한 옵션입니다. 각 객체 유형의 속성 설정은 두 가지 방식으로 정의됩니다.

-

Pre-placement settings – 대부분의 Blanket 객체 속성 또는 논리적으로 미리 정의할 수 있는 속성은 Preferences dialog의 Schematic - Defaults 페이지에서 편집 가능한 기본 설정으로 제공됩니다(설계 공간 오른쪽 상단의

버튼에서 접근). Primitive List 에서 객체를 선택하면 오른쪽에 해당 옵션이 표시됩니다.

버튼에서 접근). Primitive List 에서 객체를 선택하면 오른쪽에 해당 옵션이 표시됩니다.

-

Post-placement settings – 모든 Blanket 객체 속성은 설계 공간에서 배치된 Blanket을 선택했을 때 Blanket dialog 및 Properties panel에서 편집할 수 있습니다.

Double Click Runs Interactive Properties 옵션이

Preferences dialog의

Schematic - Graphical Editing page에서 비활성화되어 있으면(기본값), 프리미티브를 더블클릭하거나 선택된 프리미티브를 오른쪽 클릭한 후

Properties를 선택하면 dialog가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면

Properties panel이 열립니다.

dialog와 panel의 옵션은 동일하지만, 옵션의 순서와 배치는 약간 다를 수 있습니다.

아래 옵션 목록에서 Preferences dialog의 기본 설정으로 제공되지 않는 옵션은 "Properties panel only"로 표시되어 있습니다.

Properties

-

Border Width - 드롭다운을 사용하여 원하는 테두리 폭을 선택합니다.

-

Line Style - 드롭다운을 사용하여 원하는 선 스타일을 선택합니다.

-

Border Color - 색상 상자를 클릭하여 테두리에 사용할 원하는 색상을 선택합니다.

-

Fill Color - 색상 상자를 클릭하여 채우기에 사용할 원하는 색상을 선택합니다.

-

Collapsed and Disabled - 체크하면 blanket이 접히고 비활성화됩니다.

간접(파라미터 기반) 지시문

Parameter Set directives는 파라미터를 포함할 수 없는 Schematic의 설계 객체를 대상으로 지정할 때 필요하지만, 파라미터를 포함할 수 있는 객체의 경우 관련 schematic 객체에 파라미터로 추가(및 정의)하여 설계 지시문을 간접적으로 적용할 수 있습니다. 본질적으로 이들은 parameter-based directives입니다.

파라미터 기반 지시문의 사용 예로는 특정 컴포넌트의 높이를 제한하거나 설계의 모든 객체를 대상으로 하는 클리어런스 제약을 추가하는 경우가 있습니다. 제약을 정의하는 데 필요한 파라미터는 규칙으로 객체에 추가됩니다.

PCB와 동기화되면 schematic의 객체에 추가된 파라미터 기반 지시문은 PCB 설계 규칙이 됩니다. 해당 PCB 설계 규칙의 범위는 파라미터가 처음 할당된 객체의 성격에 따라 결정됩니다. 다음 표는 지원되는 schematic 파라미터-대-PCB 규칙 범위 옵션을 요약한 것입니다.

각 경우 모두 규칙 기반 파라미터를 추가하는 방법은 동일합니다. 해당 탭 또는 dialog에서 다음을 수행합니다.

-

파라미터를 규칙으로 추가합니다.

-

사용할 규칙 유형을 선택합니다.

-

선택한 규칙 유형에 대한 제약 조건을 구성합니다.

schematic의 객체에 설계 규칙 파라미터를 추가하면 각 규칙 파라미터에 고유 ID가 부여됩니다. 동일한 ID가 PCB에 생성되는 해당 설계 규칙에도 부여됩니다. 이 고유 ID를 통해 규칙의 제약 조건을 schematic 측이나 PCB 측 어느 쪽에서든 편집할 수 있으며, 동기화 시 변경 사항을 반영할 수 있습니다.

컴포넌트 클래스 지정

비슷한 방식으로, 대상 컴포넌트에 ClassName 파라미터를 추가하고 그 값을 원하는 클래스 이름으로 설정하여 schematic에서 컴포넌트 클래스를 정의할 수 있습니다. 설계를 PCB로 전송하면 정의된 컴포넌트 클래스가 생성됩니다.

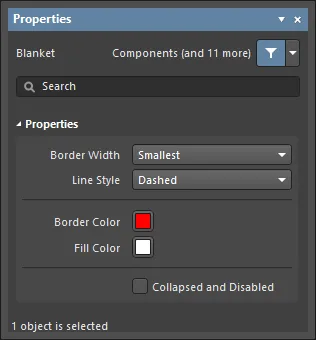

Schematic에서 정의한 Component Classes가 PCB로 전달되도록 하려면 Project Options dialog에서 다음 옵션을 설정해야 합니다.

-

dialog의 Class Generation tab에 있는 User-Defined Classes 영역에서 Generate Component Classes 옵션을 활성화합니다.

-

dialog의 Comparator tab에서 Differences Associated with Components » Extra Component Classes Mode 설정을

Find Differences로 지정합니다.

위에 나열된 Class Generation tab 옵션은 아래 이미지에 표시되어 있습니다. 이미지를 마우스로 가리키면 Comparator tab 옵션 설정을 볼 수 있습니다.

Component Classes를 PCB로 전달하려면 Class Generation tab에서 Generate Component Classes 옵션을 활성화하십시오. 이미지를 마우스로 가리키면 Comparator tab이 표시되며, 여기서 Extra Component Classes Mode 설정을 Find Differences로 지정해야 합니다.

정의가 완료되면 각 컴포넌트 속성의 Properties panel에 있는 Properties 영역에서 클래스를 잠글 수 있습니다.

PCB editor에서 컴포넌트는 여러 Component Classes에 속할 수 있습니다. 이를 schematic에서 정의하려면 schematic 컴포넌트 파라미터 값에서 각 PCB Component Class 이름을 쉼표로 구분하십시오(show image![]() ).

).

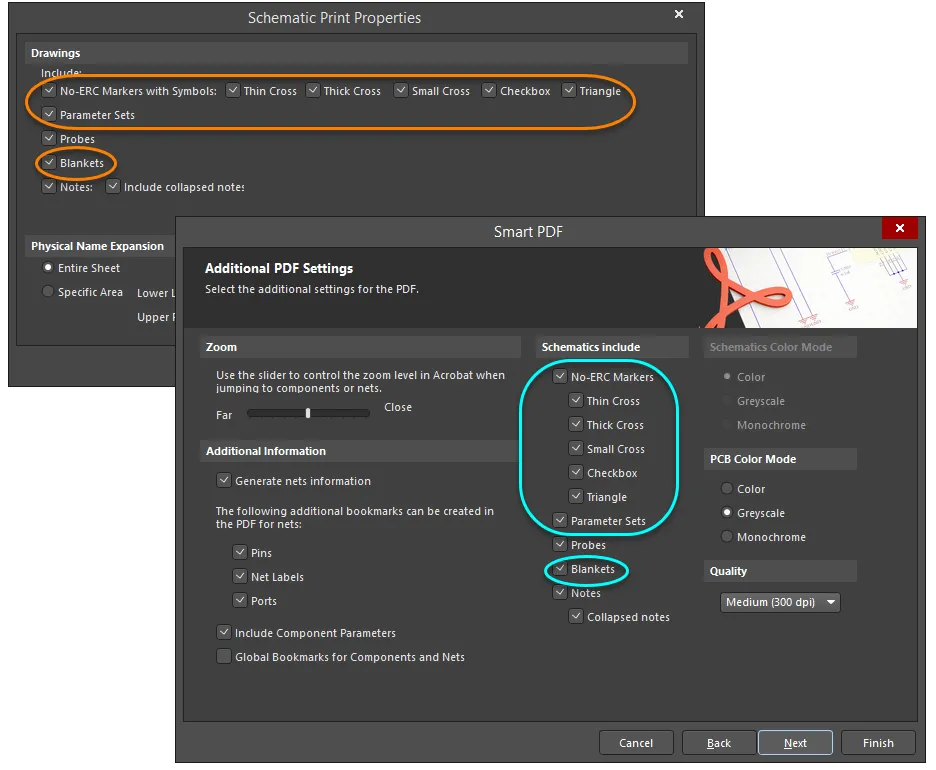

지시문 인쇄 제어

기본적으로 모든 설계 지시문은 schematic 시트 인쇄에 포함됩니다. 하지만 다음과 같이 변경할 수 있습니다.

필요에 따라 지시문의 인쇄를 제어하십시오. No ERC 지시문의 경우 특정 심볼 스타일은 인쇄하고 다른 스타일은 제외하도록 선택할 수 있습니다.

AI로 번역됨

AI로 번역됨