该软件包含多种验证检查,可在生成输出时作为输出内容包含在内。每项检查都会生成一个 HTML 报告文件。

可通过文件中 [Add New Validation Output] 控件在 Validation Outputs 区域的菜单,或通过主菜单的 Edit » Add Validation Outputs 子菜单,将验证输出添加到当前活动的 Output Job 文件中。

请注意,这些验证报告的设置保存在 OutputJob 中。当你在软件的其他位置配置某项验证检查时,其设置会随对应文件保存——例如,项目错误检查的设置存储在项目文件中,PCB DRC 设置存储在 PCB 文件中。

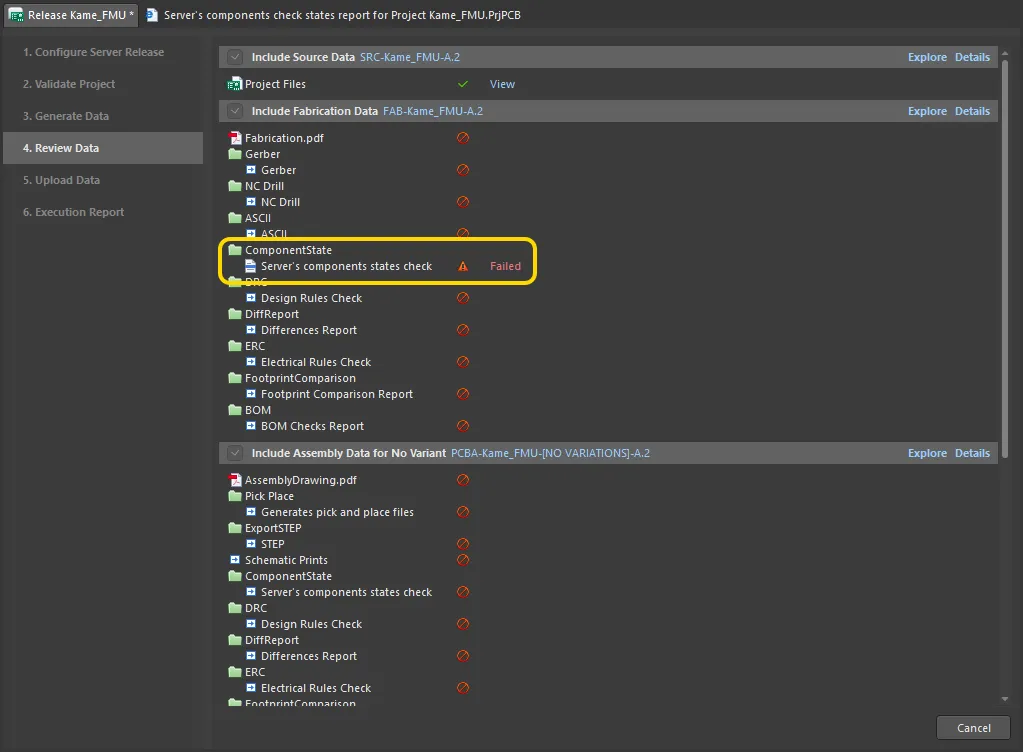

使用在已分配的 Output Job 文件中定义的验证报告,可将设计验证作为其

设计项目发布流程 的一个组成部分。每次发布都会执行这些验证检查,若有任何验证检查未成功通过,发布将失败。这能让你更安心,避免因临近发布的最后更改而将代价高昂的错误带入已发布的设计中。验证在 PCB Release 视图的流程中于

Validate Design 阶段运行。在 Design Mode 下,验证检查会在生成输出之前直接对你的项目执行。在 Release Mode 下,发布流程会先从你的项目构建一个自包含的快照,其中包含所有项目文档与外部依赖项,然后在该快照上执行验证检查。这进一步确保快照已正确捕获项目所需的全部依赖项。

验证组件状态

Workspace Components 为设计人员提供了一套正式的高质量、高完整性的设计构建模块集合。通过修订控制与生命周期管理,公司可以授权其组件库,使公司内的设计人员在每个新启动的设计项目中都能正式使用这些组件。然而,尽管组件可能已获授权可复用,仍需要在发布验证阶段进行自动检查,以确认它们确实处于可用的正确状态。

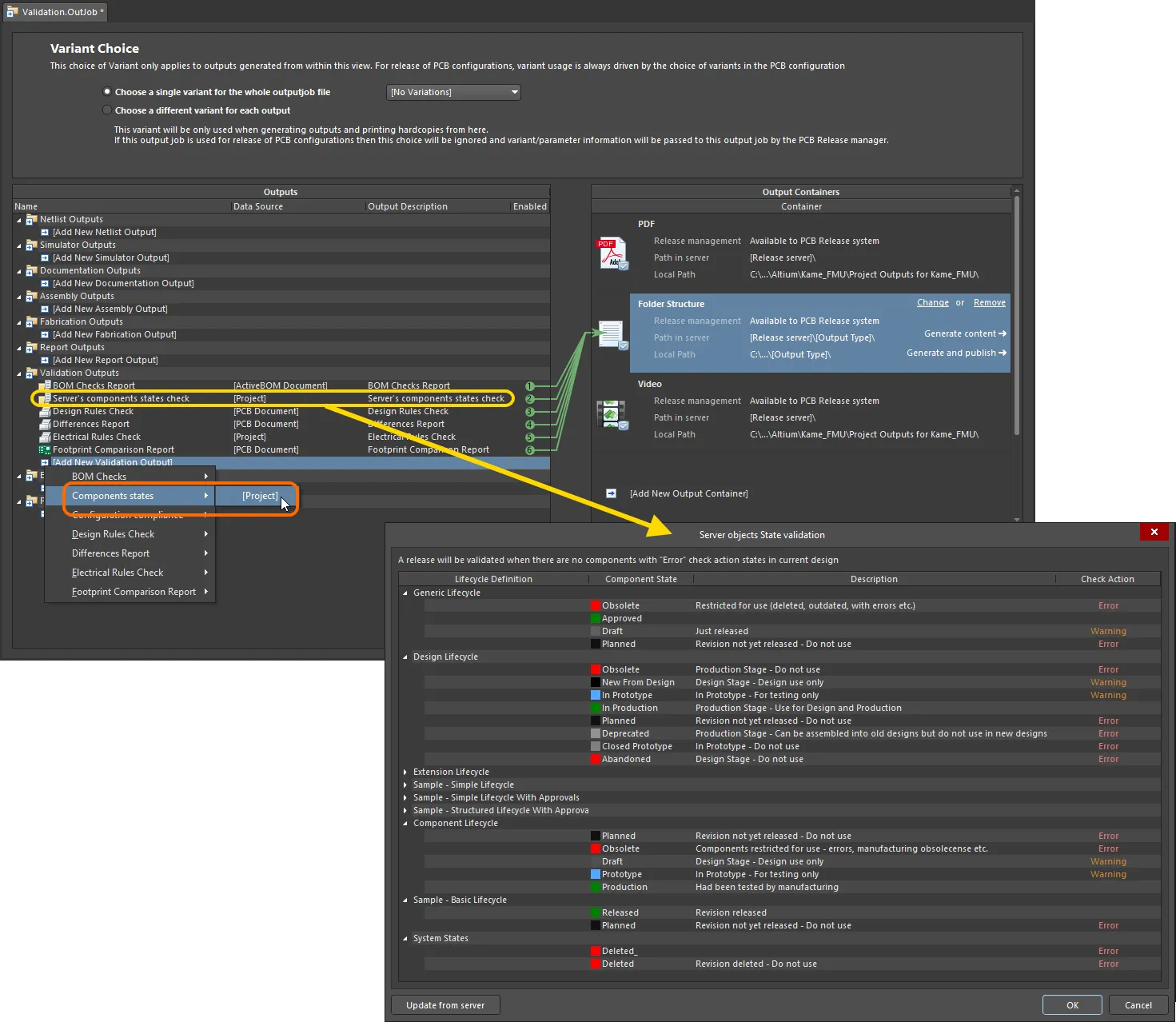

Altium Designer 结合你的 connected Workspace,以 Component State Checking 的形式为此提供了一个优雅的解决方案。可将一个基于验证的输出生成器添加到 Output Job 文件中——Components states。它可配置为检查处于受限状态的组件。在配置过程中,你需要为 Workspace 中每个当前定义的 Lifecycle Definition 的每个当前定义状态,指定要采取的动作——不采取动作、警告或生成错误。选择“生成错误”将阻止设计发布。此外,运行检查会生成一个便捷的基于 HTML 的报告,让你一目了然地看到哪些设计组件处于无效状态。

可从 Validation Outputs 部分将此类输出生成器添加到 OutJob file 中。配置在 Server objects State validation 对话框中完成。

要访问该配置对话框,可双击输出生成器条目;或右键单击其条目并从上下文菜单中选择 Configure;或选中其条目并使用 Alt+Enter 键盘快捷键。

在板卡设计发布期间,将组件状态检查添加并配置为整体验证方案的一部分。

Options and Controls of the Server objects State validation Dialog

该对话框会显示你当前连接的 Workspace 中定义的所有生命周期定义。对于每个定义,会列出每个唯一状态及其描述。对于你在设计中用于组件的每个生命周期定义所关联的每个状态,只需指定要执行的检查动作即可。单击某个状态的 Check Action 字段,并从关联的下拉菜单中选择所需动作。可用的检查选项为 None、Warning 和 Error。

单击

按钮可直接从 Workspace 刷新对话框,获取最新的生命周期定义信息。

设计中使用的 Component Items 的修订若处于受限状态(其 Check Action 被设置为 Error 的状态),将阻止板卡发布。生成的报告文件将列出所有警告与错误。

示例:在验证阶段检查组件状态时,板卡发布失败。将鼠标悬停在图像上可查看生成的报告。此处发现设计包含四个处于受限生命周期状态的组件,发布流程因此以失败终止。

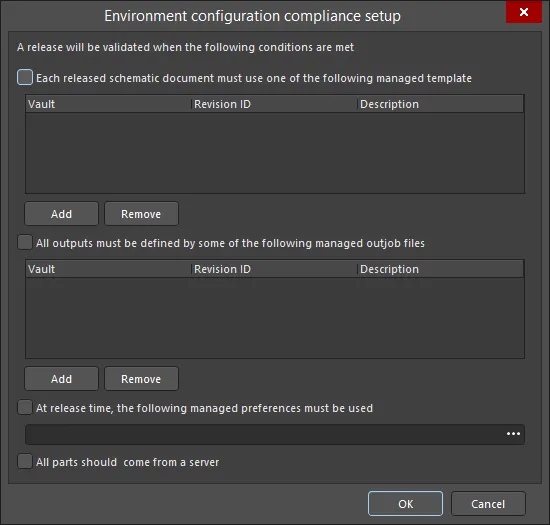

准备环境配置合规性检查报告

Environment Configuration Compliance Check 提供了一种方法,用于对设计中公司授权的数据元素的使用进行确定性测试与强制执行——也就是说,如果你未使用通过环境配置(由你被分配的角色可用)所允许的数据项,发布将失败。这可防止设计中出现“各行其是”的做法,并确保遵循与符合在企业层面集中确定的工作设计环境。

所需报告在 Environment Configuration Compliance Setup 对话框中配置。

Environment configuration compliance setup 对话框

Options and Controls of the Environment configuration compliance setup Dialog

-

Each released schematic document must use one of the following managed template - 勾选此选项以添加受管模板。该设置决定设计中源原理图文档可使用哪些受管原理图模板。

-

Add - 单击以打开 Choose Item 对话框并选择所需模板。

-

Remove - 单击以从列表中移除所选模板。

-

All outputs must be defined by some of the following managed outjob files - 勾选此选项以添加受管 outjob 文件。该设置决定可使用哪些受管 Output Job 项从设计生成输出。

-

Add - 单击以打开 Choose Item 对话框并选择所需文件。

-

Remove - 单击以从列表中移除所选文件。

-

At release time, the following managed preferences must be used - 勾选此选项以选择发布时必须使用的受管首选项。使用  选择所需首选项。

选择所需首选项。

-

All parts should come from a server - 勾选此选项以确保设计中的所有器件都来自服务器。如果勾选该选项且有一个或多个器件不来自服务器,则验证将失败。

在 Altium 365 以及 an Enterprise Server Workspace 中了解更多关于环境配置管理的信息。

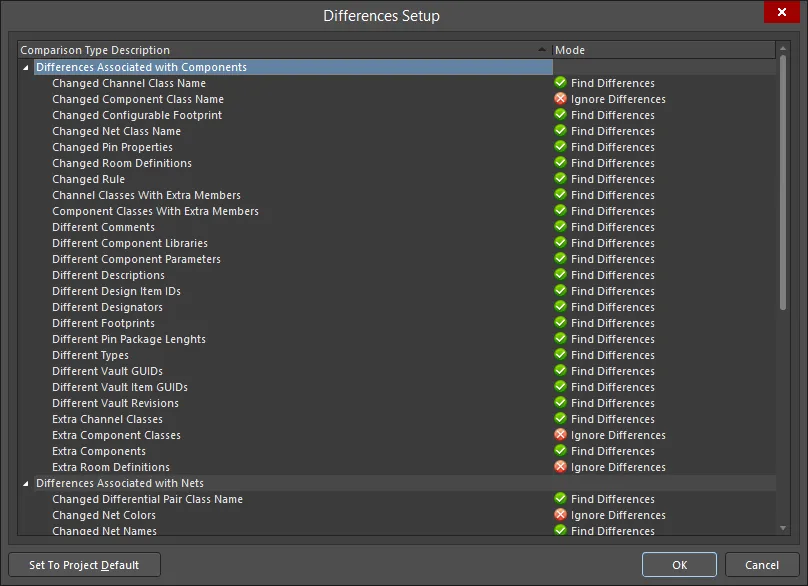

准备差异报告

Differences Report 输出生成器会生成一份报告,详细说明项目源原理图与 PCB 文档之间的差异。

所需报告在 Differences Setup 对话框中进行配置。

Differences Setup对话框

Options and Controls of the Differences Setup Dialog

-

Comparison Type Description/Mode - 这是一个列表,包含所有可供检查并生成报告的差异项。单击 Mode 列中的条目,可从以下比较类型中进行选择:

-

Ignore Differences

-

Find Differences

-

Set To Project Default - 单击以恢复为默认设置。

了解更多关于 保持原理图与 PCB 同步。

准备电气规则检查(ERC)报告

Electrical Rules Check 输出生成器会生成一份报告,详细列出项目源原理图文档中制图检查与电气检查的违规项。

所需报告在 Electrical Rules Check Setup 对话框中进行配置。

Electrical Rules Check Setup 对话框

Options and Controls of the Electrical Rules Check Setup Dialog

所选设置可以比为项目在 Project Options 中定义的设置更严格或更宽松。你可以单击 Set To Project Default 按钮,将电气规则检查的设置重置为与 Project Options 相同。

Columns 选项卡

-

Validation - 使用下拉列表定义在板卡设计发布流程中,将 ERC 输出生成器作为验证环节的一部分时所允许的最大错误等级。发布流程的验证阶段(无论是 Design 还是 Release 模式)只使用 Output Job 中定义的检查,而不使用项目级 ERC 检查。通过这种方式,你可以定义一套更严格/更刚性的检查要求,从而确保更高的设计数据完整性。选项包括:

、

、  、

、  。

。

-

Suppressed Errors - 启用此选项以报告任何被抑制(suppressed)的错误。

-

Show Columns - 选择在 ERC 报告中显示哪些列。选项包括 Class、Document 和 Message。随着选择的进行,Preview 区域会更新以显示列设置。

-

Preview - 根据对话框各选项卡中定义的错误检查进行验证后,显示当前为设计检测到的错误。更改某个检查级别后,设计会动态重新验证(重新编译),预览区域也会随之更新。使用 Show Columns 区域中的选项可切换预览区域内相应列的显示。

Error Reporting 选项卡

此选项卡用于定义在编译项目时,源原理图文档中可能存在的各类违规项的报告级别。项目编译时,这些违规设置将与 Connection Matrix 选项卡配合使用,以测试源文档中的违规情况。任何被发现且报告级别为 No Report、 Warning、 Error, 或 Fatal Error 的违规项,都会在 Messages 面板中显示为违规消息。此外,如果启用了在原理图上显示编译器错误与警告(在 Preferences 对话框的 Schematic - Compiler Preferences 页面中启用),违规对象下方会显示彩色波浪线标记。

Violations Grid

该区域展示项目源文档中可能存在的所有违规项。违规项按以下类别归类:

每种具体的违规类型都包含以下字段:

-

Violation Type Description - 对该违规类型的简要描述。

-

Report Mode - 使用此字段指定违反该检查时对应的严重级别。使用下拉列表从以下报告级别中选择:

Right-Click Menu

右键菜单提供以下命令:

-

All Off - 将所有违规类型的 Report Mode 设置为 No Report。

-

All Warning - 将所有违规类型的 Report Mode 设置为 Warning。

-

All Error - 将所有违规类型的 Report Mode 设置为 Error。

-

All Fatal - 将所有违规类型的 Report Mode 设置为 Fatal Error。

-

Default - 将所有违规类型的 Report Mode 恢复为默认设置。

可使用标准多选方式(Ctrl+click、Shift+click)选择多个违规类型。

Notes

-

使用 Connection Matrix 选项卡可专门为与引脚、端口和页入口相关的电气违规指定报告级别。

-

设计中可能存在一些你知道会被标记为电气违规、但你不希望被标记的点。要抑制这些违规,请在这些位置放置一个 No ERC 原理图设计指令对象。

-

通常更好的做法是先使用默认设置编译设计并检查警告。对于当前设计而言不构成问题的警告,可以再调整其报告级别。

Connection Matrix 选项卡

此选项卡显示一个矩阵,用于建立元件引脚与网络标识符(如 Ports 和 Sheet Entries)之间的连通性规则。它定义哪些逻辑或电气条件需要报告为警告或错误。例如,输出引脚连接到另一个输出引脚通常会被视为错误,但两个相连的无源引脚则不会。

项目编译时,这些违规设置将与 Error Reporting 选项卡中定义的设置配合使用,以测试源文档中的违规情况。任何被发现且报告级别为 No Report、Warning、Error、 或 Fatal Error 的违规项,都会在 Messages 面板中显示为违规消息。此外,如果启用了在原理图上显示编译器错误与警告(在 Preferences 对话框的 Schematic - Compiler 页面中启用),违规对象下方会显示彩色波浪线标记。

Matrix

该矩阵展示所有可能的布线连接检查:包括引脚、端口与页入口的各种组合之间的检查,以及对未连接实体的测试。矩阵按横向/纵向方式读取,行列交叉处的矩阵元素颜色用于指定编译器在测试该特定条件时的响应方式。

要更改矩阵中某个违规检查的报告模式,只需单击两类实体所在行与列交叉处的彩色方块。每单击一次,模式会切换到下一个报告级别。支持以下级别:

当鼠标悬停在某个方块上时,矩阵下方会显示文本,用于描述该违规项及其报告模式。

Right-Click Menu

右键菜单提供以下命令:

-

All Off - 将矩阵中的所有条目设置为 No Report。

-

All Warning - 将矩阵中的所有条目设置为 Warning。

-

All Error - 将矩阵中的所有条目设置为 Error。

-

All Fatal - 将矩阵中的所有条目设置为 Fatal Error。

-

Default - 将矩阵中的所有条目恢复为默认设置。

Notes

-

使用 Error Reporting 选项卡可为更多电气与制图违规指定报告级别。

-

设计中可能存在一些你知道会被标记为电气违规、但你不希望被标记的点。要抑制这些违规,请在这些位置放置一个 No ERC 原理图设计指令对象。

Additional Control

了解更多关于 验证你的设计项目。