電子設計において、回路の繰り返しセクションを含むことは珍しくありません。それはステレオアンプであるかもしれませんし、64チャンネルのミキシングデスクであるかもしれません。このタイプの設計は、マルチチャンネル設計として知られる機能セットによって完全にサポートされています。

ビデオマルチプレクサーの2つのデコーダーチャンネル。マルチチャンネル設計構造を使用すると、デコーダーチャンネルは一度だけキャプチャされます。

マルチチャネル設計では、繰り返される回路を一度キャプチャし、その後、ソフトウェアに必要な回数だけ繰り返すよう指示します。設計が自動的にコンパイルされると、ユーザー定義のチャネル命名スキームに従って、必要な回数だけ全てのコンポーネントと接続性がメモリ内で展開されます。

キャプチャした論理設計は実際にはフラット化されず、ソースは常にマルチチャネルの回路図として残ります。それをPCBレイアウトに転送すると、物理的なコンポーネントとネットが必要な回数だけ自動的にステップアウトされます。回路図とPCBの間で作業するために利用可能な標準のクロスプロービングおよびクロスセレクティングツールに完全にアクセスできます。また、PCBエディタには、1つのチャネルの配置とルーティングを他の全チャネルに複製するツールがあり、1つのチャネル全体を簡単に移動および再配置する機能があります。

動的コンパイル

関連ページ: 設計プロジェクトの検証

設計の接続モデルは、ユーザー操作ごとに動的コンパイルを通じて段階的に更新されます。プロジェクトを手動でコンパイルする必要はありません。これは自動的に行われます。設計プロジェクトにおいて、自動コンパイルプロセスは3つの機能を実行します:

- 設計階層をインスタンス化します。

- すべての設計シート間のネット接続を確立します。

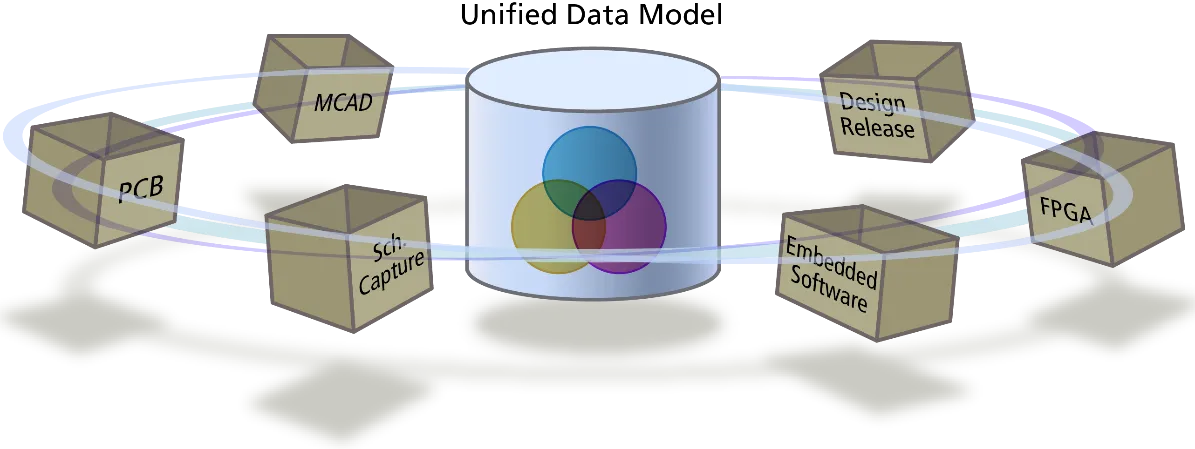

- 設計の内部統一データモデル(UDM)を構築します。

これにより、行われた設計変更がナビゲーターおよびプロジェクトパネルに即座に反映されることが保証されます。

プロジェクトのコンパイルされたモデルは、統一データモデル(UDM)として参照されます。UDMには、設計内のすべてのコンポーネントの詳細な説明と、それらがどのように接続されているかが含まれています。

UDMとコンパイラ設定の間の論理的、電気的、およびドラフトのエラーをチェックするためには、プロジェクトを検証する必要があります。このコマンドは、メインメニューから Project » Validate Projectコマンドを選択するか、プロジェクトパネルでプロジェクトのエントリを右クリックして、コンテキストメニューからValidate Projectコマンドを選択することでアクセスできます。

コンパイラによって検出された違反は、メッセージパネルに警告および/またはエラーとしてリストされます。コンパイラは、ソースドキュメントの違反をチェックする際に、プロジェクトタイプに適用される場合、プロジェクトのオプションダイアログのエラーレポートおよび接続マトリックスタブで定義されたオプションを使用します。

Altium Designer 20.0より前のバージョンでは、Unified Data Modelを構築するためにプロジェクトを手動でコンパイルする必要がありました。それ以降、デザインデータモデルはユーザー操作ごとに動的コンパイルを通じてインクリメンタルに更新され、Dynamic Data Model(DDM)と呼ばれるものが作成されます。プロジェクトの手動コンパイルは一切関与せず、すべて自動的に行われます。デザインの接続モデルも、動的コンパイルのおかげでユーザー操作ごとにインクリメンタルに更新されます。

Unified Data Model

マルチチャネル設計を理解するには、デザインデータがどのように管理されているかを理解することが役立ちます。ソフトウェアの基本的な要素はUnified Data Model(UDM)です。プロジェクトが自動的にコンパイルされると、デザインプロセスの中心に位置する一つの統合されたモデルが作成されます。そのモデル内のデータは、ソフトウェア内のさまざまなエディターやサービスを使用してアクセスおよび操作することができます。さまざまなデザイン領域ごとに別々のデータストアを使用するのではなく、UDMはデザインのすべての側面、コンポーネントとその接続性を含むすべての情報を収容するように構造化されています。

統合データモデルは、すべてのエディタに設計データを利用可能にし、マルチチャネル設計のような高度な機能を提供するのに役立ちます。

UDMは、階層型設計システムと組み合わせて、マルチチャネル設計機能を提供するために活用されます。「チャネル」とは、シートシンボル内の回路であり、このシートシンボルの下には単一のシートがあるか、またはプロジェクト構造の全体の枝が含まれている場合があり、他のサブシートを含むことができます。また、チャネル内にチャネルを作成することもでき、2レベルのマルチチャネル設計では、上位のチャネルをバンクと呼び、下位のものをチャネルと呼びます。

この完全な、PCB準備が整った記述がメモリ内に存在するため、コンポーネントの指定やネットなど、繰り返されるオブジェクトを扱うための体系的な方法がある限り、回路の一部を繰り返すことが可能です。体系的な命名は、プロジェクトのオプションダイアログのマルチチャネルタブで定義されています。以下で説明します。

マルチチャネル設計の作成

設計がマルチチャネルであるとは、回路の一部が繰り返されることを意味します。これはシートシンボルレベルで行われ、以下のいずれかの方法で実現します:

- 同じ子スキーマを参照する複数のシートシンボルを配置するか、または

- 必要な回数だけ子スキーマを繰り返すように単一のシートシンボルを設定する

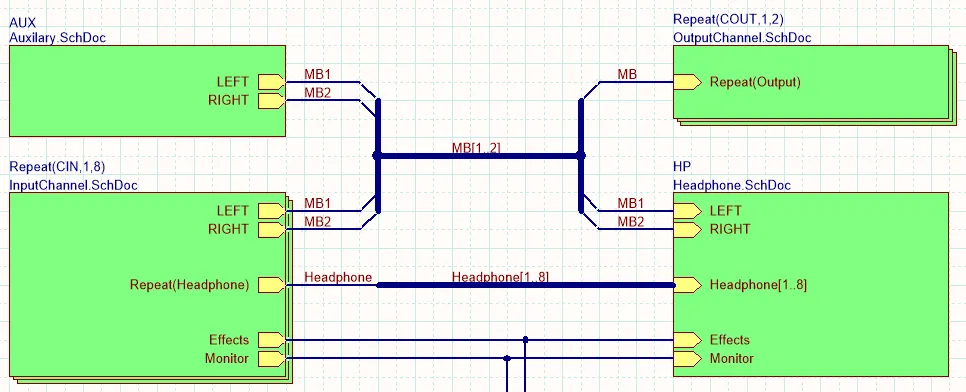

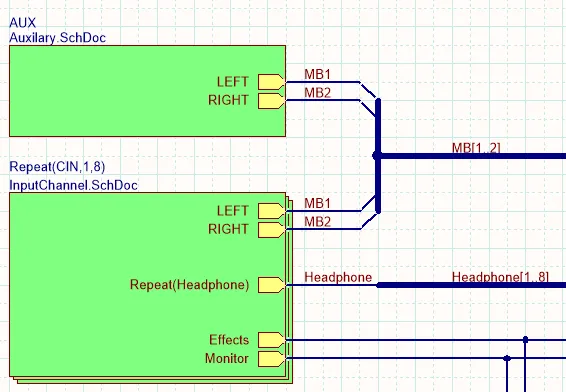

最初の画像 - 4つのシートシンボルがあり、すべて同じ子シート(PortIO.SchDoc)を参照しています。二番目の画像 - Repeatキーワードを使用して、InputChannel.SchDocが8回、OutputChannel.SchDocが2回繰り返されています。

上記の画像には、マルチチャネル設計を作成するための2つのアプローチが示されています。最初の画像では、同じ子シート(PortIO.SchDoc)を参照する4つのシートシンボルがあります。2番目の画像では、InputChannel.SchDocが8回繰り返され、OutputChannel.SchDocが2回繰り返されており、これはシートシンボルのデザインネータフィールドにRepeatキーワードが存在することによります。

プロジェクト内の繰り返されるコンポーネントのデザインネータとネット名は、標準的な命名規則を使用して解決されます。例えば、一つの命名規則は、繰り返されるコンポーネントとネット識別子(ネットラベルおよびポート)にチャネルインデックスを追加することです。これは、以下の画像のハイライトで示されています。

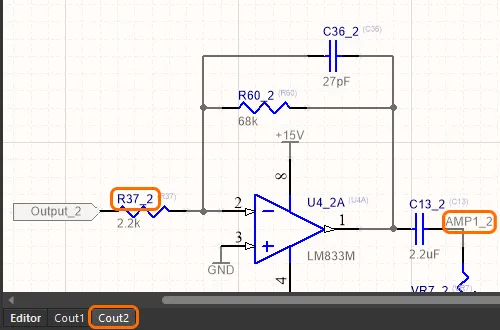

プロジェクトを開いたときに、回路図の下部に表示されるタブに注目してください。エディタータブには、あなたがキャプチャした論理設計が含まれています。他のコンパイルされたタブ(COUT1およびCOUT2)も表示され、これらはPCBエディターに転送される物理設計を表しています。物理チャネルごとにタブがあります。

コンパイルされたプロジェクトで、論理ビューのタブとPCBに転送される各物理チャネルのタブが表示されます。繰り返される指定子とネット識別子の管理方法に注目してください。

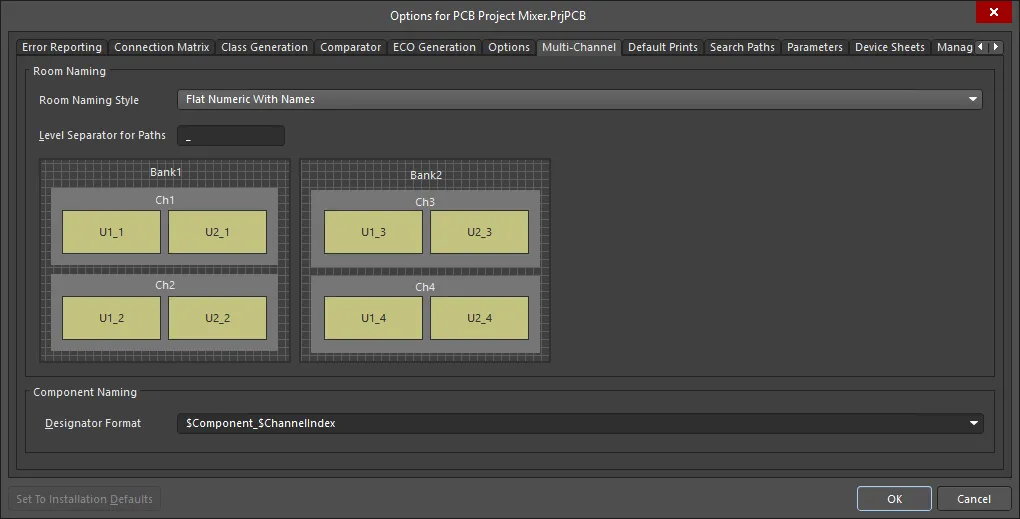

チャネル命名規則は、プロジェクトのオプションダイアログのマルチチャネルタブで定義されています。

Repeatキーワード

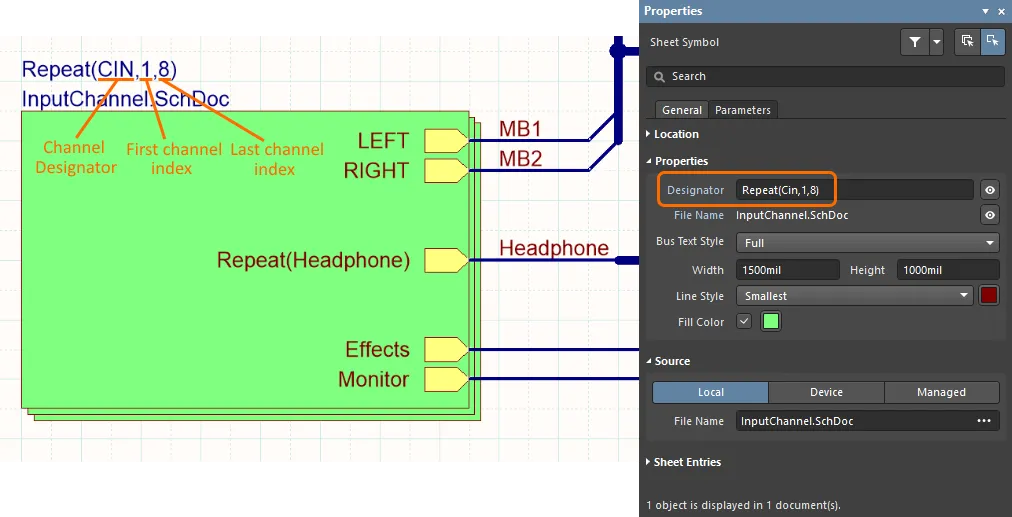

上記で述べたように、チャネルは同じ子シートを参照する複数のシートシンボルを配置するか、シートシンボルの指定子フィールドにRepeatキーワードを含めることで繰り返されます。Repeatキーワードを使用すると、シートシンボルは重ねられたシートシンボルのセットとして描画されます。

Repeat文はチャネル指定子とチャネル数を定義します。シートシンボルが重ねられたシンボルのセットとして描かれていることに注目してください。これは繰り返されるチャネルを示しています。

各チャネルは、シートシンボルのデザイン指定子から来るチャネル指定子によって識別されます。複数のシートシンボルを配置してデザインがチャネル化される場合、チャネル指定子は各シートシンボルに定義されたデザイン指定子の値です。デザインがRepeatキーワードの使用によってチャネル化される場合、チャネル指定子はRepeatキーワードによって定義されたChannelIdentifier+ChannelIndexです。

Repeatキーワードが使用される場合のデザイン指定子フィールドの構文は以下の通りです:

Repeat(<ChannelIdentifier>,<ChannelIndex_1>,<LastChannelIndex_n>)

シートシンボルの新しいインデックス付けオプションが

プロジェクトオプションダイアログのオプションタブで有効になっている場合、繰り返されるシートシンボルの最初または最後のインデックスとして、0を含む任意の数字または数値を使用できます。ただし、最後のインデックスは常に最初のインデックスより大きくなければならず、負の数は使用できません。

マルチチャネル命名

一度キャプチャしてから繰り返すことができるという概念 - マルチチャネル設計 - は、ソフトウェアの統一データモデル(UDM)を基盤として構築されています。繰り返されるコンポーネントは、以下に示すように、プロジェクトのオプションダイアログのマルチチャネルタブで設定される体系的な命名スキームを使用して名付けられます。

このダイアログには、ルームの命名を制御するための上部セクションと、それらのルーム内のコンポーネントの命名を制御するための下部セクションが含まれています。ルームレベルでは、2つのフラットな命名スタイルと3つの階層的な命名スタイルがあり、通常、設計にチャネル内のチャネルがある場合にのみ、階層的な命名スタイルを選択する必要があります。それ以外の場合は、フラットなルームの命名スタイルの方が短くて理解しやすいです。

コンポーネントの命名については、$Component$ChannelAlpha または $Component_$ChannelIndex オプションが、最も短く、最も容易に解釈できるコンポーネント指定を提供します。また、利用可能なキーワードを使用して、独自の指定子命名スキームを構築することも可能です。

繰り返し使用されるコンポーネント(およびネット)は、プロジェクトオプションダイアログのマルチチャネルタブで選択された体系的な命名規則を適用することによって管理されます。

- コンポーネントだけでなく、コンポーネント命名スキームは、各チャネル内のネットを一意に識別するために使用されます。このスキームは、ネットラベルやポートを含むネット識別子の名前を変更するために使用されます。

- これらの名前が回路図シート上に表示される方法については、下記のコンパイル済み名前の表示セクションで説明します。

ルームの役割

ルームは、PCBデザインオブジェクトであり、ボード上のエリアを定義するために使用され、次の2つの方法で使用できます:

- オブジェクトを含む - ルームは任意の多角形の形状のオブジェクトとして配置されますが、実際には設計ルールとして作成されます。ルームの定義の一部は、そのルームに含まれる必要があるオブジェクト(多くの場合はコンポーネント)を指定することです。そのルームが移動すると、ルーム内のすべてのコンポーネントも移動します。

- 他の設計ルールの範囲を定める - 自身がルールであると同時に、ルームは他の設計ルールの範囲を定めるためにも使用できます。例えば、あるネットクラスのルーティング幅を定義する設計ルールがある場合、より高い優先度を持つ設計ルールがルームの範囲でそのネットクラスに適用される異なる幅を指定することができます。

ルームはマルチチャネル設計に非常に適しています。設計が回路図エディタからPCBエディタに転送される際に、クラス生成タブのプロジェクトオプションダイアログのオプションに基づいて、各シートシンボルごとに自動的に作成することができます。そのチャネル内のコンポーネントをクラスタリングするだけでなく、そのルーム内のコンポーネントの命名にルームを使用することができます。ルームとそのボード設計プロセスにおける役割については、この記事のマルチチャネルPCB設計セクションでさらに詳しく説明されています。

フラットなコンポーネント番号システムを好む場合は、ボードレベルアノテーションを実行することで、体系的な命名スキームを置き換えることが可能です。ボードレベルアノテーションとは、コンポーネントの指定子がPCBになる運命の完全なコンパイル済み設計(物理設計)にのみ適用されるため、この名前が付けられています。

マルチチャネル設計における接続性

マルチチャネル設計の場合、ネット識別子スコープを自動、階層的、または厳格な階層に設定します。マルチチャネル設計は階層的でなければならず、ソフトウェアはこの構造モデルを使用して、設計がコンパイルされるときにメモリ内でチャネルをインスタンス化します。

繰り返されるチャネルに接続するネットに対して、ソフトウェアがサポートする必要がある接続要件は2つあります。ネットは以下のいずれかになります:

これに対するサポートレベルは、チャネルを定義するために使用された方法(複数のシートシンボル、またはRepeatキーワードを介して)によって異なります。設計が複数のシートシンボル(各チャネルごとに個別のシートシンボル)を使用する場合、ネットの接続性は、設計者によって配置された配線によって明示的に定義されます。

この設計ではRepeatキーワードを使用して複数のチャネルを作成しています。

設計でRepeatキーワードを使用する場合、以下の接続規則が適用されます。

| 全チャネルへのネットの渡し方 |

あるネットを全てのチャネルで利用可能にするには、シートエントリに接続するだけです。上の画像で示されているように、Monitor ネットが InputChannel.SchDoc シートシンボルに接続されています。ネット Effects、MB1、MB2 も全てのチャネルで利用可能になります。バス内のネットも同様に扱われます。バスがシートエントリに接続されると、そのバス内の各要素が全てのチャネルで利用可能になります。 |

| 特定のチャネルへのネットの渡し方 |

バスから単一のネットを各チャネルに割り当てるには、シートエントリで Repeat キーワードを使用します。上の画像で、シートエントリの名前が Repeat(Headphone) となっている Headphone バスが示されています。この場合、ネット Headphone1 はチャネル CIN1 に、Headphone2 はチャネル CIN2 に接続され、以下同様です。Repeat キーワードを使用してチャネルを作成した場合、個々のネットをただ一つのチャネルにのみ渡すことはできません。これが必要な場合は、各チャネルごとに個別のシートシンボルを配置する必要があります。 |

Repeatキーワードを使用する際にハーネスをチャネルに渡すことはサポートされていないことに注意してください。

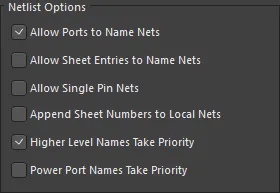

ネットの命名方法

最終的に、PCB上の各ネットは1つの名前しか持つことができません(1つのPCBネットが2つの名前を持つことはできません)。ソフトウェアは自動的に複数の名前を持つネットをプロジェクト内で単一の名前に解決します。これは、ネットが意味のある方法でラベル付けされるように、マルチチャネル設計で命名オプションを設定することが重要です。ネット命名オプションは、プロジェクトのオプションダイアログのオプションタブのネットリストオプションセクションにあります。

マルチチャネル設計でこれらのオプションを設定する良い方法は、上位の名前を優先するオプションを有効にし、チャネル化された子シートに接続するすべてのネットにネットラベルを配置することです。

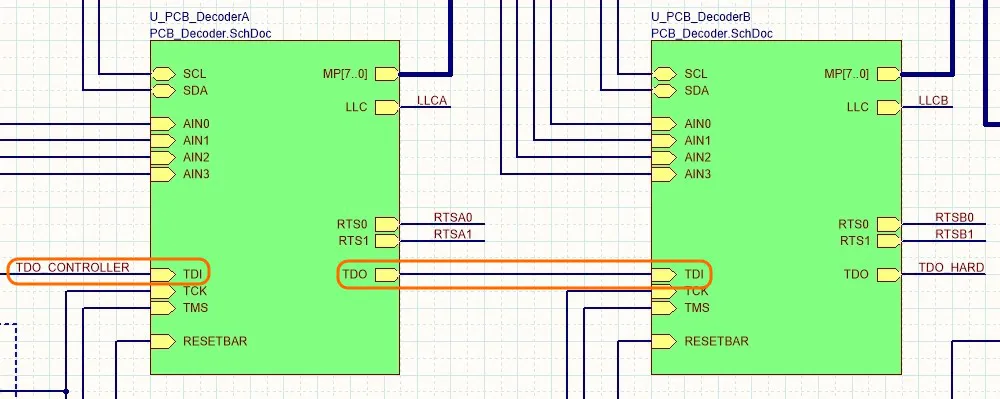

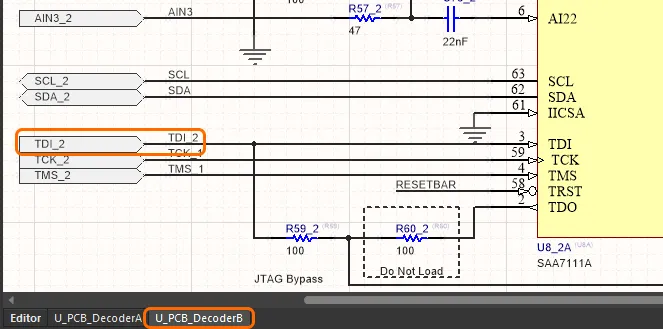

例として、以下の画像を考えてみてください。両方のシートシンボルがPCB_Decoder.SchDocシートを指しているため、この回路にはU_PCB_DecoderAとU_PCB_DecoderBの2つのチャネルがあります。

シートシンボルには、JTAG境界スキャンチェーンのTest Data InラインであるTDIというシートエントリが含まれています。TDO(テストデータ出力)はDecoderAから次のデバイスのTDIに接続され、そのデバイスはDecoderBチャネルにあります。

2つのデコーダチャンネルは、同じ回路図PCB_Decoder.SchDocを参照する2つのシートシンボルを配置することで作成されます。

プロジェクトを開くと、回路図ビューの下部にU_PCB_DecoderAおよびU_PCB_DecoderBのチャネルタブが表示されます。これらのタブは、PCBエディタに渡される物理設計を示しています。下の画像では、デコーダ回路の回路図がキャプチャされたとおりにエディタタブの左下に表示され、その回路図の2つの物理チャネル、U_PCB_DecoderAおよびU_PCB_DecoderBが続きます。

元のキャプチャされた回路図では、ネットは設計者によってTDIとラベル付けされました(最初の画像)。ソフトウェアが、より高いレベルのネット名であるTDO_CONTROLLERをDecoderAタブに適用したことに注意してください(2番目の画像)。これは、この設計で優先されるように設定された、より高いレベルのネット名です。DecoderBには、より高いレベルの名前が定義されていないため、元のネット名TDIがこのチャンネルでTDI_2として識別されました(3番目の画像)。これは、プロジェクト オプションダイアログのマルチチャネルタブで定義された命名規則に基づいています(コンポーネント命名規則は、各チャンネル内のコンポーネントとネットの両方を識別するために使用されます)。

PCB_Decoder.SchDoc 回路図:最初の画像 - キャプチャされた回路図;二番目と三番目の画像 - 二つのチャネルのコンパイルされたビュー。

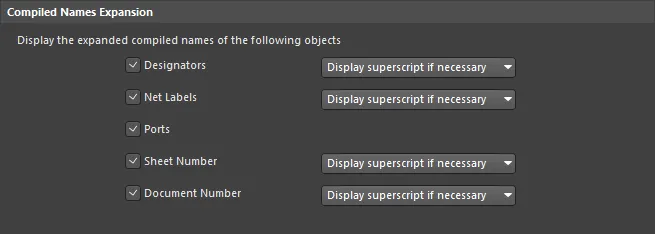

コンパイルされた名前の表示

マルチチャネル設計でネットを追跡・分析する際、繰り返されるネットを識別するために名前を変更する必要があり、それらが独自であることを維持することは混乱を招くことがあります。これを支援するために、コンパイルされたオブジェクト名の表示を制御するための多くのオプションがあります。これには、コンポーネントの指定子、ネットラベル、電源ポート、およびポートが含まれます。シートとドキュメント番号に関するオプションもあり、これらは印刷タイプの出力を生成する準備ができたときに重要になります。

コンパイルされたオブジェクト名の表示は、PreferencesダイアログのSchematic - Compilerページで設定され、以下の画像に示されています。

コンパイルされたオブジェクト名の表示を設定します。コンポーネント指定子には上付き文字が便利です。

通常、設計者とネットラベルが表示されるようにしたいでしょう。問題を診断している場合は、ポートも便利です。シート番号とドキュメント番号も重要で、正しく設定されている必要があります。デザイン注釈セクションで、コンポーネントとシートの番号付けに関する情報へのリンクが見つかります。

ネットラベルオプションは、設定ダイアログの回路図 - コンパイラページでも、パワーポートオブジェクトの展開を決定します。

必要に応じて上付き文字を表示オプションが選択されている場合、現在のドキュメントビューには、非表示ビューからのオブジェクト識別子が上付き文字として含まれます。これらをご自身の好みに合わせて設定してください。

マルチチャネル設計のチャネル2(CIN2)のビューです。元の論理回路図の指定子とネット名が上付き文字として表示されていることに注目してください。

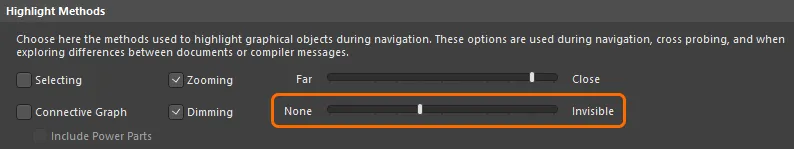

チャネル(物理)タブで一部の回路図要素が薄く表示されるのはなぜですか?デフォルトでは、チャネルタブで編集可能なオブジェクトを標準の表示強度で表示し、編集不可能なオブジェクトを薄く表示します。この薄く表示する設定は、

システム - ナビゲーションページの

設定ダイアログで設定します。オブジェクトを薄く表示する利点は、チャネルタブでネットラベルを移動するなど、サポートされていない編集アクションを試みるのを防ぐのに役立ちます。必要に応じて薄く表示するレベルを設定してください。

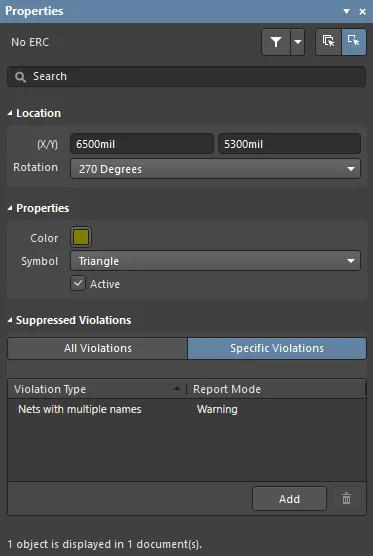

複数のネット名エラーを解決する

回路図エディタのエラーチェックオプションは、複数の名前を持つネットのすべてのインスタンスにフラグを立てるようにデフォルト設定されています。これは、例えばネットがシートシンボルに入るときに名前を意図的に変更した場合などに発生する可能性があります。下の画像では、左右の出力がトップシートでバスにまとめられていますが、シートエントリ内ではLeftとRightと呼ばれている例がいくつか示されています。

バスが使用されたのは、2つの出力チャンネルを単一のシートシンボルで表現できるようにするためであり、Repeatキーワードが使用されています。左右のチャンネルに別々のワイヤーを使用した場合、設計者は左右の出力チャンネルそれぞれに対応するシートシンボル(どちらも同じ子回路図シートを指している)を配置し、各出力をそれぞれの出力シートシンボルに配線する必要がありました。

複数のネット識別子をどのように扱うかソフトウェアに指示する必要があります。これを行うには、以下のいずれかを行う必要があります:

- プロジェクトのオプションダイアログのエラーレポートタブで、複数名のネットエラーチェックを報告しないに設定します。これは推奨されるオプションではありません。なぜなら、設計全体でこのエラー条件のチェックがすべてブロックされるからです。代わりに、以下の操作を行うことができます。

- メッセージパネルのエラー/警告を右クリックし、この違反のための特定のNo ERCマーカーを配置コマンドを選択することで、影響を受けるネットに特定のNo ERCディレクティブを配置します。これを行うと、事前に設定された特定のNo ERCマーカーがカーソルに添付されたNoERCオブジェクト配置モードになり、エラーのあるネット上に配置する準備が整います。配置後、スタイルと色を設定するためにダブルクリックします。

オレンジで囲まれた小さな三角形に注目してください。これは、MB1およびMB2ネット上の重複ネット名エラーを無効にするために配置された特定のNo ERCマーカーです。

マルチボード設計の注釈

設計キャプチャプロセスの重要な部分は、設計に注釈を付けることです。つまり、各コンポーネントと各回路図シートに一意の識別子を付けることです。これはマルチチャネル設計において二段階のプロセスです - 最初に、配置したコンポーネントと描いたシートを番号付けする必要があります。次に、繰り返されるチャネルによってインスタンス化されたコンポーネントとシートも番号付けされる必要があります。

フラットな部品番号システムを好む場合、ボードレベルの注釈を行うことで、体系的な命名スキームを置き換えることができます。ボードレベルの注釈とは、コンポーネントの指定子がPCBになる運命の完全なコンパイル済み設計(物理設計)にのみ適用されるため、この名前が付けられています。複数部品のコンポーネントがパッケージ化され、各コンポーネントに一意の識別子が割り当てられることを保証するため、回路図の注釈がボードレベルの注釈の前提条件であることに注意してください。

これらのボードレベルの注釈は、.Annotation ファイルに保存され、各論理指定子を割り当てられた物理指定子にマッピングします。このファイルはプロジェクトの一部であるため、保存するように求められます。

マルチチャネル設計の注釈プロセスでは、コンポーネントの指定子が非常に長くなることがあるため、PCB内での指定子文字列の配置が難しくなることがあります。PCB上で論理的および物理的な指定子表示の間で選択できます -

詳細を見る。

PCBエディターで、位置に基づいてターゲットコンポーネントの指定子を体系的に割り当てることもできます。

PCB位置注釈を使用してください。

マルチチャネルPCB設計

回路図エディターからPCBエディターに設計を転送すると、プロジェクトオプションでルーム作成が有効になっている場合、各シートのコンポーネントがPCB配置ルームにクラスタリングされます。

マルチチャネル設計でルームを使用する大きな利点は、PCBエディタが一つのルーム(チャネル)から他のルーム(チャネル)への配置と配線の複製をサポートしていることです。ルームは単一のオブジェクトとして移動することもでき、PCB上でのチャネルの配置プロセスを簡素化します。

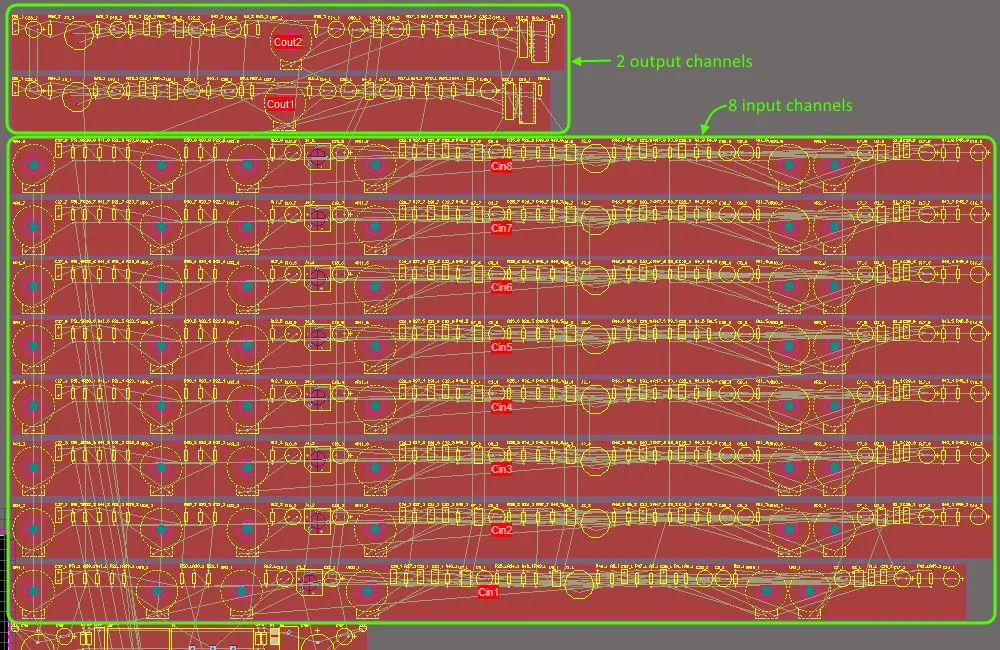

回路図エディタからPCBエディタに設計が転送された後の8つの入力チャネルと2つの出力チャネル、赤いエリアがルームです。

PCBルームの役割

「

ルーム」は、ボード上のエリアを定義するために使用されるPCB設計オブジェクトであり、次の2つの方法で使用できます:

- オブジェクトを含む - ルームは任意の多角形の形状オブジェクトのように配置されますが、実際には配置設計ルールとして作成されます。ルームの定義の一部は、そのルーム内に含まれる必要があるオブジェクト(多くの場合はコンポーネント)を指定することです。そのルームが移動すると、ルーム内のすべてのコンポーネントも移動します。

- 他の設計ルールの範囲を指定する - 自身がルールであると同時に、ルームは他の設計ルールの範囲を指定するためにも使用できます。例えば、ある配線幅設計ルールがネットのクラスのための配線幅を定義している場合、ルームの範囲を持つ優先度の高い設計ルールが、そのルーム内のそのクラスのネットに適用される異なる幅を指定できます。

ルームはマルチチャネル設計で非常にうまく機能します。設計が回路図エディタからPCBエディタに転送される際に、プロジェクトのオプションダイアログのクラス生成タブのオプションに基づいて自動的に作成され、各シートシンボルに対して1つのルームが作成されます。そのチャネル内のコンポーネントをクラスタリングするだけでなく、そのルーム内のコンポーネントの命名にルームを使用することもできます。

便利なルーム操作コマンド

- Design » Rooms - このサブメニューには、ルームの定義と変更に役立つ多くのコマンドがあります。

- Design » Rooms » Copy Room Formats - このコマンドを使用して、あるルーム(チャネル)の配置と配線を他のルーム(チャネル)に複製します。

- Design » Rooms » Move Room - カーソルの下に他の設計オブジェクトがない場所でクリックして保持することで、ルームを移動できます。カーソルは、最も近いコンポーネントパッドまたはルームの頂点(どちらが近いか)にスナップします。設計オブジェクトをクリックせずにクリックして保持できない場合は、このコマンドを使用します。

- Edit » Select » Room Connections - このコマンドを使用して、パッドから始まりルーム内で終わるすべての銅セグメントを選択します。

PCB上での指定子の表示

マルチチャネル設計では、指定子文字列の位置を決めることが難しい場合があります。それらは非常に長くなることがあります。短い名前を結果とする命名オプションを選択することと同様に、別のオプションとしては、元の、論理的なコンポーネント指定を表示することもできます。例えば、C30_CIN1はC30として表示されます。これには、コンポーネントオーバーレイ上で各チャネルを囲むボックスなど、ボードに別の表記を追加する必要があります。

PCBエディタのその他セクションのPropertiesパネル(View » Panels » Properties)で、論理指定子と物理指定子の表示を選択できます。マルチチャネル設計のコンポーネントに論理指定子を表示することを選択した場合、これらはPCBおよび印刷物やガーバーファイルなど、生成されるあらゆるアウトプットに表示されます。ただし、独自の物理指定子は、部品表を生成する際に常に使用されます。

► コンポーネントの注釈付けについてもっと学ぶ

パラメトリック・マルチチャネル階層設計

設計の一部を再利用する際の課題、例えば、現在のプロジェクトのシートシンボルを会社の好みの電源スキーマにリンクする場合、コンポーネントの値は次の設計から次へと常に固定されているわけではありません。

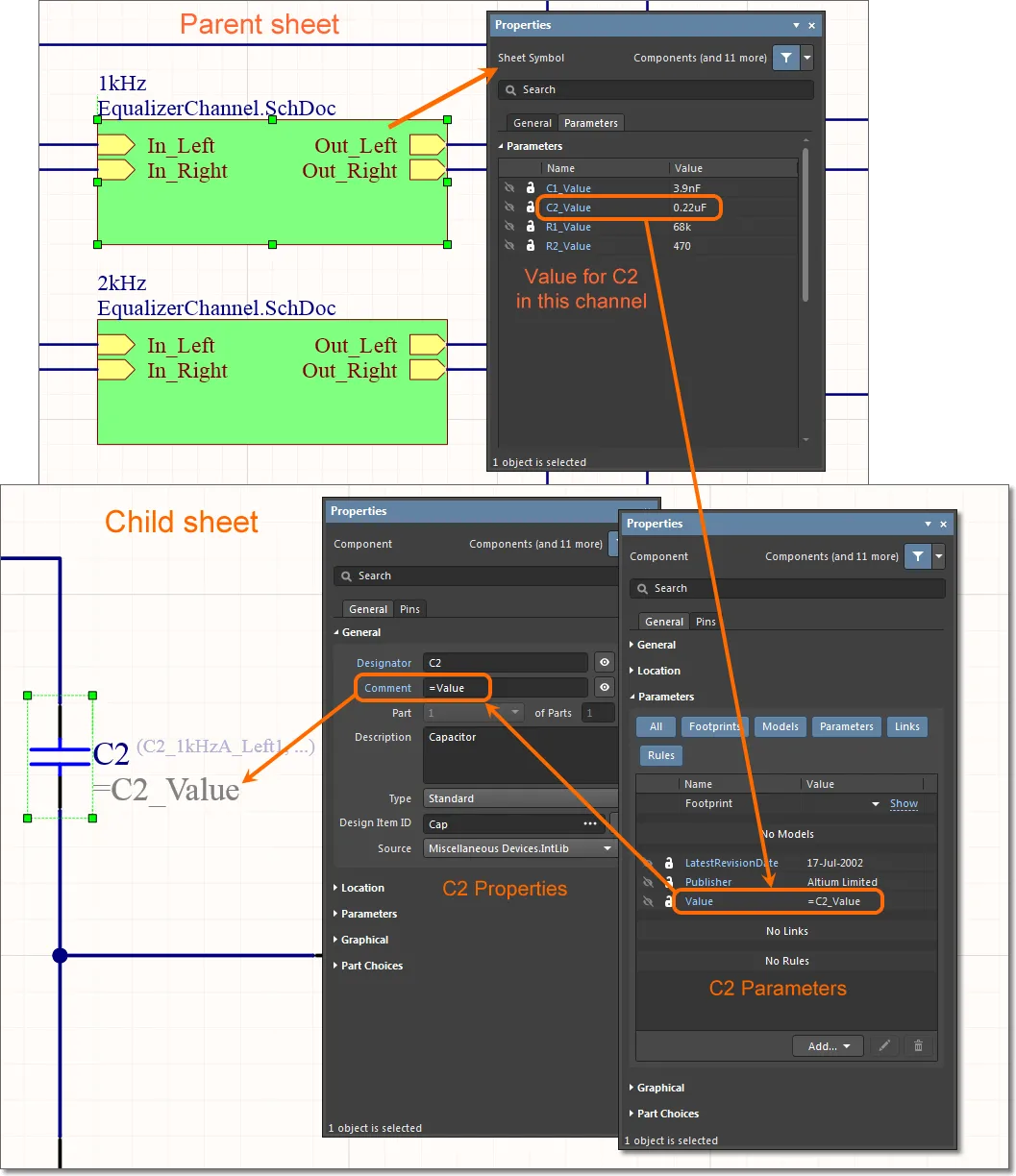

パラメトリック階層設計はこれを解決します - これにより、コンポーネントの値の仕様を回路図シートから、そのシートを参照するシートシンボルに移動することができます。この機能はマルチチャネル設計にも完璧に対応しており、各チャネルで異なるコンポーネントの値を持つことができます。ただし、各チャネルには独自のシートシンボルが必要であることに注意してください。これは、コンポーネントの値が格納される場所だからです。

例えば、グラフィックイコライザーは同じ回路を何度も繰り返すことができますが、各チャネル間の唯一の違いはコンポーネントの値です。したがって、コンデンサは異なるチャネルで0.12µF、0.056µF、0.033µFの値を取るかもしれません。これを実装することは簡単で、各チャネルを参照するシートシンボルにこれらの値を指定するだけで、コンポーネントの値が異なるだけの多くの類似した回路図を持つ必要がなくなります。

パラメトリックコンポーネントは、シートシンボルのパラメータとしてその値を宣言し、そのパラメータを対象コンポーネントで参照することによって定義されます。下の画像は、左側にグラフィックイコライザーのトップシートと、隣に1KHzシートシンボルのパラメータを示しています。この画像には、下位レベルのキャプチャされた回路図と、下のタブで選択されたコンパイルされた1KHzチャンネルも表示されています。

各チャンネルで異なるキャパシタと抵抗値を持つグラフィックイコライザー。実際のコンポーネント値はシートシンボルで定義されているため、下位レベルの回路図を1つだけキャプチャする必要があります。

以下の画像に示されているように、それぞれのシートシンボルパラメータは、下位レベルのシート上の回路図コンポーネントのパラメータの値としても定義されています。各シートシンボルパラメータの値は、関連する回路図コンポーネントに渡され、そこでコンポーネントのコメントフィールドにマッピングされます。値パラメータが回路図コンポーネントの値を示すために直接使用される場合、コンポーネントのコメントパラメータではなく、シートシンボルパラメータをコンポーネントの値パラメータにマッピングする(Value=C2_Value)だけで、それを可視化することが唯一の要件です。

Valueパラメータに=C2_Valueという値が設定されているため、コンパイラは実際のコンポーネントの値を上位レベルのシートシンボルで探す必要があることを知っています。

パラメトリック階層はコンポーネントの値に限定されません。任意のコンポーネントパラメータ、および基本的な接続要素(コンポーネントID、ポートオブジェクト、ドキュメントファイル名を除く)を除く、回路図シート上の他のオブジェクトテキストラベルをパラメトリックに参照できます。階層の上の多くのシートからパラメータを参照する場合、システムは一致するパラメータを見つけるまで階層を検索します。