印刷电子设计

电子产品设计与开发领域一个令人振奋的演进,是能够将电子电路直接印刷到基材上,例如作为产品一部分的塑料模件上。

|

|

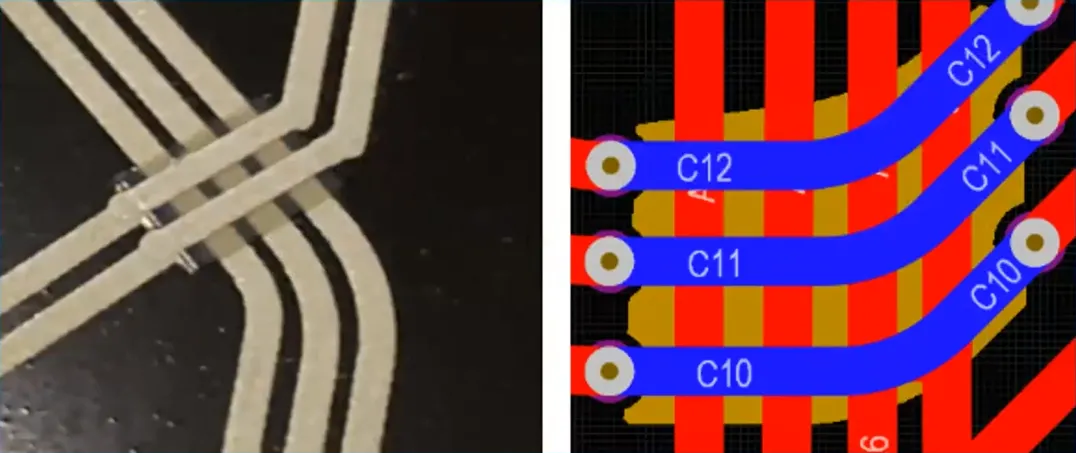

这些幻灯片展示了一个印刷电子布局示例的 2D 和 3D 视图。(图片由 “csi entwicklungstechnik” 提供,来自其采用 TactoTek® In-Mold Structural Electronics 的设计)。

|

这种面向表面的实现技术被称为 Printed Electronics。虽然术语 Printed Electronics 并不能精确描述该技术(因为“印刷”并不是唯一的制造手段),但该术语在行业内被广泛接受,因此本页将使用该术语。

目前正在开发多种实现印刷电子的方法,包括:使用导电油墨的 3D 打印;可同时形成导体以及晶体管等简单电路元件的冲压工艺;以及能够以超高精度在极小尺度上构建导电路径的激光沉积工艺。

印刷电子将成为一项关键技术,使电子技术能够融入新的市场。印刷电子让电路与产品之间实现更紧密的结合。从可直接贴附在人体上的柔性传感器,到多传感器、指尖形状的模件(使机器人手在向软塑料杯中倒入液体时仍能稳稳握持),印刷电子将推动众多细分市场中创新解决方案的诞生。

技术原理

从技术所实现的 what 来看,核心规则并未改变——电子元件仍通过导电通路相互连接,形成执行有用功能的电子电路。不同之处在于构建电路的方式。

传统 PCB 所采用的层叠式制造技术属于 reductive process。每一层导电层最初都是一整片连续的导电材料(如铜箔),随后通过蚀刻去除多余部分,仅保留形成所需导电通路的铜。它也是一个多阶段流程:各导电层与绝缘层交替叠合,并配合钻孔与后续电镀等工艺。

印刷电子属于 additive process:信号通路直接印刷在基材上。如果后续的信号通路需要跨越已有通路,则在所需位置直接印刷一小块绝缘材料。它像一座微型桥梁,使新的信号通路能够跨过既有通路而不与其电连接。举例来说,如果设计采用 DuPont InMold 技术,电路会先印刷在平整的塑料基材上,然后再进行热成型与注塑,最终形成产品的目标外形。

采用印刷电子后,不再需要传统的刚性玻纤 PCB 基板。电路将直接作为产品的一部分形成,导体最终会沿着产品表面的形状与轮廓走线。由于材料用量更少、废料更少,在许多场景下,印刷电子最终将比传统 PCB 更具成本效益。

NOTE - 目前,Altium Designer 的印刷电子设计功能仅支持平面基材表面。若要进行完整的 3D 电路设计,Altium Designer 现已提供专用的 3D-MID 设计工具。

请参阅 True 3D-MID Design 功能页面以概览相关功能。

请参阅 3D-MID Design 文档页面以了解更多信息。

在 Altium Designer 中设计印刷电子

除了承载印刷的基材外,印刷电子产品中并不存在物理层——导电通路直接印刷在基材上。当设计需要通路相互跨越时,会在该位置印刷一小块介电材料,并在跨越区域之外适当扩展,以达到不同信号之间所需的隔离水平。

用于驱动印刷流程所需的输出文件,使用标准输出格式生成,例如 Gerber。

输出将包含以下文件:

-

每一次导电印刷走线(pass)——本质上类似于传统 PCB 中的铜走线层

-

每一次介电印刷走线(pass)——由于介电“补丁”需要被印刷,其形状也必须在输出文件(如 Gerber 文件)中定义。

定义层叠结构

那么,在 PCB 编辑器中如何定义这些多次印刷走线(pass)呢?在印刷电子中,每一次印刷走线都需要一个输出文件,因此与其将其视为由介电层分隔的一系列铜层,不如将其视为一组印刷走线:每一次走线要么是导电油墨层,要么是非导电油墨层。

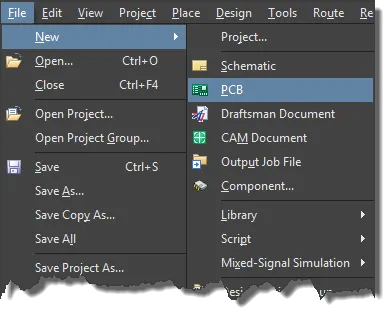

要创建印刷电子设计,首先通过主菜单使用 File » New » PCB 新建一个 PCB。

将新板配置为印刷电子设计,需要在 Layer Stack Manager 中完成。通过主菜单选择 Design » Layer Stack Manager 以访问 Layer Stack Manager。使用  下拉菜单并选择 Printed Electronics ,或通过主菜单选择 Tools » Features » Printed Electronics。

下拉菜单并选择 Printed Electronics ,或通过主菜单选择 Tools » Features » Printed Electronics。

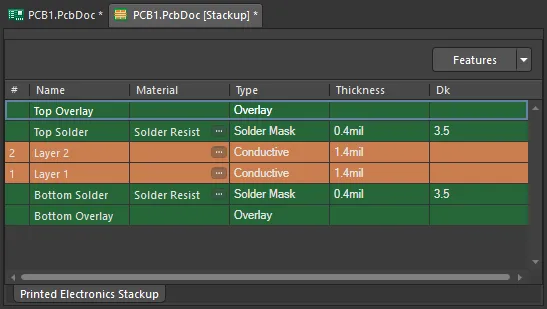

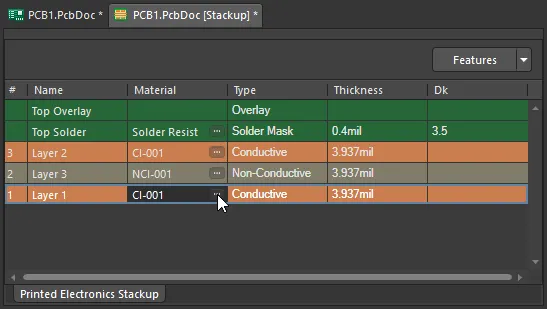

新建 PCB 默认包含两层铜层,中间由一层介电层分隔。

新建 PCB 默认包含两层铜层,中间由一层介电层分隔。

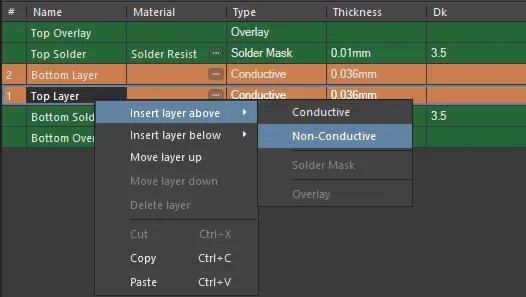

当启用 Printed Electronics 功能后,两层铜层之间的介电层会消失。为什么?因为印刷电子要求每一层都生成一个输出文件,而介电层并不用于生成输出文件,因此不会使用传统意义上的介电层。

当启用 Printed Electronics 功能后,介电层会被移除。

当启用 Printed Electronics 功能后,介电层会被移除。

取而代之的是添加非导电层。在这些层上,可以在导电层的信号路径需要相互跨越的位置,手动或自动定义称为补丁(patch)的介电形状。

Non-Conductive可在 Conductive 层之间插入层,并在其上定义介电补丁。

在某一层上右键,可在其上方或下方插入层、将层上移或下移,或删除该层。印刷电子不使用 Bottom Solder 或 Bottom Overlay;这些已被移除。

添加完各层后,为每一层设置材料属性。

使用省略号按钮为每个印刷层选择要使用的材料。

使用省略号按钮为每个印刷层选择要使用的材料。

材料选择

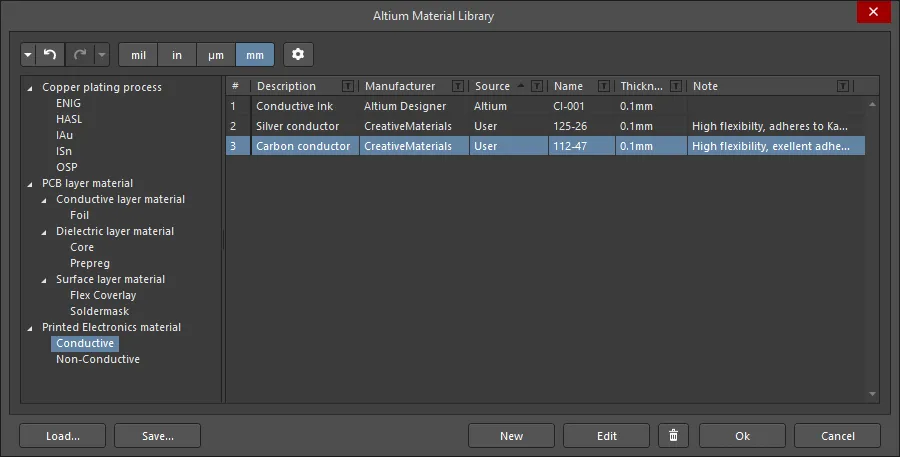

传统 PCB 设计与印刷电子设计所用材料,都在 Layer Stack Manager 的 Material Library 中选择。

当 Layer Stack Manager 打开时,使用 Tools » Material Library 命令打开 Altium Material Library 对话框。

-

Altium Material Library 对话框包含导电层与非导电层的材料。

-

可在库中定义新材料,点击对话框底部的 New 按钮。如果创建了用户自定义材料,可将其保存到并从用户自定义材料库中加载。

-

要为特定层选择材料,请在 Layer Stack Manager 中该层对应的 Material 单元格里点击省略号控件(

)。将打开 Select Material 对话框,并仅显示适用于该层类型的材料。选择所需材料并点击 OK。

)。将打开 Select Material 对话框,并仅显示适用于该层类型的材料。选择所需材料并点击 OK。

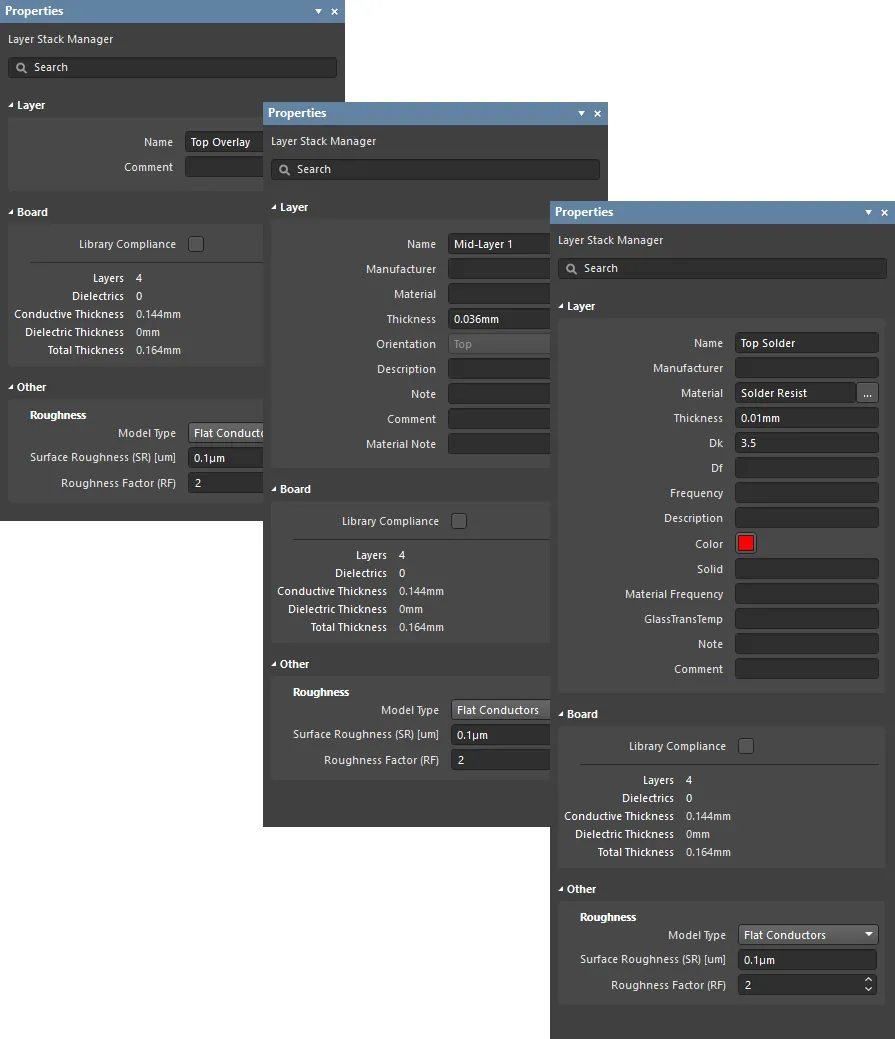

属性面板

当 Layer Stack 文档的 Printed Electronics Stackup 选项卡处于活动状态时, Properties 面板允许你编辑并配置印刷设计的 Layer Stack 层属性。

-

Layer

-

Name – 层名称。

-

Manufacturer – 层制造商。

-

Material – 层材料。可在 Altium Material Library dialog(Tools » Material Library)的 Constructions 字段中预先定义,或在 Layer Stack 中由用户自定义。点击

打开 Select Material dialog,为层叠结构中当前选中的层选择所需材料。

打开 Select Material dialog,为层叠结构中当前选中的层选择所需材料。

-

Thickness – 信号层厚度。

-

Dk – 介电常数(在电磁学中也称为 εr)。它表示绝缘材料的相对介电率,即材料在电场中储存电能的能力。用于绝缘时,介电常数较低的材料更好;在射频应用中,较高的介电常数可能更理想。此外,相对介电常数越低,材料性能越接近空气。该属性对于满足某些传输线的阻抗匹配要求至关重要。

-

Df – 损耗因子(Dissipation Factor)。它通过显示在某种振荡模式(如机械、电气或机电振荡)下的能量损失速率来表征绝缘材料的效率。换言之,该属性描述了传输能量中有多少被材料吸收。损耗正切越大,材料吸收的能量越多。该属性会直接影响高速信号的衰减。

-

Frequency – 材料测试频率,以及 Dk / Df 的数值所对应的频率。频率也可来自材料参考资料。

-

Description – 输入有意义的描述。

-

Color – 所需的阻焊颜色。点击打开下拉菜单以设置/更改颜色。

-

Solid – 不适用

-

Material Frequency – 不适用

-

GlassTransTemp – 玻璃化转变温度(Glass Transition Temperature,也称为 TG),指树脂从玻璃态转变为无定形态并改变其机械行为(例如膨胀率)的温度。

-

Note – 输入该层的任何相关备注。

-

Comment– 输入该层所需的任何注释。

-

Board

-

Library Compliance – 启用后,对于从材料库中选择的每一层,会将当前层属性与库中该材料定义的数值进行比对检查。

-

Layers – 导电层的数量。

-

Dielectrics – 介质层的数量。

-

Conductive Thickness – 所有信号层与平面层(所有铜层或导电层)厚度之和。

-

Dielectric Thickness – 介质层的厚度。

-

Total Thickness – 成品板的总厚度。

-

Other

Roughness – 显示导电层的粗糙度。

-

Model Type – 用于计算表面粗糙度影响的首选模型(有关各种模型的更多信息,请参阅下方文章)。适用于叠层中的所有铜层。

-

Surface Roughness – 表面粗糙度的数值(可从制造商处获得)。输入 0 到 10µm 之间的数值,默认值为 0.1µm

-

Roughness Factor – 用于表征由于粗糙度效应导致导体损耗的预期最大增幅。输入 1 到 100 之间的数值,默认值为 2。

布线网络

-

印刷电子设计中的网络布线方式与传统 PCB 相同,使用 Interactive Routing 命令。

-

导电层之间的切换可通过数字小键盘上的 + 和 - 键,或使用 Ctrl+Shift+Wheelroll 快捷键来完成。

-

在布线过程中切换层时会添加一个过孔,过孔属性由适用的 Routing Via Style 设计规则决定。

需要过孔吗?

软件需要放置过孔,以在布线过程中保持网络连通性,并在通过推挤或拖动修改布线时管理连通性。层与层之间的连通并不需要过孔,软件假定不同层上重叠的走线是相互连接的。

增加走线厚度

如有需要,可以叠加走线厚度,例如实现印刷天线等结构。方法是在不同导电层上将多条走线相互叠放。

添加介质形状

网络布线完成后,下一步是创建用于隔离不同网络交叉处所需的介质补丁。介质形状定义在非导电层上。它们可以手动定义,也可以使用 Dielectric Shapes Generator 自动创建。

手动形状可由圆弧、线段、填充或实心区域创建。实心区域对象提供最大的灵活性,因为其边缘可调整以创建几乎任何形状。

介质形状生成器

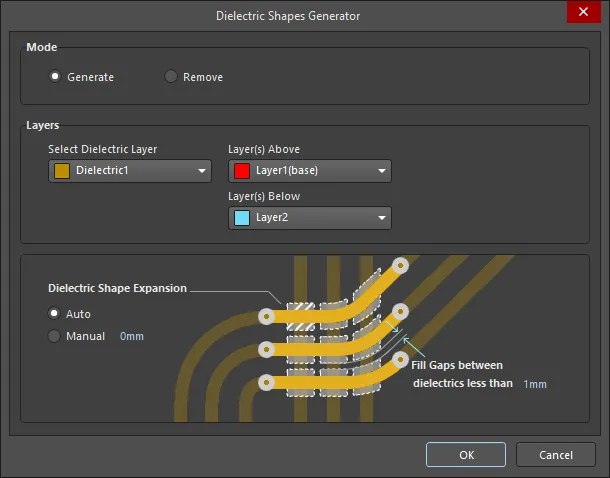

软件还包含一个自动 Dielectric Shapes Generator。其思路是先在导电层上按需求完成布线,并通过放置过孔在层间切换。

布线完成后,运行 Tools » Printed Electronics » Generate Dielectric Patterns 命令以打开 Dielectric Shapes Generator 对话框。运行介质形状生成器时,它会删除目标层上的所有形状,然后重新创建它们。如果已手动定义形状,请在运行 Dielectric Shapes Generator 之前将其锁定。

Options and Controls of the Dielectric Shapes Generator Dialog

-

Mode - 选择所需模式:

-

Generate - 选择为 Layers 区域中指定的所有已启用层生成新的介质补丁。

-

Remove - 选择在添加自身形状之前,先移除生成器在 Layers 区域所指定层上检测到的任何现有形状。

-

Layers - 生成器将识别所有交叉,并根据对话框此区域中的设置添加介质补丁。

-

Select Dielectric Layer - 使用下拉列表选择介质层。如果选择 All ,生成器会在任意一对导电层上查找交叉,并将补丁放置在这两层之间的某个介质层上。如果未选择介质层,则会为所有层之间的所有交叉在合适的介质层上创建介质形状。使用 Layer(s) Above 和 Layer(s) Below 来 选择你希望生成器在搜索交叉时检查的两层导电层。 如果它在 Layer(s) Above 上发现一个对象与 Layer(s) Below 上的对象交叉, 则会生成一个用于放置在它们之间的补丁,并将其放置在 Select Dielectric Layer 区域中指定的层上。若在 Mode 区域选择了 Remove ,则 Layer(s) Above 和 Layer(s) Below 选项不可用。

-

Dielectric Shape Expansion

-

Auto - 在此模式下,介质形状会自动扩展,以满足适用的 Clearance Constraint 设计规则要求。

-

Manual - 在此模式下,生成器会构建一个与交叉对象形成的形状相匹配的形状,然后按输入的距离向外扩展。例如使用此模式时,如果不同层上的两条走线距离过近而产生间距违规,则不会放置补丁。

-

Fill Gaps between dielectrics less than <xx> - 如果希望填充介质之间小于你指定数值的间隙,请指定一个测量值。 这可用于将相邻的介质补丁合并为更大的补丁。

网络连通性与设计规则检查

当层叠配置为 Printed Electronics 时,由于用于定义违规条件的逻辑不同(例如不同层上的网络交叉会被标记为短路),因此不支持在线 DRC。布线完成并定义隔离补丁后,在 Design Rule Checker 对话框(Tools » Design Rule Check)中单击 Run Design Rule Check 按钮以执行批量 DRC。

关于网络连通性与设计规则检查的说明:

-

当网络需要切换到另一导电层时,请插入过孔。这可确保在拖动或推挤布线时,走线段能被正确处理。

-

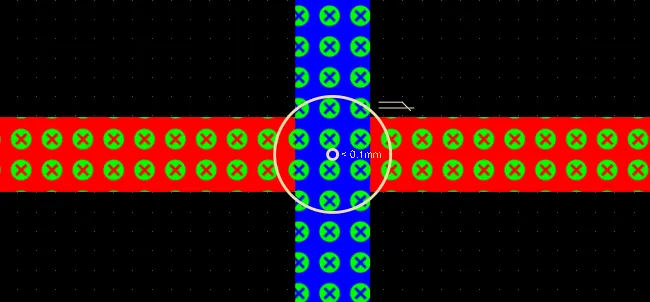

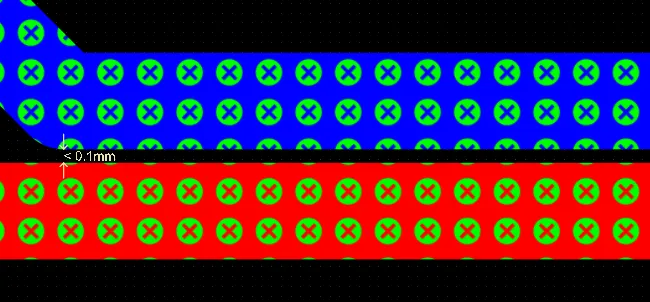

不同层上的接触/交叉走线被视为已连接。如果它们属于同一网络,不会被标记为断网;如果属于不同网络,则会被标记为短路。

-

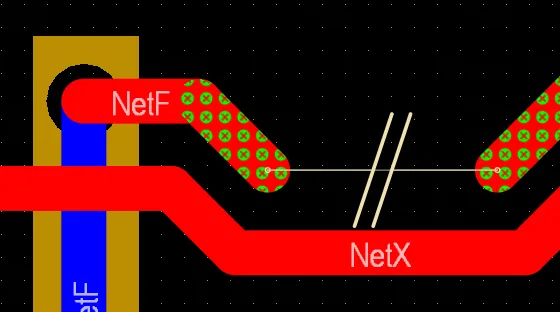

需要使用介质形状来隔离接触/交叉走线,该形状放置在非导电层上。介质形状可手动放置,或由 Dielectric Shape Generator 放置。介质形状必须充分超出交叉走线的边缘,以满足适用的间距约束设计规则。

-

对于印刷电子设计,短路、间距违规以及未布线网络的设计规则检查行为如下所述。

短路设计规则

在 Printed Electronics 设计中,当不同网络在不同层上交叉时,会被标记为短路。通过在非导电层上放置介质补丁来隔离这些交叉。

间距设计规则

网络与网络之间的间距会在所有层上进行测试,而不仅仅是在同一层上。

未布线网络

层间切换不需要过孔,网络分析器会识别该网络未断开。