配置 DRC

设计规则检查的配置是在通过 PCB 文档中的 Tools » Design Rule Check 命令打开的 Design Rule Checker 对话框中完成的。

该 Design Rule Checker 对话框显示默认设置,其中禁用了某些在线 DRC 检查以提升 PCB 编辑器性能。使用相关选项可将某类设计规则纳入在线 DRC 和/或批量 DRC 的检查范围。

该 Design Rule Checker 对话框显示默认设置,其中禁用了某些在线 DRC 检查以提升 PCB 编辑器性能。使用相关选项可将某类设计规则纳入在线 DRC 和/或批量 DRC 的检查范围。

Options and Controls of the Design Rule Checker Dialog

该对话框的功能基本分为两个区域:

-

与批量 DRC 相关的选项配置。

-

配置要检查哪些规则,以及这些规则是否应作为在线和/或批量 DRC 的一部分进行检查。

这些区域对应于左侧窗格中的文件夹式条目,并可通过它们访问。

报告选项

单击 Report Options 文件夹,会在对话框右侧加载运行批量 DRC 时可用的附加选项。

DRC 报告选项

分割平面 DRC 报告选项

-

Report Broken Planes – 启用此选项可让批量规则检查过程查找并报告断裂平面(broken planes)。当平面中某个与网络连通的区域在电气上与平面其余部分断开时,就会出现断裂平面。例如:连接器跨放在分割平面上但未与其连接。引脚周围的避空区连在一起,完全切断平面铜皮,从而将其有效分成两部分。

-

Report Dead Copper larger than – 启用此选项可让批量规则检查过程查找并报告大于指定面积的“死铜”(dead copper)区域。死铜是指与任何网络都不连通、并且也与原始母平面在电气上断开的铜皮区域。例如:一个未连接到平面的连接器,其引脚间距很小,引脚周围的避空区连在一起,将平面铜皮的某些区域与平面其余部分隔离。使用相关字段指定允许的死铜最大面积,超过该值即视为违规(默认值 = 100 sq. mils)。

-

Report Starved Thermals with less than n% available copper – 启用此选项可让批量规则检查过程查找并报告大于指定百分比的“热焊盘连接不足”(starved thermal connections)。热焊盘(Thermals)是通过在连接处设置热隔离“开窗”来与平面相连,以降低向平面铜皮的导热。当连接到平面的铜辐条(spokes)表面积被避空区域削减时,热焊盘可能会出现“连接不足”。此选项还会将热焊盘本体的表面积(不仅是辐条)与侵入热焊盘的任何避空区域进行对比检查。使用相关字段指定必须保留的最小连接铜皮百分比,低于该值即视为违规(默认值 = 50%)。

-

Run Design Rule Check – 单击此按钮可根据为批量检查启用的规则以及为该类检查定义的附加选项执行批量 DRC。

检查完成后,所有违规将显示在 Messages 面板中。

要检查的规则

单击 Rules To Check 文件夹,会在对话框右侧加载所有可检查规则类型的列表。或者,单击某个特定类别(位于该文件夹下方)以仅列出与该类别相关的设计规则类型。

对于每种规则类型,会显示以下信息;

-

Rule – 规则类型。

-

Category – 该规则类型所属的父类别。

-

Online – 该规则类型相对于在线 DRC 的当前状态(如适用)。单击可切换。

-

Batch – 该规则类型相对于批量 DRC 的当前状态。单击可切换。

根据需要为每种规则类型启用在线和/或批量检查。

使用右键菜单可快速访问命令,以便为在线或批量 DRC 快速启用/禁用所有规则类型,或仅启用/禁用已使用的规则类型(已定义并启用使用的规则)。

注意事项

-

生成的《设计规则验证报告》会列出在批量检查过程中按本对话框指定所测试的每条规则。每个被定位到的违规都会列出完整的参考信息细节,例如层、网络名、元件标号和焊盘编号,以及对象的位置。单击违规对象的条目可直接交叉探测到设计空间中的该对象。

- 为了在设计空间中显示规则违规时提供更高的灵活性,两种违规显示类型——违规详情(自定义违规图形)和违规叠加层——分别关联了独立的系统颜色。这样你就可以用不同且清晰区分的颜色来区分这两者。颜色分配在 Layers & Colors 选项卡的 View Configuration panel 中完成:

-

Violation Details – 使用 System Colors 区域中为 Violation Markers 颜色分配的颜色。

-

Violation Overlay – 使用 System Colors 区域中为 DRC Error Markers 颜色分配的颜色。

-

运行 Batch DRC 后,在 Messages 面板中双击某条违规消息,可交叉探测到设计空间中导致该违规的对象。

-

运行 Online 或 Batch DRC 时,任何规则违规都会列在 PCB Rules and Violations panel 的 Violations 区域中。

-

与特定设计对象相关的违规可以直接在 PCB 设计空间中检查。将光标移到违规对象上,右键单击,然后从 Violations 子菜单中选择命令。你可以选择调查该对象参与的某一条具体违规,或使用 Show All Violations 命令查看它参与的所有违规。无论哪种情况,都会弹出 Violation Details dialog,提供详细的违规信息,以及用于高亮并跳转到违规对象的控制项。

在对话框左侧的文件夹树窗格中,所有可检查其规则类型的设计规则类别都列在 Rules To Check 文件夹下。单击该顶层文件夹,会在对话框右侧列出所有可检查的规则类型。或者,单击某个具体类别,仅列出与该类别相关的设计规则类型。使用该对话框为你要检查的每种规则类型启用/禁用 Online(如可用)和/或 Batch 模式检查。

使用右键菜单可访问命令,以便快速为 Online 或 Batch DRC 启用/禁用所有规则类型,或仅启用/禁用“已使用”的规则类型(即在设计中已定义并启用使用的规则类型)。

强烈建议在生成最终光绘文件之前始终执行一次批处理模式的设计规则检查。Online DRC 只会检测新的违规——即在该功能启用之后产生的违规——而 Batch DRC 允许在板卡设计过程中的任何时间手动运行检查。因此,优秀的设计人员既了解 Online DRC 的价值,也知道板卡设计应以 Batch DRC 开始并以 Batch DRC 结束。有关 Batch DRC 的配置选项详情,请参阅

Using Batch DRC。

Using Online DRC

Online Design Rule Checking 在后台实时运行,用于标记和/或自动阻止设计规则违规。这在 interactively routing 你的板卡时尤其有用,可立即高亮间距、线宽以及平行线段违规。要使某条规则受 Online DRC 约束,必须满足以下三个要求:

-

该规则必须已启用。可在 PCB Rules and Constraints Editor dialog 中确保该规则的 Enabled 选项被勾选,或在 PCB Rules and Violations panel 中确保该规则的 On 选项被勾选。

请确保你希望由 Online DRC 监控的设计规则确实已在设计中启用使用。

该规则类型必须在 Design Rule Checker 对话框中启用在线检查。

请确保你希望由 Online DRC 监控的设计规则确实已在设计中启用使用。

该规则类型必须在 Design Rule Checker 对话框中启用在线检查。

请确保该规则类型已为 Online DRC 启用。

必须开启 Online DRC 功能。可在 Preferences 对话框的 PCB Editor - General page 上启用 Online DRC 选项来完成。

请确保该规则类型已为 Online DRC 启用。

必须开启 Online DRC 功能。可在 Preferences 对话框的 PCB Editor - General page 上启用 Online DRC 选项来完成。

请确保 Online DRC 功能已启用。

请确保 Online DRC 功能已启用。

如果发现任何对象违反了某条适用且已启用在线检查的设计规则,它们将根据已定义的 violation display options 在设计空间中被高亮显示。

Using Batch DRC

Online DRC 只会检测新的违规——即在该功能启用之后产生的违规——而 Batch DRC 允许在板卡设计过程中的任何时间手动运行检查。因此,优秀的设计人员既了解 Online DRC 的价值,也知道板卡设计应以 Batch DRC 开始并以 Batch DRC 结束。

要清除现有的错误标记,请从 PCB 编辑器菜单中选择 Tools » Reset Error Markers。

根据需要在 Design Rule Checker 对话框中启用用于批处理检查的规则类型(可回看 Configuring the DRC 小节)。运行 Batch DRC 时还提供多种附加选项,包括生成报告文件的能力。通过单击对话框文件夹树窗格中的 Report Options 文件夹可访问这些选项。其中两个关键选项(在下图中高亮)为:

访问适用于运行 Batch DRC 以及生成 DRC 报告的选项。

访问适用于运行 Batch DRC 以及生成 DRC 报告的选项。

通过单击对话框左下角的 Run Design Rule Check 按钮来启动批处理模式 DRC。检查完成后,所有违规会作为消息列在 Messages 面板中。如果你选择生成报告,则会创建 DRC 报告,并(若已配置)自动打开为主设计窗口中的活动文档。报告会列出在 Design Rule Checker 对话框中指定并被测试的每条规则。设计中不存在的规则不会被测试。

DRC Reports

在 Design Rule Checker dialog 中启用 Create Report File 选项,将在执行 Batch DRC 时生成 DRC 报告。Preferences 对话框的 PCB Editor - Reports page 上提供的选项可用于指定报告格式,以及是否在生成后自动显示报告。

在 Batch DRC 过程中生成 DRC 报告。

支持的格式包括:

-

TXT - 生成文件 Design Rule Check - <PCBDocumentName>.drc。

-

HTML - 生成文件 Design Rule Check - <PCBDocumentName>.html。

-

XML - 生成文件 <PCBDocumentName>.xml 。

报告会列出在批处理检查过程中实际测试的每条规则(如 Design Rule Checker 对话框中所指定)。每个被定位到的违规都会以完整细节列出,包括层、网络名、元件标号、焊盘编号等参考信息,以及对象的位置。

在 HTML 格式报告中,单击违规对象的条目可直接交叉探测到设计空间中的该对象。请注意,该单击动作的缩放级别在 Preferences 对话框的 System – Navigation 页面中配置。

Violation Display Options

按指定设计规则检查设计是一回事,但当一条或多条规则被违反时会怎样?无论是在设计过程中运行 Online DRC,还是手动运行 Batch DRC,都需要有某种视觉指示来显示这些规则违规发生的位置。PCB Editor 提供了强大的违规显示选项,以清晰直观的方式指示违规所在。

Custom Violation Graphics

大多数可纳入 Online 和/或 Batch 设计规则检查的设计规则,都关联了自定义违规图形——当某条规则被违反时会显示在设计空间中。这些图形能让 DRC 视图更清爽。当某条设计规则被违反时,相关的自定义违规图形(如适用)只会绘制在与该违规相关的层上。

在某些情况下,该图形不仅显示违规发生的位置,还会显示原因——展示该规则定义的约束值,并指示违规图元是低于还是高于该值。

示例:展示线宽规则与最小环宽(Minimum Annular Ring)规则违规所使用的自定义图形。

示例:展示线宽规则与最小环宽(Minimum Annular Ring)规则违规所使用的自定义图形。

其他图形(包括用于表示 Net Antennae、Short-Circuit、Un-Routed Net、Room Definition、Layer Pairs 以及 Vias Under SMD 规则违规的图形)将以图形方式呈现,因为这些规则没有可显示的可定义约束值。

更多自定义违规图形示例。从左到右:Net Antennae 违规;Short-Circuit 违规;Un-Routed Net 违规。

更多自定义违规图形示例。从左到右:Net Antennae 违规;Short-Circuit 违规;Un-Routed Net 违规。

Violation Overlay除了自定义违规图形外,还提供了一个可用于设置和使用的违规“叠加层(overlay)”。该叠加层会绘制在设计图元之上。你可以从多种样式中选择要在图元上显示的图案样式。

在显示 DRC 违规时,可使用违规叠加层作为自定义违规图形的替代方案。

在显示 DRC 违规时,可使用违规叠加层作为自定义违规图形的替代方案。

将这两种违规显示类型结合使用,在提供“粗略”和“精细”的违规指示方面会很有帮助。缩小视图时,违规叠加层可以标示出存在违规的位置;随后放大以查看由相关自定义违规图形提供的细节。

配置违规显示首选项

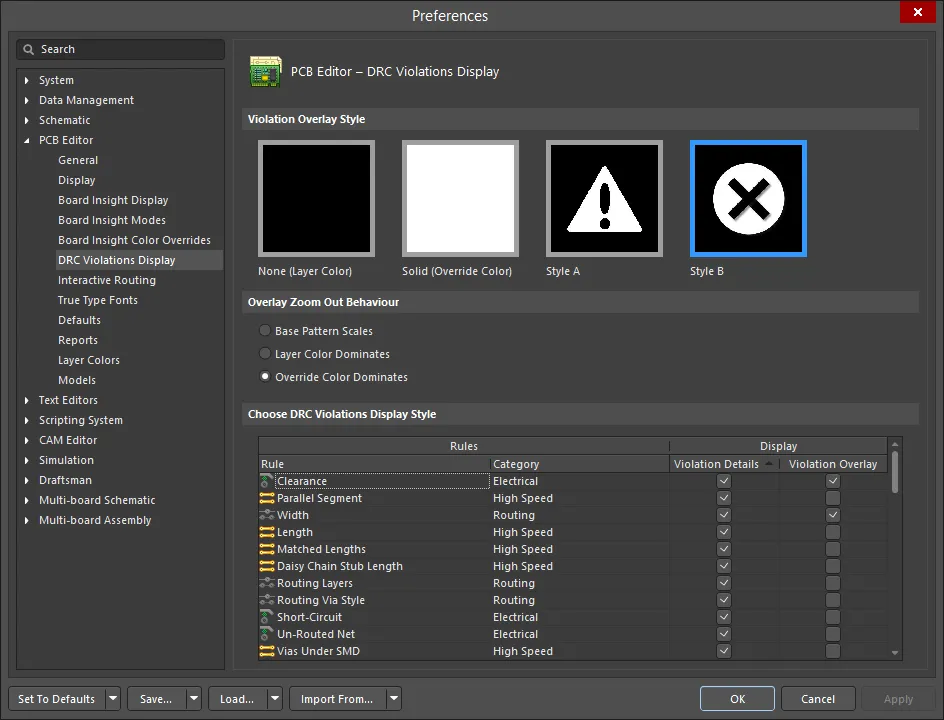

对 DRC 违规如何显示的控制——使用自定义违规图形和/或定义的违规叠加层——在 PCB Editor - DRC Violations Display page 的 Preferences 对话框中指定。

作为软件首选项的一部分,配置 DRC 违规在设计空间中的显示方式——使用自定义图形和/或定义的违规叠加层。

可用选项允许你:

-

使用 Violation Overlay Style 选择所用的违规叠加层样式——错误标记可通过以下四种方式之一显示。单击选择你偏好的样式:

-

None (Layer Color) - 错误标记以层颜色显示,因此 不可见。

-

Solid (Override Color) - 错误标记以 Error Marker 层颜色显示。

-

Style A - 错误标记显示为警告三角形。

-

Style B - 错误标记显示为内部带十字的圆点。

-

使用 Overlay Zoom Out Behavior 确定缩小视图时的违规叠加层显示行为——当你缩小视图时,错误标记将执行以下行为:

-

Base Pattern Scales - 无论缩放级别如何,错误标记都会按比例缩放(标记类型由上方选择的 Violation Overlay Style 决定)。

-

Layer Color Dominates - 随着缩小视图,错误标记会变为以层颜色显示的一块实心色块。

-

Override Color Dominates - 随着缩小视图,错误标记会变为以 Error Marker 层颜色显示的一块实心色块。

-

在 Choose DRC Violations Display Style 区域中按规则逐一选择所用的显示样式。为某个规则类型启用 Violation Details 选项,将使用关联的自定义违规图形来显示该规则的 DRC 违规。启用 Violation Overlay 选项将使用指定的叠加层样式显示违规。 默认情况下,所有规则类型都启用了 Violation Details 显示样式,而 Violation Overlay Style 显示仅对 Clearance、 Width 和 Component Clearance 规则启用。

在网格内右键单击可访问命令菜单,以便快速为所有规则类型启用或禁用某种违规显示类型。还提供命令,可仅针对当前在设计中使用的规则,快速启用违规显示——详细图形或叠加层样式。

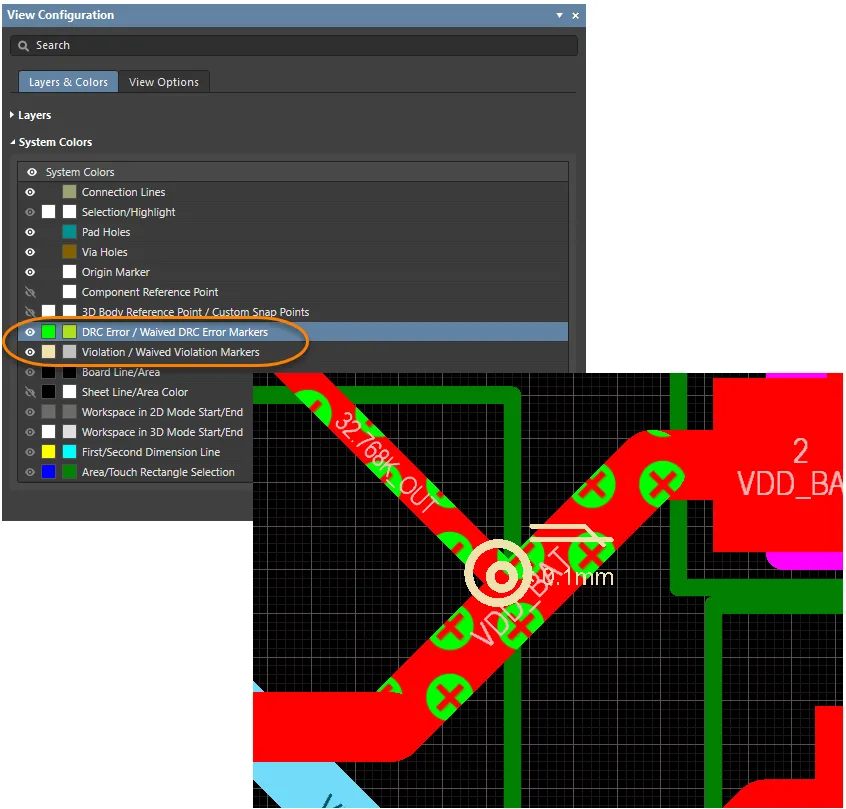

定义违规着色

为了在设计空间中显示规则违规时提供更大的灵活性,两种违规显示类型——违规细节(自定义违规图形)和违规叠加层——分别关联不同的系统颜色。这样你就可以用不同且清晰区分的颜色来区分两者。颜色分配在 View Configuration panel 的 Layers & Colors 选项卡上的 System Colors 部分中完成:

-

Violation Details – 使用 Violation Markers 系统颜色(对使用此显示样式的已豁免违规,使用 Waived Violation Markers 系统颜色)。

-

Violation Overlay – 使用 DRC Error Markers 系统颜色(对使用此显示样式的已豁免违规,使用 Waived DRC Error Markers 系统颜色)。

为两种违规显示类型指定不同的着色,并按需启用/禁用其显示。

为两种违规显示类型指定不同的着色,并按需启用/禁用其显示。

要使用某种违规显示类型,请确保可见性图标 (位于颜色样本左侧)已启用(

),否则将不会显示相应的违规细节或违规叠加层。

AI 翻译

AI 翻译