プリンテッド・エレクトロニック・デザイン

電子製品の設計・開発における刺激的な進化の1つが、電子回路を基材へ直接印刷できるようになったことです。たとえば、製品の一部となるプラスチック成形品などが基材になります。

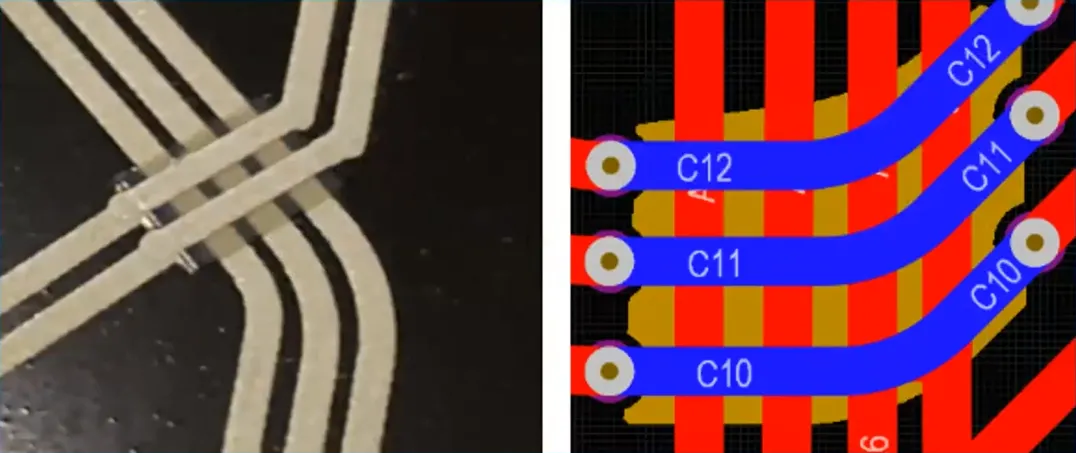

|

|

これらのスライドは、プリンテッド・エレクトロニクスのレイアウト例の2D/3Dビューを示しています。(画像提供:「csi entwicklungstechnik」。TactoTek® In-Mold Structural Electronics を用いた同社設計より)。

|

この表面指向の実装技術は Printed Electronics と呼ばれます。Printed Electronics という用語は、印刷がそれを作る唯一の手法ではないため技術を厳密に表すものではありませんが、業界で広く受け入れられているため、本ページではこの用語を使用します。

プリンテッド・エレクトロニクスを実現するためのアプローチは複数開発されており、導電性インクによる3Dプリント、導体に加えてトランジスタなどの簡単な回路素子も形成できるスタンピング技術、超高精度で極小スケールの導通パスを積層できるレーザー堆積技術などがあります。

プリンテッド・エレクトロニクスは、新しい市場へ電子機能を統合することを可能にする中核技術になっていきます。プリンテッド・エレクトロニクスは、回路と製品を密接に結び付けます。身体に直接貼り付けられるフレキシブルセンサーから、液体を注ぐ際にロボットハンドが柔らかいプラスチックカップを保持できるようにする、指先形状のマルチセンサー成形品に至るまで、プリンテッド・エレクトロニクスは多くの市場セグメントで革新的な新ソリューションの開発を可能にします。

技術

whatが提供するものという観点では、基本は同じです。電子部品は導電パスで相互接続され、有用な機能を果たす電子回路を構成します。異なるのは、回路を作り上げるためのアプローチです。

従来のPCBを作る層指向の製造技術は reductive process です。各導電層は、銅などの導電材料の連続シートとして始まり、そこから不要部分をエッチングで除去して、必要な導電パスを形成する銅だけを残します。また、個々の導電層を絶縁層と交互に挟み込んで積層し、各種の穴あけや後工程のめっき処理を行うため、多段階のプロセスでもあります。

プリンテッド・エレクトロニクスは additive process であり、信号パスは基材へ直接印刷されます。後続の信号パスが既存のパスを横切る必要がある場合、必要な位置に小さな絶縁パッチを直接印刷します。小さなブリッジとして機能し、既存パスに接続することなく、その上を新しい信号パスが跨いで印刷できるようにします。例として、設計で DuPont InMold 技術を使用する場合、まず平坦なプラスチック基材に回路を印刷し、その後、熱成形と射出成形によって最終製品形状へ加工します。

プリンテッド・エレクトロニクスを用いることで、従来の硬質ガラス繊維のプリント基板基材は不要になります。代わりに、回路は製品の一部として直接形成され、導体は最終的に製品表面の形状や輪郭に沿うようになります。使用材料が少なく廃棄も減るため、多くの状況で、プリンテッド・エレクトロニクスは従来PCBよりも最終的にコスト効率の高いアプローチになっていきます。

NOTE - 現時点では、Altium Designer のプリンテッド・エレクトロニクス設計機能でサポートされるのは平坦な基材表面のみです。完全な3D回路設計には、Altium Designer の専用 3D-MID 設計ツールが現在利用可能です。

機能概要については、 True 3D-MID Design 機能ページを参照してください。

詳細については、 3D-MID Design ドキュメントページを参照してください。

Altium Designer でプリンテッド・エレクトロニクスを設計する

設計が印刷される基材を除けば、プリンテッド・エレクトロニクス製品には物理的な層は存在しません。導電パスは基材へ直接印刷されます。設計上、パス同士を交差させる必要がある場合は、その位置に誘電体材料の小さなパッチを印刷し、異なる信号間で必要な絶縁レベルを確保できるよう、交差部より十分に広げて形成します。

印刷プロセスを駆動するために必要な出力は、Gerber などの標準出力フォーマットを用いて生成されます。

出力には、次のファイルが含まれます。

-

各導電印刷パス(基本的には従来PCBの銅配線層と同等)

-

各誘電体印刷パス(誘電体パッチを印刷するため、その形状も Gerber ファイルなどの出力ファイルで指定します。)

レイヤースタックの定義

では、これら複数の印刷パスはPCBエディタでどのように定義するのでしょうか。プリンテッド・エレクトロニクスでは、各印刷パスごとに出力ファイルが必要です。そのため、誘電体層で分離された銅層の連なりとして考えるのではなく、導電性インク層または非導電性インク層のいずれかで構成される「印刷パスのセット」として捉えてください。

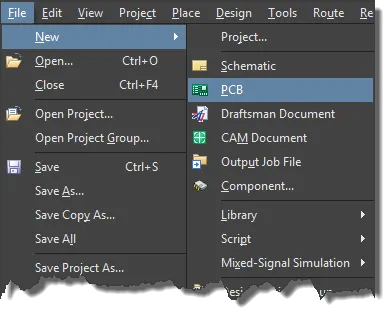

プリンテッド・エレクトロニクス設計を作成するには、まずメインメニューから File » New » PCB を使用して新しいPCBを作成します。

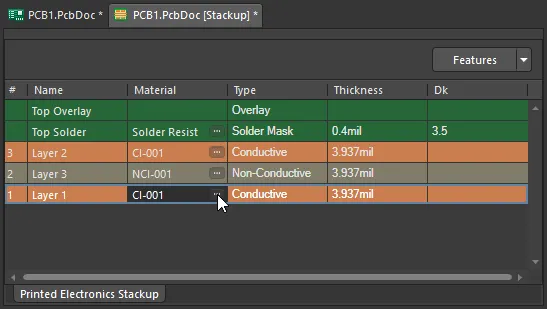

新しいボードをプリンテッド・エレクトロニクス設計として構成するには、Layer Stack Manager で行います。メインメニューから Design » Layer Stack Manager を選択して Layer Stack Manager にアクセスします。  ドロップダウンを使用して Printed Electronics を選択するか、メインメニューから Tools » Features » Printed Electronics を選択します。

ドロップダウンを使用して Printed Electronics を選択するか、メインメニューから Tools » Features » Printed Electronics を選択します。

新規PCBは、誘電体層で分離された2つの銅層がデフォルトです。

新規PCBは、誘電体層で分離された2つの銅層がデフォルトです。

Printed Electronics 機能を有効にすると、2つの銅層の間にある誘電体層が消えます。なぜでしょうか。プリンテッド・エレクトロニクスでは各層ごとに出力ファイルが必要であり、誘電体層は出力ファイル生成に使われないため、使用しないからです。

When the Printed Electronics feature is enabled, the dielectric layer is removed.

代わりに、非導電層が追加されます。誘電体形状(パッチと呼ばれます)は、導電層上で信号パス同士が交差する必要がある箇所に、これらの層上で手動または自動で定義できます。

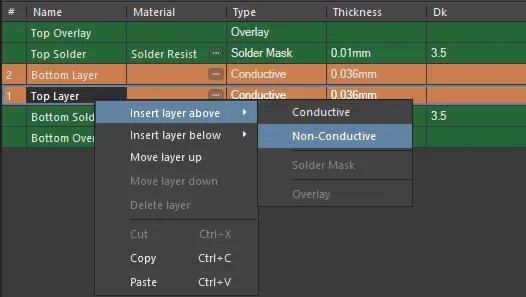

Non-Conductive Conductive layers の間に層を挿入し、その上に誘電体パッチを定義できます。

レイヤーを右クリックして、上または下にレイヤーを挿入、レイヤーを上下に移動、またはレイヤーを削除できます。プリンテッド・エレクトロニクスでは Bottom Solder や Bottom Overlay は使用しないため、これらは削除されています。

レイヤーを追加したら、各レイヤーの材料プロパティを設定します。

各印刷レイヤーに使用する材料は、省略記号(…)ボタンを使って選択します。

各印刷レイヤーに使用する材料は、省略記号(…)ボタンを使って選択します。

材料の選択

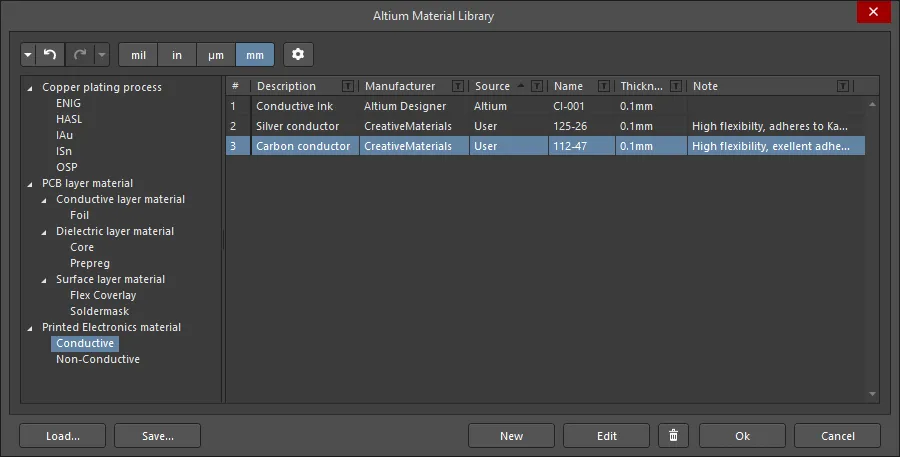

従来のPCB設計とプリンテッド・エレクトロニクス設計の両方で使用する材料は、Layer Stack Manager の Material Library で選択します。

Layer Stack Manager を開いた状態で、Tools » Material Library コマンドを使用して Altium Material Library ダイアログを開きます。

-

Altium Material Library ダイアログには、導電層と非導電層の両方の材料が含まれています。

-

新しい材料はライブラリで定義できます。ダイアログ下部の New ボタンをクリックしてください。ユーザー定義材料を作成した場合、それらはユーザー定義材料ライブラリへ保存したり、そこから読み込んだりできます。

-

特定のレイヤーに材料を選択するには、Layer Stack Manager で該当レイヤーの Material セルにある省略記号コントロール(

)をクリックします。Select Material ダイアログが開き、そのレイヤー Type に適した材料のみが表示されます。必要な材料を選択し、OK をクリックします。

)をクリックします。Select Material ダイアログが開き、そのレイヤー Type に適した材料のみが表示されます。必要な材料を選択し、OK をクリックします。

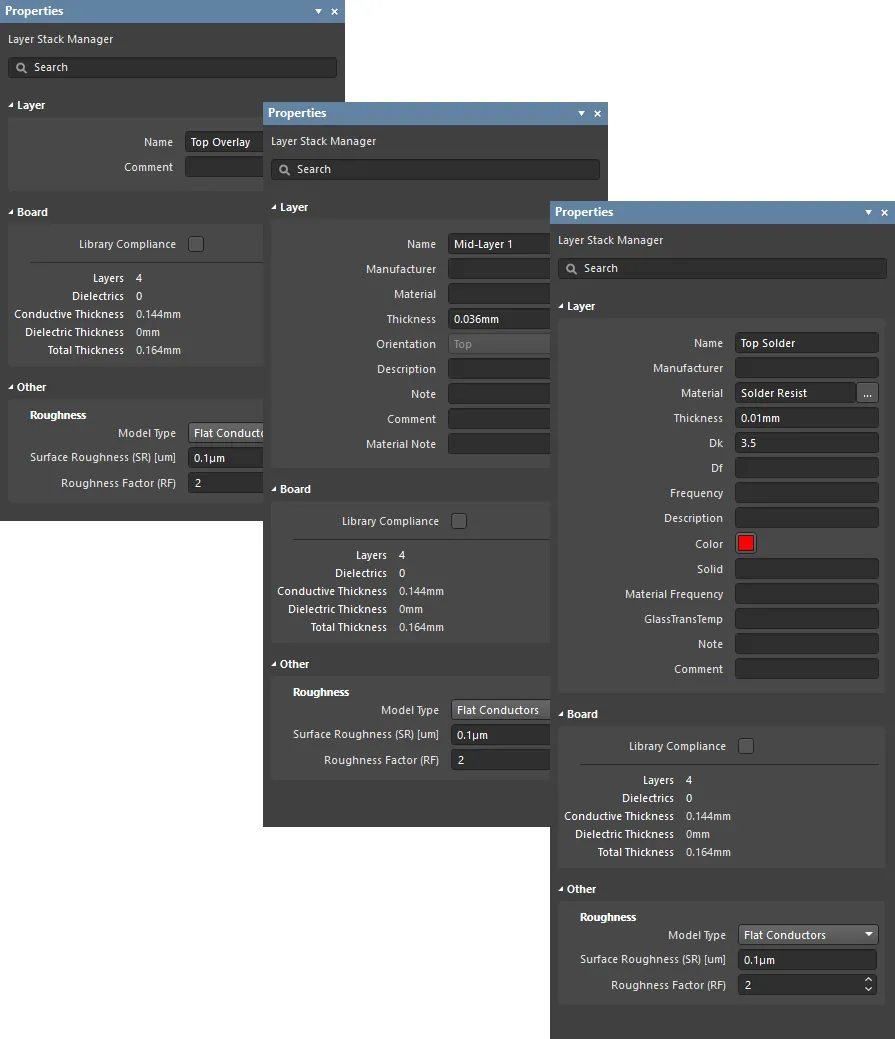

プロパティパネル

Layer Stack ドキュメントの Printed Electronics Stackup タブがアクティブなとき、Properties パネルで、プリンテッド設計向けの Layer Stack のレイヤープロパティを編集・設定できます。

-

Layer

-

Name – レイヤー名。

-

Manufacturer – レイヤーメーカー。

-

Material – レイヤー材料。これは Altium Material Library dialog(Tools » Material Library)の Constructions フィールドで事前定義するか、Layer Stack でユーザー定義できます。

をクリックして Select Material dialog を開き、レイヤースタックで現在選択されているレイヤーに対して希望の材料を選択します。

をクリックして Select Material dialog を開き、レイヤースタックで現在選択されているレイヤーに対して希望の材料を選択します。

-

Thickness – 信号層の厚み。

-

Dk – 誘電率(電磁気学では εr とも呼ばれます)。これは絶縁材料の比誘電率を示し、電界中に電気エネルギーを蓄える能力を表します。絶縁目的では誘電率が低い材料の方が望ましく、RF用途では誘電率が高い方が望ましい場合があります。また、比誘電率が低いほど材料の特性は空気に近づきます。この特性は、特定の伝送線路のインピーダンス要件に整合させるうえで重要です。

-

Df – 誘電正接(損失係数)です。機械的・電気的・電気機械的振動など、特定の振動モードにおけるエネルギー損失率を示すことで、絶縁材料の効率を表します。言い換えると、伝達されたエネルギーのうちどれだけが材料に吸収されるかを示す材料特性です。損失正接が大きいほど、材料へのエネルギー吸収は大きくなります。この特性は高速時の信号減衰に直接影響します。

-

Frequency – 材料が試験される周波数であり、Dk / Df の値が対応する周波数です。周波数は材料リファレンスからも取得されます。

-

Description – 意味のある説明を入力します。

-

Color – 必要なソルダーマスクの色です。クリックしてドロップダウンを開き、色を設定/変更します。

-

Solid – 該当なし

-

Material Frequency – 該当なし

-

GlassTransTemp – ガラス転移温度(Glass Transition Temperature、TG とも呼ばれます)です。樹脂がガラス状状態から非晶質状態へ変化し、機械的挙動(例:膨張率)が変わる温度を指します。

-

Note – レイヤーに関する注記があれば入力します。

-

Comment– レイヤーに必要なコメントを入力します。

-

Board

-

Library Compliance – 有効にすると、Material Library から選択された各レイヤーについて、現在のレイヤープロパティがライブラリ内のその材料定義の値と照合されます。

-

Layers – 導電層の数。

-

Dielectrics – 誘電体の数。

-

Conductive Thickness – すべての信号層およびプレーン層(すべての銅層/導電層)の厚みの合計です。

-

Dielectric Thickness – 誘電体層の厚み。

-

Total Thickness – 完成基板の総厚。

-

Other

Roughness – 導電層の粗さを表示します。

-

Model Type – 表面粗さの影響を計算するための推奨モデル(各モデルの詳細は下記記事を参照)。スタック内のすべての銅層に適用されます。

-

Surface Roughness – 表面粗さの値(製造業者から入手可能)。0~10µm の値を入力します。デフォルトは 0.1µm です。

-

Roughness Factor – 粗さ効果によって導体損失が増加する最大見込み量を特徴付けます。1~100 の値を入力します。デフォルトは 2 です。

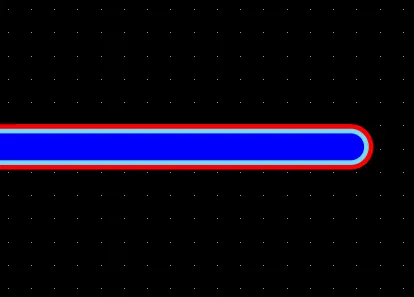

ネットの配線

-

プリンテッド・エレクトロニクス設計のネットは、従来の PCB と同様に Interactive Routing コマンドを使用して配線します。

-

導電層の切り替えは、テンキーの + および - キー、または Ctrl+Shift+Wheelroll ショートカットで行います。

-

配線中にレイヤーを変更するとビアが追加され、ビアのプロパティは適用される Routing Via Style デザインルールによって決まります。

ビアは必要ですか?

ソフトウェアは、配線中にネットの接続性を維持するため、またプッシュ/ドラッグによって配線が変更された際の接続性を管理するためにビアを配置する必要があります。レイヤー間の接続性そのものにはビアは不要で、ソフトウェアは異なるレイヤー上で重なっているトラックは接続されているものとみなします。

配線厚の増加

必要に応じて配線厚を積み増しできます。たとえば、印刷アンテナのような構造を実装する場合です。これは、異なる導電層上で複数の配線を互いに重ねて配置することで実現します。

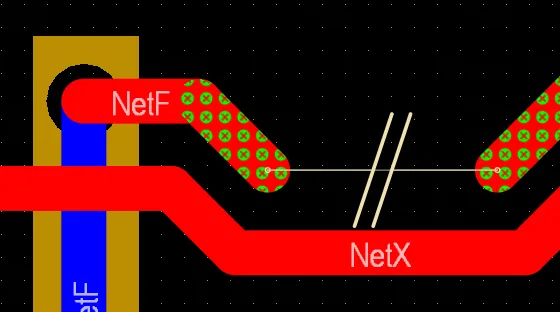

誘電体シェイプの追加

ネットの配線が完了したら、次のステップは、異なるネット同士のクロスオーバーを分離するために必要な誘電体パッチを作成することです。誘電体シェイプは非導電層上に定義します。手動で定義することも、Dielectric Shapes Generator を使用して自動作成することもできます。

手動シェイプは、Arc、Line、Fill、または Solid Region から作成できます。Solid Region オブジェクトは最も柔軟性が高く、エッジを調整してほぼ任意の形状を作成できます。

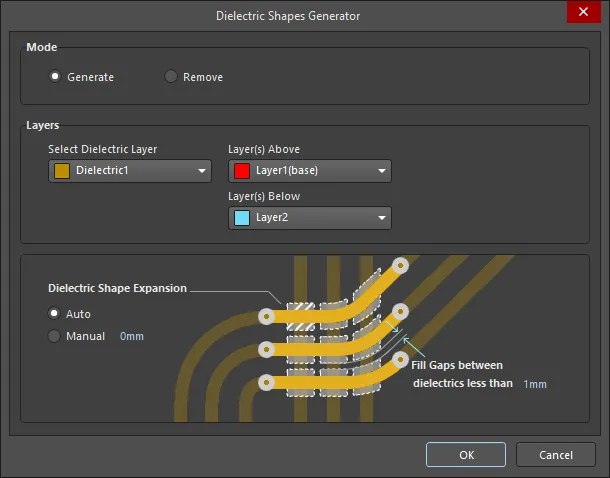

誘電体シェイプ・ジェネレーター

ソフトウェアには自動 Dielectric Shapes Generator も含まれています。ここでの考え方は、まず導電層上で必要な配線を完了し、レイヤーを切り替えるためにビアを配置することです。

配線が完了したら、Tools » Printed Electronics » Generate Dielectric Patterns コマンドを実行して Dielectric Shapes Generator ダイアログを開きます。 誘電体シェイプ・ジェネレーターを実行すると、対象レイヤー上のすべてのシェイプが削除された後、再作成されます。手動でシェイプを定義している場合は、Dielectric Shapes Generator を実行する前にそれらをロックしてください。

Options and Controls of the Dielectric Shapes Generator Dialog

-

Mode - 目的のモードを選択します:

-

Generate - Layers region で指定された有効レイヤーすべてに対して、新しい誘電体パッチを生成するよう選択します。

-

Remove - Layers region で指定されたレイヤー上にジェネレーターが検出した既存シェイプを、自身のシェイプを追加する前に削除するよう選択します。

-

Layers - ジェネレーターはすべてのクロスオーバーを特定し、ダイアログのこの region の設定に従って誘電体パッチを追加します。

-

Select Dielectric Layer - ドロップダウンで誘電体レイヤーを選択します。All を選択すると、ジェネレーターは任意の導電層ペア上のクロスオーバーを探し、それら 2 つの導電層の間にある誘電体レイヤー上にパッチを配置します。誘電体レイヤーが選択されていない場合、すべてのレイヤー間のすべてのクロスオーバーに対して、適切な誘電体レイヤー上に誘電体シェイプが作成されます。 Layer(s) Above と Layer(s) Below を使用して 、クロスオーバー検索時にジェネレーターが対象とする 2 つの導電層を選択します。 Layer(s) Above 上のオブジェクトが Layer(s) Below 上のオブジェクトと交差していることを検出すると、 それらの間に配置するパッチを生成し、Select Dielectric Layer region で指定されたレイヤー上に配置します。 Layer(s) Above および Layer(s) Below オプションは、Mode region で Remove が選択されている場合は使用できません。

-

Dielectric Shape Expansion

-

Auto - このモードでは、適用される Clearance Constraint デザインルールの要件を満たすように、誘電体シェイプが自動的に拡張されます。

-

Manual - このモードでは、ジェネレーターはクロスしたオブジェクトが形成する形状に一致するシェイプを作成し、その後、入力した距離だけ外側へ拡張します。たとえばこのモードでは、 異なるレイヤー上の 2 本のトラックがクリアランス違反となるほど近い場合、パッチは配置されません。

-

Fill Gaps between dielectrics less than <xx> - 指定した値未満の誘電体間ギャップを埋めたい場合は、測定値を指定します。 これは隣接する誘電体パッチをより大きなパッチへ結合するために使用できます。

ネット接続性とデザインルールチェック

Printed Electronics としてレイヤースタックが構成されている場合、違反条件の定義に用いるロジックが異なる(例:異なるレイヤー上でネットが交差すると短絡としてフラグされる)ため、Online DRC はサポートされません。配線が完了し、分離パッチが定義されたら、Design Rule Checker ダイアログ(Tools » Design Rule Check)の Run Design Rule Check ボタンをクリックしてバッチ DRC を実行します。

ネット接続性とデザインルールチェックに関する注意:

-

ネットを別の導電層へ切り替える必要がある場合は、ビアを挿入します。これにより、配線をドラッグ/プッシュした際にトラックセグメントが正しく処理されます。

-

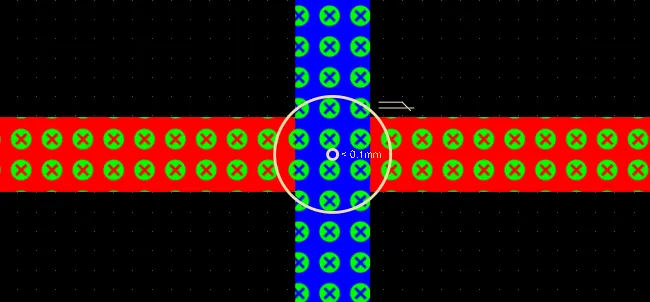

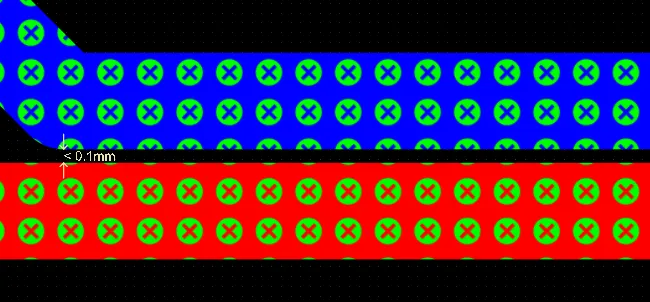

異なるレイヤー上のトラックが接触/交差している場合、それらは接続されているとみなされます。同一ネットであれば断線ネットとしてはフラグされず、異なるネットであれば短絡としてフラグされます。

-

接触/交差しているトラックを分離するには誘電体シェイプが必要で、このシェイプは非導電層上に配置します。誘電体シェイプは手動で配置するか、Dielectric Shape Generator によって配置できます。誘電体シェイプは、適用されるクリアランス制約デザインルールを満たすのに十分なだけ、交差するトラックのエッジより外側へ延長されている必要があります。

-

プリンテッド・エレクトロニクス設計では、短絡、クリアランス違反、未配線ネットに対するデザインルールチェックは以下のとおり動作します。

短絡デザインルール

Printed Electronics 設計では、異なるネットが異なるレイヤー上でクロスオーバーすると短絡としてフラグされます。これらのクロスオーバーは、非導電層上に誘電体パッチを配置することで分離されます。

クリアランスデザインルール

ネット間クリアランスは、同一レイヤーだけでなくすべてのレイヤーでテストされます。

未配線ネット

レイヤー遷移にビアは不要で、ネットアナライザーはネットが断線していないことを認識します。