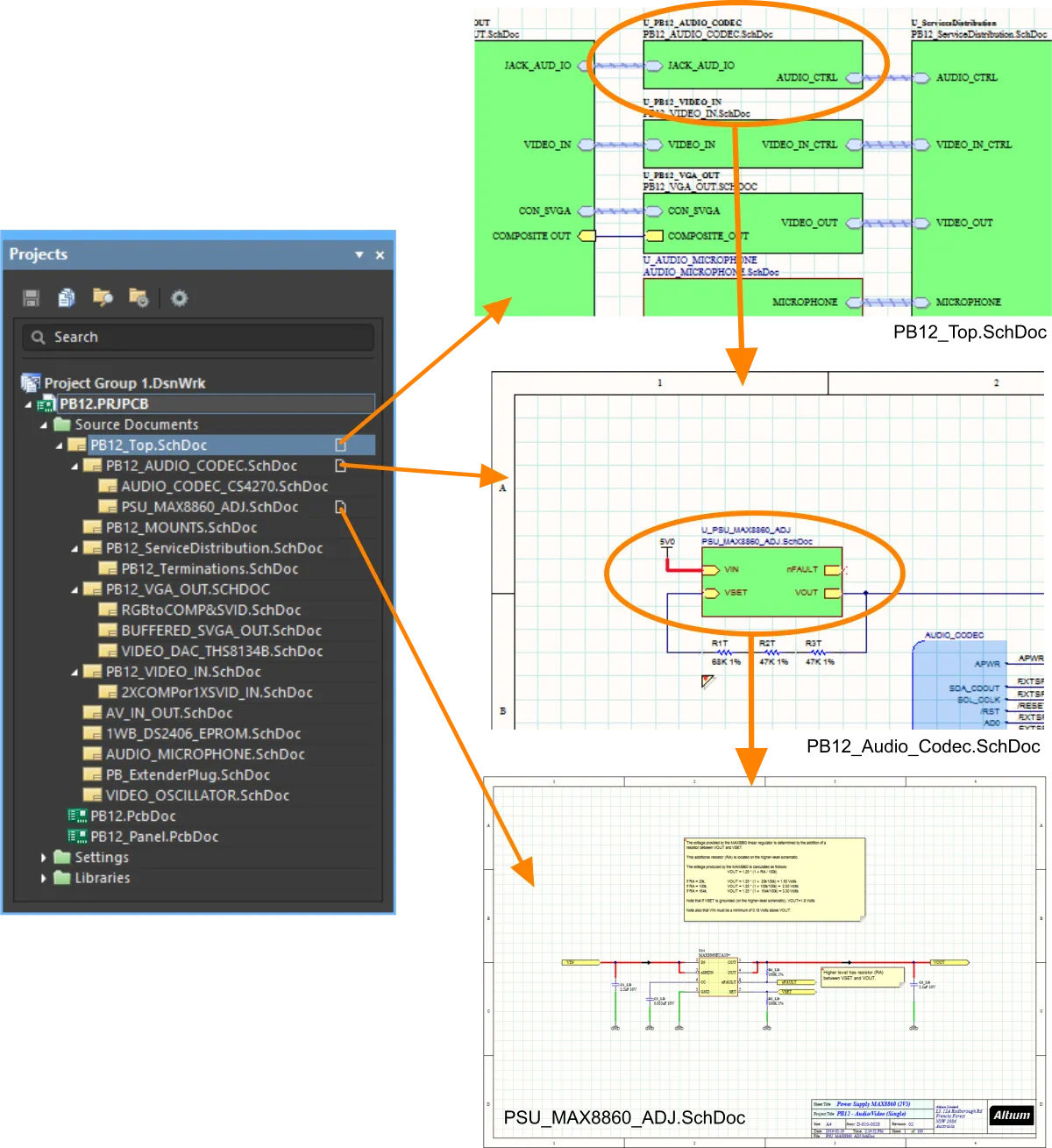

회로도가 처음에는 종이에 작성되었을 때, 종이 한 장에 모두 그려졌으며, 이 종이는 대형 제도 테이블을 가득 채울 만큼 컸고, 전용 대형 복사기로 복제되었습니다. 하지만 지금은 시대가 변해, 회로도는 데스크톱 PC에서 작성되고, 서버에 저장되며, 소형 레이저 프린터로 출력됩니다.

이러한 변화로 인해, 단순한 설계라도 여러 개의 회로도 시트에 나누어 표현하면 더 쉽게 표시하고 이해할 수 있게 되었습니다. 설계가 특별히 복잡하지 않더라도, 여러 시트로 구성하면 얻을 수 있는 이점이 있습니다.

예를 들어, 설계에 다양한 모듈형 요소가 포함될 수 있습니다. 이러한 모듈을 개별 문서로 유지하면 여러 명의 설계자가 동시에 프로젝트를 진행할 수 있습니다. 설계를 논리적인 모듈로 분할하면 설계의 가독성이 크게 향상되어, 제품의 수명 주기 동안 회로도를 읽고 해석해야 하는 사람들에게 중요한 고려사항이 됩니다. 또 다른 장점은, 여러 시트에 걸쳐 설계가 구성되어 각 시트에 부품 수가 적을 경우, 레이저 프린터와 같은 소형 프린터로도 출력이 가능하다는 점입니다.

설계를 여러 시트에 나누어 작성하려면 두 가지 결정을 내려야 합니다:

이 선택은 각 프로젝트의 크기와 유형, 그리고 개인적인 선호도에 따라 달라질 수 있습니다.

이 글에서는 시트 간의 구조적 관계, 그 작동 방식, 그리고 다중 시트 설계를 만들기 위한 도구와 기법에 대해 중점적으로 다룹니다. 연결성 생성 방법에 대해 더 알고 싶다면 Creating Connectivity 문서를 참고하세요.

플랫(Flat) 또는 계층적(Hierarchical) 설계

앞서 언급했듯이, 설계자는 회로도 시트를 어떻게 구성할지, 그리고 시트 간의 연결성을 어떻게 설정할지 결정해야 합니다. 이 두 결정은 별개가 아니며, 구조를 선택할 때 시트 간 연결 방식을 함께 선택해야 합니다.

다중 시트 설계 구조에는 flat 또는 hierarchical 두 가지 접근 방식이 있습니다.

두 방식 모두 유효하며, 각각의 장단점이 있습니다. 플랫 설계는 더 빠르게 만들 수 있지만, 다른 사람이 신호를 추적하거나 기능을 해석하기에는(특히 인쇄본에서) 더 어렵습니다. 계층적 설계는 연결성을 만들기 위한 단계가 더 많아 시간이 더 걸리지만, 그만큼 다른 사람이 설계의 기능을 더 쉽게 해석하고 시트 간 신호를 추적할 수 있습니다. 계층적 설계는 설계 재사용에도 중요하며, 다중 채널 설계의 필수 요소이기도 합니다.

자식 시트를 부모 시트에 연결하는 기술은 플랫 설계와 계층적 설계 모두 동일합니다. 즉, 연결성이 어떻게 생성되는지에 따라 플랫 설계인지 계층적 설계인지가 결정됩니다.

플랫 설계

플랫 설계는 마치 큰 회로도 시트를 여러 개의 작은 시트로 잘라낸 것과 같다고 생각할 수 있습니다. 플랫 설계에서는 모든 시트가 동일한 레벨에 존재합니다. 플랫 설계의 연결성은 어떤 시트에서든 다른 시트로 직접 생성되며, 이러한 연결 방식을 수평 연결성(horizontal connectivity)이라고 합니다.

플랫 설계에서 상위 시트(Top Sheet)의 사용은 선택 사항입니다. 상위 시트를 포함할 경우, 설계 내 각 시트에 대한 시트 심볼이 포함되지만, 배선은 포함할 수 없습니다. 플랫 설계에서는 시트의 개수에 제한이 없습니다.

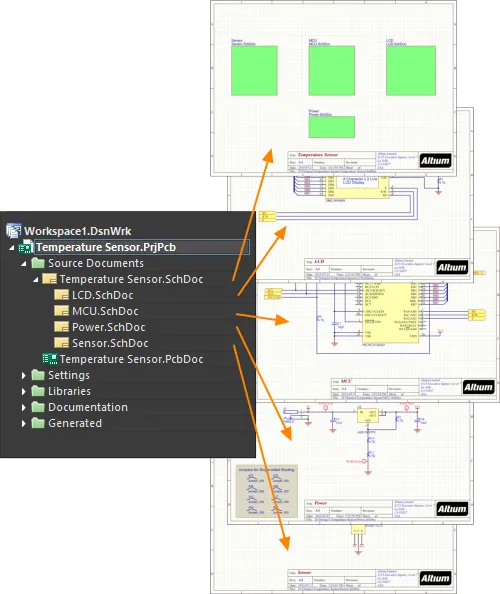

첫 번째 이미지는 플랫 설계에 상위 시트가 없는 경우이고, 두 번째 이미지는 동일한 설계에 상위 시트가 있는 경우입니다. 상위 시트에는 배선이 없으며, 단순히 설계에 포함된 시트만 보여줍니다.

위 두 이미지는 모두 플랫 설계를 보여주며, 왼쪽은 상위 시트가 없고, 오른쪽은 상위 시트가 있습니다. 두세 개의 회로도 시트만 있는 소규모 설계라면 상위 시트가 큰 의미가 없을 수 있습니다. 하지만 시트 수가 많아지면, 상위 시트는 논리 블록(시트 심볼)이 시트에 어떻게 배치되어 있는지에 따라 회로 설계의 기능을 독자가 이해하는 데 도움이 될 수 있습니다. 설계 내 모든 시트는 Projects 패널에서 동일한 레벨에 표시되며, 계층 구조가 없습니다.

Sheet Symbol

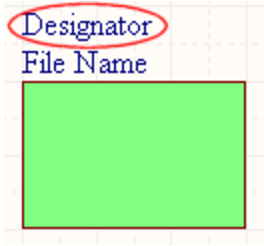

배치된 시트 심볼

요약

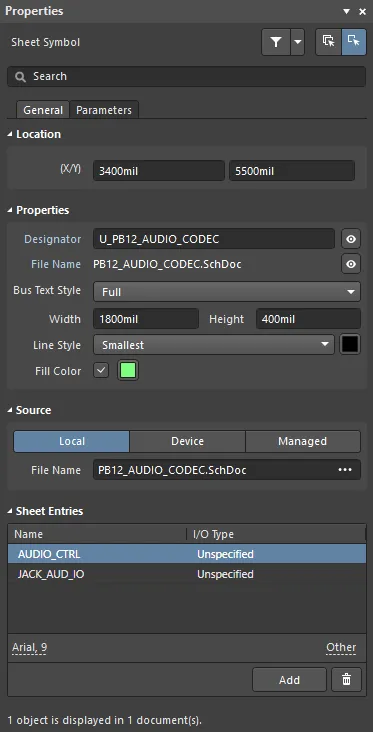

시트 심볼은 전기 설계 기본 요소입니다. 다중 시트 계층적 설계에서 하위 시트를 나타내는 데 사용됩니다. 시트 심볼에는 시트 엔트리 심볼이 포함되어 있어, 계층적 설계에서 부모 시트와 자식 시트 간 신호 연결 지점을 제공합니다. 이는 플랫 시트 설계에서 포트가 시트 간 연결을 제공하는 방식과 유사합니다.

사용 가능 여부

시트 심볼은 Schematic Editor에서만 배치할 수 있습니다. 배치 명령에 접근하려면 다음 방법 중 하나를 사용하세요:

-

메인 메뉴에서 Place » Sheet Symbol 을(를) 선택합니다.

-

디자인 공간 상단에 위치한 Active Bar의 그래픽 오브젝트 드롭다운에서 Sheet Symbol 버튼(

)을 클릭합니다. (관련 명령에 접근하려면 Active Bar버튼을 클릭하고 길게 누르세요. 한 번 사용한 명령은 해당 Active Bar섹션의 최상단에 표시됩니다.)

)을 클릭합니다. (관련 명령에 접근하려면 Active Bar버튼을 클릭하고 길게 누르세요. 한 번 사용한 명령은 해당 Active Bar섹션의 최상단에 표시됩니다.)

-

디자인 공간에서 마우스 오른쪽 버튼을 클릭한 후, 컨텍스트 메뉴에서 Place » Sheet Symbol을(를) 선택합니다.

-

을 클릭하여 Wiring툴바에서 실행합니다.

을 클릭하여 Wiring툴바에서 실행합니다.

배치

명령을 실행하면 커서가 십자선으로 바뀌고 시트 심볼 배치 모드로 전환됩니다. 배치는 다음과 같은 순서로 진행됩니다:

-

시트 심볼의 첫 번째 모서리를 고정하려면 클릭하거나 Enter을(를) 누르세요.

-

커서를 이동하여 시트 심볼의 크기를 조정한 후, 클릭하거나 Enter을(를) 눌러 배치를 완료합니다.

-

계속해서 추가 시트 심볼을 배치하거나, 마우스 오른쪽 버튼을 클릭하거나 Esc을(를) 눌러 배치 모드를 종료합니다.

시트 심볼이 커서에 떠 있는 상태에서 첫 번째 모서리를 고정하기 전까지 배치 중에 수행할 수 있는 추가 동작은 다음과 같습니다:

-

Tab 키를 눌러 Sheet Symbol 모드의 Properties 패널에 접근할 수 있으며, 여기서 시트 심볼의 속성을 바로 변경할 수 있습니다. 디자인 공간 일시정지 버튼 오버레이(

)를 클릭하면 배치를 재개할 수 있습니다.

)를 클릭하면 배치를 재개할 수 있습니다.

-

Alt 키를 누르고 있으면, 최초 이동 방향에 따라 수평 또는 수직 축으로 이동 방향이 제한됩니다.

-

Spacebar을(를) 눌러 시트 심볼을 반시계 방향으로, Shift+Spacebar을(를) 눌러 시계 방향으로 회전할 수 있습니다. 회전은 90° 단위로 이루어집니다.

-

X 또는 Y 키를 눌러 시트 심볼을 X축 또는 Y축을 기준으로 미러링할 수 있습니다.

속성은 배치 중에도 수정할 수 있습니다(

Tab을(를) 통해

Properties 패널에 접근). 단,

Permanent 옵션이

Schematic – Defaults 페이지의

Preferences 대화상자에서 활성화되어 있지 않으면, 수정된 값이 이후 배치의 기본 설정으로 적용된다는 점을 유의하세요. 이 옵션이 활성화되어 있으면, 변경 사항은 현재 배치 중인 객체와 같은 배치 세션에서 추가로 배치되는 객체에만 적용됩니다.

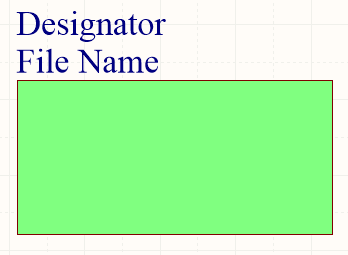

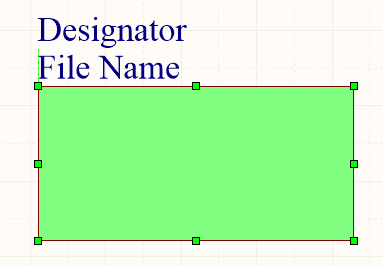

그래픽 편집

이 편집 방법은 디자인 공간에서 배치된 시트 심볼 객체를 직접 선택하여 크기, 모양 또는 위치를 그래픽적으로 변경할 수 있습니다.

시트 심볼 객체가 선택된 상태에서, 편집 핸들을 클릭하고 드래그하여 시트 심볼의 크기를 조절할 수 있습니다.

선택된 시트 심볼

편집 핸들이 아닌 시트 심볼의 아무 곳이나 클릭한 후 드래그하여 위치를 이동할 수 있습니다. 드래그하는 동안, 시트 심볼은 (Spacebar/Shift+Spacebar) 키로 회전하거나, (X 또는 Y 키로 X축 또는 Y축을 기준으로 미러링할 수 있습니다.

시트 심볼의 크기를 조절해도 내부에 정의된 시트 엔트리의 절대 위치에는 영향을 주지 않습니다.

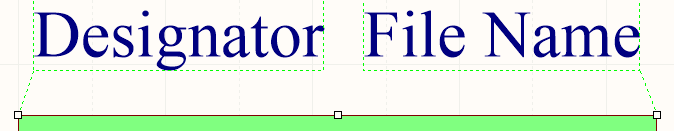

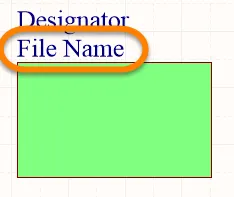

시트 심볼의 Designator 및 File Name 텍스트 필드는 사용된 글꼴 크기를 변경해야만 크기 조절이 가능합니다(해당 객체의 Properties 패널에서 접근). 따라서, 이 객체들이 선택된 경우에는 편집 핸들이 제공되지 않습니다.

시트 심볼의 선택된 Designator 및 Filename

-

점선 상자 내부를 아무 곳이나 클릭한 후 드래그하여 텍스트 객체의 위치를 원하는 대로 이동할 수 있습니다. 드래그하는 동안, 텍스트는 (Spacebar/Shift+Spacebar) 키로 회전하거나, (X 또는 Y 키로 X축 또는 Y축을 기준으로 미러링할 수 있습니다.

-

객체의 텍스트는 다음과 같이 인라인으로 편집할 수 있습니다:

-

Designator 또는 Filename 텍스트를 한 번 클릭하여 선택합니다.

-

다시 한 번 클릭(또는 Enter 키를 누름)하여 인라인 편집 모드로 진입합니다. 두 번 클릭으로 인식되지 않도록 각 클릭 사이에 충분한 시간을 두어야 합니다(두 번 클릭 시 관련 Properties 패널이 열립니다).

-

인라인 텍스트 편집을 마치려면 Enter 키를 누르거나 마우스로 텍스트 객체 외부를 클릭하세요.

Locked 속성이 활성화된 객체를 그래픽적으로 수정하려고 하면, 편집을 계속할지 확인하는 대화상자가 나타납니다. Protect Locked Objects 옵션이 Schematic – Graphical Editing 페이지의 Preferences 대화상자에서 활성화되어 있고, 해당 디자인 객체의 Locked 옵션도 활성화되어 있다면, 해당 객체는 선택하거나 그래픽적으로 편집할 수 없습니다. 잠긴 객체를 클릭하여 선택한 후, Locked 속성을 List 패널에서 비활성화하거나 Protect Locked Objects 옵션을 비활성화하여 그래픽 편집이 가능하도록 하세요.

비그래픽 편집

다음과 같은 비그래픽 편집 방법이 제공됩니다.

시트 심볼 대화상자 또는 속성 패널을 통한 편집

Properties page: 시트 심볼 속성

이 편집 방법은 관련 시트 심볼 대화상자와 Properties 패널 모드를 사용하여 시트 심볼 객체의 속성을 수정합니다.

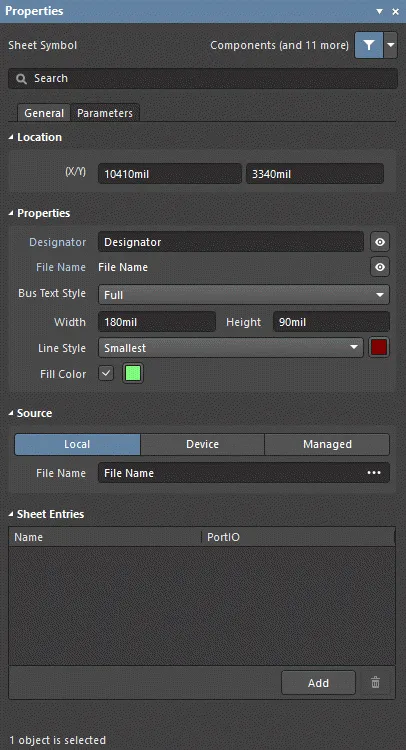

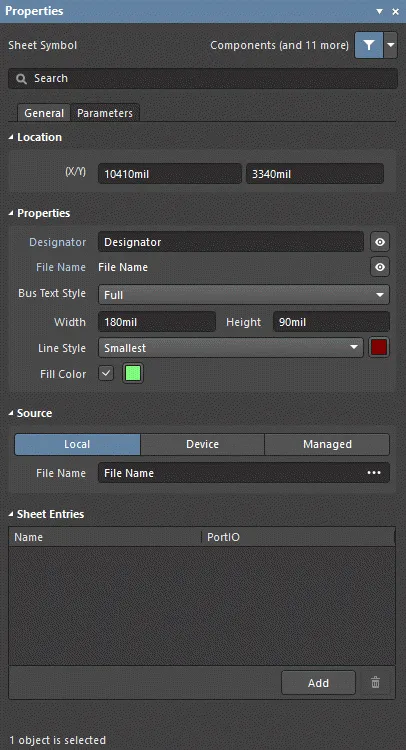

왼쪽의 Sheet Symbol 대화상자와 오른쪽의 속성 패널 Sheet Symbol 모드

배치 후, Sheet Symbol 대화상자에 접근하는 방법:

-

배치된 시트 심볼 객체를 더블 클릭합니다.

-

시트 심볼 객체 위에 커서를 올리고 마우스 오른쪽 버튼을 클릭한 후, 컨텍스트 메뉴에서 Properties을(를) 선택합니다.

배치 중에는 Sheet Symbol 모드의 Properties 패널에 Tab 키를 눌러 접근할 수 있습니다. 시트 심볼이 배치되면 모든 옵션이 표시됩니다.

배치 후, Sheet Symbol 모드의 Properties 패널에 접근하는 방법은 다음과 같습니다:

-

Properties 패널이 이미 활성화된 경우, 시트 심볼 객체를 선택합니다.

-

시트 심볼 객체를 선택한 후, 디자인 공간 오른쪽 하단의 Properties 패널을 Panels 버튼에서 선택하거나 View » Panels » Properties을(를) 선택합니다.

Double Click Runs Interactive Properties 옵션이

Schematic - Graphical Editing 페이지의

Preferences 대화상자에서 비활성화(기본값)되어 있으면, 프리미티브를 더블 클릭하거나 선택된 프리미티브에서 마우스 오른쪽 버튼을 클릭한 후

Properties을(를) 선택하면 대화상자가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면,

Properties 패널이 열립니다.

대화상자와 패널의 옵션은 동일하지만, 옵션의 순서와 배치가 약간 다를 수 있습니다.

시트 심볼 속성은 배치 모드에 진입하기 전에

Schematic – Defaults 페이지의

Preferences 대화상자에서 접근할 수 있습니다. 이를 통해 시트 심볼 객체의 기본 속성을 변경할 수 있으며, 이후 시트 심볼 배치 시 적용됩니다.

다중 객체 편집

Properties 패널은 다중 객체 편집을 지원하며, 현재 선택된 모든 객체에서 동일한 속성 값만 수정할 수 있습니다. 동일한 객체 유형을 수동으로 여러 개 선택하거나, Find Similar Objects 대화상자 또는 SCH Filter나 SCH List 패널을 통해 선택한 경우, Properties 패널 필드 항목이 별표(*)로 표시되지 않으면 모든 선택된 객체에 대해 해당 값을 수정할 수 있습니다.

리스트 패널을 통한 편집

Panel pages: 리스트 패널, SCH Filter

List 패널을 사용하면 하나 이상의 문서에서 디자인 객체를 표 형식으로 표시하여 객체 속성을 빠르게 확인하고 수정할 수 있습니다. 적절한 필터링(Filter 패널 또는 Find Similar Objects 대화상자 사용)과 함께 활용하면, 활성 필터 범위에 해당하는 객체만 표시하여 여러 디자인 객체를 더욱 정확하고 효율적으로 편집할 수 있습니다.

시트 심볼 작업

Designator 및 File Name 서식 지정

시트 심볼의 Designator 및 File Name 필드는 시트 심볼과 독립적으로 서식을 지정할 수 있습니다. 해당 Properties 패널은 위에서 설명한 배치 후 방법을 사용하여 접근할 수 있습니다(시트 심볼 대신 속성을 확인/수정하려는 해당 객체로 대체).

시트 심볼의

File Name (

Sheet Symbol 모드의

Properties 패널에서 설정)는 해당 심볼이 나타내는 회로도 시트의 파일명으로 반드시 설정해야 합니다.

시트 심볼 우클릭 명령

배치된 시트 심볼 위에서 마우스 오른쪽 버튼을 클릭하면 상황에 맞는 메뉴가 나타나며, 여기서 해당 시트 심볼(또는 현재 선택된 모든 시트 심볼)에 적용되는 다음 명령( Sheet Symbol Actions 하위 메뉴에 있음)을 사용할 수 있습니다.

-

Open SubSheet "<SheetName.SchDoc>"- 이 심볼이 참조하는 하위 시트를 열람할 때 사용합니다. 해당 시트가 이미 열려 있지 않다면 열리고, 메인 디자인 창에서 활성 문서로 전환됩니다.

-

Create Sheet From Sheet Symbol - 시트 심볼에서 새로운 회로도 문서를 생성하고, 심볼에 있는 각 시트 엔트리에 해당하는 포트를 해당 문서에 추가할 때 사용합니다. 이렇게 하면, 상위 시트에 생성 및 배치한 시트 심볼을 기반으로 멀티 시트 회로도 설계의 하위 시트를 자동으로 생성할 수 있습니다.

생성된 회로도 문서는 시트 심볼의 File Name 필드에 입력된 이름을 사용하여 명명됩니다. 명령을 실행하기 전에 이 필드에 문서의 원하는 이름(확장자 포함, 예: DocumentName.SchDoc)을 입력하거나, 이름을 비워두고 나중에 생성된 문서를 저장할 때 이름을 입력할 수 있습니다.

이미 동일한 파일 이름의 시트가 존재하는 경우, 시트 심볼에서 시트를 생성할 때 주의해야 합니다. 동일한 파일 이름의 새로운 시트가 생성됩니다. 저장 시에는 새 시트를 다른 이름으로 저장하거나, 필요하다면 기존 시트를 덮어써서 중복을 해결할 수 있습니다.

-

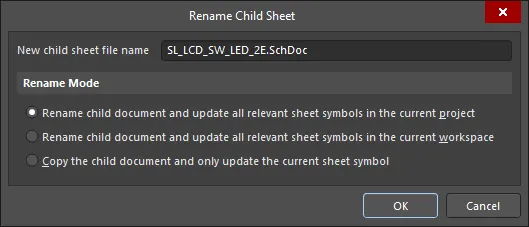

Rename Child Sheet (메인 메뉴에서 Design » Rename Child Sheet 명령을 선택하여 접근할 수도 있습니다) - 시트 심볼이 참조하는 하위 회로도 시트의 이름을 빠르게 변경할 때 사용합니다. Rename Child Sheet 대화 상자가 열립니다.

Rename Child Sheet 대화 상자

회로도 시트의 새 이름을 New child sheet file name 필드에 지정하되, .SchDoc 확장자는 반드시 유지해야 합니다. 또한, 다음 옵션 중에서 이름 변경의 범위(작업의 적용 범위)를 결정합니다:

-

Rename child document and update all relevant sheet symbols in the current project– 이 옵션을 활성화하면 하위 시트의 이름을 변경하고, 활성 프로젝트의 소스 회로도에 있는 해당 시트를 참조하는 모든 시트 심볼도 함께 업데이트합니다. 각 시트 심볼의 File Name이(가) 새로 이름이 변경된 하위 시트를 반영하도록 업데이트됩니다.

-

Rename child document and update all relevant sheet symbols in the current workspace– 이 옵션을 활성화하면 하위 시트의 이름을 변경하고, 열려 있는 모든 프로젝트의 소스 회로도에 있는 해당 시트를 참조하는 모든 시트 심볼도 함께 업데이트합니다. 각 시트 심볼의 File Name이(가) 새로 이름이 변경된 하위 시트를 반영하도록 업데이트됩니다.

-

Copy the child document and only update the current sheet symbol– 이 옵션을 활성화하면 이름을 변경하기 전에 하위 시트의 복사본을 만듭니다. 이 옵션을 사용할 경우 현재 커서 아래에 있는 시트 심볼만 업데이트됩니다. 시트 심볼의 File Name 필드가 복사된 하위 시트를 참조하도록 업데이트됩니다.

하위 시트의 복사본을 만드는 것은, 현재 하위 시트가 여러 시트 심볼에서 참조되고 있고, 그 중 한 시트 심볼만 해당 시트의 회로를 수정한 버전을 참조해야 할 때 유용합니다. 원본 시트는 그대로 유지하면서, 단일 시트 심볼에서 참조할 수 있도록 이름이 변경된 복사본을 생성하는 것입니다. 이후 복사된 시트의 내용을 필요에 따라 수정할 수 있습니다.

-

Synchronize Sheet Entries and Ports - 시트 심볼의 시트 엔트리와 하위 시트 포트를 동기화할 때 사용합니다. 포트를 시트 엔트리와 동기화 대화 상자가 열립니다. 이 대화 상자를 사용하여 시트 심볼의 모든 시트 엔트리가 아래에 참조된 하위 시트의 포트와 이름 및 I/O 타입이 일치하는지 확인할 수 있습니다.

-

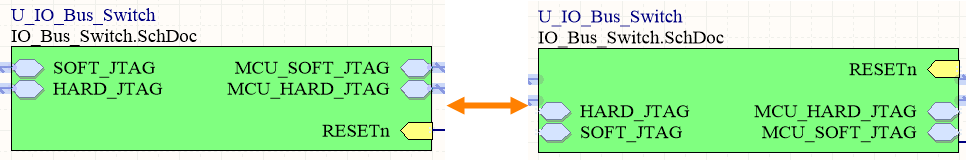

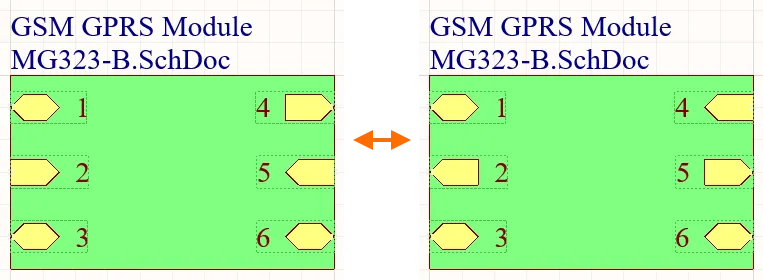

Flip Sheet Symbol Along X - 시트 심볼을 X축을 기준으로 뒤집을 때 사용합니다. 심볼에 연결된 시트 엔트리는 본질적으로 심볼의 반대편(수평 방향)으로 이동됩니다. 왼쪽에 있던 엔트리는 오른쪽으로, 오른쪽에 있던 엔트리는 왼쪽으로 재배치됩니다. 시트 엔트리의 I/O Type은 변경되지 않습니다.

X축을 기준으로 시트 심볼을 뒤집은 예시

하나 또는 여러 개의 시트 심볼이 현재 선택되어 있으면, 명령은 Flip Selected Sheet Symbols Along X로 표시됩니다. 이 명령은 메인 메뉴의 Edit » Move 하위 메뉴와 Active Bar에서도 사용할 수 있습니다. 여러 시트 심볼을 동시에 뒤집을 경우, 선택된 심볼들의 경계 중간에 위치한 가상의 수직선을 기준으로 뒤집기가 이루어집니다.

-

Flip Sheet Symbol Along Y - 시트 심볼을 Y축을 기준으로 뒤집을 때 사용합니다. 심볼에 연결된 시트 엔트리는 본질적으로 심볼의 반대편(수직 방향)으로 이동됩니다. 위쪽에 있던 엔트리는 아래쪽으로, 아래쪽에 있던 엔트리는 위쪽으로 재배치됩니다. 시트 엔트리의 I/O Type은 변경되지 않습니다.

Y축을 기준으로 시트 심볼을 뒤집은 예시

하나 또는 여러 개의 시트 심볼이 현재 선택되어 있으면, 명령은 Flip Selected Sheet Symbols Along Y로 표시됩니다. 이 명령은 메인 메뉴의 Edit » Move 하위 메뉴와 Active Bar에서도 사용할 수 있습니다. 여러 시트 심볼을 동시에 뒤집을 경우, 선택된 심볼들의 경계 중간에 위치한 가상의 수평선을 기준으로 뒤집기가 이루어집니다.

-

Toggle All Sheet Entries IO Type in Sheet Symbol - 시트 심볼 내 모든 시트 엔트리의 I/O 타입을 동시에 전환할 때 사용합니다(적용 가능한 경우). Toggle All Sheet Entries IO Type In (Selected) Sheet Symbols을 클릭하거나 Edit » Move 메인 메뉴 또는 Active Bar에서도 사용할 수 있습니다.

시트 엔트리 I/O 전환 결과 예시

시트 엔트리 I/O 전환 결과 예시

실제 변경은 현재 PortIO 타입에 따라 다음과 같이 달라집니다:

-

Unspecified Unspecified로 유지됩니다.

-

Output Input로 변경됩니다.

-

Input Output로 변경됩니다.

-

BidirectionalBidirectional로 유지됩니다.

참고

-

시트 엔트리 그룹을 선택된 시트 심볼에 붙여넣을 때, 해당 엔트리가 심볼의 현재 경계 밖에 위치한다면, 심볼이 자동으로 크기가 조정되어 엔트리를 수용합니다.

-

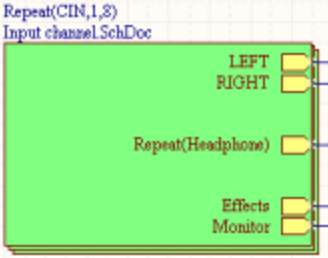

시트 심볼 인스턴스화를 사용하면, 동일한 하위 시트의 여러 채널을 단일 시트 심볼에서 참조할 수 있습니다. 이때 Repeat 키워드를 시트 심볼의 Designator 필드에 사용하며, 형식은 다음과 같습니다:

Repeat(SheetSymbolDesignator, FirstInstance, LastInstance),

여기서 SheetSymbolDesignator는 시트 심볼의 기본 이름이고, FirstInstance 와 LastInstance은 인스턴스화할 채널 수를 정의합니다.

New Indexing of Sheet Symbols 옵션이 Project Options 대화 상자의

Options 탭에서 활성화되어 있으면, 반복되는 시트 심볼의 첫 번째 또는 마지막 인덱스로 0을 포함한 임의의 숫자를 사용할 수 있습니다. 단, 마지막 인덱스는 항상 첫 번째 인덱스보다 커야 하며, 음수는 허용되지 않습니다.

-

하나의 시트 심볼이 여러 하위 시트를 참조할 수도 있습니다. File Name 필드에 각 파일 이름을 세미콜론(;)으로 구분하여 입력하면 됩니다. 하위 시트에 오프 시트 커넥터를 효과적으로 배치하면, 설계의 한 부분을 여러 시트에 분산시켜 마치 하나의 거대한(플랫) 시트처럼 다룰 수 있습니다. 단, 오프 시트 커넥터는 동일한 시트 심볼이 참조하는 시트에서만 사용할 수 있다는 점에 유의하세요.

SheetSymbolDesignator 특수 문자열을 사용할 수 있습니다. 이 특수 문자열은 하위 회로도 시트에 배치하여 상위 회로도 시트에 배치된 관련 Sheet Symbol 객체의 디자인레이터를 표시할 수 있습니다. 이 특수 문자열은 다중 채널 설계에서도 사용할 수 있습니다. 하위 회로도 시트의 컴파일된 탭을 선택하면 특수 문자열의 변환된 값을 확인할 수 있습니다.

-

상위 시트 심볼의 한쪽 면에 배치된 선택된 시트 엔트리의 순서를 반대로 하려면, 메인 메뉴에서 Edit » Move » Reverse Selected Sheet Entries Order 명령을 선택하거나, Reverse Selected Sheet Entries Order 명령을 Active Bar에서 찾아 사용하면 됩니다. 이 명령이 적용되려면, 시트 심볼의 특정 면에 두 개 이상의 시트 엔트리가 선택되어 있어야 합니다. 동일한 상위 시트 심볼의 서로 다른 면이나, 활성 회로도 시트에 있는 여러 시트 심볼에 대해 동시에 시트 엔트리의 순서를 변경할 수 있습니다. 명령을 실행하면 순서가 변경됩니다. 순서 변경은 선택된 시트 엔트리의 위치를 해당 시트 심볼 면을 따라, 가장 바깥쪽에 있는 두 엔트리 사이의 중간 지점을 기준으로 대칭 이동시켜 이루어집니다. I/O Type 시트 엔트리의 I/O Type는 순서 변경에 의해 변경되지 않습니다.

Sheet Symbol Properties

회로도 에디터 객체 속성은 배치된 객체의 시각적 스타일, 내용 및 동작을 지정하는 정의 가능한 옵션입니다. 각 객체 유형의 속성 설정은 두 가지 방식으로 정의됩니다:

-

Pre-placement settings – 대부분의 Sheet Symbol 객체 속성, 또는 논리적으로 사전 정의가 가능한 속성은 Schematic - Defaults 페이지의 Preferences 대화상자(설계 공간 우측 상단의

버튼에서 접근)에서 기본값으로 편집할 수 있습니다. Primitive List에서 객체를 선택하면 우측에 해당 옵션이 표시됩니다.

버튼에서 접근)에서 기본값으로 편집할 수 있습니다. Primitive List에서 객체를 선택하면 우측에 해당 옵션이 표시됩니다.

-

Post-placement settings – 모든 Sheet Symbol 객체 속성은 설계 공간에서 배치된 Sheet Symbol을 선택했을 때 Sheet Symbol 대화상자와 Properties 패널에서 편집할 수 있습니다.

만약

Double Click Runs Interactive Properties 옵션이

Schematic - Graphical Editing 페이지의

Preferences 대화상자에서 비활성화(기본값)되어 있다면, 프리미티브를 더블 클릭하거나 선택된 프리미티브에서 마우스 오른쪽 버튼을 클릭한 후

Properties를 선택하면 대화상자가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면

Properties 패널이 열립니다.

대화상자와 패널에서 제공되는 옵션은 동일하지만, 옵션의 순서와 배치가 약간 다를 수 있습니다.

아래 속성 목록에서, Preferences 대화상자에서 기본값으로 제공되지 않는 옵션은 "Properties panel only"로 표시되어 있습니다.

일반 탭

위치 (Properties panel only)

-

(X/Y)

-

X (첫 번째 필드) - 객체 기준점의 현재 X(수평) 좌표로, 현재 설계 공간 원점 기준입니다. 값을 편집하여 객체의 X 위치를 변경할 수 있습니다. 값은 미터법 또는 영국식 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 값을 입력할 때는 단위를 함께 입력해야 합니다.

-

Y (두 번째 필드) - 객체 기준점의 현재 Y(수직) 좌표로, 현재 원점 기준입니다. 값을 편집하여 객체의 Y 위치를 변경할 수 있습니다. 값은 미터법 또는 영국식 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 값을 입력할 때는 단위를 함께 입력해야 합니다.

속성

소스 (Properties panel only)

-

Local / Device / Managed- 파일의 소스입니다.

-

File Name - 현재 시트 심볼이 참조하는 회로도 문서를 표시합니다. 이 필드는 시트 심볼과 해당 심볼이 나타내는 회로도 하위 시트 간의 연결을 제공합니다.

를 클릭하면

를 클릭하면 ![]() 참조할 문서 선택 대화상자가 열리며, 필요한 대상 하위 시트를 선택할 수 있습니다. 이 대화상자에는 프로젝트 내의 모든 소스 회로도 시트 목록이 표시됩니다(현재 심볼이 배치된 시트는 제외).

참조할 문서 선택 대화상자가 열리며, 필요한 대상 하위 시트를 선택할 수 있습니다. 이 대화상자에는 프로젝트 내의 모든 소스 회로도 시트 목록이 표시됩니다(현재 심볼이 배치된 시트는 제외).

하나의 시트 심볼이 여러 하위 시트를 참조할 수 있습니다. 각 파일 이름은 세미콜론(;)으로 구분하여 File Name 필드에 입력합니다. 하위 시트에 오프 시트 커넥터를 효과적으로 배치하면, 설계의 한 부분을 여러 시트에 걸쳐 배치할 수 있으며, 마치 하나의 거대한(플랫) 시트처럼 취급할 수 있습니다. 단, 오프 시트 커넥터는 동일한 시트 심볼이 참조하는 시트에서만 사용할 수 있습니다.

시트 엔트리 (Properties 패널 전용)

-

Grid - 현재 시트 심볼에 정의된 모든 시트 엔트리의 Name 및 PortIO Type을 나열합니다. 그리드에 시트 엔트리가 있을 경우, 엔트리를 선택하면 다음과 같은 추가 옵션을 사용할 수 있습니다:

-

Font - 시트 엔트리의 글꼴 스타일을 설정하려면 클릭합니다.

-

Other - 추가 옵션을 변경할 수 있는 드롭다운을 열려면 클릭합니다:

-

Kind - 드롭다운에서 시트 엔트리 종류를 선택합니다.

-

Border Color - 테두리 색상을 선택할 수 있는 컨트롤에 접근하려면 클릭합니다.

-

채우기 Color - 채우기 색상을 선택할 수 있는 컨트롤에 접근하려면 클릭합니다.

-

Add - 시트 엔트리를 추가하려면 클릭합니다.

을 사용하여 테이블에서 선택한 엔트리를 삭제할 수 있습니다.

을 사용하여 테이블에서 선택한 엔트리를 삭제할 수 있습니다.

파라미터 탭

파라미터

-

Grid - 현재 시트 심볼에 정의된 모든 파라미터의 Name 및 Value을 나열합니다. 그리드에 파라미터가 있을 경우, 파라미터를 선택하면 다음과 같은 추가 옵션을 사용할 수 있습니다:

-

Font - 파라미터의 글꼴 스타일을 설정하려면 클릭합니다.

-

Other - 추가 옵션을 변경할 수 있는 드롭다운을 열려면 클릭합니다:

-

Show Parameter Name - 파라미터 이름을 디자인 공간에 표시하려면 활성화합니다.

-

Allow Synchronization with Database - 데이터베이스와 동기화하려면 활성화합니다. 이 옵션은 코멘트가 업데이트될 수 있는지 제어합니다. 기본적으로 이 옵션은 활성화되어 있어 소스 라이브러리/데이터베이스와 항상 동기화가 가능합니다. 업데이트 과정에서 해당 코멘트가 포함되지 않도록 하려면 이 옵션을 비활성화할 수 있습니다.

-

X/Y - 원하는 X, Y 좌표를 입력합니다.

-

Rotation - 드롭다운에서 회전 각도를 선택합니다.

-

Autoposition - 자동 위치 지정을 활성화하면, 컴포넌트를 이동하거나 회전할 때 텍스트가 선택한 위치에 유지됩니다.

-

Add - 파라미터를 추가하려면 클릭합니다.

을 사용하여 테이블에서 선택한 엔트리를 삭제할 수 있습니다.

을 사용하여 테이블에서 선택한 엔트리를 삭제할 수 있습니다.

Sheet Symbol Designator

시트 심볼 디지네이터

요약

시트 심볼 디지네이터는 전기적 설계 프리미티브의 비전기적 하위 객체입니다. 이는 시트 심볼에 의미 있는 이름을 부여하여 동일한 회로도 시트에 배치된 다른 시트 심볼과 구분할 수 있도록 사용됩니다. 일반적으로 이 이름은 해당 심볼이 나타내는 회로도 하위 시트의 전체 기능을 반영합니다.

사용 가능성 및 배치

시트 심볼 디지네이터는 상위 컴포넌트 파트 객체가 배치될 때 자동으로 배치됩니다. 사용자가 직접 배치할 수 있는 설계 객체는 아닙니다.

시트 심볼 배치 중

Designator 필드에서 변경을 하면,

Permanent 옵션이

Schematic - Defaults 페이지의

Preferences 대화상자에서 활성화되어 있지 않은 한, 시트 심볼 디지네이터 객체의 기본 속성이 업데이트됩니다. 이 옵션이 활성화되어 있으면, 변경 사항은 현재 배치 중인 시트 심볼 객체와 동일한 배치 세션에서 추가로 배치되는 시트 심볼 객체의 디지네이터에만 영향을 미칩니다.

그래픽 편집

이 편집 방법을 사용하면 설계 공간에서 시트 심볼 디지네이터 객체를 직접 선택하여 위치를 그래픽적으로 변경할 수 있습니다. 시트 심볼 디지네이터는 Font 의 크기를 속성 패널에서 변경하여 크기만 조정할 수 있습니다. 따라서, 시트 심볼 디지네이터 객체를 선택해도 편집 핸들은 제공되지 않습니다:

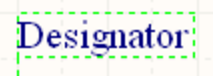

선택된 시트 심볼 디지네이터

점선 상자 내부를 아무 곳이나 클릭한 후 드래그하여 시트 심볼 디지네이터 객체의 위치를 원하는 대로 이동할 수 있습니다. 드래그 중에 객체를 회전하거나 반전할 수 있습니다:

-

Tab키를 누르면 Properties 패널이 열리며, 여기서 시트 심볼 디지네이터의 속성을 즉시 변경할 수 있습니다.

-

Alt키를 누르면 이동 방향이 처음 이동한 방향에 따라 수평 또는 수직 축으로 제한됩니다.

-

Spacebar을 누르면 시트 심볼 디지네이터가 반시계 방향으로, Shift+Spacebar을 누르면 시계 방향으로 회전합니다. 회전은 90° 단위로 이루어집니다.

-

X 또는 Y키를 누르면 시트 심볼 디지네이터를 X축 또는 Y축을 기준으로 미러링할 수 있습니다.

In-Place Editing 옵션이

Schematic - General 페이지의

Preferences 대화상자에서 활성화되어 있으면, 설계 공간에서 시트 심볼 디지네이터의 이름을 직접 편집할 수 있습니다. 디지네이터를 선택한 후 한 번 클릭하면 해당 기능이 활성화됩니다. 원하는 새 이름을 입력한 후, 시트 심볼 디지네이터 필드 밖을 클릭하거나

Enter 을 눌러 변경을 적용합니다.

Locked 속성이 활성화된 객체를 그래픽적으로 수정하려고 하면, 편집을 계속할지 확인하는 대화상자가 나타납니다. Protect Locked Objects 옵션이 Schematic – Graphical Editing 페이지의 Preferences 대화상자에서 활성화되어 있고, 해당 설계 객체의 Locked 옵션도 활성화되어 있다면, 해당 객체는 선택하거나 그래픽적으로 편집할 수 없습니다. 잠긴 객체를 클릭하여 선택한 후, Locked 속성을 List 패널에서 비활성화하거나 Protect Locked Objects 옵션을 비활성화하여 객체를 그래픽적으로 편집할 수 있습니다.

비그래픽 편집

다음과 같은 비그래픽 편집 방법을 사용할 수 있습니다.

파라미터 대화상자 또는 속성 패널을 통한 편집

Panel page: 시트 심볼 디지네이터 속성이 편집 방법은 관련 Parameter 대화상자와 Properties패널 모드를 사용하여 시트 심볼 디지네이터 객체의 속성을 수정합니다.

Parameter 대화상자(왼쪽)와 속성 패널의 Parameter 모드(오른쪽)

Parameter 대화상자(왼쪽)와 속성 패널의 Parameter 모드(오른쪽)

배치 후, Parameter 대화상자는 다음 방법으로 접근할 수 있습니다:

- 배치된 시트 심볼 지정자 객체를 더블 클릭합니다.

-

시트 심볼 지정자 객체 위에 커서를 올리고 마우스 오른쪽 버튼을 클릭한 후, 컨텍스트 메뉴에서 Properties를 선택합니다.

배치 중에 Parameter 모드의 Properties 패널은 Tab 키를 눌러 접근할 수 있습니다. 시트 심볼 지정자가 배치되면 모든 옵션이 나타납니다.

배치 후에는 Parameter 모드의 Properties 패널에 다음 방법 중 하나로 접근할 수 있습니다:

-

Properties 패널이 이미 활성화되어 있다면, 시트 심볼 지정자 객체를 선택합니다.

-

시트 심볼 지정자 객체를 선택한 후, 디자인 공간 오른쪽 하단의 Panels 버튼에서 Properties 패널을 선택하거나 View » Panels » Properties를 선택합니다.

Schematic - Graphical Editing 페이지의

Double Click Runs Interactive Properties 옵션이

Preferences 대화상자에서 비활성화(기본값)되어 있을 때, 프리미티브를 더블 클릭하거나 선택된 프리미티브에서 마우스 오른쪽 버튼을 클릭한 후

Properties을 선택하면 대화상자가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면

Properties 패널이 열립니다.

대화상자와 패널에서 제공되는 옵션은 동일하지만, 옵션의 순서와 배치가 약간 다를 수 있습니다.

시트 심볼 지정자 속성은 배치 모드에 들어가기 전에

Schematic – Defaults 페이지의

Preferences 대화상자에서 접근할 수 있습니다. 이를 통해 시트 심볼 지정자 객체의 기본 속성을 변경할 수 있으며, 이후에 배치되는 시트 심볼 지정자에 적용됩니다.

여러 객체 편집

Properties 패널은 여러 객체 편집을 지원하며, 현재 선택된 모든 객체에서 동일한 속성 설정을 수정할 수 있습니다. 동일한 객체 유형을 수동으로 여러 개 선택하거나, Find Similar Objects 대화상자, Filter 또는 List 패널을 통해 선택한 경우, 별표(*)로 표시되지 않은 Properties 패널 필드 항목은 선택된 모든 객체에 대해 수정할 수 있습니다.

리스트 패널을 통한 편집

Panel pages: 리스트 패널, SCH Filter, SCHLIB Filter

List 패널을 사용하면 하나 이상의 문서에서 디자인 객체를 표 형식으로 표시하여 객체 속성을 빠르게 확인하고 수정할 수 있습니다. 적절한 필터링(Filter 패널 또는 Find Similar Objects 대화상자 사용)과 함께 사용하면, 활성 필터 범위에 해당하는 객체만 표시되어 여러 디자인 객체를 더욱 정확하고 효율적으로 편집할 수 있습니다.

참고

-

텍스트 프레임은 X 또는 Y축을 따라 회전하거나 미러링할 수 있지만, 내부 텍스트의 방향에는 영향을 주지 않습니다.

-

간단한 한 줄 텍스트 주석에는 Text String 객체 사용을 고려하세요.

-

시트 심볼 인스턴스화를 사용하면 동일한 서브시트의 여러 채널을 하나의 시트 심볼에서 참조할 수 있습니다. 이때 Repeat 키워드를 시트 심볼 지정자 필드에 사용하며, 형식은 다음과 같습니다:

Repeat(SheetSymbolDesignator, FirstInstance, LastInstance).

Repeat 키워드 사용

SheetSymbolDesignator은 시트 심볼의 기본 이름이며, FirstInstance와 LastInstance가 함께 인스턴스화할 채널 수를 정의합니다. 프로젝트를 빌드할 때, 컴파일러는 내부 컴파일 모델을 생성하면서 각 채널에 포함된 모든 부품을 고유하게 식별할 수 있도록 선택한 주석 방식을 사용하여 필요한 횟수만큼 채널을 인스턴스화합니다. 채널 서브시트는 복제되지 않으며, 컴파일 후에는 해당 시트의 각 채널마다 메인 디자인 창 하단에 별도의 탭이 나타납니다.

New Indexing of Sheet Symbols 옵션이 Project Options 대화상자의

Options 탭에서 활성화되어 있으면, 반복되는 Sheet Symbol의 첫 번째 또는 마지막 인덱스로 0을 포함한 모든 숫자를 사용할 수 있습니다. 단, 마지막 인덱스는 항상 첫 번째 인덱스보다 커야 하며 음수는 허용되지 않습니다.

-

SheetSymbolDesignator 특수 문자열을 사용할 수 있습니다. 이 특수 문자열은 하위 회로도 시트에 배치하여 상위 회로도 시트에 배치된 관련 Sheet Symbol 객체의 지정자를 표시할 수 있습니다. 이 특수 문자열은 다중 채널 설계에서도 사용할 수 있습니다. 하위 회로도 시트의 컴파일된 탭을 선택하면 특수 문자열의 변환된 값을 확인할 수 있습니다.

Sheet Symbol Designator Properties

회로도 에디터 객체 속성은 배치된 객체의 시각적 스타일, 내용 및 동작을 지정하는 정의 가능한 옵션입니다. 각 객체 유형의 속성 설정은 두 가지 방법으로 정의됩니다:

-

Pre-placement settings – 대부분의 Sheet Symbol Designator 객체 속성 또는 논리적으로 사전 정의할 수 있는 속성은 Schematic - Defaults 페이지의 Preferences 대화상자(디자인 공간 우측 상단의  버튼에서 접근)에서 기본값으로 편집할 수 있습니다. Primitive List에서 객체를 선택하면 오른쪽에 해당 옵션이 표시됩니다.

버튼에서 접근)에서 기본값으로 편집할 수 있습니다. Primitive List에서 객체를 선택하면 오른쪽에 해당 옵션이 표시됩니다.

-

Post-placement settings – 모든 Sheet Symbol Designator 객체 속성은 디자인 공간에서 배치된 Sheet Symbol Designator를 선택하면 Parameter 대화상자와 Properties 패널에서 편집할 수 있습니다.

Schematic - Graphical Editing 페이지의

Double Click Runs Interactive Properties 옵션이

Preferences 대화상자에서 비활성화(기본값)되어 있을 때, 프리미티브를 더블 클릭하거나 선택된 프리미티브에서 마우스 오른쪽 버튼을 클릭한 후

Properties을 선택하면 대화상자가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면

Properties 패널이 열립니다.

대화상자와 패널에서 제공되는 옵션은 동일하지만, 옵션의 순서와 배치가 약간 다를 수 있습니다.

아래 속성 목록에서 Preferences 대화상자에서 기본 설정으로 제공되지 않는 옵션은 "Properties panel only"로 표시되어 있습니다.

위치 (Properties panel only)

-

(X/Y)

-

X(첫 번째 필드) - 객체 기준점의 현재 X(수평) 좌표로, 현재 디자인 공간 원점 기준입니다. 값을 수정하여 객체의 X 위치를 변경할 수 있습니다. 값은 미터법 또는 영국식 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 값을 입력할 때는 단위를 함께 입력하세요.

-

Y (두 번째 필드) - 객체 기준점의 현재 Y(수직) 좌표로, 현재 원점 기준입니다. 값을 수정하여 객체의 Y 위치를 변경할 수 있습니다. 값은 미터법 또는 영국식 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 값을 입력할 때는 단위를 함께 입력하세요.

-

Rotation - 드롭다운을 사용하여 회전 각도를 선택하세요.

속성

Sheet Symbol File Name

시트 심볼 파일 이름

요약

시트 심볼 파일 이름은 전기적 설계 프리미티브의 비전기적 자식 객체입니다. 이는 시트 심볼과 해당 심볼이 나타내는 회로도 서브 시트 간의 연결을 제공합니다.

사용 가능 여부 및 배치

시트 심볼 파일 이름은 상위 시트 심볼 객체가 배치될 때 자동으로 배치됩니다. 사용자가 직접 배치할 수 있는 설계 객체는 아닙니다.

배치 중에 속성을 수정할 수 있지만(

Tab를 눌러

Properties 패널에 접근), 이 설정은

Permanent 옵션이

회로도 – 기본값 페이지의

Preferences 대화상자에서 활성화되지 않는 한 이후 배치의 기본 설정이 됩니다. 이 옵션이 활성화되면 변경 사항은 현재 배치 중인 객체와 동일한 배치 세션에서 추가로 배치되는 객체에만 적용됩니다.

그래픽 편집

이 편집 방법을 사용하면 설계 공간에서 시트 심볼 파일 이름 객체를 직접 선택하여 위치를 그래픽적으로 변경할 수 있습니다. 시트 심볼 파일 이름은 Font 의 크기를 속성 패널에서 변경하여 크기만 조정할 수 있습니다. 따라서 시트 심볼 파일 이름 객체를 선택해도 편집 핸들은 제공되지 않습니다.

점선 상자 내부를 아무 곳이나 클릭한 후 드래그하여 시트 심볼 파일 이름 객체의 위치를 원하는 대로 이동할 수 있습니다. 드래그하는 동안 객체를 회전하거나 뒤집을 수 있습니다.

점선 상자 내부를 아무 곳이나 클릭한 후 드래그하여 시트 심볼 파일 이름 객체의 위치를 원하는 대로 이동할 수 있습니다. 드래그하는 동안 객체를 회전하거나 뒤집을 수 있습니다.

Spacebar를 눌러 파일 이름을 회전할 수 있습니다. 회전은 90°씩 반시계 방향으로 이루어집니다.

In-Place Editing 옵션이

회로도 - 일반 페이지의

Preferences 대화상자에서 활성화되어 있으면, 설계 공간에서 시트 심볼 파일 이름의 이름을 직접 편집할 수 있습니다. 디자인레이터를 선택한 후 한 번 클릭하면 해당 기능이 실행됩니다. 필요한 새 이름을 입력한 후 시트 심볼 파일 이름에서 벗어나 클릭하거나

Enter 를 눌러 변경을 적용하세요.

Locked 속성이 활성화된 객체를 그래픽적으로 수정하려고 하면, 편집을 계속할지 확인하는 대화상자가 나타납니다. Protect Locked Objects 옵션이 Schematic – Graphical Editing 페이지의 Preferences 대화상자에서 활성화되어 있고, 해당 설계 객체의 Locked 옵션도 활성화되어 있으면, 해당 객체는 선택하거나 그래픽적으로 편집할 수 없습니다. 잠긴 객체를 클릭하여 선택한 후 Locked 속성을 List 패널에서 비활성화하거나 Protect Locked Objects 옵션을 비활성화하여 객체를 그래픽적으로 편집할 수 있습니다.

비그래픽 편집

다음과 같은 비그래픽 편집 방법을 사용할 수 있습니다.

파라미터 대화상자 또는 속성 패널을 통한 편집

Panel page: 시트 심볼 파일 이름 속성이 편집 방법은 관련 Parameter 대화상자와 Properties 패널 모드를 사용하여 시트 심볼 파일 이름 객체의 속성을 수정합니다.

Parameter 대화상자(왼쪽)와 속성 패널의 Parameter 모드(오른쪽)

Parameter 대화상자(왼쪽)와 속성 패널의 Parameter 모드(오른쪽)

배치 후, Parameter 대화상자는 다음 방법으로 접근할 수 있습니다:

-

배치된 시트 심볼 객체를 더블 클릭합니다.

-

시트 심볼 객체 위에 커서를 올리고 마우스 오른쪽 버튼을 클릭한 후, 컨텍스트 메뉴에서 Properties를 선택합니다.

배치 중에는 Parameter 모드의 Properties 패널에 Tab 키를 눌러 접근할 수 있습니다. 시트 심볼이 배치되면 모든 옵션이 나타납니다.

배치 후, Parameter 모드의 Properties 패널은 다음 방법 중 하나로 접근할 수 있습니다:

-

Properties 패널이 이미 활성화되어 있다면, 시트 심볼 객체를 선택합니다.

-

시트 심볼 객체를 선택한 후, 설계 공간 오른쪽 하단의 Properties 패널을 선택하거나 View » Panels » Properties을 선택합니다.

Double Click Runs Interactive Properties 옵션이

회로도 - 그래픽 편집 페이지의

Preferences 대화상자에서 비활성화(기본값)되어 있으면, 프리미티브를 더블 클릭하거나 선택된 프리미티브에서 마우스 오른쪽 버튼을 클릭한 후

Properties를 선택하면 대화상자가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면,

Properties 패널이 열립니다.

대화상자와 패널의 옵션은 동일하지만, 옵션의 순서와 배치가 약간 다를 수 있습니다.

시트 심볼 파일 이름 속성은 배치 모드에 들어가기 전에

회로도 – 기본값 페이지의

Preferences 대화상자에서 접근할 수 있습니다. 이를 통해 시트 심볼 파일 이름 객체의 기본 속성을 변경할 수 있으며, 이후 시트 심볼 파일 이름을 배치할 때 적용됩니다.

여러 객체 편집

Properties 패널은 여러 객체의 속성을 동시에 편집할 수 있도록 지원합니다. 현재 선택된 모든 객체에서 동일한 속성 설정은 수정이 가능합니다. 동일한 객체 유형을 수동으로 선택하거나, Find Similar Objects 대화상자, 또는 Filter나 List 패널을 통해 여러 객체를 선택한 경우, Properties 패널 필드 항목에 별표(*)가 표시되지 않는 항목은 선택된 모든 객체에 대해 편집할 수 있습니다.

리스트 패널을 통한 편집

Panel pages: 리스트 패널, SCH Filter, SCHLIB Filter

List 패널을 사용하면 하나 이상의 문서에서 디자인 객체를 표 형식으로 표시할 수 있어, 객체 속성의 빠른 확인 및 수정이 가능합니다. 적절한 필터링과 함께 사용하면(해당 Filter 패널이나 Find Similar Objects 대화상자를 통해), 활성 필터 범위에 해당하는 객체만 표시할 수 있어, 여러 디자인 객체를 더욱 정확하고 효율적으로 선택 및 편집할 수 있습니다.

Sheet Symbol Filename Properties

회로도 에디터 객체 속성은 배치된 객체의 시각적 스타일, 내용, 동작을 지정하는 옵션입니다. 각 객체 유형의 속성 설정은 두 가지 방식으로 정의됩니다:

-

Pre-placement settings – 대부분의 Sheet Symbol Filename 객체 속성 또는 논리적으로 미리 정의할 수 있는 속성은 Schematic - Defaults 페이지의 Preferences 대화상자(디자인 공간 우측 상단의

버튼에서 접근)에서 기본값으로 편집할 수 있습니다. Primitive List에서 객체를 선택하면 우측에 해당 옵션이 표시됩니다.

버튼에서 접근)에서 기본값으로 편집할 수 있습니다. Primitive List에서 객체를 선택하면 우측에 해당 옵션이 표시됩니다.

-

Post-placement settings – 모든 Sheet Symbol Filename 객체 속성은 디자인 공간에서 Sheet Symbol Filename이 선택된 경우 Parameter 대화상자와 Properties 패널에서 편집할 수 있습니다.

만약

Double Click Runs Interactive Properties 옵션이

Schematic - Graphical Editing 페이지의

Preferences 대화상자에서 비활성화(기본값)되어 있다면, 프리미티브를 더블 클릭하거나 선택된 프리미티브에서 마우스 오른쪽 버튼을 클릭 후

Properties을 선택하면 대화상자가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면

Properties 패널이 열립니다.

대화상자와 패널에서 제공되는 옵션은 동일하지만, 옵션의 순서와 배치가 약간 다를 수 있습니다.

아래 속성 목록에서, Preferences 대화상자에서 기본값으로 제공되지 않는 옵션은 "Properties panel only"로 표시되어 있습니다.

위치 (Properties panel only)

-

Search - Properties 패널 내에서 원하는 텍스트를 검색할 때 이 필드를 사용합니다. 검색된 텍스트는 하이라이트됩니다.

(첫 번째 필드) - 객체 기준점의 현재 X(수평) 좌표로, 현재 디자인 공간 원점을 기준으로 합니다. 값을 수정하여 객체의 X 위치를 변경할 수 있습니다. 값은 미터법 또는 영국식 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 값을 입력할 때는 단위를 함께 입력해야 합니다.

-

Y (두 번째 필드) - 객체 기준점의 현재 Y(수직) 좌표로, 현재 원점을 기준으로 합니다. 값을 수정하여 객체의 Y 위치를 변경할 수 있습니다. 값은 미터법 또는 영국식 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 값을 입력할 때는 단위를 함께 입력해야 합니다.

Rotation - 드롭다운을 사용하여 회전 각도를 선택합니다.

속성

-

Sheet Symbol - 이 객체와 연결된 시트 심볼입니다.

-

Name - 이름을 표시합니다.

-

Value - 실제 파일명 텍스트를 표시합니다.

/

/  을 사용하여 객체의 Value 표시 여부를 결정할 수 있습니다. 자동 위치 지정을 활성화하려면 Autoposition을 체크하세요.

을 사용하여 객체의 Value 표시 여부를 결정할 수 있습니다. 자동 위치 지정을 활성화하려면 Autoposition을 체크하세요.

-

Font - 글꼴, 글꼴 크기, 색상, 굵게, 밑줄 등 특수 설정을 구성할 수 있습니다.

-

Justification - 텍스트의 정렬 방식을 선택합니다.

계층적 설계

계층적 설계의 경우, 프로젝트에는 반드시 하나의 최상위 시트만 존재해야 한다는 점을 기억하는 것이 중요합니다. 다른 모든 소스 문서는 시트 심볼을 통해 참조되어야 합니다. 설계 검증을 수행할 때,

Multiple Top Level Documents violation check를 통해 이 조건이 충족되지 않은 경우를 확인할 수 있습니다. 또한, 어떤 시트 심볼도 자신이 위치한 시트나 그보다 상위 시트를 참조해서는 안 됩니다. 그렇지 않으면 구조상 해결할 수 없는 루프가 발생합니다.

계층적 설계란 트리 구조 또는 시트 간 관계가 설계 내에서 표현되는 구조를 의미합니다. 이는 시트 심볼을 통해 구현되며, 시트 심볼은 설계 계층 내 하위 시트를 나타냅니다. 심볼은 하위 시트를 나타내고, 그 안의 시트 엔트리는 하위 시트의 포트와 연결(또는 대응)됩니다. 연결은 시트 심볼 내의 Sheet Entries를 통해 이루어지며, 한 시트의 포트에서 다른 시트의 포트로 직접 연결되는 것이 아닙니다.

플랫 설계와 마찬가지로, 하위 시트는 시트 심볼에 파일명을 지정하여 식별합니다. 계층적 설계에서는 하위 시트에도 시트 심볼을 포함시켜 더 하위 시트를 참조할 수 있으므로, 계층 구조에 또 다른 레벨이 추가됩니다. 아래 이미지는 3단계 계층 구조를 가진 계층적 설계 예시입니다.

계층적 설계에서 트리 구조는 시트 심볼로 생성된 상위-하위 관계에 의해 결정됩니다.

계층적 설계에서 하위 시트의 신호는 포트를 통해 시트를 빠져나와 상위 시트의 대응 Sheet Entry로 연결됩니다. 상위 시트에는 하위 신호를 다른 시트 심볼의 Sheet Entry로 전달하는 배선이 포함되어 있으며, 이후 두 번째 하위 시트의 대응 포트로 신호가 전달됩니다(아래 이미지 참조).

이러한 상위-하위 시트 구조는 원하는 깊이까지 정의할 수 있으며, 계층적 설계 내 시트의 개수에도 제한이 없습니다.

시트 간 연결성은 Net Identifier Scope에 의해 결정됩니다. 이는 Options 탭의 Options for Project 대화상자에서 설정할 수 있습니다. 연결성 생성에 대해 더 자세히 알고 싶다면 Creating Connectivity 페이지를 참고하세요. Net Identifier Scope에는 Automatic 옵션이 포함되어 있으며, 특별한 연결 요구가 없다면 이 옵션을 사용하는 것이 좋습니다.

계층적 설계의 장점은 설계의 구조를 명확하게 보여주며, 연결성이 항상 하위 시트에서 상위 시트의 시트 심볼로 이어지기 때문에 예측 가능하고 추적이 쉽다는 점입니다.

계층적 설계의 또 다른 장점은 고급 설계 재사용 시스템을 제공할 수 있는 기반을 마련한다는 것입니다. 이 시스템은 데이터 저장 방식에 따라 파일 기반 또는 서버 기반으로 제공됩니다.

-

파일 기반 시스템은 Device Sheets라고 하며, Device Sheets 라이브러리에 있는 기존 회로도를 생성 중인 설계에 직접 배치하는 방식입니다. Device Sheets에 대해 더 자세히 알아보려면 Device Sheets 사용하기 페이지를 참고하세요.

-

Workspace 기반 시스템은 Managed Schematic Sheets라고 하며, 연결된 Workspace에 있는 기존 회로도를 생성 중인 설계에 직접 배치하는 방식입니다. Managed Sheets에 대해 더 자세히 알아보려면 Managed Schematic Sheets 사용하기 페이지를 참고하세요.

Port

배치된 Port

배치된 Port

요약

포트(Port)는 전기 설계 프리미티브입니다. 여러 시트(플랫 및 계층적 설계 모두)를 사용하는 설계에서 한 회로도 시트와 다른 시트 또는 시트 심볼(해당 시트 엔트리를 통해) 간에 전기적 연결을 할 때 사용됩니다. 포트의 이름이 연결을 정의하며(즉, 한 회로도 시트의 포트는 프로젝트 내 다른 시트에 동일한 이름을 가진 포트 또는 시트 엔트리와 연결됩니다).

교차 참조 기능은 상호 연결된

포트의 위치와 상호 연결된 오프 시트 커넥터의 위치 그리드 참조를 식별합니다. 두 가지 유형의 회로도 연결 객체 모두에 대해, 기존

Reports » Port Cross Reference » Add To Project 명령은 대상 시트 이름과 위치 그리드 참조를 기반으로 교차 참조 파라미터를 추가합니다.

사용 가능 위치

포트는 Schematic Editor에서 다음과 같은 방법으로 배치할 수 있습니다:

-

메인 메뉴에서 Place » Port을 클릭합니다.

-

디자인 공간 상단에 위치한 Active Bar의 지시문 드롭다운에서 포트 버튼(

)을 클릭합니다. (Active Bar 버튼을 클릭한 채로 누르면 다른 관련 명령에 접근할 수 있습니다. 한 번 명령을 사용하면 해당 명령이 Active Bar의 해당 섹션에서 최상단에 표시됩니다.)

)을 클릭합니다. (Active Bar 버튼을 클릭한 채로 누르면 다른 관련 명령에 접근할 수 있습니다. 한 번 명령을 사용하면 해당 명령이 Active Bar의 해당 섹션에서 최상단에 표시됩니다.)

-

마우스 오른쪽 버튼을 클릭한 후 Place » Port을 선택합니다.

배치

명령을 실행하면 커서가 십자선으로 바뀌고 포트 배치 모드로 진입합니다. 배치는 다음 순서로 진행합니다:

-

포트의 왼쪽 끝을 고정하려면 클릭하거나 Enter를 누릅니다.

-

커서를 이동하여 포트의 길이를 조정한 후, 클릭하거나 Enter를 눌러 포트 배치를 완료합니다.

-

추가 포트를 계속 배치하거나, 마우스 오른쪽 버튼을 클릭하거나 Esc를 눌러 배치 모드를 종료합니다.

포트가 커서에 떠 있는 상태에서(왼쪽 끝이 고정되기 전) 배치 중에 수행할 수 있는 추가 동작은 다음과 같습니다:

-

Tab 키를 눌러 배치를 일시 중지하고 Port 모드의 Properties 패널에 접근하여 속성을 즉시 변경할 수 있습니다. 디자인 공간의 일시정지 버튼 오버레이(

)를 클릭하면 배치가 재개됩니다.

)를 클릭하면 배치가 재개됩니다.

-

Spacebar를 눌러 포트를 반시계 방향으로, Shift+Spacebar를 눌러 시계 방향으로 회전할 수 있습니다. 회전은 90° 단위로 이루어집니다.

-

X 또는 Y 키를 눌러 포트를 X축 또는 Y축 기준으로 미러링할 수 있습니다.

배치 중 속성을 수정할 수 있지만(Tab을 눌러 관련 Properties 패널에 접근), 이 경우 이후 배치에도 해당 설정이 기본값으로 적용됩니다. 단, Permanent 옵션이 Schematic – Defaults 페이지의 Preferences 대화상자에서 활성화되어 있으면, 변경 사항은 현재 배치 중인 객체와 동일 세션 내에서 추가로 배치되는 객체에만 적용됩니다.

그래픽 편집

이 편집 방법은 디자인 공간에서 배치된 포트 객체를 선택한 후, 길이, 높이, 위치를 그래픽적으로 변경할 수 있습니다.

포트 객체를 선택하면, 편집 핸들을 클릭하고 드래그하여 포트의 크기를 조절할 수 있습니다.

선택된 Port

선택된 Port

편집 핸들 이외의 포트 영역을 클릭한 후 드래그하여 위치를 이동할 수 있습니다. 드래그 중에는 포트를 회전(Spacebar/Shift+Spacebar)하거나, X축 또는 Y축 기준으로 미러링(X 또는 Y 키)할 수 있습니다.

포트 객체의 이름은 다음과 같이 in-place 편집할 수 있습니다:

-

포트를 한 번 클릭하여 선택합니다.

-

다시 한 번 클릭(또는 Enter을 누름)하여 인플레이스 편집 모드로 진입합니다. 두 번 클릭으로 인식되지 않도록 각 클릭 사이에 충분한 시간을 두어야 하며, 두 번 클릭 시 Properties 패널이 열릴 수 있습니다.

-

인플레이스 텍스트 편집을 마치려면 Enter을 누르거나 마우스로 포트 외부를 클릭합니다.

-

포트의 이름 길이/높이에 맞게 포트 크기가 자동으로 조정됩니다.

Locked 속성이 활성화된 객체를 그래픽적으로 수정하려고 하면, 편집 진행 여부를 묻는 대화상자가 나타납니다. Protect Locked Objects 옵션이 Schematic – Graphical Editing 페이지의 Preferences 대화상자에서 활성화되어 있고, 해당 설계 객체에 대한 Locked 옵션도 활성화되어 있다면, 해당 객체는 선택하거나 그래픽적으로 편집할 수 없습니다. 잠긴 객체를 클릭하여 선택한 후, Locked 속성을 List 패널에서 비활성화하거나 Protect Locked Objects 옵션을 비활성화하여 그래픽 편집이 가능합니다.

비그래픽 편집

다음과 같은 비그래픽 편집 방법이 제공됩니다.

Port 대화상자 또는 속성 패널을 통한 편집

Properties page: Port 속성

이 편집 방법은 관련 Port 대화상자와 Properties패널 모드를 사용하여 포트 객체의 속성을 수정합니다.

Port 대화상자(왼쪽)와 속성 패널의 Port 모드(오른쪽)

Port 대화상자(왼쪽)와 속성 패널의 Port 모드(오른쪽)

배치 후, Port 대화상자는 다음 방법으로 접근할 수 있습니다:

-

배치된 포트 객체를 더블 클릭합니다.

-

포트 객체 위에 커서를 올리고 마우스 오른쪽 버튼을 클릭한 후, 컨텍스트 메뉴에서 Properties을 선택합니다.

배치 중에는 Port 모드의 Properties 패널에 Tab 키를 눌러 접근할 수 있습니다. 포트가 배치되면 모든 옵션이 표시됩니다.

배치 후, Port 모드의 Properties 패널은 다음 방법 중 하나로 접근할 수 있습니다:

-

Properties 패널이 이미 활성화되어 있다면, 포트 객체를 선택합니다.

-

포트 객체를 선택한 후, 디자인 공간 우측 하단의 Properties 패널을 Panels 버튼에서 선택하거나, 메인 메뉴에서 View » Panels » Properties을 선택합니다.

Double Click Runs Interactive Properties 옵션이

Schematic - Graphical Editing 페이지의

Preferences 대화상자에서 비활성화(기본값)되어 있으면, 프리미티브를 더블 클릭하거나 선택된 프리미티브에서 마우스 오른쪽 버튼을 클릭한 후

Properties을(를) 선택하면 대화상자가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면

Properties 패널이 열립니다.

대화상자와 패널에서 제공되는 옵션은 동일하지만, 옵션의 순서와 배치가 약간 다를 수 있습니다.

포트 속성은 배치 모드에 들어가기 전에

Schematic – Defaults 페이지의

Preferences 대화상자에서 접근할 수 있습니다. 이를 통해 포트 객체의 기본 속성을 변경할 수 있으며, 이후 포트를 배치할 때 변경된 기본 속성이 적용됩니다.

여러 객체 편집

Properties 패널은 여러 객체 편집을 지원하며, 현재 선택된 모든 객체에서 동일한 속성 설정을 수정할 수 있습니다. 동일한 객체 유형을 수동으로 여러 개 선택하거나, Find Similar Objects 대화상자 또는 SCH Filter나 SCH List 패널을 통해 선택한 경우, Properties 패널 필드 항목이 별표(*)로 표시되지 않으면 선택된 모든 객체에 대해 편집할 수 있습니다.

리스트 패널을 통한 편집

Panel pages: 리스트 패널, SCH Filter

List 패널을 사용하면 하나 이상의 문서에서 디자인 객체를 표 형식으로 표시하여 객체 속성을 빠르게 확인하고 수정할 수 있습니다. 적절한 필터링과 함께 사용하면(해당 Filter 패널 또는 Find Similar Objects 대화상자 사용) 활성 필터 범위에 해당하는 객체만 표시할 수 있어, 여러 디자인 객체를 더욱 정확하고 효율적으로 선택 및 편집할 수 있습니다.

포트 동작

배치된 포트에서 마우스 오른쪽 버튼을 클릭하면 상황에 맞는 메뉴가 나타나며, 해당 포트(또는 여러 포트가 선택된 경우 모든 포트)에 대해 다음 명령을 사용할 수 있습니다(Port Actions 하위 메뉴에서):

-

Jump to Sheet Entry <PortName> - 포트가 위치한 하위 시트를 참조하는 상위 시트 심볼의 해당 시트 항목으로 이동할 때 사용합니다.

-

Toggle Port IO Type - 포트의 I/O 타입을 전환할 때 사용합니다.

실제 변경 내용은 현재 I/O 타입에 따라 다음과 같습니다:

-

Unspecified 는 Unspecified로 유지됩니다.

-

Output 는 Input로 변경됩니다.

-

Input 는 Output로 변경됩니다.

-

Bidirectional 는 Bidirectional로 유지됩니다.

여러 포트가 선택된 경우, 명령은 Toggle Selected Ports IO Type로 표시됩니다. 이 명령은 선택된 모든 포트에 적용됩니다.

-

Place Harness Connector of Type <HarnessConnectorType> - 포트에 연결할 하니스 커넥터(정의된 하니스 엔트리 포함)를 배치할 때 사용합니다.

이 명령은 Harness Type가 정의된 포트에만 사용할 수 있습니다.

-

Jump to Port <PortName> on <SheetName> - 지정된 소스 회로도 문서에서 동일한 이름을 가진 다른 포트로 이동할 때 사용합니다.

참고

-

포트와 시트 심볼 간의 관계는 프로젝트에 대해 선택된 Net Identifier Scope에 의해 결정됩니다. 이 범위는 Net Identifier Scope 옵션을 Project Options - Options 대화상자(Project » Project Options)에서 설정하여 정의합니다.

-

Flat 또는 Global로 설정된 경우, 동일하거나 다른 회로도 문서 내에서 동일한 이름을 가진 모든 포트는 전기적으로 연결된 것으로 간주됩니다.

-

Hierarchical 또는 Strict Hierarchical로 설정된 경우, 포트는 해당 시트 엔트리와 수직으로만 연결됩니다. 동일한 이름의 다른 포트와 수평으로는 연결되지 않습니다.

-

I/O Type 옵션은 Properties 패널에서 포트의 전기적 타입을 정의할 수 있습니다. Input, Output, Bidirectional, Unspecified 중에서 선택할 수 있습니다. Port Direction 옵션이 Schematic – General 페이지의 Preferences 대화상자에서 활성화되어 있으면, 포트는 자동으로 I/O 타입을 표시합니다.

-

포트 이름에 바(bar)를 추가(이름 위에 선을 표시)하려면 다음 방법 중 하나를 사용하세요:

-

기본적으로 포트 이름은 넷 이름으로 사용되지 않습니다. 포트가 넷 이름으로 사용되길 원한다면, Allow Ports to Name Nets 옵션을 Options 탭의 Options for Project 대화상자에서 활성화하세요. 이 옵션이 비활성화되어 있으면, 해당 넷에 넷 라벨이나 파워 객체가 없거나, 계층적 설계에서 Allow Sheet Entries to Name Nets 옵션이 활성화되어 있지 않은 경우 시스템에서 생성한 넷 이름이 사용됩니다. 자세한 내용은 How Nets are Named을(를) 참고하세요.

-

포트는 이름의 길이나 높이에 맞게 자동으로 크기가 조정됩니다. 자동 크기 조정은 Port 모드의 Properties패널을 사용하거나 디자인 공간에서 직접 인플레이스 편집을 통해 텍스트를 입력하는 경우 모두 적용됩니다.

-

포트가 Signal Harness에 연결되면, 포트는 하니스 객체로 변환됩니다. 기본적으로 포트의 색상은 Signal Harness의 색상과 일치하도록 변경됩니다.

-

포트가 Signal Harness를 통해 Harness Connector에 연결되면, Harness Type는 Properties 패널에서 해당 Harness Connector의 Harness Type으로 자동으로 채워집니다. 포트가 Signal Harness를 통해 Sheet Entry에 연결되고, Sheet Entry에 Harness Type이 선언되어 있으면, 포트는 하니스 객체로 변환되어 Signal Harness의 색상으로 변경됩니다. 포트를 Harness Connector나 Sheet Entry에서 이동시키면, 포트는 기본 색상으로 되돌아갑니다.

-

기본적으로 포트의 Name에 사용되는 글꼴은 Document Font 옵션에서 설정한 전역 문서 수준의 글꼴을 따릅니다(Document Options모드의 Properties 패널에서 작업 공간에 선택된 객체가 없을 때). 이는 개별 포트 수준에서 Font 설정을 Properties 패널에서 변경하여 오버라이드할 수 있으므로, 필요에 따라 포트의 텍스트 표현을 완전히 제어할 수 있습니다.

-

OrCAD 디자인을 Import Wizard을(를) 사용하여 가져올 때, 생성된 회로도 문서에서 커스텀 포트 커넥터가 지원됩니다. 이러한 포트는 원본 디자인과 동일한 그래픽을 가집니다. 자세한 내용은 OrCAD에서 디자인 가져오기를 참조하세요.

-

xDX Designer 디자인을 Import Wizard을(를) 사용하여 가져올 때, 생성된 회로도 문서에서 커스텀 포트가 지원됩니다. 이러한 포트는 원본 디자인과 동일한 그래픽을 가집니다. 자세한 내용은 xDX Designer 또는 DxDesigner에서 디자인 가져오기를 참조하세요.

이 기능은 오픈 베타 상태이며, Importer.UseCustomConnectors 옵션이 고급 설정 대화상자에서 활성화되어 있을 때 사용할 수 있습니다.

Port Properties

회로도 에디터 객체 속성은 배치된 객체의 시각적 스타일, 내용 및 동작을 지정하는 정의 가능한 옵션입니다. 각 객체 유형의 속성 설정은 두 가지 방법으로 정의됩니다:

-

Pre-placement settings – 대부분의 Port 객체 속성 또는 논리적으로 미리 정의할 수 있는 속성은 Schematic - Defaults 페이지의 Preferences 대화상자(디자인 공간 우측 상단의

버튼에서 접근)에서 편집 가능한 기본 설정으로 제공됩니다. 객체를 Primitive List 에서 선택하면 우측에 해당 옵션이 표시됩니다.

버튼에서 접근)에서 편집 가능한 기본 설정으로 제공됩니다. 객체를 Primitive List 에서 선택하면 우측에 해당 옵션이 표시됩니다.

-

Post-placement settings – 모든 Port 객체 속성은 디자인 공간에서 배치된 Port를 선택했을 때 Port 대화상자와 Properties패널에서 편집할 수 있습니다.

Double Click Runs Interactive Properties 옵션이

Schematic - Graphical Editing 페이지의

Preferences 대화상자에서 비활성화(기본값)되어 있으면, 프리미티브를 더블 클릭하거나 선택된 프리미티브에서 마우스 오른쪽 버튼을 클릭한 후

Properties을(를) 선택하면 대화상자가 열립니다.

Double Click Runs Interactive Properties 옵션이 활성화되어 있으면

Properties 패널이 열립니다.

대화상자와 패널에서 제공되는 옵션은 동일하지만, 옵션의 순서와 배치가 약간 다를 수 있습니다.

아래 속성 목록에서, Preferences 대화상자에서 기본 설정으로 제공되지 않는 옵션은 "Properties 패널 전용"으로 표시되어 있습니다.

일반 탭

위치 (Properties 패널 전용)

-

(X/Y)

-

X (첫 번째 필드) - 객체 기준점의 현재 X(수평) 좌표로, 현재 디자인 공간 원점 기준입니다. 값을 편집하여 객체의 X 위치를 변경할 수 있습니다. 값은 미터법 또는 영국식 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 값을 입력할 때는 단위를 함께 입력하세요.

-

Y (두 번째 필드) - 객체 기준점의 현재 Y(수직) 좌표로, 현재 원점 기준입니다. 값을 편집하여 객체의 Y 위치를 변경할 수 있습니다. 값은 미터법 또는 영국식 단위로 입력할 수 있으며, 현재 기본 단위가 아닌 값을 입력할 때는 단위를 함께 입력하세요.

속성

-

Name - 포트의 이름입니다.

-

I/O Type - 포트의 전기적 특성을 정의합니다. 드롭다운 목록에서 옵션을 선택하세요.

이 설정은 회로의 연결성에는 영향을 주지 않지만, 전기 규칙 검사 실행 시 고려되어, 호환되지 않는 포트 방향을 감지하도록 설정할 수 있습니다.

-

Harness Type - 드롭다운을 사용하여 하니스 유형을 선택하세요.

-

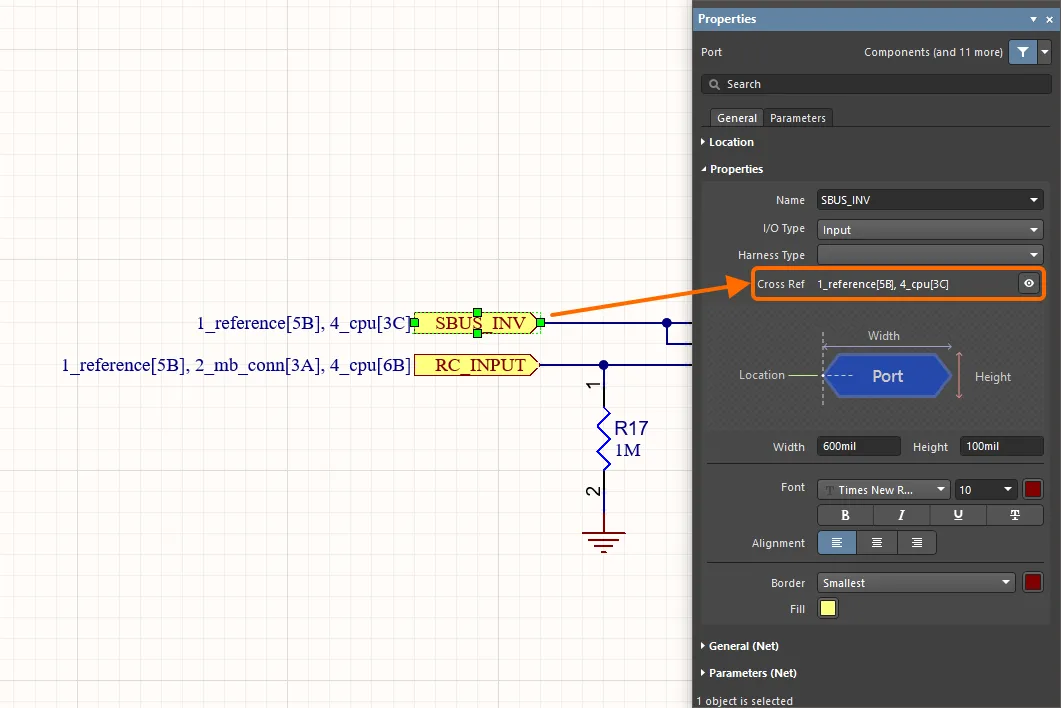

Cross Ref - 이 필드는 포트에 적용된 교차 참조 값을 표시합니다.

-

Width - 편집할 수 있습니다.

-

Height - 편집할 수 있습니다.

-

Font - 원하는 경우, 컨트롤을 사용하여 글꼴, 글꼴 크기, 색상, 굵게, 이탤릭 등 속성을 선택하세요.

-

Alignment - 원하는 정렬 설정을 클릭하세요.

-

Border - 드롭다운을 사용하여 사용 가능한 선택지 중 기본값을 선택하세요. 색상 상자를 클릭하면 드롭다운이 열리며, 여기서 기본 색상을 선택할 수 있습니다.

-

Fill - 색상 상자를 클릭하면 드롭다운이 열리며, 여기서 기본 색상을 선택할 수 있습니다.

일반(네트)

포트에 할당된 네트의 속성을 표시합니다. 필요에 따라 업데이트하세요.

Power Net 및 High Speed 필드는 지시문이 객체에 추가된 후에 사용할 수 있습니다.

파라미터(네트)

-

Selection buttons - 그리드에 표시할 원하는 객체를 클릭하세요.

-

Add - 드롭다운을 사용하여 원하는 객체를 추가한 후 값을 정의하세요.

Add 버튼은 지시문이 객체에 추가된 후에 사용할 수 있습니다.

파라미터 탭

파라미터

이 영역에서는 현재 선택된 포트 객체에 첨부된 파라미터를 관리할 수 있습니다.

-

Grid - 현재 포트에 정의된 Name 및 Value 파라미터를 나열합니다. 필요에 따라 필드를 직접 편집할 수 있습니다.

및

및  을(를) 사용하여 파라미터를 표시/숨김 처리할 수 있습니다. 자물쇠 아이콘을 사용하여 선택한 파라미터를 잠그거나 잠금 해제할 수 있습니다.

을(를) 사용하여 파라미터를 표시/숨김 처리할 수 있습니다. 자물쇠 아이콘을 사용하여 선택한 파라미터를 잠그거나 잠금 해제할 수 있습니다.

-

Font Settings - 클릭하여 글꼴을 정의하는 메뉴를 엽니다.

-

Other - 클릭하여 추가 옵션을 변경할 수 있는 드롭다운을 엽니다:

-

Show Parameter Name - 활성화하면 파라미터 이름이 표시됩니다.

-

Allow Synchronization with Database - 활성화하면 데이터베이스와 동기화됩니다.

-

X/Y - X 및 Y 좌표를 입력하세요.

-

Rotation - 드롭다운을 사용하여 회전값을 선택하세요.

-

Autoposition - 자동 위치 지정을 활성화하려면 체크하세요.

-

Add - 클릭하여 파라미터를 추가하세요.

를 사용하여 테이블에서 선택한 항목을 삭제할 수 있습니다.

를 사용하여 테이블에서 선택한 항목을 삭제할 수 있습니다.

교차 참조 기능은 상호 연결된

포트 및 시트 외부 커넥터의 위치 그리드 참조를 식별합니다. 두 가지 유형의 회로도 연결 객체 모두에 대해, 기존

Reports » Port Cross Reference » Add To Project 명령은 대상 시트 이름과 위치 그리드 참조를 기반으로 교차 참조 파라미터를 추가합니다.

Sheet Entry

배치된 시트 엔트리

요약

시트 엔트리는 시트 심볼 내에 속하는 전기적 설계 프리미티브입니다. 시트 심볼 내에 배치되어 해당 심볼의 입력/출력 포트를 지정합니다. 시트 엔트리는 심볼이 나타내는 소스 회로도 하위 시트에 배치된 포트와 대응됩니다.

사용 가능 여부

시트 엔트리는 Schematic Editor에서 다음과 같은 방법으로만 배치할 수 있습니다:

-

메인 메뉴에서 Place » Sheet Entry을(를) 선택하세요.

- Sheet Entry 버튼(

)을 디자인 공간 상단에 위치한 Active Bar의 그래픽 오브젝트 드롭다운에서 클릭하세요. (Active Bar 버튼을 클릭한 채로 누르고 있으면 관련된 다른 명령을 사용할 수 있습니다. 한 번 명령을 사용하면 해당 명령이 Active Bar의 해당 섹션에서 가장 위에 표시됩니다.)

)을 디자인 공간 상단에 위치한 Active Bar의 그래픽 오브젝트 드롭다운에서 클릭하세요. (Active Bar 버튼을 클릭한 채로 누르고 있으면 관련된 다른 명령을 사용할 수 있습니다. 한 번 명령을 사용하면 해당 명령이 Active Bar의 해당 섹션에서 가장 위에 표시됩니다.)

-

디자인 공간에서 마우스 오른쪽 버튼을 클릭한 후, 컨텍스트 메뉴에서 Place » Sheet Entry을 선택하세요.

-

버튼을 Wiring 툴바에서 클릭하세요.

버튼을 Wiring 툴바에서 클릭하세요.

배치

명령을 실행하면 커서가 십자선 모양으로 바뀌고 시트 엔트리 배치 모드로 진입합니다. 배치는 다음 순서로 진행합니다:

-

커서에 연결된 시트 엔트리를 시트에 배치된 시트 심볼 위로 이동합니다.

-

시트 엔트리의 위치를 시트 심볼의 가장자리와 맞추어 조정한 후, 클릭하거나 Enter 키를 눌러 시트 엔트리를 원하는 가장자리에 고정하고 배치를 완료합니다.

-

계속해서 추가 시트 엔트리를 배치하거나, 마우스 오른쪽 버튼을 클릭하거나 Esc 키를 눌러 배치 모드를 종료합니다.

시트 엔트리의 색상은 올바른 배치에 도움이 됩니다. 시트 심볼 외부에 있을 때는 엔트리가 회색으로 표시되어 배치가 불가능합니다. 시트 심볼 위에 있을 때는 파란색으로 변하며, 해당 위치에 배치할 수 있음을 나타냅니다. 배치가 완료되면, 엔트리는

Fill Color 속성에 따라

Properties panel에서 정의된 실제 색상으로 돌아갑니다.

배치 중에도 속성을 수정할 수 있습니다(

Tab를 눌러

Properties 패널에 접근). 단,

Permanent 옵션이

Schematic – Defaults page의

Preferences 대화상자에서 활성화되어 있지 않으면, 수정한 값이 이후 배치의 기본값으로 적용됩니다. 이 옵션이 활성화되어 있으면, 변경 사항은 현재 배치 중인 오브젝트와 같은 배치 세션에서 추가로 배치되는 오브젝트에만 적용됩니다.

그래픽 편집

이 편집 방법은 디자인 공간에서 배치된 시트 엔트리 오브젝트를 직접 선택하여 위치를 그래픽적으로 변경할 수 있습니다.

시트 엔트리는 I/O Type을 Properties 패널에서 변경하여 모양만 조정할 수 있습니다. 따라서 시트 엔트리 오브젝트를 선택해도 편집 핸들은 제공되지 않습니다.

선택된 시트 엔트리

-

시트 엔트리를 클릭하고 드래그하여 상위 시트 심볼 내에서 원하는 위치로 이동할 수 있습니다.

-

Ctrl 키를 누른 상태에서 시트 엔트리를 클릭하고 드래그하면, 현재 시트 심볼에서 다른 시트 심볼로 이동할 수 있습니다. 시트 엔트리가 원본 시트 심볼의 경계를 벗어나면 Ctrl 키를 놓을 수 있습니다.

-

시트 엔트리를 시트 심볼 경계 밖으로 클릭하여 드래그하면, 시트 심볼이 자동으로 크기가 조정되어 엔트리의 새로운 위치를 수용합니다.

여러 개의 시트 엔트리를 동시에 이동하려면, Ctrl 키를 누른 채로 이동할 엔트리들을 모두 선택한 후, 선택된 엔트리 중 하나를 클릭하여 전체를 드래그하세요. 드래그를 시작하면 Ctrl 키를 놓을 수 있습니다. Shift 키를 누른 채로 여러 오브젝트를 선택할 수 있습니다.

Enable In-Place Editing 옵션이

Schematic – General page의

Preferences 대화상자에서 활성화되어 있다면, 디자인 공간에서 시트 엔트리의 이름을 직접 편집할 수 있습니다. 시트 엔트리 오브젝트를 선택한 후 한 번 클릭하면 이름 편집 기능이 활성화됩니다. 원하는 이름을 입력한 후, 시트 엔트리 오브젝트 밖을 클릭하거나

Enter 키를 눌러 변경을 적용하세요.

Locked 속성이 활성화된 오브젝트를 그래픽적으로 수정하려고 하면, 편집을 계속할지 확인하는 대화상자가 나타납니다. Protect Locked Objects 옵션이 Schematic – Graphical Editing 페이지의 Preferences 대화상자에서 활성화되어 있고, 해당 디자인 오브젝트의 Locked 옵션도 활성화되어 있다면, 해당 오브젝트는 선택하거나 그래픽적으로 편집할 수 없습니다. 잠긴 오브젝트를 클릭하여 선택한 후, Locked 속성을 List 패널에서 비활성화하거나 Protect Locked Objects 옵션을 비활성화하여 그래픽 편집이 가능하도록 하세요.

비그래픽 편집

다음과 같은 비그래픽 편집 방법을 사용할 수 있습니다.

시트 엔트리 대화상자 또는 속성 패널을 통한 편집

Properties page: Sheet Entry Properties이 편집 방법은 관련 Sheet Entry 대화상자와 Properties 패널 모드를 사용하여 시트 엔트리 오브젝트의 속성을 수정합니다.

Sheet Entry 모드의 Properties (첫 번째 이미지) 패널과 Sheet Entry 대화상자(두 번째 이미지)

배치 후, Sheet Entry 대화상자는 다음 방법으로 접근할 수 있습니다:

-

배치된 시트 엔트리 오브젝트를 더블 클릭합니다.

-

시트 엔트리 오브젝트 위에 커서를 올리고 마우스 오른쪽 버튼을 클릭한 후, 컨텍스트 메뉴에서 Properties를 선택합니다.

배치 중에는 Properties 패널의 Sheet Entry 모드에 Tab 키를 눌러 접근할 수 있습니다. 시트 엔트리가 배치되면 모든 옵션이 표시됩니다.

배치 후, Properties 패널의 Sheet Entry 모드는 다음 방법 중 하나로 접근할 수 있습니다:

-

Properties 패널이 이미 활성화되어 있다면, 시트 엔트리 오브젝트를 선택합니다.

-

시트 엔트리 오브젝트를 선택한 후, 디자인 공간 우측 하단의 Panels 버튼에서 Properties 패널을 선택하거나 View » Panels » Properties을 선택합니다.

Double Click Runs Interactive Properties 옵션이

Schematic – Graphical Editing page의

Preferences 대화상자에서 기본값(활성화)으로 설정되어 있으면, 프리미티브를 더블 클릭하거나 선택된 프리미티브에서 마우스 오른쪽 버튼을 클릭 후

Properties을 선택하면

Properties 패널이 열립니다.

Double Click Runs Interactive Properties 옵션이 비활성화되어 있으면, 대화상자가 열립니다.

대화상자와 패널에서 제공되는 옵션은 동일하지만, 옵션의 순서와 배치가 약간 다를 수 있습니다.

시트 엔트리 속성은 배치 모드에 진입하기 전에

Schematic – Defaults page의

Preferences 대화상자에서 접근할 수 있습니다. 이를 통해 시트 엔트리 오브젝트의 기본 속성을 변경할 수 있으며, 이후 배치되는 시트 엔트리에 적용됩니다.

여러 오브젝트 편집

Properties 패널은 여러 오브젝트 동시 편집을 지원합니다. 현재 선택된 모든 오브젝트에서 동일한 속성 값은 수정이 가능합니다. 동일한 오브젝트 유형을 수동으로 여러 개 선택하거나, Find Similar Objects 대화상자, Filter 또는 List 패널을 통해 선택한 경우, Properties 패널 필드 항목이 별표(*)로 표시되지 않으면 선택된 모든 오브젝트에 대해 수정할 수 있습니다.

목록 패널을 통한 편집

Panel pages: 목록 패널, SCH 필터

A List 패널을 사용하면 하나 이상의 문서에서 설계 객체를 표 형식으로 표시할 수 있어 객체 속성을 빠르게 확인하고 수정할 수 있습니다. 적절한 필터링과 함께 사용하면 – 해당 Filter 패널이나 유사 객체 찾기 대화상자를 통해 – 활성 필터 범위에 해당하는 객체만 표시할 수 있으므로, 여러 설계 객체를 더욱 정확하고 효율적으로 선택 및 편집할 수 있습니다.

시트 엔트리 우클릭 작업

배치된 시트 엔트리에서 마우스 오른쪽 버튼을 클릭하면 상황에 맞는 메뉴가 나타나며, 해당 시트 엔트리(또는 현재 선택된 모든 시트 엔트리, 해당되는 경우)에 대해 다음 명령을 사용할 수 있습니다(Sheet Entry Actions 하위 메뉴에서):

-

Toggle Selected Sheet Entries IO Type – 이 명령을 사용하여 시트 엔트리의 I/O 타입을 전환할 수 있습니다. 이 명령은 Toggle Selected Sheet Entries IO Type을(를) 클릭하거나 Edit » Move 메인 메뉴 및 Active Bar에서도 사용할 수 있습니다.

시트 엔트리 IO 타입 전환 예시

실제 변경 내용은 현재 I/O 타입에 따라 다음과 같습니다:

-

Unspecified은(는) Unspecified로 유지됩니다.

-

Output은(는) Input로 변경됩니다.

-

Input은(는) Output로 변경됩니다.

-

Bidirectional은(는) Bidirectional로 유지됩니다.

-

Swap Selected Sheet Entries Side – 시트 엔트리를 상위 시트 심볼의 반대편으로 이동할 때 사용합니다. 이때 시트 엔트리의 I/O 타입은 변경되지 않습니다. 이 명령은 메인 메뉴의 Edit » Move » Swap Selected Sheet Entries Side 또는 Active Bar에서도 사용할 수 있습니다.

시트 엔트리 위치 전환 예시.

참고

-

시트 엔트리가 신호 하니스에 연결되면, 시트 엔트리는 하니스 객체가 됩니다. 기본적으로 시트 엔트리는 신호 하니스의 색상과 일치하도록 색상이 변경됩니다. 시트 엔트리의 색상을 직접 지정하거나 기본 색상을 사용하려면 Sheet Entries and Ports use Harness Color 옵션을 Schematic – Graphical Editing 페이지의 Preferences 대화상자에서 비활성화하세요.

-

시트 엔트리가 신호 하니스를 통해 하니스 커넥터에 연결되면, Harness Type가 Properties 패널에 자동으로 하니스 커넥터의 하니스 타입으로 채워집니다. 시트 엔트리가 신호 하니스를 통해 포트에 연결되고, 해당 포트에 Harness Type이(가) 선언되어 있으면, 시트 엔트리는 하니스 객체가 되어 신호 하니스의 색상으로 변경됩니다. 시트 엔트리를 하니스 커넥터에서 분리하고 Harness Type 필드가 비어 있으면, 시트 엔트리는 기본 색상으로 되돌아갑니다.

-

시트 엔트리 이름에 부정(상단에 바 표시)을 추가해야 하는 경우, 다음 방법 중 하나를 사용하세요:

-

핀 이름의 각 문자 뒤에 역슬래시 문자를 포함하세요(예:

E\N\A\B\L\E\).

-

Single '\' Negation 옵션을 Schematic – Graphical Editing 페이지의 Preferences 대화상자에서 활성화한 후, 핀 이름 앞에 역슬래시 한 개를 추가하세요(예:

\ENABLE).

-

기본 설정은 시트 엔트리 이름이 넷(nets)의 이름으로 사용되는 것입니다. 이 동작은 Allow Sheet Entries to Name Nets 옵션(Options 탭, Options for Project 대화상자)에서 제어됩니다. 이 옵션이 비활성화되어 있으면, 해당 넷에 넷 라벨이나 전원 객체가 없거나, 계층적 설계에서 Allow Ports to Name Nets 옵션이 활성화되어 있지 않은 경우 시스템에서 생성한 넷 이름이 사용됩니다. 넷 이름 지정 방법에 대해 자세히 알아보세요.

-

동일한 시트 심볼에서 여러 채널을 인스턴스화할 때, 특정 신호가 반복되어 각 인스턴스 채널로 개별적으로 전송됩니다. 시트 엔트리의 경우, 이름에 Repeat 키워드를 사용하여 신호를 반복합니다(예:

Repeat(Headphone)). 그런 다음 시트 엔트리를 버스에 연결하면, 버스가 개별 신호를 각 인스턴스 목적지로 전달합니다.

-

시트 엔트리에서 하위 시트의 해당 포트로 빠르게 이동하려면, Ctrl+Click 시트 엔트리 객체를 사용하세요. 회로도 PDF 출력물에서는 시트 엔트리를 클릭하면 하위 회로도 페이지의 포트로 이동할 수 있습니다.

Sheet Entry Properties

회로도 에디터 객체 속성은 배치된 객체의 시각적 스타일, 내용 및 동작을 지정하는 옵션입니다. 각 객체 유형의 속성 설정은 두 가지 방식으로 정의됩니다:

-

Pre-placement settings – 대부분의 시트 엔트리 객체 속성, 또는 논리적으로 사전 정의할 수 있는 속성은 Schematic – Defaults 페이지의 Preferences 대화상자(설계 공간 우측 상단 버튼에서 접근)에서 기본값으로 편집할 수 있습니다. Primitive List에서 객체를 선택하면 오른쪽에 해당 옵션이 표시됩니다.

-

Post-placement settings – 모든 시트 엔트리 객체 속성은 Properties 패널과 Sheet Entry 대화상자에서, 설계 공간에 배치된 시트 엔트리를 선택했을 때 편집할 수 있습니다.

Double Click Runs Interactive Properties 옵션이

Schematic – Graphical Editing 페이지의

Preferences 대화상자에서 활성화되어 있으면(기본값), 프리미티브를 더블 클릭하거나 선택된 프리미티브에서 마우스 오른쪽 버튼을 클릭한 후

Properties을(를) 선택하면

Properties 패널이 열립니다.

Double Click Runs Interactive Properties 옵션이 비활성화되어 있으면 대화상자가 열립니다.

패널과 대화상자에서 제공되는 옵션은 동일하지만, 옵션의 순서와 배치가 약간 다를 수 있습니다.

속성

-

Name – 시트 엔트리의 이름입니다.

객체의

Name 속성을 배치 전에 입력하고, 입력한 값이 숫자 또는 알파벳으로 끝나면, 이후 배치되는 각 객체는 이 숫자 또는 알파벳 값이 자동으로 증가합니다. 이 동작은

Auto-Increment During Placement 옵션(

Schematic – General 페이지,

Preferences 대화상자)에서 설정할 수 있습니다. 시트 엔트리의 경우

Primary 필드만 적용되며, 객체에 여러 필드(예: 핀)가 있을 때는

Secondary 필드가 적용됩니다.

시트 엔트리 이름에 부정(상단에 바 표시)을 추가하려면, 다음 방법 중 하나를 사용하세요:

-

핀 이름의 각 문자 뒤에 역슬래시 문자를 포함하세요(예:

E\N\A\B\L\E\).

-

Single '\' Negation 옵션을 Schematic – Graphical Editing 페이지의 Preferences 대화상자에서 활성화한 후, 핀 이름 앞에 역슬래시 한 개를 추가하세요(예:

\ENABLE).

-

I/O Type – 드롭다운을 사용하여 시트 엔트리의 I/O 타입을 선택하세요.

-

Harness Type – 드롭다운을 사용하여 하니스 타입을 선택하세요.

일반 (Net)

객체에 할당된 네트의 속성을 표시합니다. 필요에 따라 업데이트하세요.

Power Net 및 High Speed 필드는 지시문이 객체에 추가된 후에 사용할 수 있습니다.

파라미터 (Net)

교차 참조 추가

프로젝트에 교차 참조를 추가하면 프로젝트 내의 회로도 시트 간 네트 연결 흐름을 쉽게 추적할 수 있습니다. 회로도 편집기는 교차 참조를 자동으로 생성 및 업데이트하는 기능을 지원합니다.

Automatic Cross References 옵션을 General 영역에서 활성화하고, Cross References 영역의 옵션을 프로젝트 옵션 대화 상자의 옵션 탭에서 구성하세요. 활성 프로젝트에 대해 특정 교차 참조 스타일을 설정하거나, Follow Cross References settings in Preferences 옵션을 활성화하여 Port Cross References 영역의 옵션을 Schematic – General 페이지의 Preferences 대화 상자에서 상속받을 수 있습니다. 여기서 교차 참조가 표시될 객체(포트, 오프시트 커넥터, 시트 엔트리)도 선택할 수 있습니다.

Options 탭의 Project Options 대화 상자에 빠르게 접근하려면, 메인 메뉴에서 Reports » Automatic Cross References Settings 명령을 선택하거나 설계 공간에서 마우스 오른쪽 버튼을 클릭한 후 컨텍스트 메뉴에서 Sheet Actions » Automatic Cross References Settings 명령을 선택하세요.

활성 프로젝트에 대한 자동 교차 참조는 Options 탭의 Project Options 대화 상자에서 구성할 수 있습니다.

교차 참조는 설정된 스타일로 선택한 객체 옆에 회로도에 표시됩니다. 교차 참조 값은 Properties 패널에도 표시되며, 여기서 선택한 객체의 교차 참조 표시 여부를 전환할 수 있습니다.

교차 참조는 회로도에서 탐색할 수 있으며, 선택한 객체에 대해 Properties 패널에서도 확인할 수 있습니다. 포트에 대한 교차 참조 예시가 여기에 나와 있습니다.

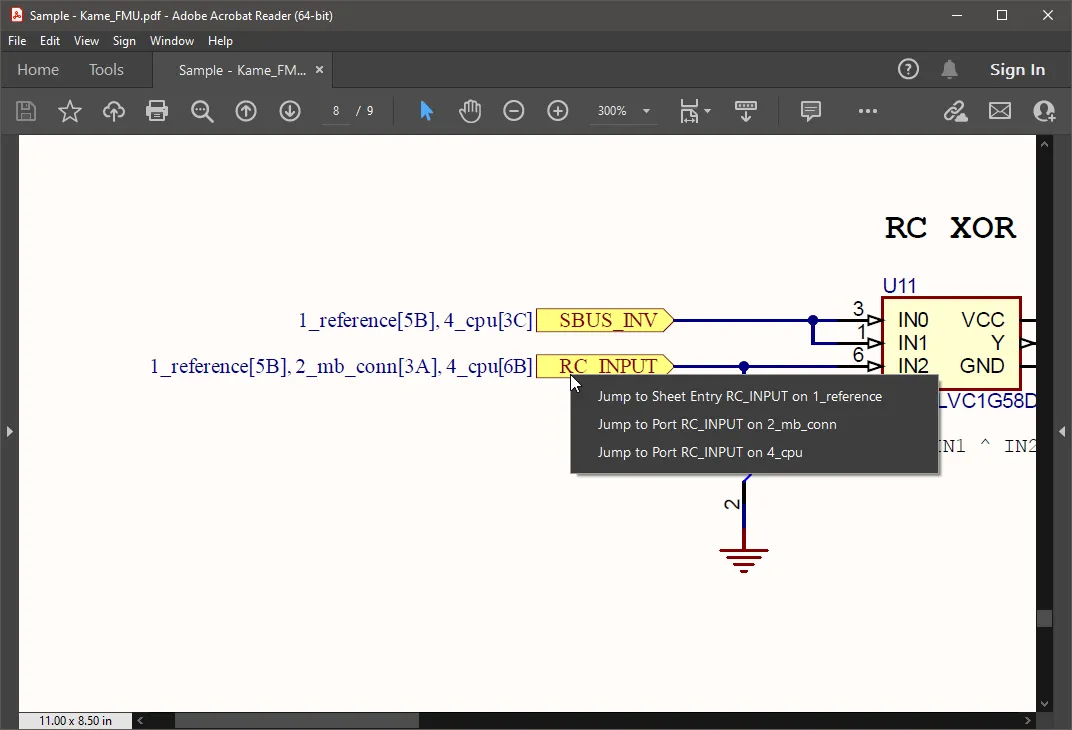

교차 참조는 회로도 PDF 출력에서도 지원됩니다. 하나의 객체가 둘 이상의 연결된 객체와 관련된 경우(예: 포트가 상위 회로도 시트의 시트 엔트리 및 다른 시트의 포트와 연결된 경우), PDF 출력에서 해당 객체를 클릭하면 연결된 객체가 위치한 시트 목록이 표시됩니다. 목록에서 항목을 선택하면 해당 페이지가 열립니다. 하나의 객체가 단일 연결 객체와만 관련된 경우, 객체를 클릭하면 바로 해당 페이지가 열립니다.

회로도 PDF 출력에서는 팝업 메뉴를 통해 여러 연결 객체를 쉽게 탐색할 수 있습니다.

다중 시트 설계 생성

프로젝트에 두 번째 회로도 시트를 추가하는 순간, 다중 시트 설계가 생성됩니다. 상위 시트 없이 플랫 설계를 계획 중이라면, 프로젝트에 계속해서 회로도 시트를 추가하면 됩니다(프로젝트의 Projects 패널에서 항목을 마우스 오른쪽 버튼으로 클릭한 후 Add New to Project » Schematic 명령을 컨텍스트 메뉴에서 선택). 그리고 Net Identifier Scope가 올바르게 설정되어 있는지 확인하세요.

하위 시트를 참조하기 위해 시트 심볼을 사용하려면, 시트 심볼을 배치한 후 수동으로 하위 시트를 올바르게 참조하도록 편집하거나, 아래에 설명된 다양한 내장 명령을 활용할 수 있습니다.

하위 시트 참조

시트 심볼의 Filename 속성이 하위 시트를 참조합니다. 이 필드에는 회로도 파일명만 입력해야 하며, 파일 위치 경로는 포함하지 않아야 합니다(이 위치 정보는 실제로 프로젝트 파일에 저장됩니다).

Filename 속성은 이 시트 심볼을 하위 회로도 시트와 연결합니다.

하위 회로도는 반드시 상위 회로도와 동일한 폴더에 저장할 필요는 없습니다. 파일이 상위 폴더보다 하위 폴더에 저장된 경우 상대 경로 참조가 사용되고, 다른 위치에 저장된 경우 절대 경로 참조가 사용됩니다. 이러한 프로젝트에서 파일을 이동할 때는 주의가 필요하며, 파일 경로를 자동으로 해결해주는 Project Packager를 사용해 파일을 ZIP으로 묶는 것이 좋습니다.

다중 시트 설계 탐색

회로도 편집기는 다중 시트 설계 내 문서 및 관련 객체 간을 빠르게 탐색할 수 있는 도구를 제공합니다.

Tools » Up/Down Hierarchy 명령은 현재 문서에서 설계 계층 구조의 상위 또는 하위 단계로 포커스를 이동할 때 사용합니다. 명령을 실행하면 커서가 십자선으로 바뀌고, 탐색 지점을 선택하라는 메시지가 표시됩니다. 시트 엔트리를 클릭하면 하위 시트의 일치하는 포트가 표시되고, 시트 심볼을 클릭하면 전체 하위 시트가 표시됩니다. 계층 구조를 위로 탐색하려면 포트를 클릭하여 상위 시트의 일치하는 시트 엔트리를 확인할 수 있습니다.

시트 엔트리나 포트가 버스에 연결된 경우, 첫 번째 클릭 시 메뉴가 팝업되어 전체 버스 또는 버스 내 개별 신호를 선택할 수 있습니다. 시트 엔트리나 포트에서 해당 배선이 강조 표시됩니다. 원래 시트 엔트리나 포트를 두 번째로 클릭하면, 각각 하위 회로도 시트의 해당 포트 또는 상위 시트의 시트 엔트리가 표시됩니다.

현재 커서 아래에 있는 시트 심볼이 참조하는 하위 시트를 열려면, 배치된 시트 심볼 위에서 마우스 오른쪽 버튼을 클릭한 후 컨텍스트 메뉴에서 Sheet Symbol Actions » Open SubSheet <SchematicDocumentName> 명령을 선택하세요. 명령을 실행하면 해당 심볼이 참조하는 회로도 문서가(아직 열려 있지 않다면) 열리고, 메인 설계 창에서 활성 문서가 됩니다.

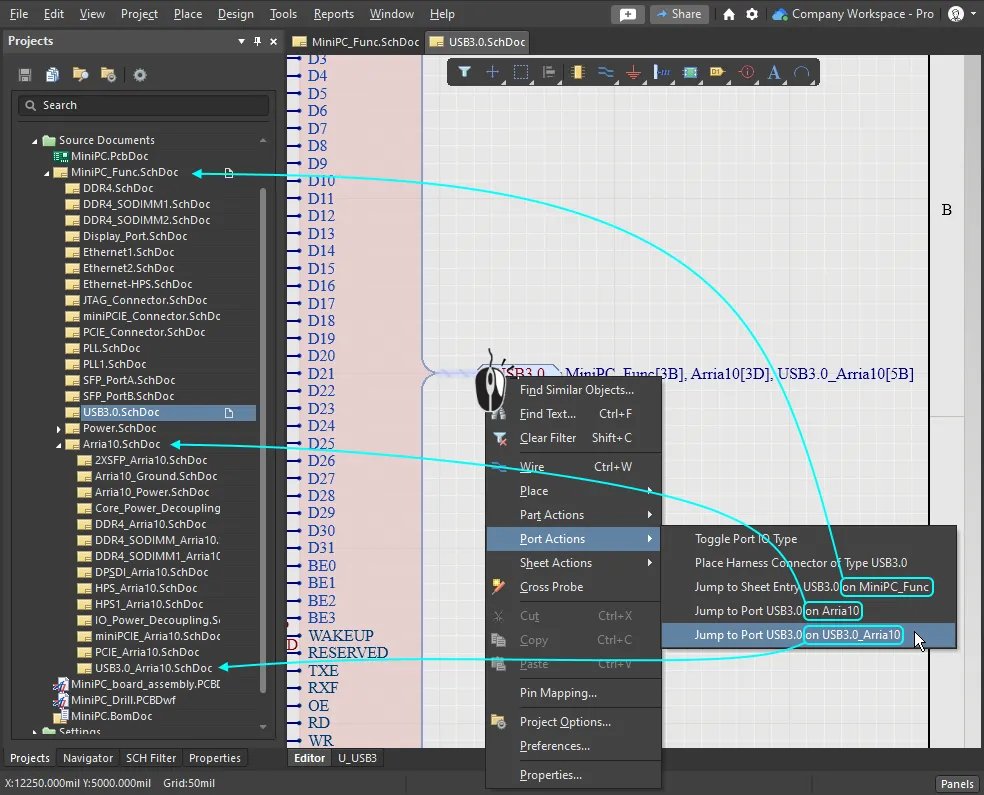

연관된 객체에 대해 자동 교차 참조가 활성화되어 있으면, 객체의 오른쪽 클릭 Jump To 명령을 Port Actions, Sheet Entry Actions 및 Off Sheet Actions(플랫 디자인의 경우) 하위 메뉴에서 사용할 수 있어 포트, 시트 엔트리, 오프-시트 커넥터 간을 쉽게 이동할 수 있습니다. 예를 들어, Automatic Cross References 옵션이 활성화되어 있고 Sheet Entry & Ports 설정 옵션이 Ports 옵션의 Options 탭에 있는 Options for Project 대화상자에서 선택된 경우, 포트 위에서 마우스 오른쪽 버튼을 클릭한 후 원하는 Port Actions » Jump to Port <PortName> on <SchematicDocumentName> 또는 Port Actions » Jump to Sheet Entry <PortName> on <SchematicDocumentName> 명령을 컨텍스트 메뉴에서 선택할 수 있습니다. 그러면 해당 포트 또는 시트 엔트리가 있는 소스 문서가 활성 문서로 전환되고, 커서는 해당 포트 또는 시트 엔트리 위에 위치하게 됩니다. 대상 문서에서 동일한 이름을 가진 모든 포트(및 연결된 배선)는 하이라이트 처리됩니다.

Jump to 명령을 사용하면 설계 내 어디서든 일치하는 객체로 바로 이동할 수 있습니다.

-

객체 간을 이동할 때마다 해당 객체가 설계 공간에서 하이라이트 처리됩니다. 시각적 표시 방식은 Highlight Methods(디밍, 확대, 선택) 설정에 따라 System - Navigation 페이지의 Preferences 대화상자에서 정의됩니다.

-

계층 구조는 Ctrl 을(를) 누른 상태에서 포트, 시트 엔트리, 시트 심볼을 더블 클릭하여 직접 탐색할 수도 있습니다.

-

또한 Interactive Navigation 기능을 사용하여 Navigator 패널에서 계층 구조를 탐색할 수도 있습니다.

계층 구조 생성

소프트웨어에는 다중 문서, 계층 구조를 빠르고 효율적으로 구축할 수 있는 다양한 명령이 포함되어 있습니다. 어떤 명령을 사용할지는 개인의 설계 방법론(상향식 또는 하향식)에 따라 달라집니다. 이러한 명령은 시트 엔트리 추가, 새로운 회로도 시트 생성, 포트 배치 등 계층 구조 생성에 필요한 모든 요소를 자동으로 처리하므로 수동으로 계층 구조를 만드는 것보다 훨씬 효율적입니다.

이 명령을 사용하여 하향식 방식으로 계층 구조를 구축할 수 있습니다:

이 명령을 사용하여 상향식 방식으로 계층 구조를 구축할 수 있습니다:

-

Create Sheet Symbol From Sheet(Design 메인 메뉴 또는 설계 공간의 Sheet Actions 오른쪽 클릭 하위 메뉴) – 이 명령을 사용하면 지정한 회로도 시트로부터 심볼을 생성할 수 있습니다. 이 명령을 사용하려면 먼저 새 시트 심볼을 배치할 시트로 전환한 후 명령을 실행하세요. ![]() 문서 선택 대화상자가 열리며, 여기서 새로 생성될 시트 심볼이 참조할 대상 회로도 문서를 선택할 수 있습니다. 시트 심볼에는 발견된 각 포트에 대응하는 시트 엔트리가 포함됩니다. 추후 포트나 시트 엔트리가 추가되거나 삭제되면 아래에서 설명한 대로 다시 동기화할 수 있습니다.

문서 선택 대화상자가 열리며, 여기서 새로 생성될 시트 심볼이 참조할 대상 회로도 문서를 선택할 수 있습니다. 시트 심볼에는 발견된 각 포트에 대응하는 시트 엔트리가 포함됩니다. 추후 포트나 시트 엔트리가 추가되거나 삭제되면 아래에서 설명한 대로 다시 동기화할 수 있습니다.

-

시트 심볼이 생성되어 활성 시트에 배치될 때, 이 시트는 Choose Document to Place 대화상자에 표시되지 않습니다. 이는 시트 심볼이 자신이 배치된 동일한 시트를 참조할 수 없기 때문입니다.

-

새로 생성된 상위 시트 심볼의 시트 엔트리에 대한 전기적 I/O 타입은 원본 하위 시트의 포트와 동일하게 설정됩니다.

이 명령을 사용하여 회로 배치 구조를 재구성할 수 있습니다:

-

Edit » Refactor » Move Selected Sub-circuit to Different Sheet - 이 명령을 사용하면 선택한 부품과 배선을 프로젝트 내의 다른 시트로 이동할 수 있습니다. Choose Destination Document 대화상자가 열리며, 프로젝트 내의 기존 회로도 중에서 원하는 시트를 선택할 수 있습니다. 이 명령에 대한 자세한 설명은 아래에서 다룹니다.

부품을 한 시트에서 다른 시트로 이동하는 전용 명령이 제공되는 이유는, 표준 잘라내기 & 복사(Cut & Copy) 명령을 사용하면 각 부품의 고유 식별자(UID)가 자동으로 재설정되기 때문입니다. UID는 회로도 부품과 PCB 부품을 연결하는 역할을 하며, 회로도 부품의 UID가 재설정되면 설계 동기화(즉, Design » Update 명령 사용 시) 시마다 디자인레이터를 통해 일치시키라는 메시지가 표시됩니다. 필요하다면 PCB 에디터 내에서 Project » Component Links 명령을 사용해 UID를 다시 동기화할 수 있습니다.

► 설계 동기화

설계 구조 재구성

Main article: 설계 리팩토링

설계 과정은 종종 비구조적이고 유기적으로 진행되며, 설계자는 여러 부분의 아이디어를 동시에 구상하고, 아이디어가 발전함에 따라 섹션을 캡처할 수 있습니다. 이로 인해 처음에는 잘 정리된 회로도 세트가 시간이 지나면서 복잡해지고 정리가 어려워질 수 있습니다. 회로도 설계를 재구성할 때 잘라내기, 복사, 붙여넣기를 사용할 수 있지만, 항상 최선의 방법은 아닙니다.

잘라내기와 복사를 사용하지 않는 이유는? 각 부품이 배치될 때 고유 식별자가 할당되며, 이 식별자는 부품이 잘라내기/복사 및 붙여넣기 될 때마다 자동으로 재설정됩니다. UID 관리는 설계 내에서 각 UID가 한 번만 사용되도록 보장하기 위해 수행되며, 이는 회로도 부품과 PCB 부품을 연결하는 핵심 필드입니다. 설계가 아직 PCB 에디터로 전송되지 않았다면 잘라내기/복사/붙여넣기 방식도 괜찮지만, 이미 전송된 경우에는 리팩토링 도구를 사용하는 것이 더 좋습니다.

서브 회로를 다른 시트로 이동하기

회로의 일부를 한 시트에서 다른 시트로 옮기는 가장 쉬운 방법은 해당 부분을 선택한 후 Edit » Refactor » Move Selected Sub-circuit to Different Sheet 명령을 실행하는 것입니다. Choose Destination Document 대화 상자가 열리며, 대상 시트를 선택하고 OK을(를) 클릭하면 해당 시트가 나타나고, 하위 회로가 커서에 떠 있는 상태로 위치 지정을 할 수 있습니다.

선택된 회로 부분은 Move Selected Subcircuit to Different Sheet 명령을 사용하여 프로젝트 내의 다른 시트로 쉽게 이동할 수 있습니다.

► Design Refactoring에 대해 자세히 알아보기.

포트와 시트 엔트리 동기화

설계 구조를 재구성하면서 부품과 배선을 이동했다면, 각 포트가 일치하는 시트 엔트리를 갖도록 하위 시트와 시트 심볼을 다시 동기화해야 할 수도 있습니다. 이는 Synchronize Sheet Entries and Ports 명령을 사용하여 수행할 수 있으며, 다음과 같은 방법이 있습니다:

-

A specific Sheet Symbol - 시트 심볼에서 마우스 오른쪽 버튼을 클릭하여 컨텍스트 메뉴를 표시한 후 Sheet Symbol Actions » Synchronize Sheet Entries and Ports 명령을 선택하면, 커서 아래의 시트 심볼만 분석합니다.

-

All Sheet Symbols in the design - Design » Synchronize Sheet Entries and Ports 명령을 선택하면 전체 설계의 모든 시트 심볼을 분석하며, 대화 상자에는 설계 내 각 시트 심볼에 대한 탭이 Only Show unmatched sheet symbols 옵션에 따라 하단에 표시됩니다.

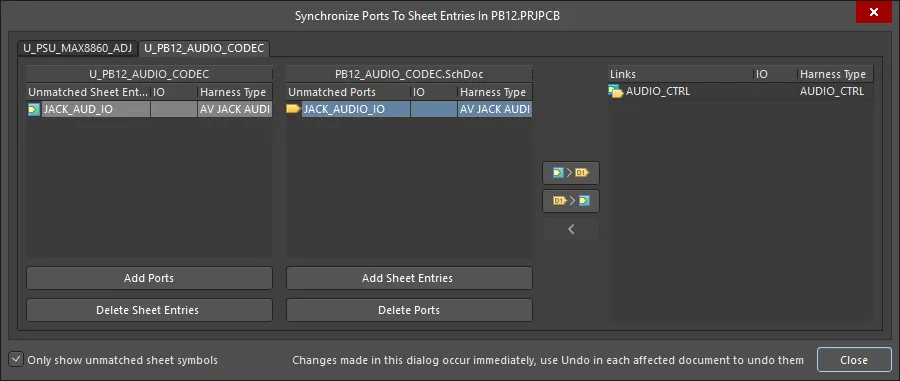

이 두 명령 모두 Synchronize Ports to Sheet Entries 대화 상자가 열립니다. 대화 상자의 오른쪽에는 이미 일치된 포트/시트 엔트리가, 왼쪽에는 일치하지 않은 포트와 시트 엔트리가 두 개의 열로 나열됩니다. 모든 시트 엔트리가 하위 시트의 해당 포트와 이름과 I/O 타입이 모두 일치하면, 시트 심볼이 참조된 하위 시트와 '동기화'되었다고 합니다.

Synchronize Ports to Sheet Entries 대화 상자는 시트 엔트리가 하위 시트의 포트와 일치하는지 확인하는 데 사용됩니다. 두 개의 탭이 있는 것을 보면, 이 설계에서 시트 엔트리/포트 불일치가 있는 시트 심볼이 두 개 있다는 것을 알 수 있습니다.

Options and Controls of the Synchronize Ports to Sheet Entries Dialog

-

Unmatched Sheet Entries - 이 영역에는 현재 시트 심볼에 연결된 모든 일치하지 않은 시트 엔트리 목록이 표시됩니다. 시트 심볼의 Designator가 영역의 헤더로 나타납니다. 각 시트 엔트리는 이름, I/O 타입, 하니스 타입으로 나열됩니다.

-

Add Ports - 이 버튼을 클릭하면, 해당 영역에서 현재 선택된 각 시트 엔트리에 대해 동일한 이름, I/O 타입, 하니스 타입을 가진 포트가 자동으로 생성됩니다. 포트가 커서에 떠 있는 상태로 하위 시트로 이동하며, 초기 위치를 지정할 수 있습니다. 클릭하거나 Enter 을(를) 눌러 포트를 배치하세요. Synchronize 대화 상자가 다시 나타나며, 각 시트 엔트리-포트 쌍이 Links 영역에 자동으로 입력됩니다.

-

Delete Sheet Entries - 이 버튼을 클릭하면 현재 선택된 시트 엔트리(들)가 삭제됩니다. 해당 엔트리(들)는 영역에서 제거되고, 상위 시트 심볼에서도 삭제됩니다.

-

Unmatched Ports - 이 영역에는 시트 심볼이 참조하는 회로도 시트에서 현재 일치하지 않은 모든 포트 목록이 표시됩니다. 문서 이름이 영역의 헤더로 나타납니다. 각 포트 엔트리는 이름, I/O 타입, 하니스 타입으로 나열됩니다.

-

Add Sheet Entries - 이 버튼을 클릭하면, 해당 영역에서 현재 선택된 각 포트에 대해 동일한 이름, I/O 타입, 하니스 타입을 가진 시트 엔트리가 자동으로 생성됩니다. 시트 엔트리가 커서에 떠 있는 상태로 시트 심볼로 이동하며, 초기 위치를 지정할 수 있습니다. 클릭하거나 Enter 을(를) 눌러 시트 엔트리를 배치하세요. Synchronize 대화 상자가 다시 나타나며, 각 시트 엔트리-포트 쌍이 Links 영역에 자동으로 입력됩니다.

-

Delete Ports - 이 버튼을 클릭하면 현재 선택된 포트(들)가 삭제됩니다. 해당 포트(들)는 영역에서 제거되고, 참조된 하위 시트에서도 삭제됩니다.

-

Links - 이 영역에는 현재 연결(또는 일치)된 시트 엔트리-포트 쌍의 목록이 표시됩니다. 각 항목은 시트 엔트리와 포트 모두에서 사용되는 이름, I/O 타입, 하니스 타입을 반영합니다.

여러 항목을 선택하려면 표준 다중 선택 방법(Ctrl+Click, Shift+Click, Click+Drag)을 사용하세요.

버튼

다음 버튼을 사용하여 동기화 과정을 수동으로 제어할 수 있습니다:

-

- 이 버튼을 클릭하면 Unmatched Sheet Entries 영역에서 선택한 시트 엔트리와 Unmatched Ports 영역에서 선택한 포트 엔트리를 시트 엔트리의 이름, I/O 타입, 하니스 타입을 사용하여 연결합니다. 포트의 이름, I/O 타입, 하니스 타입이 이에 맞게 변경됩니다.

- 이 버튼을 클릭하면 Unmatched Sheet Entries 영역에서 선택한 시트 엔트리와 Unmatched Ports 영역에서 선택한 포트 엔트리를 시트 엔트리의 이름, I/O 타입, 하니스 타입을 사용하여 연결합니다. 포트의 이름, I/O 타입, 하니스 타입이 이에 맞게 변경됩니다.

-

- 이 버튼을 클릭하면 Unmatched Sheet Entries 영역에서 선택한 포트 엔트리와 Unmatched Ports 영역에서 선택한 시트 엔트리를 포트의 이름, I/O 타입, 하니스 타입을 사용하여 연결합니다. 시트 엔트리의 이름, I/O 타입, 하니스 타입이 이에 맞게 변경됩니다.

- 이 버튼을 클릭하면 Unmatched Sheet Entries 영역에서 선택한 포트 엔트리와 Unmatched Ports 영역에서 선택한 시트 엔트리를 포트의 이름, I/O 타입, 하니스 타입을 사용하여 연결합니다. 시트 엔트리의 이름, I/O 타입, 하니스 타입이 이에 맞게 변경됩니다.

-

- 이 버튼을 클릭하면 Links 영역에서 현재 선택된 시트 엔트리와 포트 간의 연결이 해제됩니다. 개별 항목은 대화 상자의 해당 미일치 영역에 다시 표시됩니다.

- 이 버튼을 클릭하면 Links 영역에서 현재 선택된 시트 엔트리와 포트 간의 연결이 해제됩니다. 개별 항목은 대화 상자의 해당 미일치 영역에 다시 표시됩니다.

추가 제어

-

Only show unmatched sheet symbols - 시트 심볼의 시트 엔트리가 참조된 하위 시트의 포트와 완전히 동기화된 경우, 대화 상자에 해당 내용이 표시되며 영역이 나타나지 않습니다. 이 옵션을 비활성화하면, 일치된 항목을 확인하고 위에서 설명한 대화 상자의 모든 제어 기능을 사용할 수 있습니다.

대화 상자 왼쪽에 표시된 불일치 항목에 집중하여, 첫 번째 열에서 시트 엔트리를 선택한 후 두 번째 열에서 올바른 포트를 선택하고, 대화 상자 중간에 있는 필요한 버튼을 클릭하여 둘 중 하나를 업데이트하면 동기화되어(오른쪽 목록으로 이동) 일치됩니다.

버튼의 기능은 다음과 같습니다:

-

- 시트 엔트리 속성을 사용하여 선택한 포트에 적용합니다.

- 시트 엔트리 속성을 사용하여 선택한 포트에 적용합니다.

-

- 포트 속성을 사용하여 선택한 시트 엔트리에 적용합니다.

- 포트 속성을 사용하여 선택한 시트 엔트리에 적용합니다.

왼쪽 열에서 여러 시트 엔트리를 선택하면, 소프트웨어가 각 시트 엔트리를 두 번째 열의 인접한 포트와 동기화합니다. 인접한 포트(또는 시트 엔트리)가 없으면 새로 생성됩니다.

-

명령으로 새 시트 엔트리나 포트가 추가된 경우, 작업이 끝난 후 회로도 시트에서 올바른 위치로 배치해야 합니다.

-

대화 상자에서 변경한 내용은 즉시 적용됩니다. 대화 상자에서는 변경을 실행 취소할 수 없습니다. 변경을 되돌리려면 문서의 Undo 기능을 사용해야 합니다.

AI로 번역됨

AI로 번역됨