QuickNav - 회로도 설계 개체

이 페이지는 회로도 문서(및 해당되는 경우 회로도 라이브러리 문서)에서 사용할 수 있는 설계 객체에 대한 빠른 참조 정보를 제공하며, 각 객체의 더 자세한 정보로 빠르게 이동할 수 있도록 해줍니다.

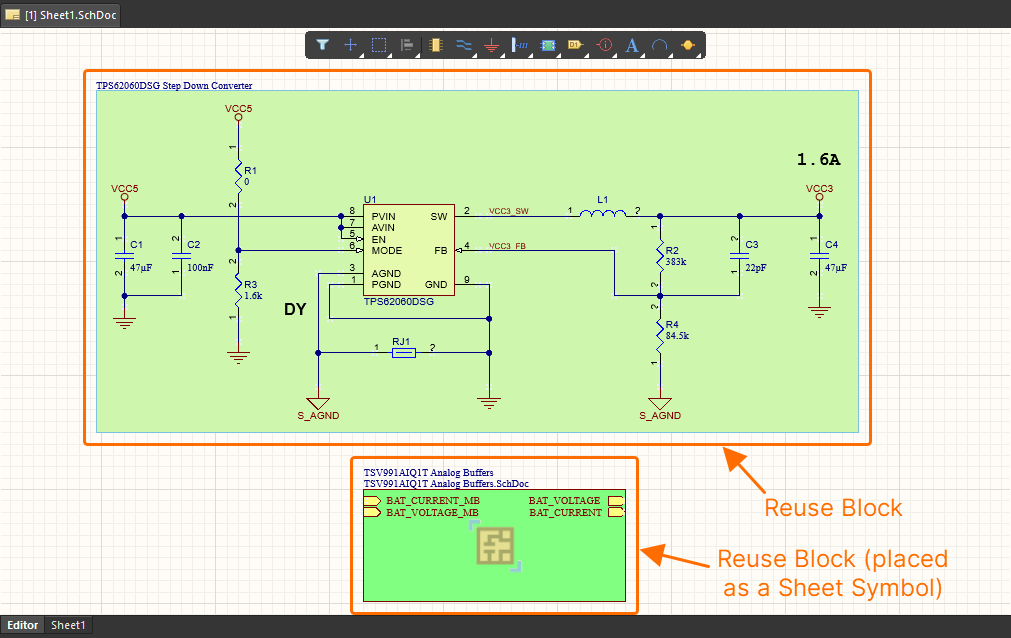

그래픽 개요

다음 이미지는 일반적으로 사용되는 회로도 설계 객체를 한데 모아 시각적으로 보여줍니다.

회로도 문서(및 해당되는 경우 회로도 라이브러리 문서)에서 일반적으로 사용되는 설계 객체입니다.

참고

-

사용 가능한 경우, 회로도 문서에 재사용 블록 또는 스니펫을 배치할 수도 있습니다. 자세한 내용은 재사용 블록 작업 및 스니펫 작업을 참조하십시오.

-

회로도 편집기의 기본 Place menu에서 device sheet 심볼을 배치할 수도 있습니다. 배치되면 이는 사실상 시트 심볼 객체로 동작합니다. 연결된 Workspace에서 managed schematic sheet를 배치하는 경우도 마찬가지입니다. 두 경우 모두 심볼은 색상에서 차이가 있으며, 재사용 가능한 엔터티를 참조한다는 것을 구분하기 위한 그래픽이 포함됩니다.

-

핀 및 IEEE 심볼 객체는 Schematic Library 편집기에서만 사용할 수 있습니다.

주요 객체 슬라이드쇼

아래 슬라이드를 살펴보면 실제 회로 내에서 다양한 설계 객체가 어떻게 사용되는지 확인할 수 있습니다. 각 객체에 대한 상위 수준의 소개와 함께 더 자세한 정보로 연결되는 링크가 제공됩니다. 특히 논리 설계를 캡처할 때 반복적으로 사용하게 되는 전기적 객체와 지시 객체에 중점을 두고 있습니다.

버스버스는 다중 와이어 연결을 나타내는 폴리라인 객체입니다. 버스는 예를 들어 주소 버스나 데이터 버스처럼 연속된 넷들의 집합을 묶는 데 사용됩니다. 핵심 요구 사항은 버스 내 각 넷의 이름이 공통 기본 이름 뒤에 숫자 식별자가 붙는 형식이어야 한다는 점입니다. 위 예에서는 6개의 개별 넷(MB_ESC_M1 - MB_ESC_M6)이 버스 MB_ESC_M[1..6]로 묶인 상태로 시트에 들어옵니다. 자세히 알아보기... 버스 엔트리버스 엔트리는 와이어를 버스 라인에 연결하는 데 사용되는 전기적 설계 프리미티브입니다. 이를 사용하면 서로 다른 두 넷을 버스의 동일한 지점에 연결할 수 있습니다. 이것을 와이어로 수행하면 두 넷이 쇼트를 일으키게 됩니다. 위 예에서는 입력 버스(MB_ESC_M[1..6])가 버스 엔트리를 사용하여 구성 넷들로 분리됩니다. 자세히 알아보기... 파트라이브러리 내의 파트(또는 컴포넌트)는 실제 인쇄 회로 기판에 배치되는 물리적 디바이스를 나타냅니다. 회로도 시트에서 컴포넌트는 회로도 심볼 모델로 표현됩니다. 각 컴포넌트는 하나 이상의 파트를 포함할 수 있습니다. 파트에는 컴포넌트의 심볼 표현과 함께 PCB 풋프린트 같은 모델에 대한 링크와, 컴포넌트 파라미터 및 공급업체 정보 등의 세부 사항을 문서화하는 데 사용되는 파라미터도 포함됩니다. 모델 링크와 파라미터가 파트에 추가되는 방식은 사용 중인 라이브러리 저장 유형에 따라 달라집니다. 자세히 알아보기... 파트 지정자 및 설명Designator 필드는 회로도 컴포넌트(파트)의 자식 파라미터 객체입니다. 이는 프로젝트의 회로도 소스 문서 전반에 걸쳐 배치된 다른 모든 파트와 구별할 수 있도록 각 배치된 파트를 고유하게 식별하는 데 사용됩니다. 자세히 알아보기... Comment 필드(이 역시 회로도 컴포넌트(파트)의 자식 파라미터 객체)는 컴포넌트에 대한 추가 정보(예: 부품 번호 또는 값)를 표시하는 데 사용됩니다. 자세히 알아보기... 전원 포트전원 포트는 설계 구조와 관계없이 회로도 프로젝트 전체에서 동일한 이름을 가진 다른 모든 전원 포트와 연결성을 생성합니다. 넷 이름은 전원 포트에 의해 자동으로 지정됩니다. 필요한 경우 이 넷은 특정 회로도 시트로 국한시킬 수 있습니다. 자세히 알아보기... 와이어와이어는 회로도 상의 점들 사이에 전기적 연결을 형성하는 데 사용되는 폴리라인 전기 설계 프리미티브입니다. 와이어는 실제 물리적 전선에 해당합니다. 자세히 알아보기... 넷 라벨넷 라벨은 동일한 회로도 시트에서 같은 이름을 가진 다른 넷 라벨과 연결성을 생성하는 데 사용되는 넷 식별자입니다. 넷 이름은 넷 라벨에 의해 자동으로 지정됩니다. 넷 라벨은 컴포넌트 핀, 와이어 및 버스에 배치할 수 있습니다. 단, 프로젝트 옵션이 Net Identifier Scope 의 Global를 사용하도록 구성되지 않은 한 넷 라벨은 시트 간에 연결되지 않습니다. 자세히 알아보기... 포트포트는 한 회로도 시트의 넷을 다른 회로도 시트에 연결하는 데 사용됩니다. 연결성은 수직 방향(계층형 설계)일 수도 있고 수평 방향(플랫 설계)일 수도 있습니다. Project Options dialog의 Options 탭에서 Allow Ports to Name Nets 옵션이 활성화되어 있으면 포트 이름이 넷 이름으로 사용됩니다. 이 경우 포트는 동일한 회로도 시트 내에서도 연결됩니다. 자세히 알아보기... 오프시트 커넥터오프시트 커넥터는 한 회로도 시트의 넷을 다른 시트에 연결하는 데 사용됩니다(같은 시트 내 연결은 아님). 이들은 수평 연결성(플랫 설계)만 지원하며 포트와 비교했을 때 기능이 제한적입니다. 자세히 알아보기... 시트 심볼시트 심볼은 다중 시트 계층형 설계에서 하위 시트를 나타내는 데 사용됩니다. 계층형 설계는 설계 내 구조, 즉 시트 간 관계가 표현되는 설계입니다. 계층형 설계의 장점은 설계 구조를 보여주고, 연결성이 항상 자식 시트에서 부모 시트의 시트 심볼로 향하므로 완전히 예측 가능하고 쉽게 추적할 수 있다는 점입니다. 또 다른 장점은 정교한 설계 재사용 시스템을 제공하는 기반이 된다는 것입니다. 이 시스템은 Workspace 기반인지 파일 기반인지에 따라 managed schematic sheets 또는 device sheets를 통해 제공됩니다. 각 경우 배치되는 심볼은 색상이 다르고 재사용 가능한 엔터티를 참조함을 구분하기 위한 그래픽을 포함하지만, 기능과 동작은 본질적으로 표준 시트 심볼과 같습니다. 자세히 알아보기... 시트 엔트리시트 엔트리는 시트 심볼 내부에 배치되며, 해당 심볼이 나타내는 원본 회로도 하위 시트에서 같은 이름의 포트와 연결성을 생성합니다. Project Options dialog의 Options 탭에서 Allow Sheet Entries to Name Nets 옵션이 활성화되어 있으면 시트 엔트리가 넷 이름으로 사용됩니다. 자세히 알아보기... 시트 심볼 지정자부모 시트 심볼의 자식 객체인 시트 심볼 지정자는, 동일한 회로도 시트에 배치된 다른 시트 심볼과 구별할 수 있도록 심볼에 의미 있는 이름을 부여하는 데 사용됩니다. 일반적으로 이 이름은 해당 심볼이 나타내는 회로도 하위 시트의 전체 기능을 반영합니다. 시트 심볼 인스턴스화를 사용하면 동일한 하위 시트의 여러 채널을 하나의 시트 심볼에서 참조할 수 있습니다. 사용되는 구문에는 시트 심볼의 Designator 필드에서 Repeat 키워드를 사용하는 방식이 포함됩니다. 자세히 알아보기... 시트 심볼 파일 이름시트 심볼 파일 이름은 부모 시트 심볼의 자식 객체이며, 시트 심볼과 해당 심볼이 나타내는 회로도 하위 시트 사이의 링크를 제공합니다. 여러 하위 시트는 File Name 필드에서 각 파일 이름을 세미콜론으로 구분하여 하나의 시트 심볼에서 참조할 수 있습니다. 자세히 알아보기... 재사용 블록재사용 블록을 사용하면 서로 다른 프로젝트 전반에서 설계 회로의 일부를 저장하고 재사용할 수 있습니다. 여기에는 회로도 회로와 PCB용 물리적 표현이 모두 포함될 수 있습니다. 이러한 재사용 블록을 회로도 시트에 배치하면 ECO 프로세스 중에 해당 물리적 표현이 PCB 문서에 자동으로 배치됩니다. 재사용 블록은 공식적으로 관리되는 Workspace 엔터티로, 읽기 전용이며 라이프사이클/리비전 제어(블록 업데이트 가능) 및 추적 가능성(where-used 지원)을 제공합니다. 재사용 블록은 회로도 시트에 직접 배치하거나 회로도 시트의 시트 심볼로 배치할 수 있습니다. 후자의 경우 배치된 시트 심볼에는 재사용 블록의 포트에 해당하는 시트 엔트리가 포함됩니다. 재사용 블록의 내용은 시트 심볼이 참조하는 자동 생성된 자식 회로도 시트에 배치됩니다. 배치된 재사용 블록의 시트 심볼에는 고유한 아이콘이 표시됩니다. 자세히 알아보기... 신호 하니스신호 하니스는 버스, 와이어 및 다른 신호 하니스를 포함한 서로 다른 신호를 논리적으로 그룹화할 수 있게 해주는 추상 연결로, 더 높은 유연성과 간소화된 설계를 제공합니다. 신호 하니스는 PCB 프로젝트에서 하위 회로 간의 상위 수준 추상 연결을 생성하고 조작할 수 있게 합니다. 이를 통해 동일한 회로도 설계 공간 내에서 더 복잡한 설계를 구현할 수 있으며, 설계의 가독성을 높이고 재사용 가능성을 확장합니다. 자세히 알아보기... 하니스 커넥터하네스 커넥터는 기본적으로 여러 신호를 하나로 묶어 신호 하네스를 구성하는 컨테이너로, 여기에는 버스, 와이어 및 기타 신호 하네스가 포함됩니다. 하네스 커넥터는 포함된 하네스 엔트리를 통해 이 하네스에 연결되는 모든 신호를 모아 주는 깔때기와 같다고 생각하면 됩니다. 자세히 알아보기... Harness Entry하네스 엔트리는 하네스 커넥터 내부에 배치되며, 와이어, 버스 및 기타 신호 하네스를 통해 전달되는 신호들을 결합하여 더 상위 수준의 신호 하네스를 형성하는 연결 지점입니다. 자세히 알아보기... Harness Type상위 하네스 커넥터의 자식 객체인 하네스 유형은 배치된 하네스 커넥터의 유형 또는 그 안에 정의된 하네스 엔트리 집합의 유형 이름을 지정하는 데 사용됩니다. 하네스 유형과 여기에 연결된 하네스 엔트리는 본질적으로 넷 자체의 이름이 아니라 넷을 담는 컨테이너의 이름입니다. 자세히 알아보기... Pin핀은 부품의 물리적 핀을 나타내기 위해 Schematic Library 편집기에서 배치됩니다. 핀의 한쪽 끝만 전기적으로 활성 상태이며, 이를 핀의 핫 엔드(hot end)라고 부르기도 합니다. 자세히 알아보기... Probe프로브는 시뮬레이션 가능한 회로의 특정 위치에서 측정을 수행하는 데 사용됩니다. 프로브를 사용하면 해당 위치의 전압, 전류 또는 전력을 확인할 수 있으며, 두 개의 프로브를 순차적으로 배치하여 전압 차도 측정할 수 있습니다. 또한 프로브에 대해 대화형 모드를 활성화하면 시뮬레이션을 매번 다시 실행하지 않아도 시뮬레이션 결과가 포함된 No ERC DirectiveNo ERC 설계 지시자는 회로의 노드에 배치되어, 회로도 프로젝트를 검증할 때 감지되는 모든 Electrical Rule Check 경고 및/또는 오류 위반 조건의 보고를 억제합니다. No ERC는 회로의 특정 지점에서 의도적으로 오류 검사를 제한하는 데 사용되며, 예를 들어 연결되지 않은 핀처럼 경고가 발생할 것이 확실한 경우에 유용합니다. 그러면서도 회로의 나머지 부분에 대해서는 포괄적인 검사를 계속 수행할 수 있습니다. 자세히 알아보기... Differential Pair Directive차동 페어 지시자(미리 정의된 파라미터 세트 지시자)는 회로도에서 차동 페어 객체를 정의할 수 있게 해줍니다. 이 유형의 지시자를 대상 페어의 양(+) 및 음(-) 넷 모두에 부착하거나, 블랭킷 객체로 해당 페어를 덮어 하나의 지시자로 여러 넷을 대상으로 지정할 수 있습니다. 넷 자체는 _P 및 _N 접미사를 사용해 이름이 지정되어야 합니다. 사용자 정의 차동 페어 접미사는 Project Options 대화상자의 Options 탭에 있는 Diff Pairs 섹션에서 정의할 수 있습니다.

이 유형의 지시자 한 쌍(양의 넷용 하나와 음의 넷용 하나)은 동기화 과정에서 PCB로 전송될 때 차동 페어 객체를 생성합니다. 생성된 각 차동 페어 객체는 All Differential Pairs의 기본 차동 페어 클래스에 추가됩니다. 생성된 차동 페어 객체의 이름은 회로도상의 넷 페어의 루트 이름이 됩니다. 예를 들어, 위 예시의 회로도에서 Parameter Set Directive파라미터 세트 지시자를 사용하면 설계 사양을 회로도 설계 내의 넷 유형 객체와 연결할 수 있습니다. 예를 들어 파라미터 세트 지시자를 사용하여 PCB 레이아웃 제약조건, 차동 페어 및 넷 클래스를 정의할 수 있습니다. 소프트웨어는 파라미터 세트 지시자 안에 있는 특정 이름의 파라미터가 존재하는지를 기준으로 어떤 설계 지시자를 배치하고 있는지 판단합니다. 자세히 알아보기... Blanket Directive파라미터 세트 지시자는 부착된 특정 넷만 대상으로 할 수 있지만, Blanket 지시자와 함께 사용하면 그 범위를 블랭킷 내부의 모든 넷으로 확장할 수 있습니다. 블랭킷 지시자는 넷 및/또는 부품의 집합 위에 배치됩니다. 단순한 직사각형 형태나 다각형 형태로 정의할 수 있으며, 다각형 형태는 시트에서 필요한 넷 객체의 적용 범위를 더 정밀하게 제어할 수 있게 해줍니다. 그런 다음 블랭킷에 적용된 파라미터 세트 지시자는 블랭킷이 덮고 있는 모든 넷과 부품에 적용됩니다. 자세히 알아보기... Compile Mask DirectiveNo ERC 지시자는 설계 내에서 소수의 위반 핀, 포트, 시트 엔트리 또는 넷을 억제하는 데 매우 유용합니다. 그러나 경우에 따라서는 부품을 포함한 설계의 전체 섹션을 제거하고 싶을 수도 있습니다. 컴파일 마스크 지시자를 사용하면 포함된 설계 영역을 컴파일러에서 사실상 숨길 수 있으며(수동 검증 수행 시), 아직 완성되지 않아 컴파일 오류를 발생시킬 회로에 대해 수동으로 오류 검사를 방지할 수 있습니다. 이는 활성 문서 또는 프로젝트를 검증하여 설계의 다른 특정 영역의 무결성을 확인해야 하지만, 아직 완성되지 않은 설계 부분과 관련된 컴파일러 생성 메시지의 '잡음'은 원하지 않을 때 매우 유용합니다. 이 기능은 위 예시처럼 설계 흐름의 일부로 시뮬레이션이 포함된 경우에도 매우 유용하게 사용할 수 있습니다. 회로 시뮬레이션을 실행할 때 전압 및 전류 소스는 필수 요소이지만, 완성된 PCB에는 필요하지 않습니다. 회로 구조를 약간만 계획해 두면 일반적으로 시뮬레이션 전용 부품을 설계의 한 영역에 모두 모을 수 있고, 그 영역은 컴파일 마스크 지시자로 쉽게 덮을 수 있습니다. 자세히 알아보기... |

Schematic Document Commenting

회로도 문서에서는 객체, 특정 지점 또는 영역에 댓글을 달 수 있습니다. 댓글은 사용자가 추가하는 메모이며 다른 사용자가 답글을 달 수 있습니다. 댓글은 데이터 자체를 변경하지 않으면서 사용자 간 협업을 촉진하는데, 이는 댓글이 연결된 Workspace에 의해 해당 데이터와 독립적으로 저장되기 때문입니다. 댓글은 Comments and Tasks 패널과 함께 사용하는 컨텍스트 댓글 창을 통해 설계 공간 내에서 직접 게시, 답글 작성 및 관리할 수 있습니다.

자세한 내용은 Document Commenting 페이지를 참조하십시오.

A-Z Listing

다음은 특정 설계 객체에 대한 자세한 정보를 QuickNav 방식으로 빠르게 찾을 수 있도록 정리한 편리한 알파벳순 목록입니다.

AI로 번역됨

AI로 번역됨