设计指令(Design Directives)是在设计捕获过程中放置在原理图上的对象,用于指定需要传递给软件其他部分的指令。可用的设计指令可通过以下两种方式使用:

-

与源原理图文档自动编译相关的指令。

-

用于将原理图页上定义的信息传递到 PCB 的指令。

以下各节将更深入地介绍这些领域及其相关指令。

与编译相关的指令

设计会随着时间推移而演进,并分阶段完成捕获。每当某个阶段稳定下来时,通常会希望将其与设计的其余部分隔离开来单独检查。在捕获过程的间歇阶段对单个原理图文档(或整个项目)进行编译,往往会产生一些错误消息,这些错误由尚未捕获的电路或仍未完成的电路片段之间的接口连线引起。这类消息并没有实际价值,因为它们只会掩盖真正有用的信息。抑制这些编译错误最快、最简单的方法,就是放置 No ERC 或 Compile Mask 指令。

No ERC 指令

No ERC 指令放置在电路中的某个节点上,用于抑制在验证原理图项目时检测到的所有电气规则检查(ERC)警告和/或错误违规条件 。更多信息请参阅 Validating Your Design Project 页面。

Compile Mask 指令

No ERC 指令非常适合用于抑制设计中少量违规的引脚、端口、页入口或网络。但在某些情况下,可能希望移除整个设计区域(包括元件)。使用 Compile Mask 指令(Place » Directives » Compile Mask command)或在 Active Bar 上的指令下拉菜单中单击 Compile Mask 按钮( ),即可有效地将其所包含的设计区域对编译器隐藏,从而手动阻止对尚未完成、且你知道会产生编译错误的电路进行错误检查。如果你需要编译当前文档或项目,以检查设计在其他特定区域的完整性,但又不希望看到与未完成部分相关的编译器消息“噪声”,这会非常有用。

),即可有效地将其所包含的设计区域对编译器隐藏,从而手动阻止对尚未完成、且你知道会产生编译错误的电路进行错误检查。如果你需要编译当前文档或项目,以检查设计在其他特定区域的完整性,但又不希望看到与未完成部分相关的编译器消息“噪声”,这会非常有用。

顾名思义,该指令会让编译器忽略任何落在 completely 所定义遮罩边界内的对象。放置遮罩的方式与放置注释或矩形对象完全相同。

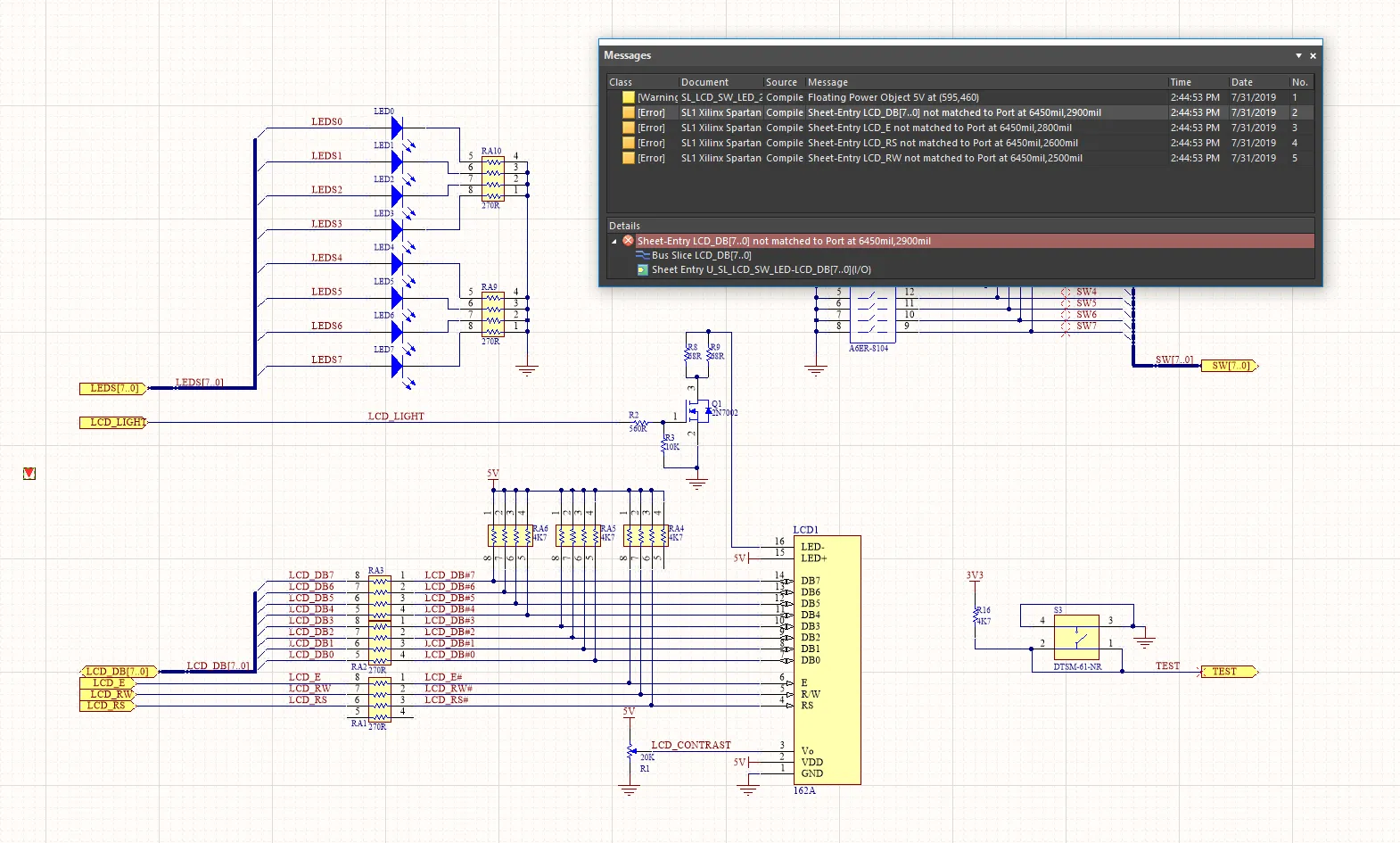

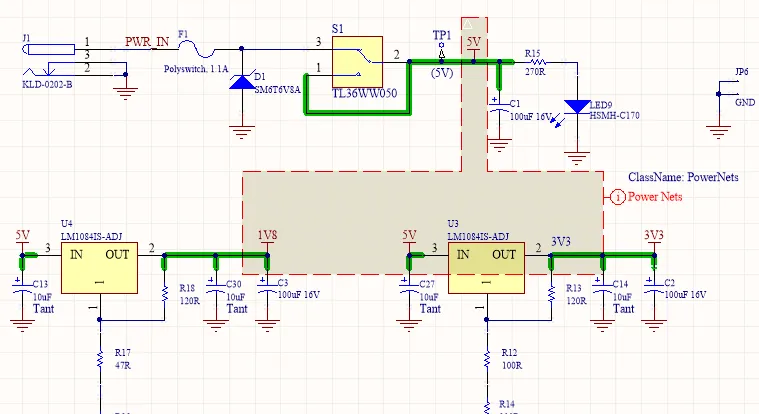

请看下图中的示例原理图电路,其中 LCD1 器件的连线尚未完成。仅编译此原理图(Project » Validate PCB Project)会产生大量违规消息(如下所示),每一条都由不完整的电路引起。将鼠标悬停在图像上可查看在不完整电路周围放置 Compile Mask 指令后的效果。这些违规将被编译器忽略,而原理图中其余已完全连线的电路仍会被检查。注意:真正被遮罩的对象——即完全落在遮罩边界矩形内的对象——会显示为灰色。

将鼠标移到图像上可显示使用 Compile Mask 指令隐藏因电路不完整而产生的编译器违规的效果。

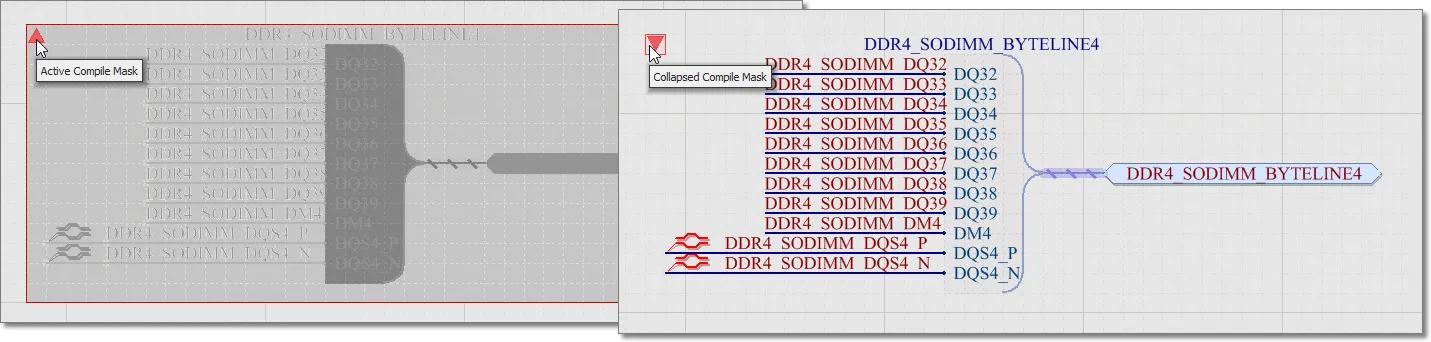

Compile Mask 可显示为展开(完整边框)或折叠(小三角形)两种模式。这两种模式分别对应遮罩启用与禁用。单击已放置 Compile Mask 左上角即可切换显示模式。当 仿真被纳入设计流程时,此功能会很有帮助:

learn more。

虽然 Compile Mask 可以旋转或沿 X/Y 轴镜像,但这不会影响其内部设计电路的方向。

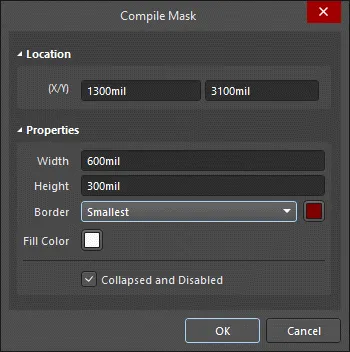

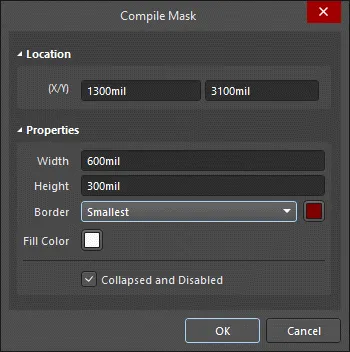

Compile Mask

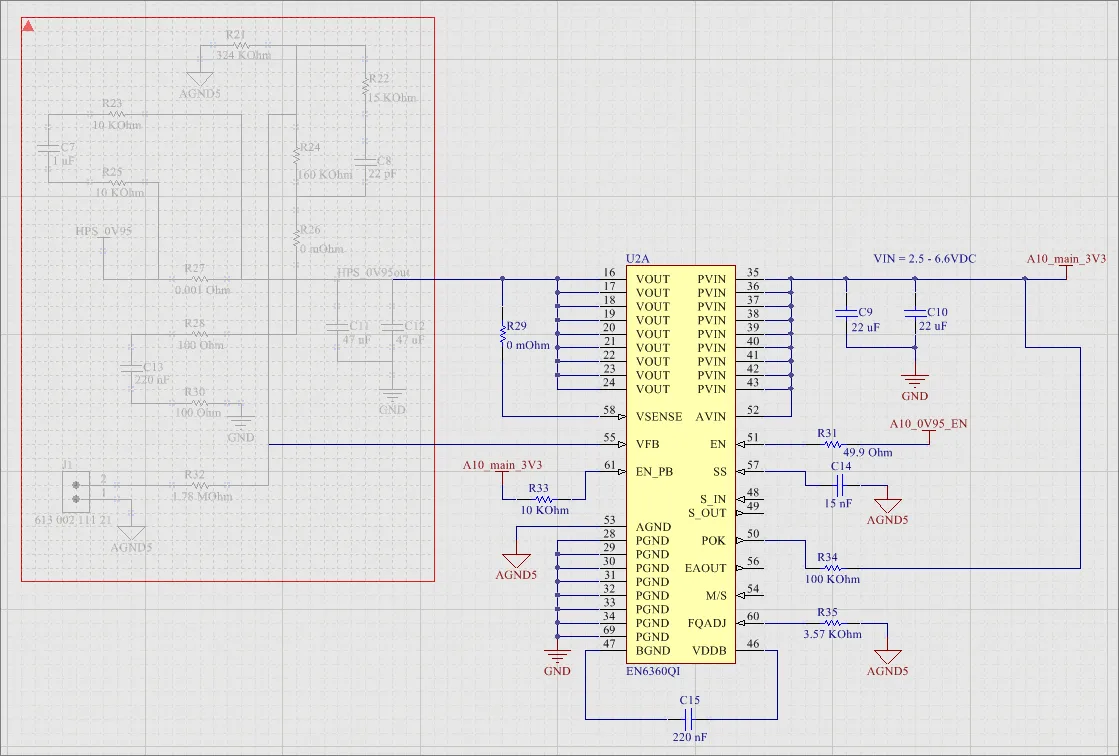

上方原理图左侧所示的已放置 Compile Mask。

上方原理图左侧所示的已放置 Compile Mask。

摘要

Compile Mask 是一种设计指令,在使用 Project » Validate Project command 执行验证时,用于有效地将其所包含的设计区域对编译器隐藏。它提供了一种手动方式,用于阻止对尚未完成且会产生验证错误的电路进行错误检查。当需要验证当前项目以检查设计在其他特定区域的完整性,但又不希望出现与未完成部分相关的编译器消息杂乱时,Compile Mask 非常有用。

尽管名为“Compile Mask”,该指令并不与编译动作本身相关——编译会在每次用户操作后自动执行,这得益于 Altium Designer 的动态编译(Dynamic Compilation)功能。Compile Mask 实际上是在你手动运行项目验证时才会生效;验证与编译是相互独立、不同的过程,并且需要用户手动触发。验证会结合

Project Options dialog 中

Error Reporting 与

Connection Matrix 选项卡上的设置,对项目内的原理图文档进行电气与制图错误检查。

可用性

Compile Mask 仅可在原理图编辑器中放置。要放置 Compile Mask:

-

从主菜单单击 Place » Directives » Compile Mask command。

-

在设计空间顶部的 Active Bar 上的指令下拉菜单中单击 Compile Mask 按钮(

)。单击并按住 Active Bar 按钮可访问其他相关命令。一旦某个命令被使用,它将成为该 Active Bar 区域中的最上层条目。

)。单击并按住 Active Bar 按钮可访问其他相关命令。一旦某个命令被使用,它将成为该 Active Bar 区域中的最上层条目。

-

在原理图编辑器中右键单击 然后单击 Place » Directives » Compile Mask。

放置

启动命令后,光标将变为十字准星 ,表示进入 Compile Mask 放置模式。放置时按以下步骤操作:

-

定位光标,然后单击或按 Enter 以锚定遮罩的第一个角点。

-

移动光标以调整遮罩大小,使其完全包围需要对编译器隐藏的设计区域,然后单击或按 Enter 锚定对角点并完成遮罩放置。完全落在遮罩边界内的设计对象将变为灰色显示。

-

继续放置更多 Compile Mask ,或右键单击或按 Esc 退出放置模式。

图形化编辑

该编辑方式允许你在设计空间中直接选择已放置的 Compile Mask 对象,并以图形方式更改其大小、形状或位置 。

Compile Mask 可显示为活动(完整边框)或折叠(带框三角形)两种模式,分别对应遮罩启用与禁用。单击已放置 Compile Mask 左上角的 ▲ 或 ▼ 图标即可切换显示模式。

单击左上角的三角形可折叠(并禁用)Compile Mask。

单击左上角的三角形可折叠(并禁用)Compile Mask。

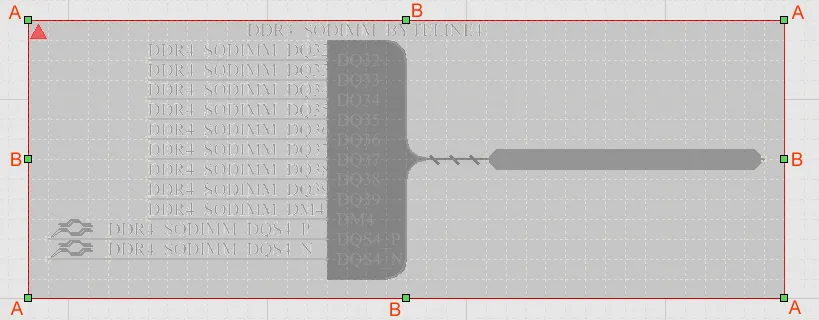

当选中一个活动(展开)的 Compile Mask 对象时,可使用以下编辑控柄:

被选中的 Compile Mask(处于活动状态时)。

被选中的 Compile Mask(处于活动状态时)。

-

单击并拖动 A 可同时在垂直与水平方向调整 Compile Mask 的大小。

-

单击并拖动 B 可分别在垂直与水平方向调整 Compile Mask 的大小。

-

在 Compile Mask 上任意位置单击(避开编辑控柄) 并拖动以重新定位。拖动时,Compile Mask 可旋转(Spacebar/Shift+Spacebar)或镜像(按 X 或 Y 键分别沿 X 轴或 Y 轴镜像)。

请注意:当 Compile Mask 处于折叠状态时,只能通过拖动到新位置来以图形方式更改其位置 。

如果尝试以图形方式修改启用了 Locked 属性的对象,将弹出对话框要求确认是否继续编辑。如果在 Preferences dialog 的 Schematic – Graphical Editing 页面上启用了 Protect Locked Objects 选项,并且该设计对象的 Locked 选项也已启用,则该对象无法被选择或进行图形化编辑。单击 被锁定的对象以选中它,然后在 List panel 中禁用 Locked 属性,或禁用 Protect Locked Objects 选项,以便对对象进行图形化编辑。

非图形化编辑

可使用以下非图形化编辑方法。

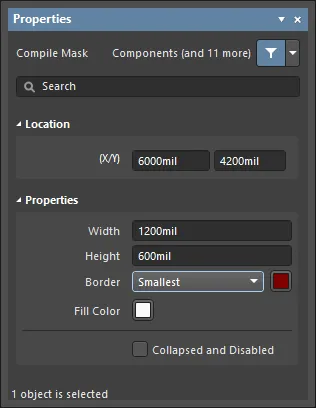

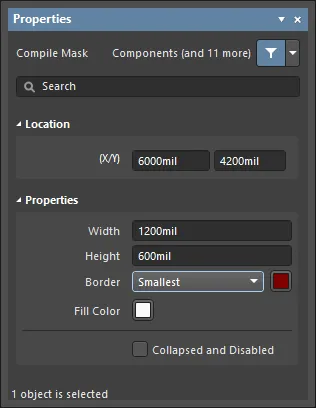

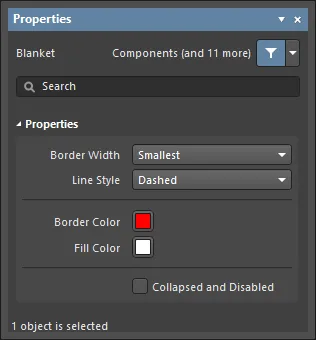

通过 Compile Mask 对话框或 Properties 面板进行编辑

Panel page: Compile Mask Properties该编辑方法使用关联的 Compile Mask dialog 以及 Properties panel 模式来修改 Compile Mask 对象的属性。

放置后,可通过以下方式访问 Compile Mask dialog:

-

双击已放置的 Compile Mask 对象。

-

选中 Compile Mask 对象,右键单击,然后从上下文菜单中选择 Properties。

放置过程中,可按 Tab 键访问 Properties panel 的 Compile Mask 模式。放置完成后,将显示所有选项。

放置后,可通过以下方式之一访问 Properties panel 的 Compile Mask 模式:

-

如果 Properties panel 已处于活动状态,选中 Compile Mask 对象即可。

-

选中 Compile Mask 对象后,通过设计空间右下角的 Panels button 选择 Properties panel,或从主菜单选择 View » Panels » Properties。

如果在

Preferences dialog 的

Schematic - Graphical Editing page 上禁用

Double Click Runs Interactive Properties 选项(默认),当双击该图元,或在选中的图元上右键并选择

Properties 时,将打开该对话框。当启用

Double Click Runs Interactive Properties 选项时,将打开

Properties panel。

尽管对话框与面板中的选项相同,但选项的顺序和位置可能会略有不同。

编辑多个对象

Properties panel 支持多对象编辑,即可修改当前所选全部对象中“相同”的属性设置。当手动选择多个相同对象类型,或通过 Find Similar Objects dialog,或通过 Filter 或 List panel 进行选择时,Properties panel 中未显示为星号(**)的字段项,都可以对所有选中对象进行编辑。

通过列表面板编辑

Panel pages: 列表面板、SCH Filter

一个 List panel 以表格形式显示来自一个或多个文档的设计对象类型,便于快速检查与修改对象属性。结合适当的过滤方式——通过选择对象类型(使用该面板的 Include 选项),或使用相应的 Filter panel 或 Find Similar Objects dialog——即可仅显示落在当前活动过滤范围内的对象。随后可直接在 List panel 中编辑所列对象的属性。

Compile Mask Properties

Schematic Editor 对象属性是一些可定义选项,用于指定已放置对象的视觉样式、内容与行为。每种对象类型的属性设置按如下方式定义:

-

Post-placement settings – 当在设计空间中选中已放置的 Compile Mask 时,所有 Compile Mask 对象属性都可在 Compile Mask dialog 和 Properties panel 中编辑。

尽管对话框与面板中的选项相同,但选项的顺序和位置可能会略有不同。

位置

-

(X/Y)

-

X (第一个字段)- 对象参考点相对于当前设计空间原点的当前 X(水平)坐标。编辑以更改对象的 X 位置。数值可用公制或英制输入;当输入的单位不是当前默认单位时,请在数值中包含单位。

-

Y (第二个字段)- 对象参考点相对于当前原点的当前 Y(垂直)坐标。编辑以更改对象的 Y 位置。数值可用公制或英制输入;当输入的单位不是当前默认单位时,请在数值中包含单位。

属性

-

Width - 输入对象的宽度。

-

Height - 输入对象的高度。

-

Border - 使用下拉列表选择所需的边框。

-

Fill Color - 单击颜色框为对象选择所需颜色。

-

Collapsed and Disabled - 勾选该复选框以折叠并禁用该对象。

与 PCB 相关的指令

作为统一设计环境,Altium Designer 允许在进行板级布局之前先定义 PCB 需求。这通过在原理图页上放置的对象中添加并指定参数来实现。

对于某些原理图设计对象——例如元件、页符号、端口等——这意味着将相关参数作为该对象属性的一部分来添加。对于导线和总线等网络对象,无法直接将参数作为导线或总线的属性添加。相反,用于承载这些信息所需的参数,是通过专用的设计指令来指定的。

以下信息可通过指令进行指定,并会在设计同步期间传递到相应的基于 PCB 的定义中:

通过在原理图中包含设计指令,设计工程师可以指定明确的设计约束,并确保原理图始终作为设计的主记录。对设计的任何修改都只需在原理图端完成,然后推送到 PCB。当多人协同设计时——尤其是异地协作——这一点会变得尤为重要。与其通过一连串邮件或电话来沟通,负责原理图录入的人可以确保在布局阶段确实会使用特定约束。

该功能的核心是 Parameter Set directive。

这些本质上是用户自定义的 Parameter Set 对象,可与原理图设计中的网络对象关联。将 PCB Layout 指令放置在导线、总线或信号线束上,以定义一个或多个面向相关网络的设计约束。当从原理图创建 PCB 时,PCB layout 指令中的信息会用于创建相应的 PCB 设计规则。PCB Layout 指令所指定的信息仅应用于该指令所连接的网络(或网络集合)。

一个 Parameter Set 指令。

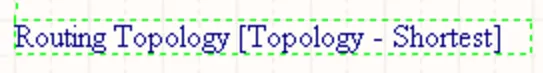

它充当一个容器,可包含任意数量、面向该 Parameter Set 指令所附着网络的参数。可以放置一个不含参数的默认 Parameter Set 指令(Place » Directives » Parameter Set) ,并在之后再添加相关参数。以下各节将更深入地介绍如何使用这些基于参数的指令。既提供用户自定义(Parameter Set)也提供预定义(Differential Pair)的参数集指令。空参数集与预定义参数集的唯一区别在于:预定义参数集包含一个参数,具体如下所述。

Moving from Directives to the Constraint Manager

最初定义设计需求的方法,是在原理图编辑器与 PCB 编辑器中分别处理:在原理图编辑器中用 Directives 定义,在 PCB 编辑器中用 Design Rules 定义。随着 Constraint Manager 的引入,这种分离已得到解决。Constraint Manager 是一个用于定义设计需求的独立编辑器,允许在设计流程的任何阶段进行配置与编辑。对于同一个项目只能使用一种方式;一个简单的检查方法是查看 Design menu 中是否有 Constraint Manager 条目。如果没有(而是在 PCB 编辑器 Design menu 中有 Rules 条目),则该项目使用的是较旧的 Design Rules 方法。

如果正在使用 Constraint Manager,则通过 parameter set 与 differential pair 指令定义的网络类、差分对、差分对类以及规则,在从原理图更新 PCB 时将not不会被检测并传递。只会传递在 Constraint Manager 中定义的网络类、差分对、差分对类以及规则。

请注意:当从原理图访问 Constraint Manager 的 Physical 或 Electrical 视图时,可通过其右键菜单中的 Import from Directives 命令,从放置在原理图中的指令导入 规则、网络类、差分对以及差分对类—— 了解更多。另请注意:从指令导入数据到 Constraint Manager 并保存这些更改后,导入的指令会在原理图设计空间中以蓝色显示(符号也会略有不同)。这表示已完成从指令到 Constraint Manager 的单向转换,蓝色指令将变为只读对象(不允许进一步编辑)。

Parameter Set

Parameter Set

概要

参数集是一种设计指令,用于将设计规范与原理图设计中的网络类型对象关联。例如,可使用参数集声明两条网络属于同一差分对。软件正是通过参数集中具有特定命名的参数,来判断你正在放置哪一种设计指令。

可用性

参数集仅可在原理图编辑器中放置。提供默认(空)与预定义(Differential Pair)两种参数集指令。空参数集与预定义参数集的唯一区别在于:预定义参数集包含一个参数,如下所述。

可从主 Place menu 按如下方式访问相应命令:

| • |

Place » Directives » Parameter Set |

|

| • |

Place » Directives » Differential Pair |

|

放置

参数集可用于向以下对象附加参数:

启动命令后,光标将变为十字准星,并进入设计指令放置模式。放置可通过以下操作完成:

-

将光标移到导线或其他网络对象上方,单击或按 Enter 放置。

-

继续放置更多指令,或右键单击或按 Esc 退出放置模式。

放置过程中还可执行的其他操作 – 当参数集仍悬浮在光标上时包括:

-

按下 Tab 键可暂停放置,并进入 Properties 面板的 Parameter Set mode ,从而可在放置过程中随时更改其属性。单击设计空间中的暂停按钮叠加层( )以继续放置。

)以继续放置。

-

按下 Alt 键可将移动方向约束为水平轴或垂直轴,具体取决于初始移动方向。

-

按下 Spacebar 可将圆弧逆时针旋转,或按 Shift+Spacebar 顺时针旋转。该操作也可在拖动对象时执行。旋转以 90° 为增量。

-

在放置模式下按 X 或 Y 键,可沿 X 轴或 Y 轴翻转参数集。

虽然在放置过程中可以修改属性(

Tab 以打开

Properties 面板),但请注意:除非在

Preferences 对话框的

Schematic – Defaults page 上启用了

Permanent 选项,否则这些修改将成为后续放置的默认设置。启用该选项后,所做更改只会影响正在放置的对象,以及同一次放置会话中随后放置的对象。

Graphical Editing

这种编辑方法允许你在设计空间中直接选择已放置的参数集指令,并以图形方式更改其位置或方向。

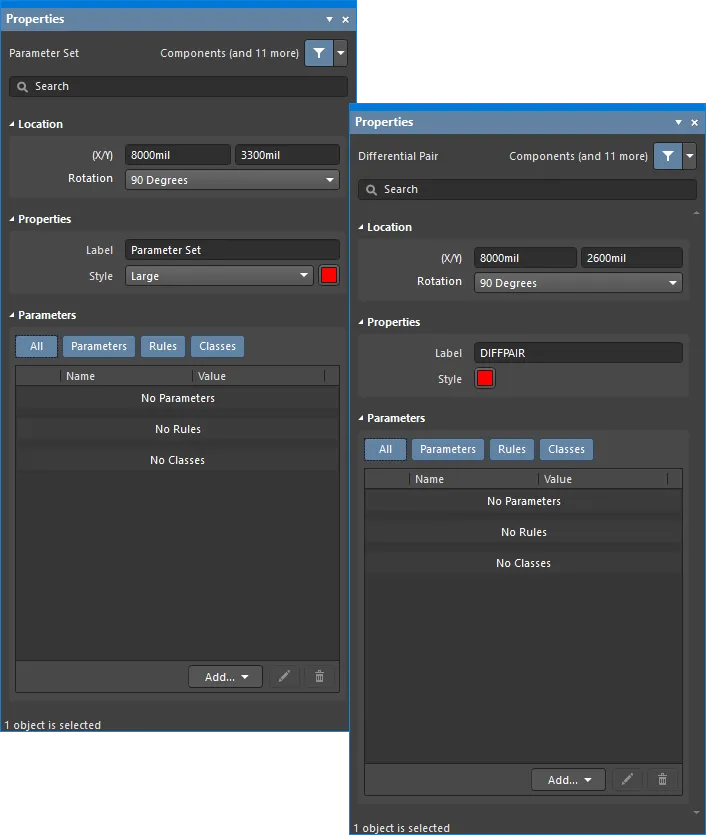

当在设计空间中选中参数集指令时,指令周围会出现一个虚线框。该框仅包围指令所占用的区域。对于参数集中每个启用了可见性的成员参数,会显示一条虚线,将参数的文本字段连接到指令主体,以确认其关联关系:

在虚线框内任意位置单击并拖动,可按需重新定位参数集。拖动时,可旋转参数集(Spacebar/Shift+Spacebar)或镜像(按 X 或 Y 键沿 X 轴或 Y 轴镜像)。

参数集的 文本字段(可独立于父指令进行图形编辑) 只能通过更改 Preferences 对话框的 Schematic – Defaults page 上的 Style 选项来调整其大小。因此,当选中这些对象时不会提供编辑手柄。

在虚线框内任意位置单击并拖动,可按需重新定位文本对象。拖动时,可旋转文本对象(Spacebar/Shift+Spacebar)或镜像(按 X 或 Y 键沿 X 轴或 Y 轴镜像)。

如果在 Preferences 对话框的 Schematic – General page 上启用了 Enable In-Place Editing 选项,则可以在设计空间中直接编辑参数值(作为规则添加的参数除外)。选择文本对象后再单击一次以调用该功能。按需输入新值,然后单击文本对象外部或按 Enter 以使更改生效。

如果尝试以图形方式修改启用了 Locked 属性的对象,将弹出对话框要求确认是否继续编辑。如果在 Preferences 对话框的 Schematic – Graphical Editing 页面上启用了 Protect Locked Objects 选项,并且该设计对象的 Locked 选项也已启用,则该对象无法被选择或进行图形编辑。单击被锁定的对象以选中它,然后在 List 面板中禁用 Locked 属性,或禁用 Protect Locked Objects 选项以对对象进行图形编辑。

Non-Graphical Editing

提供以下非图形编辑方法。

Editing via the Parameter Set Dialog or Properties Panel

Panel page: Parameter Set Properties

此编辑方法使用关联的 Parameter Set 对话框以及 Properties 面板模式来修改参数集对象的属性。

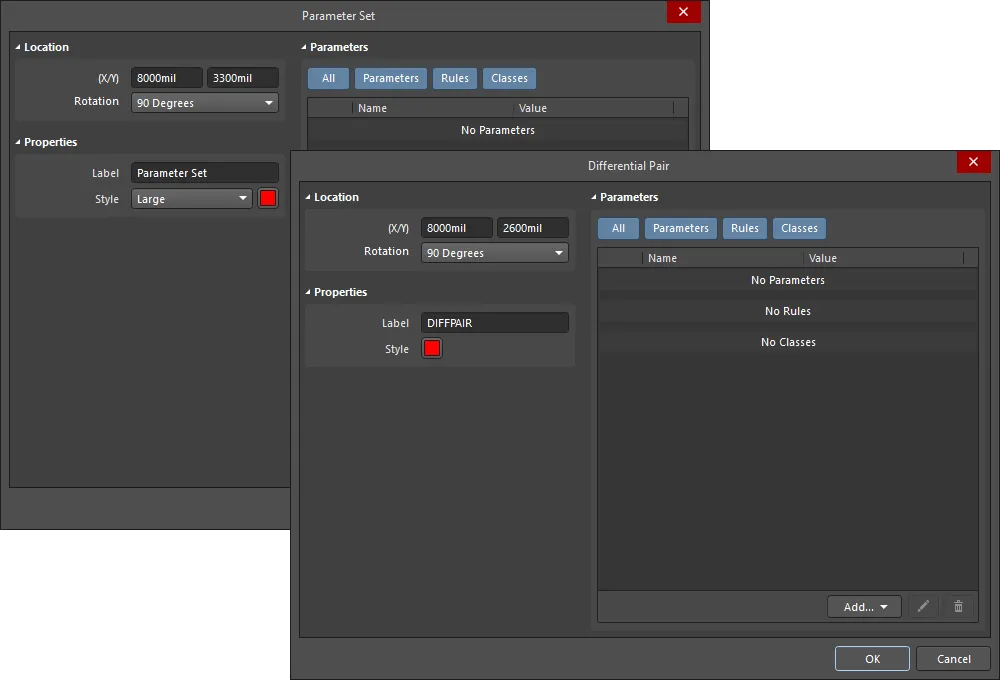

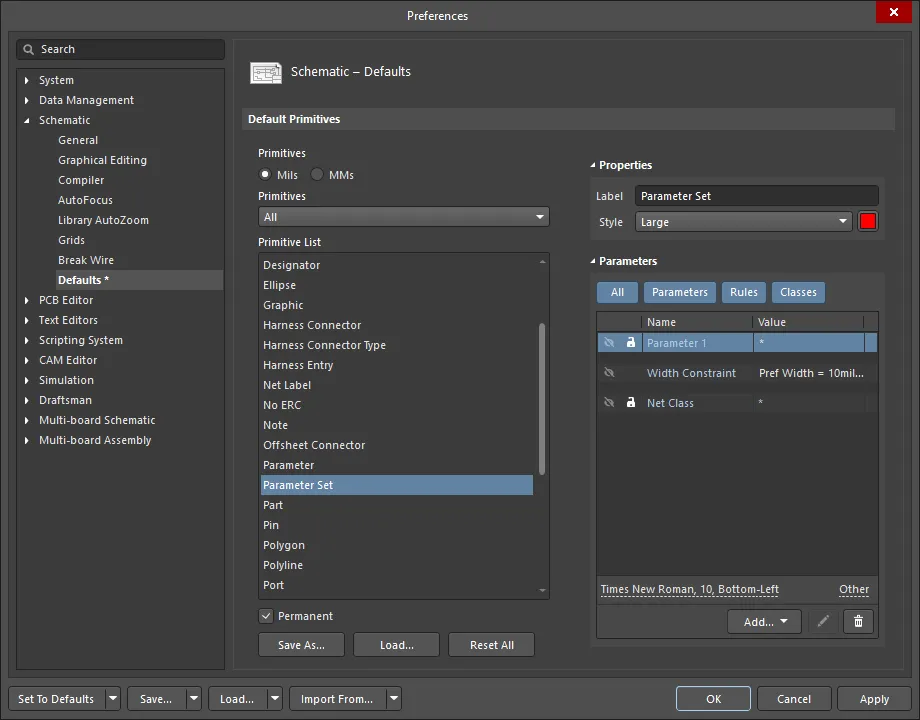

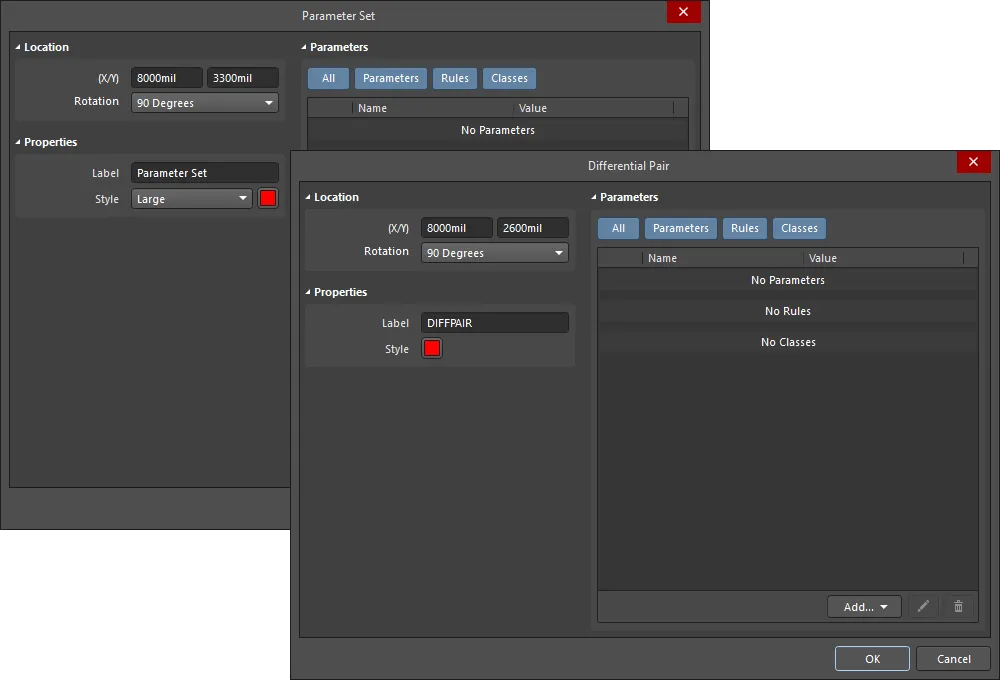

第一张图中的 Parameter Set dialog ,以及第二张图中 Properties 面板的 Parameter Set mode

放置完成后,可通过以下方式访问 Parameter Set 对话框:

-

双击已放置的参数集对象。

-

将光标悬停在参数集对象上,右键单击,然后从上下文菜单中选择 Properties。

在放置过程中,可按 Tab 键访问 Properties 面板的 Parameter Set 模式。参数集放置完成后,将显示所有选项。

放置完成后,可通过以下方式之一访问 Properties 面板的 Parameter Set 模式:

-

如果 Properties 面板已处于活动状态,选择参数集对象即可。

-

选中参数集对象后,通过设计空间右下角的 Panels 按钮选择 Properties 面板,或从主菜单选择 View » Panels » Properties。

如果在

Preferences dialog 的

Schematic – Graphical Editing page 上禁用了

Double Click Runs Interactive Properties 选项(默认),当双击该图元或在选中图元后右键并选择

Properties 时,将打开对话框。启用

Double Click Runs Interactive Properties 选项时,将打开

Properties panel。

Editing Multiple Objects

Properties 面板支持多对象编辑:可修改当前所选对象中所有对象都相同的属性设置。当通过手动选择、使用 Find Similar Objects dialog,或通过 Filter/List 面板选择多个同类型对象时,Properties 面板中未显示为星号(*)的字段条目可对所有选中对象进行编辑。

Editing via a List Panel

Panel pages: List Panels、SCH Filter

一个 List 面板可将一个或多个文档中的设计对象以表格形式显示,从而便于快速检查与修改对象属性。结合适当的过滤(使用相应的 Filter panel 或 Find Similar Objects dialog),它可以仅显示落在当前活动过滤范围内的对象——从而让你更准确、更高效地定位并编辑多个设计对象。

Notes

Parameter Set Properties

原理图编辑器对象属性是一些可定义的选项,用于指定已放置对象的视觉样式、内容和行为。

每种对象类型的属性设置通过两种不同方式定义:

-

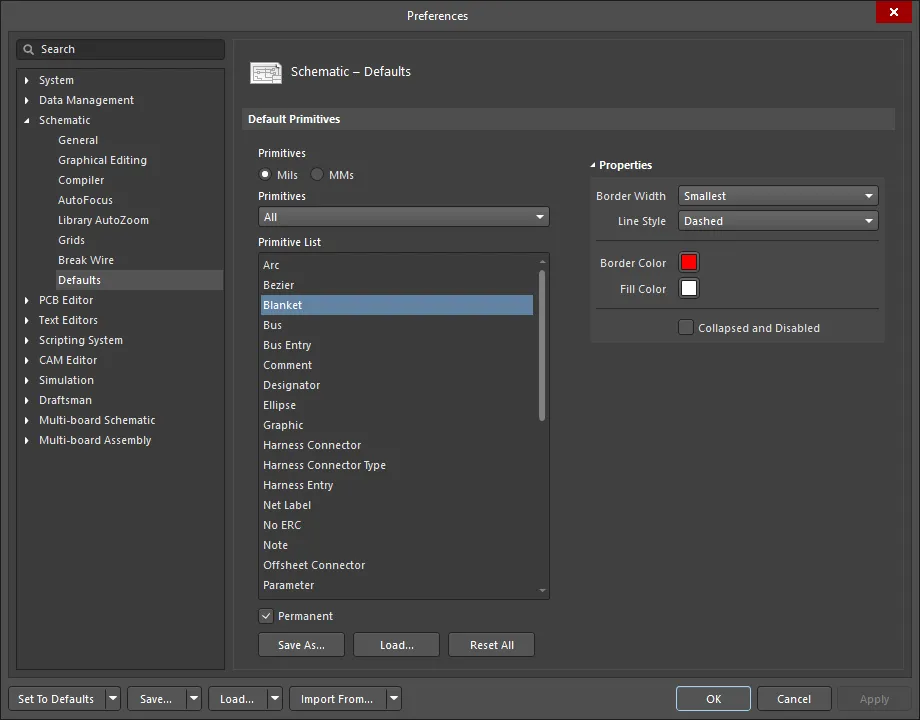

Pre-placement settings – 大多数 Parameter Set 对象属性(或那些在逻辑上可预先定义的属性)可在 Schematic – Defaults page 的 Preferences dialog(通过设计空间右上角的  按钮进入)中作为可编辑的默认设置提供。选择 Primitive List 中的对象,即可在右侧显示其选项。

按钮进入)中作为可编辑的默认设置提供。选择 Primitive List 中的对象,即可在右侧显示其选项。

-

Post-placement settings – 当在设计空间中选中 Parameter Set 时,所有 Parameter Set 对象属性都可在 Parameter Set dialogs 和 Properties panel 中进行编辑。

如果在

Preferences dialog 的

Schematic – Graphical Editing page 上禁用了

Double Click Runs Interactive Properties 选项(默认),当双击该图元,或在选中图元后右键并选择

Properties 时,将打开对话框。当启用

Double Click Runs Interactive Properties 选项时,将打开

Properties panel。

尽管对话框与面板中的选项相同,但选项的顺序和位置可能会略有不同。

在下面的属性列表中,无法作为 Preferences dialog 默认设置提供的选项会标注为“Properties panel only”。

Location

-

(X/Y)

-

X (第一个字段)– 对象参考点相对于当前设计空间原点的当前 X(水平)坐标。编辑以更改对象的 X 位置。数值可用公制或英制输入;当输入的单位不是当前默认单位时,请在数值中包含单位。

-

Y (第二个字段)– 对象参考点相对于当前原点的当前 Y(垂直)坐标。编辑以更改对象的 Y 位置。数值可用公制或英制输入;当输入的单位不是当前默认单位时,请在数值中包含单位。

-

Rotation – 使用下拉菜单选择旋转角度。

Properties

-

Label – 参数集标签。如有需要可编辑。

-

Style – 使用下拉菜单选择样式。单击颜色框可打开下拉列表,从中选择默认颜色。

Parameters

-

Grid – 列出与当前所选参数关联的参数 Name 和 Value。添加后,Name 和 Value 字段可编辑。可通过单击 Value 字段并输入所需文本来命名 Value。Name 字段只能在 Parameter Set 对象的 Properties panel 模式下通过 Ctrl+Click 来更改。此方法会打开 Properties panel 的 Parameter 模式,你可以在 Name 字段中输入所需名称。使用锁定图标(

)锁定/解锁列表中的参数。使用眼睛图标显示/隐藏参数。可通过切换 All 以及各个参数按钮,在该区域显示全部、单个或不显示任何参数。当相应按钮为灰色时参数被禁用,为蓝色时参数被启用。

)锁定/解锁列表中的参数。使用眼睛图标显示/隐藏参数。可通过切换 All 以及各个参数按钮,在该区域显示全部、单个或不显示任何参数。当相应按钮为灰色时参数被禁用,为蓝色时参数被启用。

-

Add – 使用下拉菜单添加一种 class 类型:

-

Net Class – 选择以添加新的 net class。

-

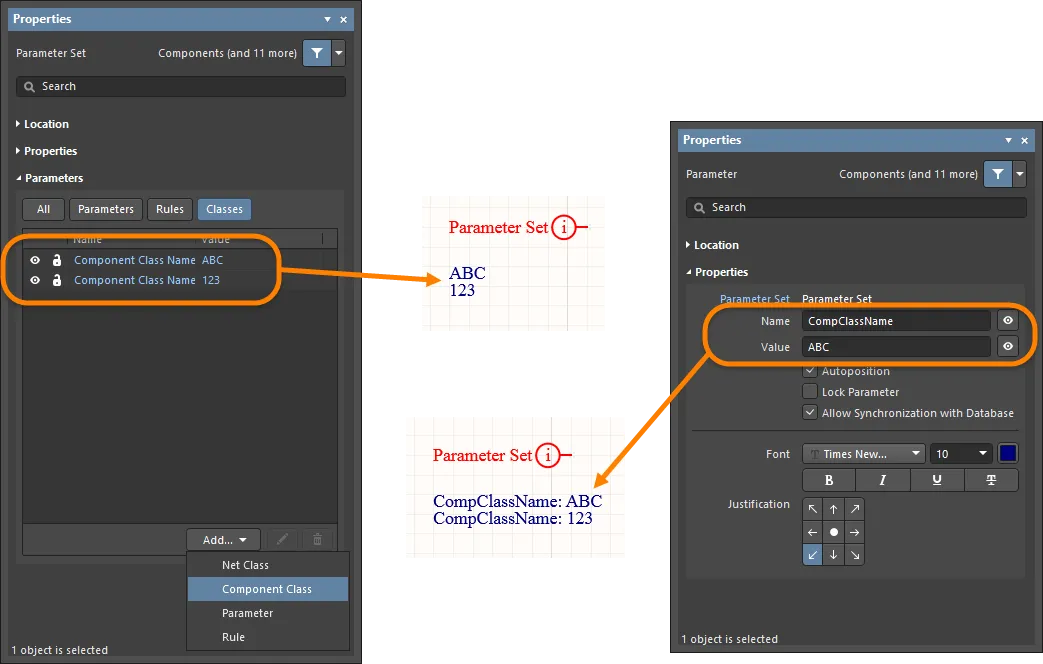

Component Class – 选择以添加新的 component class。 此选项仅可在 Parameter Set dialog 或 Properties panel 的 Parameter Set 迭代中访问。

你可以添加一个新的 class Component Class Name,用于为 blanket 内的组件设置参数。将 Component Class Name 与某个组件(或一组组件)关联后,会将组件 class 的信息(其名称与成员)发送到 PCB,方式与当前对 Net Classes 的处理相同。

-

Diff. Pair Net Class – 选择以添加新的 differential pair net class。此选项仅可在 Parameter Set dialog 或 Properties panel 的 Differential Pair 迭代中访问。

-

Parameter – 选择以添加新参数。

-

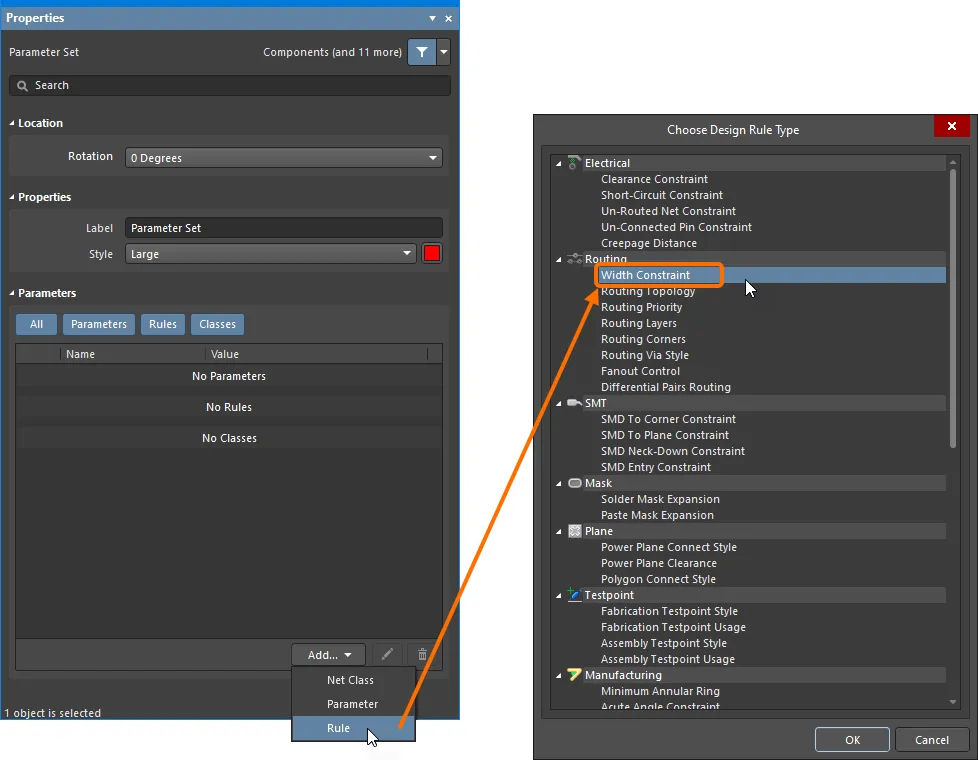

Rule – 单击以打开

![]() Choose Design Rule Type dialog ,在其中可选择一条新规则。选择新规则后单击 OK,将打开 Edit PCB Rule (From Schematic) dialog,以便按需编辑新规则。

Choose Design Rule Type dialog ,在其中可选择一条新规则。选择新规则后单击 OK,将打开 Edit PCB Rule (From Schematic) dialog,以便按需编辑新规则。

请注意:在通过

importing data from directives to the Constraint Manager 同步数据并在

Constraint Manager 中保存更改后,用于添加新项或编辑/移除现有 net class、diff pair class、component class 或 rule 的控件,会在相应 directives 的

Properties panel 中变为灰色不可用。导入到

Constraint Manager 的条目在 directive 属性中将基本变为只读,你可以使用

Constraint Manager 按钮(位于

Properties panel 的

Parameters 区域顶部)将其过滤掉。

单击铅笔( )图标打开 Edit PCB Rule (From Schematic) dialog 以编辑所选项。单击

)图标打开 Edit PCB Rule (From Schematic) dialog 以编辑所选项。单击  删除所选项。

删除所选项。

-

Font Settings – 单击显示的字体以更改字体样式。只有在已添加 net class、differential pair net class、parameter 或 rule 后,此选项才可用。

-

Other – 如果已添加 net class、differential pair net class、parameter 或 rule,单击以打开下拉菜单来更改其他选项:

-

Show Parameter Name – 启用以显示参数名称。

-

Allow Synchronization with Database – 启用以与数据库同步。

-

X/Y – 输入 X 和 Y 坐标。

-

Rotation – 使用下拉菜单选择旋转角度。

-

Autoposition – 勾选以启用自动定位。

放置 Parameter Set 指令

通过主菜单选择 Place » Directives » Parameter Set 命令,或在设计空间内右键时,放置此类型的指令。放置默认的参数集指令时,不会包含任何现有参数。参数集是一种设计指令,允许将设计规范与原理图设计中的 net 类型对象关联。例如,可使用参数集声明两条网络为差分对的成员。软件正是通过参数集中具有特定名称的参数来判断你正在放置哪一种设计指令。

除用户自定义的参数指令外,还可从 Choose Design Rule Type dialog 定义基于规则的参数指令;该对话框可从参数关联的 Properties panel 模式进入。访问步骤如下:

-

在放置 Parameter Set 之前按下 Tab,或双击已放置的 Parameter Set directive ,以显示 Properties panel 的 Parameter Set mode。

-

接着,在 Properties panel 的 Parameter Set mode 的 Parameters 区域中单击 Add 按钮,并从下拉菜单中选择 Rule,以在 Choose Design Rule Type dialog 中选择一条规则。

编辑规则的值。

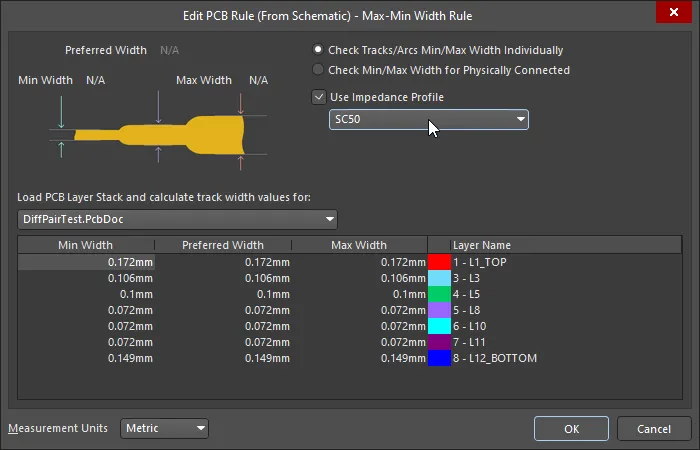

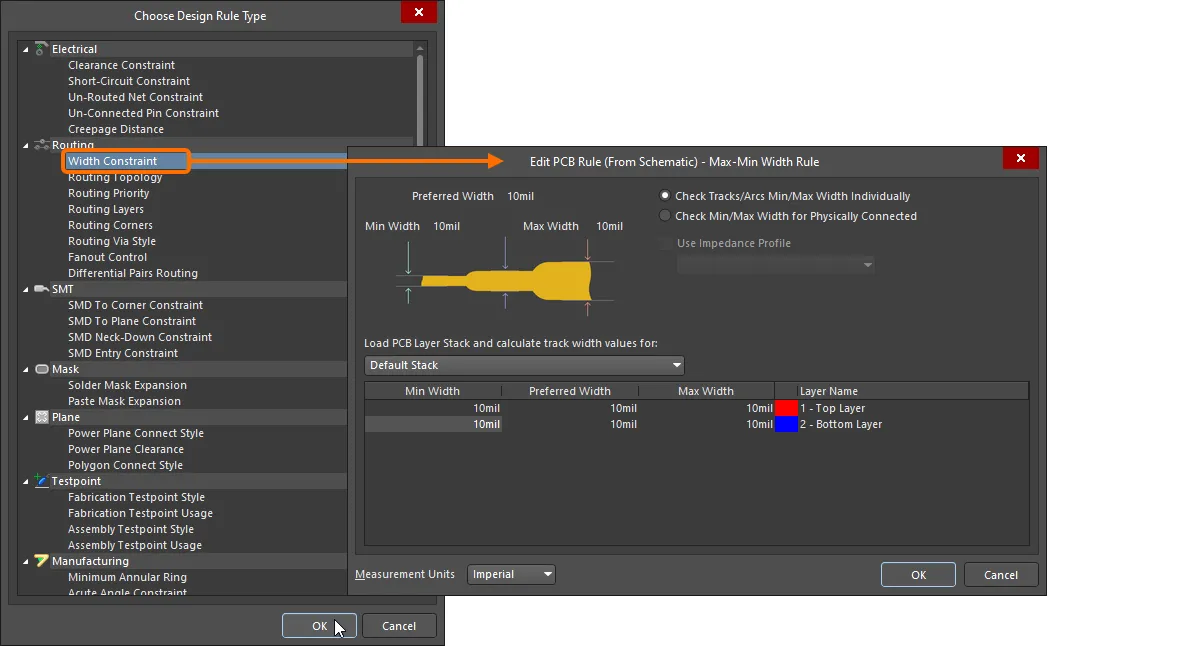

使用 Choose Design Rule Type dialog 选择你希望作为规则参数添加到该指令中的规则。双击某个规则类型将打开相应的 Edit PCB Rule (From Schematic) dialog,你可以在其中定义该规则的约束条件。

Edit PCB Rule (From Schematic) dialog 中呈现的具体属性取决于所选设计规则,并且与 PCB 编辑器中为该规则定义的属性相同。

例如,下图显示了 Max-Min Width Rule 的 Edit PCB Rule (From Schematic) dialog,你可以:为所有层配置 Min/Preferred/Max 设置;为每一层手动定义各自的宽度设置;或选择使用 Impedance Profile。如果你选择阻抗配置文件,并且 PCB 编辑器中已定义实际的物理板结构,你还可以选择板文件以 Load the PCB Layer Stack and calculate the track width values。

如果 PCB 已存在且已定义层叠结构,则可将计算得到的线宽加载到原理图中。

如果 PCB 已存在且已定义层叠结构,则可将计算得到的线宽加载到原理图中。

上述规则应用于一个网络类。这是通过放置一个 Blanket Directive 并附加一个 PCB Routing Directive 来将网络分组为一个类,然后对该类应用 Max-Min Width Rule(show image![]() )来实现的。

)来实现的。

有关每条 PCB 设计规则与约束的详细信息,请单击 此处。

使用 Measurement Units 下拉字段选择 Metric 或 Imperial 单位。

为所选规则指定约束。

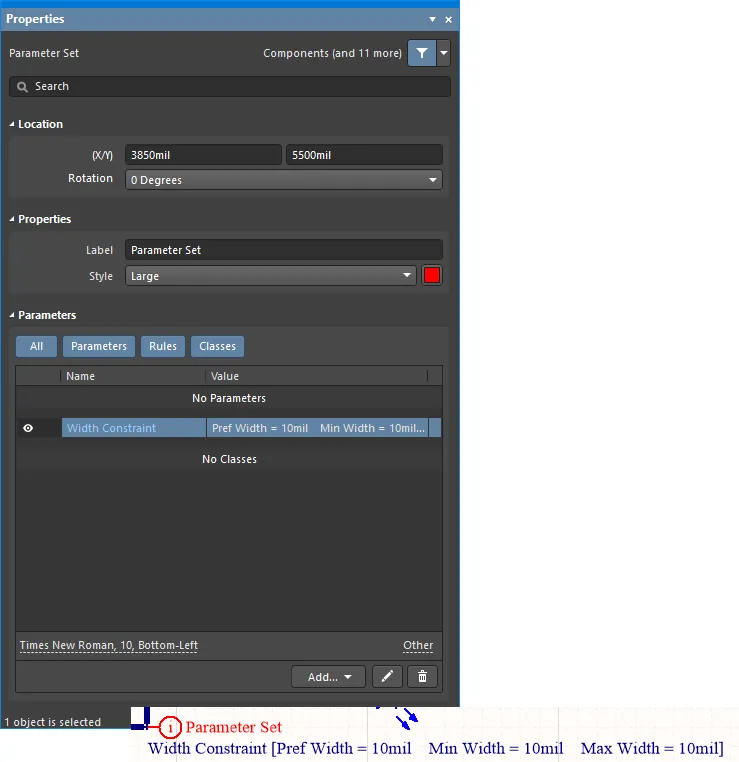

在 Parameters 区域中的条目将是所选的规则类型以及所指定的约束。下图展示了针对 Parameter Set 指令所定义的线宽约束规则参数。要在设计空间中显示该规则,请单击 Rules 区域内的可见性( )图标。

)图标。

为特定网络定义的多个规则约束,来自 Parameter Set 指令。

当通过同步过程将设计传输到 PCB 时,将根据指令中包含的信息创建相应的设计规则。每条生成规则的名称中都会使用 Schematic 一词,以区分该规则的来源。

PCB 端生成的设计规则。

请记住,可以向同一个 Parameter Set 指令添加多个参数,从而使原理图更整洁。

放置 Net Class 指令

Net Class 指令使你能够在原理图中创建用户自定义的网络类。可通过从主菜单选择 Place » Directives » Parameter Set 命令来放置 Net Class 指令,然后按该命令页面的提示 #2 所述,将参数集定义为 Net Class 指令。从原理图创建 PCB 时,Net Class 指令中的信息将用于在 PCB 上创建对应的 Net Class。要让某个网络成为某个网络类的成员,请将 Net Class 指令附加到相关的导线、总线或信号线束上,然后将该指令的 ClassName 参数设置为所需类的名称。要使用此功能,必须在 Project Options 对话框的 Class Generation 选项卡 中启用 Generate Net Classes 选项(用于用户自定义类)。

如果已为某个网络定义了 Net Class 指令,那么当设计传输到 PCB 编辑器时,由该参数集对象同时创建的任何 PCB 设计规则,其规则作用域将为 Net Class 。可以通过在已放置的 Parameter Set 指令中添加一个类来创建 Net Class 指令,并将该类的值设置为所需的 PCB Net Class。

虽然可以在 PCB 编辑器中创建 Net Class,但网络的逻辑功能或分组通常在原理图中更清晰,因此从原理图驱动该流程通常更合理。

当通过同步过程将设计传输到 PCB 时,将根据指令中包含的信息创建相应的网络类。

将 Net Class 指令附加到

Blanket 对象,可创建一个网络类,其成员为该 Blanket 覆盖的各个网络。如果该 Blanket 上还附加了 PCB Layout 指令,则 PCB Layout 指令的规则参数将以该网络类为目标,而不是以每个单独网络为目标。将更改导入 PCB 文档时,这会导致每个参数只创建一条设计规则,并将作用域设置为目标网络类。

放置 Blanket 指令

Parameter Set 指令只能作用于其所附加的特定网络,但与 Blanket 指令结合使用时,其作用域可扩展为覆盖 Blanket 内的所有网络。

通过从主菜单选择 Place » Directives » Blanket 命令来放置此类指令。放置 Blanket 时,你可以定义简单的矩形形状或多边形形状。后者能更精确地控制对页面上所需网络对象的覆盖范围。

Blanket 用于标识关注的网络——在 Blanket 边缘的任意位置放置一个 Parameter Set 指令,即可将设计要求应用到这些网络。要将周界指令应用到 Blanket 指令下的某个网络,与该网络相关联的对象——引脚、端口、网络标号、电源端口、导线/总线/线束段(包括两端)——必须落在 Blanket 的边界内。注意,对于网络标识符(如网络标号),其热点必须位于 Blanket 内。如果成员网络未按预期进入 PCB Parameter Set,请相应调整 Blanket 的覆盖区域。

要检查 Blanket 指令将应用到哪些网络,请使用

Net Colors 功能将其高亮显示。从

View » Set Net Colors 菜单中选择所需颜色,然后单击所需 Blanket 指令的周界。要清除特定网络的高亮显示,请使用

View » Set Net Colors » Clear Net Color 命令,然后单击你希望移除着色的网络。要清除所有原理图页面上的网络着色,请使用

View » Set Net Colors » Clear All Net Colors 命令。

使用 Blanket 指令将 Parameter Set 指令应用到 Blanket 内网络的示例。

Blanket 指令的示例用法包括:

-

将 Parameter Set 指令附加到 blanket 对象,使其规则参数应用到该 blanket 覆盖的每个单独网络。

-

将 Parameter Set 指令附加到 blanket 对象,以创建一个 Parameter Set,其成员为该 blanket 覆盖的各个网络。

-

将 Differential Pair 指令附加到 blanket 对象,以基于该 blanket 范围内的差分网络创建差分对对象。

将 Parameter Set 指令附加到

Blanket 对象 ,使其规则参数应用到该 blanket 覆盖的每个单独网络。如果该 blanket 上还附加了 Parameter Set 指令,并且该 Parameter Set 也包含 Net Class 参数,则 Parameter Set 指令的规则参数将以该网络类为目标,而不是以每个单独网络为目标。将更改导入 PCB 文档时,这会导致每个参数只创建一条设计规则,并将作用域设置为目标网络类。

你也可以复制一个周界 Parameter Set 指令,并将其附加到另一个 Blanket 指令,甚至附加到单独的导线、总线或线束上——结果是:与同一生成的 PCB Net Class 相关联的所有新增网络,都会被添加到同一个由该 Parameter Set 指令生成的 PCB Net Class 中。

Blanket 与 Parameter Set 指令结合使用时,也可用于为完全位于 Blanket 定义区域内的器件应用器件类与器件参数。为此,请在附加到 Blanket 的 Parameter Set 指令属性中,使用 Add 按钮下拉菜单中的 Component Class 和 Parameter 选项。关于器件类与参数的信息将在更新 PCB 的 ECO 过程中传输到项目 PCB 文档。

Blanket

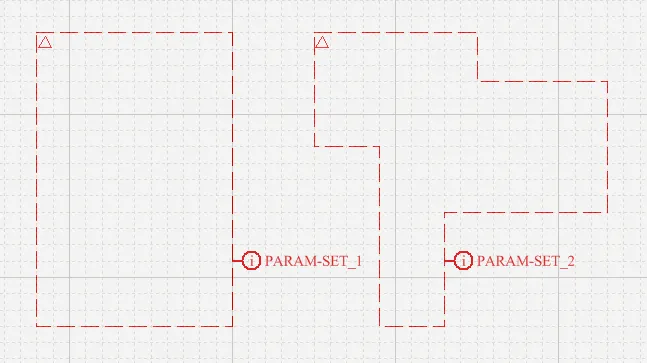

矩形 Blanket 与多边形 Blanket——每个都附加了 blanket 指令

概述

Blanket 是一种矩形或多边形的分组指令对象,放置在一组网络和/或器件之上。应用到 Blanket 的指令(Parameter Set 对象)将作用于 Blanket 覆盖的所有网络与器件。放置 Blanket 时,你可以定义简单的矩形形状或多边形形状。后者能更精确地控制对页面上所需网络对象的覆盖范围。

Blanket 适用于所有满足以下条件的网络:

-

完全位于 Blanket 定义的区域内,或

-

导线/总线/线束在 Blanket 下方至少有一个连接端点顶点,或

-

导线/总线/线束上附有网络标号,且该网络标号位于 Blanket 下方。

对于器件,Blanket 适用于位于 Blanket 定义区域内的所有器件。

应用到 Blanket 周界(Place » Directive)的指令(例如 No ERC、Differential Pair 或特定的规则/类 Parameter Set)将作用于 Blanket 对象登记的所有网络与器件。Blanket 可以被 禁用并隐藏。

可用性

Blanket 仅可在原理图编辑器中放置。要放置 Blanket:

-

从主菜单单击 Place » Directives » Blanket。

- 单击位于设计空间顶部的 Active Bar 上的指令下拉菜单中的 Blanket 按钮(

)。单击并按住某个 Active Bar 按钮可访问其他相关命令。一旦某个命令被使用,它将成为该 Active Bar 相应分区中的最上方条目。

)。单击并按住某个 Active Bar 按钮可访问其他相关命令。一旦某个命令被使用,它将成为该 Active Bar 相应分区中的最上方条目。

-

在原理图编辑器中右键单击,然后单击 Place » Directives » Blanket。

放置

放置矩形 Blanket:

-

按上述说明启动命令。

-

定位光标,然后单击或按 Enter ,以放置左上角。

-

定位光标,然后单击或按 Enter ,以放置右下角。

-

右键单击或按 Enter 完成放置。

-

继续放置更多 Blanket,或右键单击或按 Esc 退出放置模式。

放置多边形形状的 Blanket:

-

启动放置命令。

-

定位光标,然后单击或按 Enter ,以锚定 Blanket 的起始点。

-

定位光标,然后单击或按 Enter ,以锚定一系列线段,从而定义 Blanket 的形状。

-

放置最后一段后,右键单击或按 Esc 完成放置。无需“闭合”多边形,因为软件会自动通过添加所需线段,将起点与最后放置的线段连接起来,从而完成形状。

-

继续放置更多 Blanket,或右键单击或按 Esc 退出放置模式。

在放置 Blanket 线段期间,还可以执行以下附加操作:

-

按 Tab 键暂停放置,并访问 Properties 面板的 Blanket 模式,可在其中即时更改线条属性。单击设计空间的暂停按钮叠加层(

)以继续放置。

)以继续放置。

-

按 Spacebar 以更改尚未确认的线段拐角的转角方向。

-

按 Backspace 以在定义 Blanket 的多边形形状时删除先前已确认的线段。连续使用 Backspace 将按顺序删除更早的线段。

放置模式以更细的虚线表示。这在定义多边形形状的 Blanket 时最有用。可用它在确认更多线段之前预览 Blanket 的整体形状。复杂/自相交的多边形形状不受支持——软件会阻止形成此类形状。

图形化编辑

此编辑方法允许你在设计空间中直接选择已放置的 Blanket 对象,并以图形方式更改其尺寸、形状或位置。选中 Blanket 对象后,将提供以下编辑控柄:

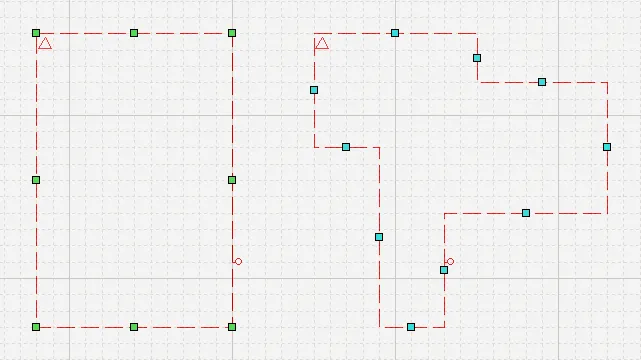

选中的矩形与多边形 Blanket,显示其图形编辑控柄。

选中的矩形与多边形 Blanket,显示其图形编辑控柄。

单击并拖动位于某条边中点的编辑控柄,可移动该边。

对于矩形 Blanket,单击并拖动角部编辑控柄,可同时在垂直与水平方向调整大小。

在远离编辑控柄的位置单击 Blanket 的轮廓线并拖动,可重新定位。拖动时可对 Blanket 进行旋转或翻转:

-

按 Spacebar 可围绕光标位置将 Blanket 逆时针旋转。Shift+Spacebar 可围绕光标将 Blanket 顺时针旋转。旋转以 90° 为增量。

-

按 X 或 Y 键,可相对于光标位置沿 X 轴或 Y 轴翻转 Blanket。

如果会导致形成复杂/自相交形状,则会阻止对多边形 Blanket 形状的修改。

如果尝试以图形方式修改启用了

Locked 属性的对象,将弹出对话框要求确认是否继续编辑。如果在

Preferences 对话框的

Schematic – Graphical Editing page 中启用了

Protect Locked Objects 选项,并且该设计对象的

Locked 选项也同样启用,则该对象无法被选中或进行图形化编辑。单击被锁定的对象以选中它,然后在

List panel 中禁用

Locked 属性,或禁用

Protect Locked Objects 选项,以便对对象进行图形化编辑。

非图形化编辑

提供以下非图形化编辑方法。

通过 Blanket 对话框或 Properties 面板编辑

Panel page: Blanket Properties

此编辑方法使用关联的 Blanket 对话框模式和 Properties 面板模式来修改 blanket 对象的属性。

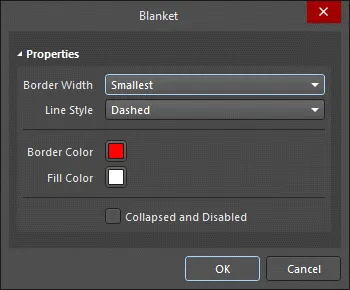

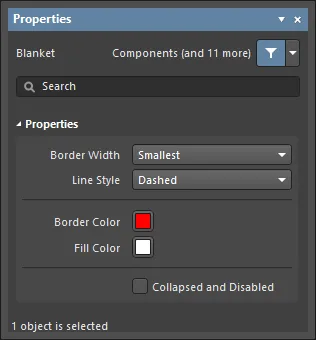

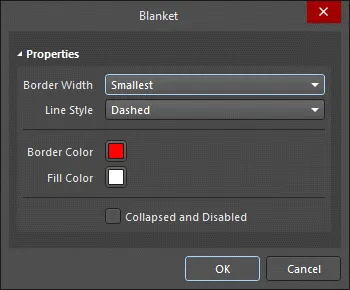

左侧为 Blanket 对话框,右侧为 Properties 面板的 Blanket 模式

左侧为 Blanket 对话框,右侧为 Properties 面板的 Blanket 模式

放置后,可通过以下方式访问 Blanket 对话框:

-

双击已放置的 blanket 对象。

-

将光标置于 blanket 对象上,右键单击,然后从上下文菜单中选择 Properties。

在放置过程中,可按 Tab 键访问 Properties 面板的 Blanket 模式。放置完成后,将显示所有选项。

放置后,可通过以下方式之一访问 Properties 面板的 Blanket 模式:

-

如果 Properties 面板已处于活动状态,选中 blanket 对象即可。

-

选中 blanket 对象后,通过设计空间右下角区域的 Panels 按钮选择 Properties panel,或从主菜单选择 View » Panels » Properties。

如果在

Preferences 对话框的

Schematic – Graphical Editing page 中启用了

Double Click Runs Interactive Properties 选项(默认),当双击该图元,或在选中图元后右键并选择

Properties 时,将打开

Properties 面板。当禁用

Double Click Runs Interactive Properties 选项时,将打开对话框。

尽管对话框与面板中的选项相同,但选项的顺序与布局可能略有不同。

编辑多个对象

Properties 面板支持多对象编辑,可修改当前所选对象中“相同”的属性设置。当手动选择多个相同对象类型,或通过 Find Similar Objects dialog,或通过 Filter 或 List 面板进行选择时,Properties 面板中未显示为星号(*)的字段条目,都可以对所有选中对象进行编辑。

通过列表面板编辑

Panel pages: List Panels、SCH Filter

List 面板以表格形式显示一个或多个文档中的设计对象类型,便于快速检查与修改对象属性。结合适当的过滤方式——通过选择对象类型(使用面板的 Include 选项),或使用相应的 Filter panel,或使用 Find Similar Objects dialog——可仅显示落在当前活动过滤器范围内的对象。随后即可在 List 面板中直接编辑所列对象的属性。

过滤支持

在使用逻辑查询表达式定位 Blanket 对象时,有两个特别有用的关键字可用。它们与基于 Blanket 属性进行定位的其他关键字相互补充。

-

Collapsed – 对象处于折叠状态(在定位 Compile Masks 时也很有用)。使用 Query Helper 时,可在 SCH Functions - Fields 类别中找到该关键字。

-

IsBlanket – 测试对象是否为 Blanket。使用 Query Helper 时,可在 SCH Functions - Object Type Checks 类别中找到该关键字。

根据需要创建逻辑表达式查询,以定位并返回设计中的 Blanket。以下是一些针对 Blanket 的逻辑查询表达式示例:

IsBlanket And Collapsed – 定位当前所有处于折叠状态的 Blanket 对象。

IsBlanket And Not Collapsed – 定位当前所有未处于折叠状态的 Blanket 对象。

禁用 Blanket

放置后,可通过单击左上角的小三角形( )临时禁用 Blanket。单击一次可禁用并隐藏 Blanket;再次单击可重新启用。这提供了一种便捷方式来控制 Blanket 的影响,而无需将其从设计中完全移除。

)临时禁用 Blanket。单击一次可禁用并隐藏 Blanket;再次单击可重新启用。这提供了一种便捷方式来控制 Blanket 的影响,而无需将其从设计中完全移除。

也可以通过在

Properties 面板中启用

Collapsed and Disabled 选项,或在通过

SCH List 面板编辑时启用

Collapsed 选项来禁用 Blanket。

Blanket Properties

原理图编辑器对象属性是可定义的选项,用于指定已放置对象的视觉样式、内容和行为。每种对象类型的属性设置通过两种不同方式定义:

-

Pre-placement settings – 大多数 Blanket 对象属性,或那些在逻辑上可以预先定义的属性,都可以在 Preferences dialog 的 Schematic - Defaults 页面中作为可编辑的默认设置使用(通过设计空间右上角的

按钮进入)。在 Primitive List 中选择该对象,即可在右侧显示其选项。

按钮进入)。在 Primitive List 中选择该对象,即可在右侧显示其选项。

-

Post-placement settings – 当在设计空间中选中已放置的 Blanket 时,所有 Blanket 对象属性都可在 Blanket dialog 和 Properties panel 中编辑。

如果在

Preferences dialog 的

Schematic - Graphical Editing page 上禁用了

Double Click Runs Interactive Properties 选项(默认),当双击该图元,或在选中图元后右键并选择

Properties 时,将打开该对话框。当启用

Double Click Runs Interactive Properties 选项时,将打开

Properties panel。

尽管 dialog 与 panel 中的选项相同,但选项的顺序和位置可能会略有不同。

在下面的选项列表中,未在 Preferences dialog 中作为默认设置提供的选项会标注为 “Properties panel only”。

Properties

-

Border Width - 使用下拉菜单选择所需的边框宽度。

-

Line Style - 使用下拉菜单选择所需的线型。

-

Border Color - 单击颜色框以选择边框所需的颜色。

-

Fill Color - 单击颜色框以选择填充所需的颜色。

-

Collapsed and Disabled - 勾选以折叠并禁用 blankets。

间接(基于参数的)指令

当需要在原理图中针对那些无法包含参数的设计对象时,就必须使用 Parameter Set directives;但对于能够包含参数的对象,也可以通过将设计指令作为参数添加(并定义)到相关原理图对象上,从而间接应用设计指令。本质上,它们是 parameter-based directives。

基于参数的指令的使用示例包括:限制某个特定器件的高度,或添加一个以设计中所有对象为目标的间距(clearance)约束。用于定义该约束的所需参数会作为规则添加到对象上。

与 PCB 同步后,添加到原理图对象上的基于参数的指令将成为 PCB 设计规则。相应 PCB 设计规则的作用域将由最初分配该参数的对象类型决定。下表汇总了所支持的“原理图参数 → PCB 规则作用域”选项。

在每种情况下,添加基于规则的参数的方法都相同。在相应的选项卡或对话框中,执行以下操作:

-

添加一个参数作为规则。

-

选择要使用的规则类型。

-

为所选规则类型配置约束条件。

当向原理图上的对象添加设计规则参数时,每个规则参数都会被分配一个唯一 ID。PCB 上创建的对应设计规则也会使用相同的 ID。借助该唯一 ID,可以在原理图端或 PCB 端编辑规则的约束,并在同步时将更改推送过去。

指定元件类

类似地,也可以通过向目标元件添加一个 ClassName 参数,并将其值设置为所需的类名,在原理图中定义元件类。当设计传输到 PCB 时,将创建所定义的元件类。

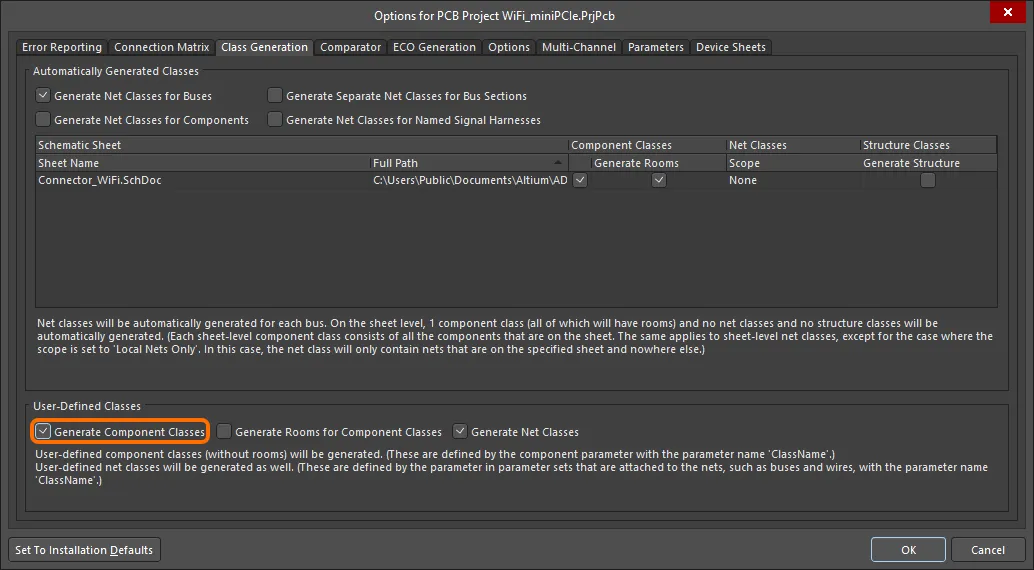

为确保在原理图中定义的元件类能够传递到 PCB,必须在 Project Options dialog 中设置以下选项:

-

启用位于对话框 Class Generation tab 的 User-Defined Classes 区域中的 Generate Component Classes 选项。

-

在对话框的 Comparator tab 上,将 Differences Associated with Components » Extra Component Classes Mode 设置 为

Find Differences。

上述所列的 Class Generation 选项卡选项显示在下图中。将鼠标悬停在图片上以查看 Comparator 选项卡选项设置。

要将元件类传递到 PCB, 请在 Class Generation 选项卡上启用 Generate Component Classes 选项。将鼠标悬停在图片上以显示 Comparator 选项卡 ,你需要在其中将 Extra Component Classes Mode 设置为 Find Differences。

一旦定义完成,可在相应元件属性的 Properties panel 的 Properties 区域中锁定这些类。

在 PCB 编辑器中,一个 元件可以属于多个元件类。要在原理图中定义这一点,请在原理图元件参数值中用逗号分隔每个 PCB 元件类名称(show image![]() )。

)。

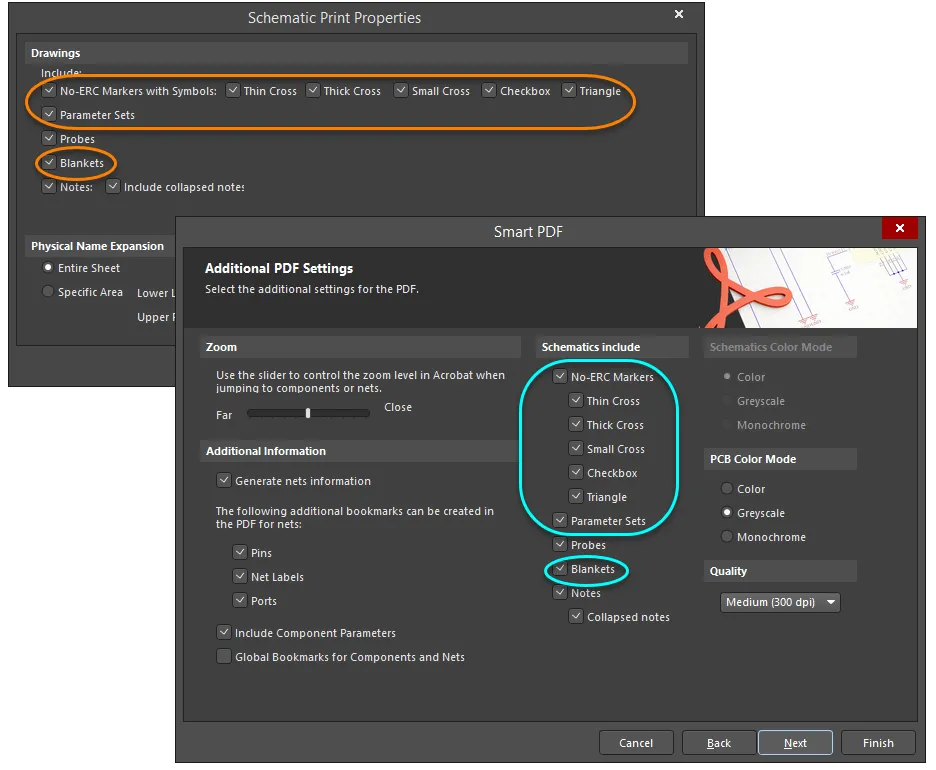

控制指令的打印

默认情况下,所有设计指令都会包含在原理图图纸的打印输出中。不过,这一行为可以更改:

根据需要控制指令的打印。对于 No ERC 指令,你可以选择打印某些符号样式,同时排除其他样式。

AI 翻译

AI 翻译