인쇄 전자 설계

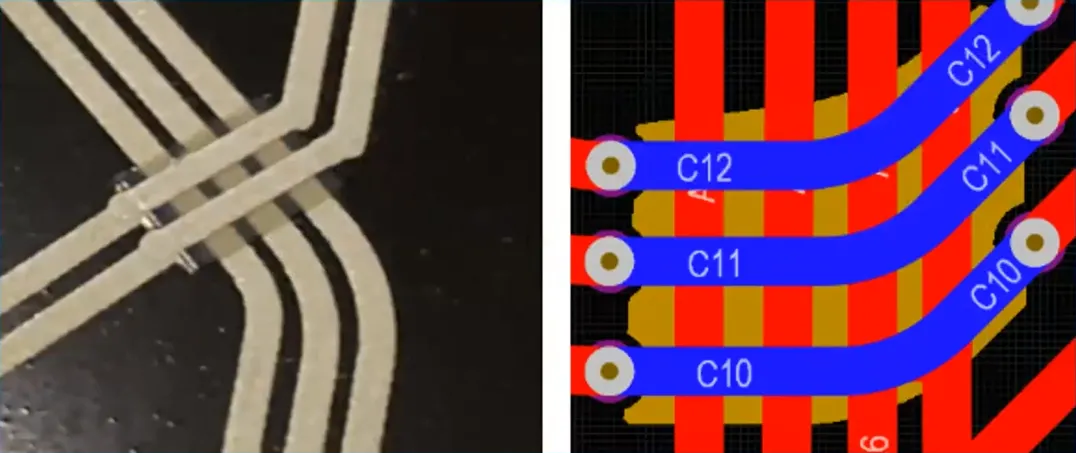

전자 제품의 설계 및 개발에서 흥미로운 진화 중 하나는, 제품의 일부가 되는 플라스틱 몰딩과 같은 기판 위에 전자 회로를 직접 인쇄할 수 있다는 점입니다.

|

|

이 슬라이드는 인쇄 전자 레이아웃 예시의 2D 및 3D 뷰를 보여줍니다. (이미지 제공: “csi entwicklungstechnik”, TactoTek® In-Mold Structural Electronics를 활용한 설계에서 발췌).

|

이러한 표면 지향 구현 기법은 Printed Electronics라고 합니다. Printed Electronics라는 용어는 인쇄가 이를 구현하는 유일한 기법이 아니므로 기술을 정확히 설명하는 표현은 아니지만, 업계에서 널리 통용되므로 이 페이지에서는 해당 용어를 사용합니다.

인쇄 전자를 구현하기 위해 개발 중인 접근 방식에는 다음이 포함됩니다: 도전성 잉크를 이용한 3D 프린팅; 트랜지스터와 같은 간단한 회로 소자뿐 아니라 도체도 만들 수 있는 스탬핑 기법; 초고정밀로 매우 미세한 스케일에서 도전 경로를 형성할 수 있는 레이저 증착 기법.

인쇄 전자는 전자 기술을 새로운 시장에 통합할 수 있게 하는 핵심 기술이 될 것입니다. 인쇄 전자는 회로와 제품 간의 매우 밀접한 결합을 가능하게 합니다. 신체에 직접 부착되는 유연 센서부터, 액체를 붓는 동안 로봇 손이 부드러운 플라스틱 컵을 잡을 수 있게 해주는 다중 센서의 손끝 모양 몰딩에 이르기까지, 인쇄 전자는 다양한 시장 세그먼트 전반에서 혁신적인 신규 솔루션 개발을 가능하게 할 것입니다.

기술

what 측면에서 보면, 기술이 제공하는 본질은 동일합니다. 전자 부품들이 도전 경로로 서로 연결되어 유용한 기능을 수행하는 전자 회로를 이룹니다. 달라지는 점은 회로를 구축하는 방식입니다.

기존 PCB를 만드는 데 사용되는 층(레이어) 지향 제조 기술은 reductive process입니다. 각 도전층은 구리와 같은 도전성 재료의 연속 시트로 시작한 뒤, 에칭으로 불필요한 부분을 제거하여 필요한 도전 경로를 형성하는 구리만 남깁니다. 또한 다단계 공정이기도 한데, 개별 도전층을 절연층과 번갈아 샌드위치처럼 적층하고, 다양한 드릴링 및 후도금 공정을 적용하기 때문입니다.

인쇄 전자는 additive process이며, 신호 경로를 기판 위에 직접 인쇄합니다. 이후의 신호 경로가 기존 경로를 교차해야 한다면, 필요한 위치에 작은 절연 패치를 직접 인쇄합니다. 이 패치는 작은 브리지처럼 동작하여, 기존 경로와 전기적으로 연결되지 않으면서 그 위로 새로운 신호 경로를 인쇄할 수 있게 해줍니다. 예를 들어 설계에서 DuPont InMold 기술을 사용한다면, 먼저 평평한 플라스틱 기판에 회로를 인쇄한 다음, 이를 열성형하고 사출 성형하여 최종 제품 형상으로 만듭니다.

인쇄 전자를 사용하면, 더 이상 일반적인 경질 유리섬유 PCB 기판이 필요하지 않습니다. 대신 회로가 제품의 일부로 직접 형성되며, 도체는 최종적으로 제품 표면의 형상과 윤곽을 따라가게 됩니다. 사용 재료와 폐기물이 줄어들기 때문에, 많은 경우 인쇄 전자는 기존 PCB보다 궁극적으로 더 비용 효율적인 접근 방식이 될 것입니다.

NOTE - 현재 단계에서는 Altium Designer의 인쇄 전자 설계 기능이 평면 기판 표면만 지원합니다. 완전한 3D 회로 설계를 위해서는 Altium Designer의 전용 3D-MID 설계 도구를 지금 사용할 수 있습니다.

기능 개요는 True 3D-MID Design 기능 페이지를 참조하세요.

자세한 내용은 3D-MID Design 문서 페이지를 참조하세요.

Altium Designer에서 인쇄 전자 설계하기

설계가 인쇄되는 기판을 제외하면, 인쇄 전자 제품에는 물리적인 레이어가 없습니다. 도전 경로는 기판 위에 직접 인쇄됩니다. 설계상 경로가 서로 교차해야 하는 경우, 해당 위치에 유전체 재료의 작은 패치를 인쇄하며, 서로 다른 신호 간에 필요한 절연 수준을 확보할 수 있도록 교차 영역보다 충분히 넓게 확장합니다.

인쇄 공정을 구동하는 데 필요한 출력물은 Gerber와 같은 표준 출력 형식을 사용해 생성됩니다.

출력에는 다음에 대한 파일이 포함됩니다:

-

각 도전성 인쇄 패스 - 본질적으로 기존 PCB의 구리 라우팅 레이어와 동일

-

각 유전체 인쇄 패스 - 유전체 패치를 인쇄하므로, 그 형상도 Gerber 파일과 같은 출력 파일에 지정됩니다.

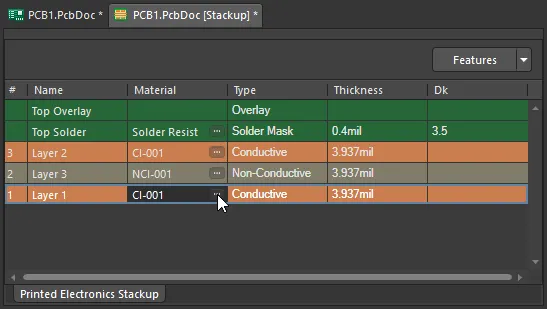

레이어 스택 정의

그렇다면 이러한 여러 인쇄 패스는 PCB 편집기에서 어떻게 정의할까요? 인쇄 전자에서는 각 인쇄 패스마다 출력 파일이 필요하므로, 유전체 레이어로 분리된 구리 레이어의 연속으로 생각하기보다는, 각 패스가 도전성 잉크 레이어 또는 비도전성 잉크 레이어인 ‘인쇄 패스의 집합’으로 생각하는 것이 좋습니다.

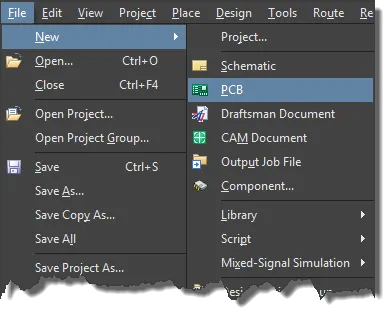

인쇄 전자 설계를 만들려면, 먼저 메인 메뉴에서 File » New » PCB를 사용해 새 PCB를 생성합니다.

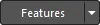

새 보드를 인쇄 전자 설계로 구성하는 작업은 Layer Stack Manager에서 수행합니다. Layer Stack Manager에 접근하려면 메인 메뉴에서 Design » Layer Stack Manager를 선택하세요. 그런 다음  드롭다운을 사용해 Printed Electronics 을 선택하거나, 메인 메뉴에서 Tools » Features » Printed Electronics를 선택하세요.

드롭다운을 사용해 Printed Electronics 을 선택하거나, 메인 메뉴에서 Tools » Features » Printed Electronics를 선택하세요.

새 PCB는 기본적으로 유전체 레이어로 분리된 두 개의 구리 레이어로 시작합니다.

새 PCB는 기본적으로 유전체 레이어로 분리된 두 개의 구리 레이어로 시작합니다.

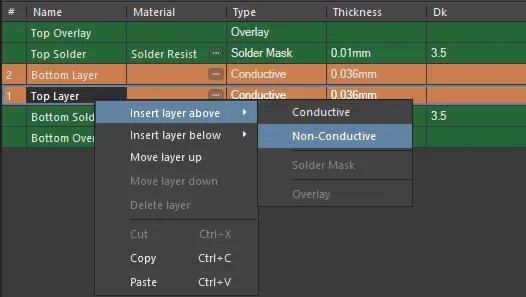

Printed Electronics 기능을 활성화하면 두 구리 레이어 사이의 유전체 레이어가 사라집니다. 왜일까요? 인쇄 전자는 모든 레이어에 대해 출력 파일이 필요하므로, 출력 파일 생성에 사용되지 않는 유전체 레이어는 사용하지 않기 때문입니다.

When the Printed Electronics feature is enabled, the dielectric layer is removed.

대신 비도전성 레이어가 추가됩니다. ‘패치’라고 하는 유전체 형상은, 도전성 레이어에서 신호 경로가 서로 교차해야 하는 위치에 수동 또는 자동으로 정의할 수 있습니다.

Non-Conductive 레이어는 Conductive 레이어 사이에 삽입할 수 있으며, 그 위에 유전체 패치를 정의할 수 있습니다.

레이어를 마우스 오른쪽 버튼으로 클릭하여 위/아래에 레이어를 삽입하거나, 레이어를 위/아래로 이동하거나, 레이어를 삭제할 수 있습니다. 인쇄 전자는 Bottom Solder 또는 Bottom Overlay를 사용하지 않으므로, 이들은 제거되었습니다.

레이어를 추가한 후에는 각 레이어의 재료 속성을 설정합니다.

각 인쇄 레이어에 사용할 재료를 선택하려면 줄임표(ellipsis) 버튼을 사용하세요.

각 인쇄 레이어에 사용할 재료를 선택하려면 줄임표(ellipsis) 버튼을 사용하세요.

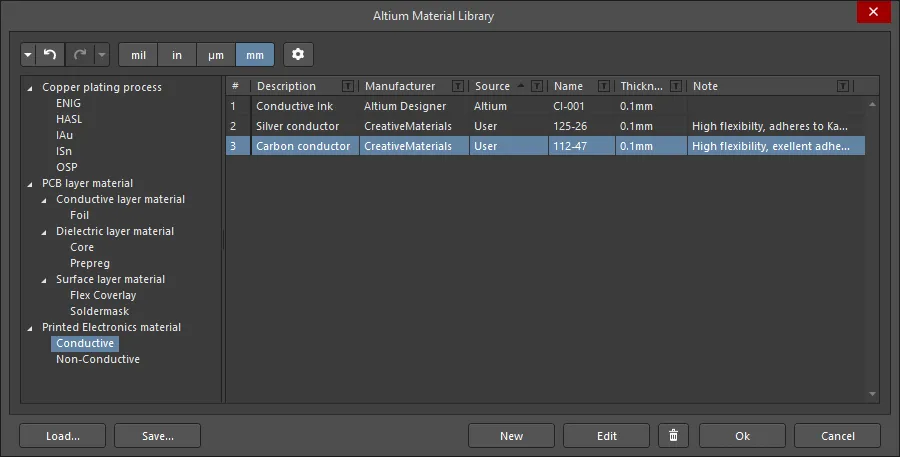

재료 선택

기존 PCB 설계와 인쇄 전자 설계에서 사용되는 재료는 모두 Layer Stack Manager의 Material Library에서 선택합니다.

Layer Stack Manager가 열려 있을 때 Tools » Material Library 명령을 사용하여 Altium Material Library 대화상자를 엽니다.

-

Altium Material Library 대화상자에는 도전성 레이어와 비도전성 레이어 모두에 대한 재료가 포함되어 있습니다.

-

라이브러리에 새 재료를 정의할 수 있으며, 대화상자 하단의 New 버튼을 클릭하세요. 사용자 정의 재료를 만들면, 사용자 정의 재료 라이브러리에 저장하고 거기서 불러올 수 있습니다.

-

특정 레이어의 재료를 선택하려면 Layer Stack Manager에서 해당 레이어의 Material 셀에 있는 줄임표 컨트롤(

)을 클릭합니다. 그러면 Select Material 대화상자가 열리고, 해당 레이어 Type에 적합한 재료만 표시됩니다. 필요한 재료를 선택한 다음 OK을 클릭하세요.

)을 클릭합니다. 그러면 Select Material 대화상자가 열리고, 해당 레이어 Type에 적합한 재료만 표시됩니다. 필요한 재료를 선택한 다음 OK을 클릭하세요.

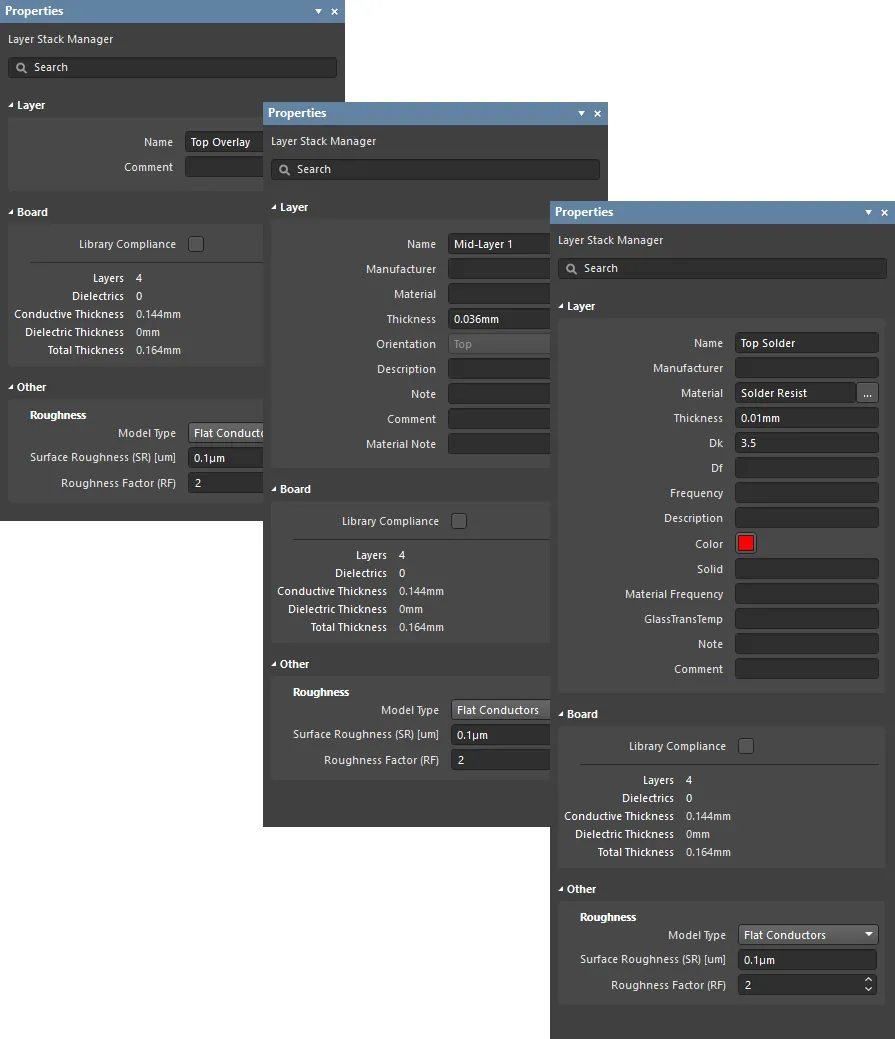

Properties 패널

Layer Stack 문서의 Printed Electronics Stackup 탭이 활성화되어 있을 때, Properties 패널에서 인쇄 설계를 위한 Layer Stack의 레이어 속성을 편집하고 구성할 수 있습니다.

-

Layer

-

Name – 레이어 이름.

-

Manufacturer – 레이어 제조사.

-

Material – 레이어 재료. 이는 Altium Material Library dialog (Tools » Material Library)의 Constructions 필드에서 미리 정의할 수 있으며, 또는 Layer Stack에서 사용자 정의할 수 있습니다.

를 클릭하면 Select Material dialog가 열리며, 레이어 스택에서 현재 선택된 레이어에 대해 원하는 재료를 선택할 수 있습니다.

를 클릭하면 Select Material dialog가 열리며, 레이어 스택에서 현재 선택된 레이어에 대해 원하는 재료를 선택할 수 있습니다.

-

Thickness – 신호 레이어의 두께.

-

Dk – 유전율(전자기학에서 εr로도 표기)입니다. 이는 절연 재료의 상대 유전율을 나타내며, 전기장 내에서 전기 에너지를 저장하는 능력을 의미합니다. 절연 목적에서는 유전율이 낮은 재료가 더 유리하고, RF 응용에서는 더 높은 유전율이 바람직할 수 있습니다. 또한 상대 유전율이 낮을수록 재료의 성능이 공기에 더 가까워집니다. 이 특성은 특정 전송선의 임피던스 요구사항을 맞추는 데 매우 중요합니다.

-

Df – 손실 계수(Dissipation Factor)입니다. 이는 기계적/전기적/전기기계적 진동과 같은 특정 진동 모드에서 에너지 손실률을 보여줌으로써 절연 재료의 효율을 나타냅니다. 즉, 전달된 에너지 중 얼마나 많은 에너지가 재료에 흡수되는지를 설명하는 재료 특성입니다. 손실 탄젠트가 클수록 재료로 흡수되는 에너지가 커집니다. 이 특성은 고속에서의 신호 감쇠에 직접적인 영향을 줍니다.

-

Frequency – 재료가 시험된 주파수이며, Dk / Df 값이 특정 주파수에 대응합니다. 주파수는 재료 참고 자료에서도 가져옵니다.

-

Description – 의미 있는 설명을 입력하세요.

-

Color – 솔더 마스크에 필요한 색상입니다. 드롭다운을 열어 색상을 설정/변경할 수 있습니다.

-

Solid – 해당 없음

-

Material Frequency – 해당 없음

-

GlassTransTemp – 유리 전이 온도(Glass Transition Temperature, TG)입니다. 수지가 유리 같은 상태에서 비정질 상태로 변하면서 기계적 거동(예: 팽창률)이 바뀌는 온도입니다.

-

Note – 레이어에 대한 관련 메모를 입력하세요.

-

Comment– 레이어에 필요한 코멘트를 입력합니다.

-

Board

-

Library Compliance – 활성화하면, Material Library에서 선택된 각 레이어에 대해 현재 레이어 속성을 라이브러리의 해당 재질 정의 값과 비교해 확인합니다.

-

Layers – 도전성 레이어의 개수입니다.

-

Dielectrics – 유전체의 개수입니다.

-

Conductive Thickness – 모든 신호 및 플레인 레이어(모든 구리/도전성 레이어) 두께의 합입니다.

-

Dielectric Thickness – 유전체 레이어(들)의 두께입니다.

-

Total Thickness – 완성된 보드의 총 두께입니다.

-

Other

Roughness – 도전성 레이어의 거칠기를 표시합니다.

-

Model Type – 표면 거칠기의 영향을 계산하기 위한 선호 모델입니다(다양한 모델에 대한 자세한 내용은 아래 문서를 참조). 스택의 모든 구리 레이어에 적용됩니다.

-

Surface Roughness – 표면 거칠기 값(제조사에서 제공 가능)입니다. 0~10µm 사이의 값을 입력하며, 기본값은 0.1µm입니다.

-

Roughness Factor – 거칠기 효과로 인해 도체 손실이 증가할 것으로 예상되는 최대 증가량을 특성화합니다. 1~100 사이의 값을 입력하며, 기본값은 2입니다.

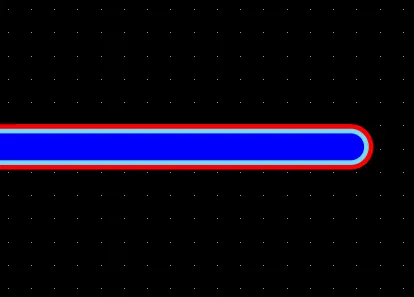

네트 라우팅

-

인쇄 전자(Printed Electronics) 설계의 네트는 기존 PCB와 동일한 방식으로 Interactive Routing 명령을 사용해 라우팅합니다.

-

도전성 레이어 전환은 숫자 키패드의 + 및 - 키 또는 Ctrl+Shift+Wheelroll 단축키로 수행합니다.

-

라우팅 중 레이어를 변경하면 비아가 추가되며, 비아 속성은 적용 가능한 Routing Via Style 설계 규칙에 의해 결정됩니다.

비아가 필요한가요?

소프트웨어는 라우팅 중 네트의 연결성을 유지하고, 푸시/드래그로 라우팅이 수정될 때도 연결성을 관리하기 위해 비아를 배치해야 합니다. 레이어 간 연결 자체를 위해 비아가 필요한 것은 아니며, 소프트웨어는 서로 다른 레이어에서 겹치는 트랙이 연결되어 있다고 가정합니다.

비아의 지름은 라우팅 폭과 동일한 크기로 설정할 수 있습니다.

라우트 두께 증가

필요한 경우(예: 인쇄 안테나 같은 구조 구현) 라우트 두께를 적층해 늘릴 수 있습니다. 이는 서로 다른 도전성 레이어에 여러 라우트를 서로 겹치도록 배치하여 구현합니다.

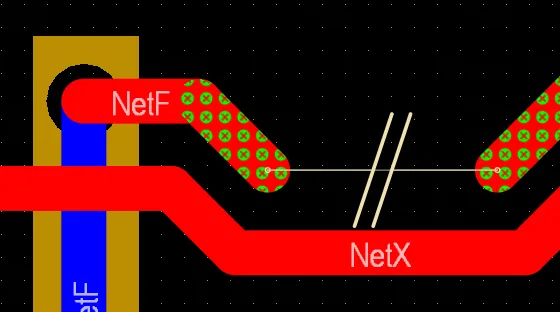

유전체 도형 추가

네트 라우팅이 완료되면, 다음 단계는 서로 다른 네트의 크로스오버를 분리하는 데 필요한 유전체 패치를 만드는 것입니다. 유전체 도형은 비도전성 레이어에 정의됩니다. 수동으로 정의할 수도 있고, Dielectric Shapes Generator를 사용해 자동으로 생성할 수도 있습니다.

수동 도형은 Arc, Line, Fill 또는 Solid Region으로 만들 수 있습니다. Solid Region 객체가 가장 유연하며, 가장자리를 조정해 사실상 어떤 형태든 만들 수 있습니다.

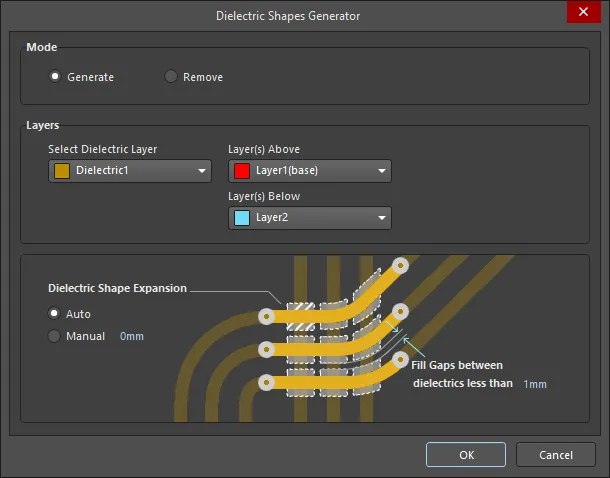

유전체 도형 생성기

소프트웨어에는 자동 Dielectric Shapes Generator도 포함되어 있습니다. 여기서의 개념은 먼저 도전성 레이어에서 필요한 라우팅을 완료하고, 레이어 전환을 위해 비아를 배치하는 것입니다.

라우팅이 완료되면 Tools » Printed Electronics » Generate Dielectric Patterns 명령을 실행해 Dielectric Shapes Generator 대화상자를 엽니다. Dielectric Shapes Generator를 실행하면 대상 레이어의 모든 도형을 제거한 다음 다시 생성합니다. 수동으로 도형을 정의했다면 Dielectric Shapes Generator를 실행하기 전에 잠그세요.

Options and Controls of the Dielectric Shapes Generator Dialog

-

Mode - 원하는 모드를 선택합니다:

-

Generate - Layers 영역에 지정된 활성화된 모든 레이어에 대해 새 유전체 패치를 생성하도록 선택합니다.

-

Remove - 생성기가 자체 도형을 추가하기 전에 Layers 영역에 지정된 레이어에서 감지한 기존 도형을 모두 제거하도록 선택합니다.

-

Layers - 생성기는 모든 크로스오버를 식별하고, 대화상자의 이 영역 설정에 따라 유전체 패치를 추가합니다.

-

Select Dielectric Layer - 드롭다운에서 유전체 레이어를 선택합니다. All 를 선택하면 생성기는 어떤 도전성 레이어 쌍에서든 크로스오버를 찾고, 그 두 도전성 레이어 사이에 있는 유전체 레이어에 패치를 배치합니다. 유전체 레이어를 선택하지 않으면, 모든 레이어 간 모든 크로스오버에 대해 적절한 유전체 레이어에 유전체 도형이 생성됩니다. 생성기가 크로스오버를 검색할 때 어떤 두 도전성 레이어 사이를 볼지 Layer(s) Above 및 Layer(s) Below 를 사용해 선택합니다. Layer(s) Above의 객체가 Layer(s) Below의 객체를 가로지르는 것을 발견하면, 그 사이에 배치할 패치를 생성하고 Select Dielectric Layer 영역에 지정된 레이어에 배치합니다. Layer(s) Above 및 Layer(s) Below 옵션은 Mode 영역에서 Remove 가 선택된 경우 사용할 수 없습니다.

-

Dielectric Shape Expansion

-

Auto - 이 모드에서는 적용 가능한 Clearance Constraint 설계 규칙 요구사항을 만족하도록 유전체 도형이 자동으로 확장됩니다.

-

Manual - 이 모드에서는 생성기가 교차된 객체들이 형성하는 모양과 일치하는 도형을 만든 다음, 입력한 거리만큼 그 도형을 바깥으로 확장합니다. 예를 들어 이 모드를 사용하면, 서로 다른 레이어의 두 트랙이 간격 위반이 발생할 정도로 너무 가까운 경우 패치가 배치되지 않습니다.

-

Fill Gaps between dielectrics less than <xx> - 지정한 값보다 작은 유전체 간 간격을 채우고 싶다면 측정값을 지정합니다. 이는 인접한 유전체 패치를 더 큰 패치로 병합하는 데 사용할 수 있습니다.

네트 연결성과 설계 규칙 검사

Printed Electronics로 레이어 스택이 구성된 경우, 위반 조건을 정의하는 로직이 다르기 때문에(예: 서로 다른 레이어에서 네트가 교차하면 단락으로 표시됨) Online DRC는 지원되지 않습니다. 라우팅이 완료되고 절연 패치가 정의되면 Design Rule Checker 대화상자(Tools » Design Rule Check)에서 Run Design Rule Check 버튼을 클릭해 배치 DRC를 수행하세요.

네트 연결성과 설계 규칙 검사에 대한 참고 사항:

-

네트가 다른 도전성 레이어로 전환해야 할 때는 비아를 삽입하세요. 이렇게 하면 라우팅을 드래그하거나 푸시할 때 트랙 세그먼트가 올바르게 처리됩니다.

-

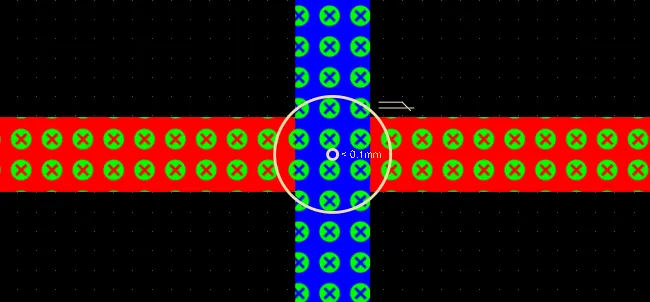

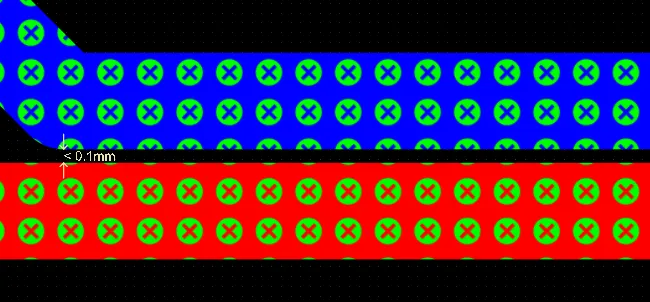

서로 다른 레이어에 있는 트랙이 접촉/교차하면 연결된 것으로 간주됩니다. 같은 네트라면 단선(broken net)으로 표시되지 않으며, 다른 네트라면 단락(short circuit)으로 표시됩니다.

-

접촉/교차하는 트랙을 절연하려면 유전체 도형이 필요하며, 이 도형은 비도전성 레이어에 배치됩니다. 유전체 도형은 수동으로 배치하거나 Dielectric Shape Generator로 배치할 수 있습니다. 유전체 도형은 적용 가능한 clearance constraint 설계 규칙을 만족하도록 교차 트랙의 가장자리 밖으로 충분히 확장되어야 합니다.

-

인쇄 전자 설계에서 단락, 간격 위반, 미배선 네트에 대한 설계 규칙 검사는 아래와 같이 동작합니다.

단락 설계 규칙

Printed Electronics 설계에서는 서로 다른 네트가 서로 다른 레이어에서 교차하면 단락으로 표시됩니다. 이러한 크로스오버는 비도전성 레이어에 유전체 패치를 배치하여 절연합니다.

간격(Clearance) 설계 규칙

네트 간 간격은 동일 레이어뿐 아니라 모든 레이어에서 테스트됩니다.

미배선 네트

레이어 전환에는 비아가 필요하지 않으며, 네트 분석기는 네트가 끊어지지 않았음을 인식합니다.