良い基板設計の重要な要素の1つが部品配置です。大規模な設計では、部品の基板上での位置が、そのデジグネータと何の関係もない場合があります。たとえば、R1 が R2 の基板反対側に配置されることもあります。基板上で部品を見つけやすくするために、位置に基づいてデジグネータを再割り当て(基板を再アノテート)できます。

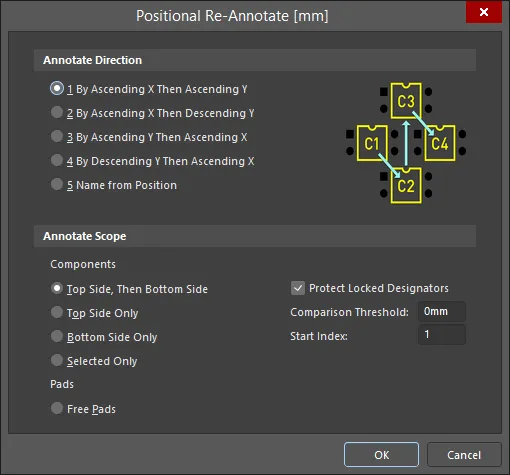

PCB Editorで、対象部品またはフリーパッドのデジグネータを位置に基づいて体系的に割り当てるには、Tools » Re-Annotate をクリックして、以下に示す Positional Re-Annotate ダイアログを開きます。このダイアログでは、アノテーションの範囲(部品(さらに面や選択で対象を絞り込み)、またはフリーパッド)、アノテーションの方向(オブジェクト位置に基づく)、開始インデックスやロックされたデジグネータを保護するかどうかといった追加オプションを設定できます。

アノテーションのスタイルを選択すると、ダイアログ内にグラフィカルな図が表示され、アノテーションがどのように進むかを視覚的に確認できます。

Positional Re-Annotate ダイアログには、各方式のグラフィカルな表現が含まれています。

Options and Controls of the Positional Re-Annotate Dialog

部品位置の特定

各部品は、文字列を除外した外接矩形(バウンディング矩形)で識別されます。部品はリストに並べ替えられ、その順序でリストがリナンバリングされて新しい部品デジグネータが作成されます。X方向で2つの部品を比較する場合は、バウンディング矩形の左辺を使用します。Y方向で比較する場合は、リナンバリング方向に応じて使用する辺が変わります。昇順Yでは下辺、降順Yでは上辺を使用します。

Comparison Threshold オプションは、2つの辺を比較して等しいかどうかを判断する際のバッファ値として使用できます。たとえば、2つの左辺の差が75.0 mil以内で、比較しきい値が100.0 milに設定されている場合、これら2つの部品は同じX位置(左辺)にあると見なされます。これにより、わずかにずれた部品でも、下図のように論理的な順序でリナンバリングできます。ここでは、隣接する抵抗と正しくアノテートされるように、R27 を他の抵抗より低い位置にしています(Comparison Threshold は 10mils に設定)。

位置に基づいて再アノテートされた抵抗の一連。R27は他の抵抗より低い位置にあるにもかかわらず、アノテーション順序に残っている点に注意してください。

位置に基づいて再アノテートされた抵抗の一連。R27は他の抵抗より低い位置にあるにもかかわらず、アノテーション順序に残っている点に注意してください。

Annotate Scope オプションでは、両面実装の基板に対するアノテーション処理も制御できます。基板のBottom Sideでは、基板を裏返して見ているかのように部品が再アノテートされます。そのため、裏面でのX方向比較では、ソフトウェアは実際にはバウンディング矩形の右辺を使用します。裏面から見た場合、この辺が左側に見えることを考慮しているためです。

Selected Only オプションが有効で、再アノテートの結果、選択セット内の部品に既存の未選択部品と重複するデジグネータが割り当てられる場合、未選択部品のデジグネータには一意性を保つために _1 が付加されます。

回転した部品は、以下の画像に示すように、回転後の向きにおいて元のバウンディング矩形を包含する最小のバウンディング矩形で識別される点に注意してください。

左の画像はR2のバウンディング矩形、右の画像はR2を回転したときの新しいバウンディング矩形を示しています。

左の画像はR2のバウンディング矩形、右の画像はR2を回転したときの新しいバウンディング矩形を示しています。

変更を回路図へ反映

PCBでRe-Annotateを実行したら、次に Design » Update コマンドを使用してこれらの変更を回路図へ戻します。コマンド実行時、ソフトウェアはまず各回路図部品を、その部品の一意IDを用いて対応するPCB部品と照合し、その後、各回路図デジグネータを新しいPCBデジグネータに更新します。アノテーション処理の最終化について詳しく学んでください。

Design » Update コマンドを実行してアノテーション変更を回路図へプッシュバックした後、回路図に切り替えると、各部品の横に新しいデジグネータが表示され、さらにその部品が以前持っていたデジグネータが、括弧付きの薄い上付き文字として表示されます。これは設計コンパイラが以前の値を保持しているためです。Project » Validate PCB Project <ProjectName> コマンドを実行してコンパイラの更新を強制し、以前の値を削除します(show image)。

Was-Isファイルの生成

位置に基づく再アノテートを実行するたびに、以前のデジグネータから新しいデジグネータへの対応関係もASCIIテキストファイル(DesignName[Date][Time].WAS、Projects パネルの Generated\Text Documents サブフォルダ配下)に書き込まれます。これらのファイルはPCBドキュメントと同じフォルダに保存されます。

コンピュータベースの回路図/PCB設計ツールが最初に開発された当時、Was-IsファイルはPCBの位置再アノテートを回路図へ戻すために開発された手法でした。この「初期デジグネータ値」と「再アノテート後デジグネータ値」の対応ファイルは、PCBと回路図ファイルが別の場所にある場合でも、Annotate ダイアログの Back Annotate 機能を使って回路図に変更を読み込む用途として、現在も利用できます。Was-Isファイルを使用してバックアノテーションを行う方法について詳しく学んでください。

デジグネータの再割り当てを防ぐ

部品のデジグネータが再割り当てされないようにするには、Positional Re-Annotate ダイアログで Protect Locked Designators チェックボックスを有効にし、保護するデジグネータについて、Properties パネルで Locked アイコンが有効になっていることを確認します(以下に示すとおり)。