テストは基板製造工程の重要な部分です。製造後、基板は通常、短絡や開回路がないことを確認するためにテストされます。すべての部品が完全に実装された後、基板はしばしば再度テストされ、シグナルインテグリティとデバイスの動作を確認します。このプロセスを支援するために、テスト機器がプローブして必要なテストを実行できるボード上のポイント(テストポイント )のスキームを持つことが基本的に有益です。

ボード上のテストポイントの位置は、テストモード(ベアボード製造テスト、インサーキットアセンブリ・テストなど)やテスト方法(フライングプローブやベッドオブネイルズフィクスチャーを使用した自動テスト、手作業によるテストなど)を含む要因によって異なります。例えば、ベアボード製造テストを実施する場合、基板は実装されていないため、テストポイントの割り当てに関しては、すべてのパッドとビアが「フェアゲーム」である。しかし、インサーキットアセンブリーテストを実施する場合、テストポイントに使用する位置はほとんどの場合異なります。基板が実装されると、部品パッドへのプローブアクセスができなくなり、部品下のパッドやビアへのアクセスもできなくなります!

Altium Designerは、テストポイントのニーズを処理し、ボードのテスト性を向上させる強力なシステムを提供し、必要に応じてベアボードファブリケーションテストやインサーキットアセンブリテスト用のテストポイントを個別に割り当てることができます。テストポイントの割り当ては、手動で行うこともできますが、Testpoint Managerダイアログを使用することで、より合理的で自動化された方法で行うこともできます。

テストポイント戦略の検討

テストポイントの位置としてパッドやビアを割り当てる前に、一歩下がって何が必要かを考えることをお勧めします。以下は、デザインにテストポイントを組み込む戦略を定義する際に考慮すべきポイン トです:

-

ボードのどの側にテストポイントを設けるかを決める際には、テストプロセスや使用する治具を考慮する必要があります。例えば、基板を下面のみからプローブするのか、上面のみからプローブするのか、あるいは両面からプローブするのか。

-

ベアボードのテスト段階では、部品の下(部品と同じ側のボード)にテストポイントを設置するのが一般的です。このことは、アセンブル・ボードのテストにおけるテストポイントの位置を計画する際に考慮する必要がある。

-

すべてのテストポイントをボードの片面だけに配置することが望ましく、必要であればビアを使用してこれを実現する。この理由は、デュアルヘッドのテスト・フィクスチャーは、シングルヘッドのテスト・フィクスチャーよりもコストがかかるという事実にあります。

-

テストポイントのパターンが非標準的で複雑であればあるほど、ボードをテストするための治具を構成するコストが高くなります。最良の哲学は、汎用的なテスト可能性をもたらす方法論を開発することです。研ぎ澄まされ、適応可能なテストポイントの方針は、異なる設計を効率的かつコスト効率よくテストすることを可能にします。

-

設計のテント張り要件については、慎重に検討する必要があります。テストポイントに指定されたビアをテント化すると、テストプローブとの接触が効果的に遮断されます。LPI(Liquid Photo Imageable)ソルダーマスクを使用した部分的なテント張りは、マスク液がビアホールから流出しやすいため、コンタクトの問題を引き起こします。剥離可能なソルダーマスクは、そのような指定されたビアの一時的なテント張りに確かに使用されるかもしれませんが、これはしばしば非常にコストがかかることが判明する可能性があります。

-

テストポイントを指定する際、特定の設計パラメータが考慮されていることを確認するために、製造会社や組立会社とよく相談してください。これには、テストポイント間のクリアランスや、テストポイントからコンポーネントまでのクリアランスなど、通常の配置配線クリアランスよりも厳しいものが含まれる可能性があります。

以下のセクションでは、製造試験と組立試験について、それぞれに関連する具体的なテストポイ ント制約と考慮事項を含めて詳しく見ていきます。

製造試験

製造試験は、製造の組立前段階におけるプリント回路基板の試験に関するもので、基板上に部品が配置される前の段階である。そのため、ベアボード試験と呼ばれることが多い。このテスト方法では、一般的にフライングプローブデバイスを使用してネットバイネットテストを実施します。基本的には、2つのプローブが連動して動作するようにプログラムされ、一方がネットを通して信号をパルス化し、もう一方がその信号の有無(または有無)を検出します。

ベアボード製造テストの一般的なテストシナリオは次の2つです:

-

意図的に端から端まで連続した銅が、(最大許容インピーダンスのしきい値の下で)きれいな信号を、開回路のない状態で伝送することを確認するテスト。

-

ネットが互いに短絡していないことを確認するテスト。

Testpoint Location Constraints

-

ファブリケーション・テストでは、専用のテストポイントパッド/ビアは通常必要ありません。基板にはまだ部品が搭載されていないため、プローブは部品パッドに自由にアクセスできます。この段階では、パッドにはんだマスクがないことが多いため、テストポイントは通常、パッド自体に直接配置されます。

-

フライングプローブは非常に精密な位置決めが可能であるため、フライングプローブテストはグリッドによる制約を受けない。

-

プローブヘッドの物理的な大きさのため、各位置のペアは最小限の間隔によって制約されます。

例外とその他の考慮事項

-

ファインピッチ・デバイスの場合、単一の部品パッドをプローブすることは不可能(あるいは実用的)かもしれません。そのような銅フィーチャーは極小でデリケートであるため、テストプローブとの接触を避けることが推奨される場合があります。このような場合、設計者はボードに専用のテストパッド/ビアを追加するのがよいでしょう。

-

ベアボードの製造テストでは、ベッドオブネイル治具を使用することもできます。このような治具を使用すると、フライングプローブよりもテスト時間が短くなります。しかし、ベッドオブネイルテストでは、テストポイントの位置の制約がより厳しくなることがあり、テスト治具がカスタマイズされたものでない場合には、テストポイントが特定のグリッドに適合することがしばしば要求されます。

-

特定のテストポイント位置のペアが、フライングプローブによって協調してテストされない場合があります。これは通常、ネットが隣接していない(両方のネットのすべてのオブジェクトが物理的な近接によって相互に分離されている)ため、ネット間のショート(またはクロストーク)の危険性がない場合です。

組立試験

組立試験とは、部品表(BOM)で指定された部品がすべて実装された後の、組立後の製造段階におけるプリント回路基板の試験に関するものである。そのため、インサーキットテストまたは電気テストと呼ばれることが多い。この試験方法には、通常、手動で構成されたベッドオブネイル治具が使用されます(ただし、これに限定されるものではありません)。治具を使用して実施される試験の種類によって、ボードに電源が入る場合と入らない場合があります。

インサーキットアセンブリテストの一般的なテストシナリオは以下の2つです:

-

各ネット(または関心のあるネット)に対して、1つの専用テストポイントを同時にプローブする。これは、各プローブに個別にパルス信号を送り、他のすべてのプローブによる信号受信結果を検出することによって行われる。

-

特定のコンポーネント/バスをテストし、装置自体が適切に動作していることを確認する。これらは専門的な試験であり、さまざまな試験方法を用いて実施できる。最も単純なケースでは、ベッド・オブ・ネイル治具を使用して、コンポーネントのパッド全体をテストすることができます。

テストポイントの位置の制約

テストポイントの位置の制約とは、テストポイントの位置の制約を意味します。

-

テストポイントの位置は通常、最小間隔要件に適合する必要がある。ベッド・オブ・ネイルズ・フィクスチャーのプローブ・ヘッドなどのテスト機器は、互いの近接を制約するボディ・サイズを持っています。カスタム治具を使用しない限り、テストポイントの位置は特定のグリッド上にあることが要求されることが多い。カスタム治具の製作は、再利用可能なベッド・オブ・ネイル治具を構成するよりもコストと時間がかかります。

-

テストポイントは、部品本体に対する最小クリアランスに従って配置することが要求されることがあります。ほとんどのテスト・フィクスチャのプローブ・ヘッドは、フィクスチャに近いほど大きく、プローブのシャンクに近づくにつれて小さくなる傾向があります。背の高い部品は、より大きなクリアランスを必要とします。したがって、基板上の部品の最大高さを考慮し、この最悪のシナリオを考慮したボディ全体のクリアランスを定義するのが最善です。

-

テストポイントの位置は、基板エッジに対する最小クリアランスに従って配置するよう要求することができる。フライング・プローブのペアやプローブのアレイを基板に接触させるプロセスは、基板自体に負担をかける可能性があり、自動テストのひずみによって基板がある程度たわむ可能性があります。このため、薄くて壊れやすい基板へのダメージは、テストポイントが基板の端から離れた位置にある場合に最小化される。

-

プローブがアクセス可能な専用のテストポイント・パッド/ビアは、いくつかの理由から、通常、設計中に各ネットに追加する必要があります:

-

ベア銅の部品パッドは通常、配置された部品の存在によってアクセスできなくなる。

-

基板がテストを念頭に置いて特別に設計されていない限り、部品パッドやビアが必要なテストポイント・グリッド上に配置されることはまずありません。

-

部品パッドそのものがテストポイントの位置として適しているように見えても、部品本体とのクリアランスの制約がその使用を妨げることが多い。

例外とその他の考慮事項

-

ベッドオブネイルフィクスチャーはアセンブリー試験の一般的な方法ですが、決してそれが唯一の方法というわけではありません。さまざまな選択肢の中には、フライングプローブ装置を使用するケースもありますが、設置された部品と衝突しないように注意が必要です。

-

特定の部品に対して電気試験を行う場合、部品パッドはある程度テストプローブでアクセスできるかもしれない。しかし、部品本体がそのようなパッドの中心を隠していることが多いことに注意することが重要である。言い換えれば、基板が組み立てられた後、パッドのアクセス可能な部分にパッドの中心位置が含まれることはほとんどない。

パッドとビアのテストポイントのサポート

Altium Designer はテストポイントを完全にサポートしており、パッド(スルーホールまたはSMD)またはビアを指定し、ファブリケーションやアセンブリテストでテストポイントとして使用することができます。パッドまたはビアは、関連するテストポイントプロパティを設定し、2つの重要な質問に答えることにより、テストポイントとして使用することができます:

-

パッド/ビアを製造/組立テストポイントとして使用すべきか?

-

パッド/ビアを基板のどの面(上面、下面、またはその両方)でテストポイントとして使用するか?

これらのプロパティは、デザインスペースでパッド(Pad Propertiesを参照)またはビア(Via Propertiesを参照)オブジェクトが選択されると、プロパティパネルで確認できます。

選択されたパッドまたはビアは、Propertiesパネルから利用可能な関連オプションを通して、テストポイントとして使用するために指定されます。

選択されたパッドまたはビアは、Propertiesパネルから利用可能な関連オプションを通して、テストポイントとして使用するために指定されます。

プロセスを合理化し、パッド/ビアのテストポイントプロパティを手動で設定する必要性を軽減するために、Altium Designer では、定義されたデザインルールに基づき、

Testpoint Manager を使用してテストポイントを自動的に割り当てる方法を提供しています。この自動割り当てにより、それぞれのケースでパッド/ビアに関連するテストポイントプロパティが設定されます。また、手動でテストポイントを指定するオプションもあり、要するに、個々のパッド/ビアレベルでハンドクラフトすることで、ボードに採用するテストポイントスキームを完全にコントロールすることができます。

Summer 09 リリース以前のソフトウェアで作成した PCB デザインを開く場合、有効なテストポイントオプションは、有効なFabricationテストポイントオプションになります。

テストポイントの設計ルール

PCB デザインの制約は、練り上げられたデザインルールとして実装されるべきです。すべての定義されたテストポイントがアクセスでき、ベアボードやインサーキットテストの一部として使用できる、成功するテストポイントスキームを実装するために、制約を管理する必要があります。この目的のために、以下のルールタイプは PCB エディタの Design Rules システムの一部として定義可能です:

PCB Rules and Constraints Editor ダイアログ(Design » Rules)からこれらのタイプのルールにアクセスし定義します。

デザイン内のどのパッドやビアがファブリケーションテストポイントやアセンブリテストポイントとして使用でき、どのネットがテストポイントを必要とするかを制約するために個別のデザインルールを定義します。

デザイン内のどのパッドやビアがファブリケーションテストポイントやアセンブリテストポイントとして使用でき、どのネットがテストポイントを必要とするかを制約するために個別のデザインルールを定義します。

Testpoint StyleルールとUsageルールは、2つのテストモード(ファブリケーションとアセンブリ)間で制約という点では同じです。スタイルルールは、基本的に、パッドまたはビアがテストポイントの位置として選択されるために満たすべき制約を指定します。使用ルールは、どのネットがテストポイントを必要とするかを指定します。

Testpoint Usageルール(上)とTestpoint Styleルール(下)のデフォルト制約。

Testpoint Usageルール(上)とTestpoint Styleルール(下)のデフォルト制約。

スタイルルールを定義する際、Rule Scope Helper領域で利用可能なオプションを使用して、テストポイントを考慮する正確なパッドやビア・オブジェクトをターゲットとするルール・スコープを素早く作成することができます。

テストポイント・デザイン・ルールは、テストポイントマネージャ、オートルーター、オンラインDRC、バッチDRCプロセス、および出力生成時に使用されます。

デフォルトのファブリケーションおよびアセンブリ テストポイント スタイルとテストポイント使用ルールがあります。これらのルールがボードの要件に合っているかを確認し、必要に応じて変更してください。同じタイプのルールが複数必要な場合は、デザイン ルールの優先順位を使用して、より具体的なスコープを持つルールが最初に適用されるようにします(DRC の実行時など)。

Testpoint Managerが正常にテストポイントを割り当てるには、All のスコープを持つ対応する Testpoint Style ルールが常に 1 つ以上必要です。

PCB デザインを開く、または Summer 09 リリース以前のソフトウェアで作成したデザインルールをインポートする場合、Testpoint Style ルールは Fabrication Testpoint Style ルールになり、Testpoint Usage ルールは Fabrication Testpoint Usage ルールになります。

テストポイントの管理

テストポイントの割り当てを手作業で行うことは、骨の折れる骨の折れる作業となります。ボードデザインのテストポイントの管理を合理化するために、Altium Designer は PCB Editor にTestpoint Manager を装備しています。Testpoint Managerは、定義されたデザインルールに基づいて、自動化された方法でベアボードファブリケーションテストやインサーキットアセンブリテストのテストポイントを割り当てることができます。この自動割り当てにより、それぞれのケースでパッド/ビアに関連するテストポイント・プロパティが設定されます。

メインメニューからTools » Testpoint Managerコマンドを選択することでアクセスできます。

テストポイントマネージャを使用して、ファブリケーションとアセンブリのテストポイント要件を迅速かつ効率的に管理します。

テストポイントマネージャを使用して、ファブリケーションとアセンブリのテストポイント要件を迅速かつ効率的に管理します。

ダイアログを使用して、便利な1つの場所からテストポイントを自動的に割り当てたり、クリアしたりすることができます。Testpoint Net Status領域には、デザイン内のすべてのネットのリストが表示され、ベアボード・ファブリケーションとインサーキット・アセンブリ・テストの両方で、テストポイントのカバレッジ(CompleteまたはIncomplete)を示すステータスが表示されます。Fabrication TestpointsまたはAssembly Testpointsボタンをクリックするか、グリッド内で右クリックすると、そのタイプのテストポイントを割り当てたり、クリアしたりするコマンドにアクセスできます。なお、ダイアログの上部領域でネットを手動で選択して、テストポイントを選択的に割り当て/クリアすることもできます。

デザイン内の一部のネットまたはすべてのネットにテストポイントを割り当てる場合、Testpoint Managerはファブリケーションおよびアセンブリのテストポイントに定義されたスタイルと使用ルールに従います。有効なオブジェクトが検索される順序を確認するには、Search Orderボタンをクリックします。

順序を変更するには、Search Order リストのエントリを右クリックし、フローティング メニュー コマンド、またはShift+上矢印とShift+下矢印 のショートカットを使用して、リストの上下に移動します。

ネットに割り当てられたテストポイントが適用可能なテストポイントデザインルールに違反する場合、

Testpoint Managerダイアログの

Testpoint Net Status領域に

Illegalと表示されます。

割り当てられたテストポイントの妥当性を確認するには、PCB エディタの Design Rule Check 機能を使用してください。

Status Summaries領域は、両方のテストモードに対して、ボードのテストポイントステータスの完全な要約を提供します。この領域は、割り当てやクリアランスを実行するたびに更新されます。より低レベルの詳細については、Assignment Results領域を使用します。これは、例えば、割り当て/クリアランスに関与したトップ/ボトムパッド/ビアの数や、失敗の表示などの詳細を提供します。

テストポイントの妥当性チェック

定義された製造とアセンブリのテストポイントルールは、PCB エディタのDesign Rule Checking(DRC) 機能の一部として従います。オンラインおよび/またはバッチ DRC チェック機能は、Design Rule Checker ダイアログ(Tools » Design Rule Check)から様々なルールタイプで有効にできます。

オンラインまたはバッチ DRC プロセスの一部としてテストポイントのデザイン・ルールを含めます。

オンラインまたはバッチ DRC プロセスの一部としてテストポイントのデザイン・ルールを含めます。

テストポイント関連のクエリ・フィールド

デザインに割り当てることができる様々なファブリケーションおよびアセンブリのテストポイントをサポートするために、論理クエリ式を使用してテストポイントをターゲットにする場合に使用できるキーワードを以下に示します。以下のそれぞれは、Query Helper を使用している時、PCB Functions - Fieldsカテゴリで見つけることができます:

-

IsAssyTestpoint- アセンブリテストポイントです。

-

IsFabTestpoint- ファブリケーションテストポイント。

-

IsTestpoint- トップまたはボトム側のテストポイントです。

-

Testpoint- トップ側テストポイントかボトム側テストポイントか。

-

TestpointAssy- 組立テストポイントかどうか。

-

TestpointAssyBottom- ボトム側のアセンブリ・テストポイントかどうか。

-

TestpointAssyTop- トップ側の組み立てテストポイントか?

-

TestpointBottom- ボトム側のテストポイントか?

-

TestpointFab- ファブリケーションテストポイントです。

-

TestpointFabBottom- ボトム側の加工テストポイントです。

-

TestpointFabTop- トップ側のファブリケーションテストポイントです。

-

TestpointTop- トップ側のテストポイントか?

クエリの論理式を作成し、必要に応じてデザイン内のテストポイントをターゲットにして返します。ファブリケーションおよびアセンブリのテストポイントをターゲットとする論理クエリ式の例を以下に示します:

-

(ObjectKind = 'Pad') And (TestpointAssy = 'True')

アセンブリ・テストポイントのすべてのパッドを対象とします。

-

IsPad And (TestpointAssyTop = 'True')

トップ側のアセンブリテストポイントであるすべてのパッドを対象とします。

-

(ObjectKind = 'Pad') And (TestpointFab = 'True')

ファブリケーションテストポイントであるすべてのパッドを対象とします。

-

((IsPad または IsVia)) かつ (TestpointAssy = 'True')

アセンブリテストポイントであるすべてのパッドとビアを対象とします。

-

((IsPad または IsVia)) かつ IsFabTestpoint

ファブリケーション・テストポイントであるすべてのパッドとビアを対象とする。

テストポイントレポートの生成

Altium Designer には、ファブリケーションとアセンブリのテストポイントレポートを生成する専用のレポートジェネレータがあります。これら 2 つのレポートジェネレータは、デザイン内のパッドとビアのプリミティブに関連するテストポイントプロパティを利用します。

ファブリケーション・テストポイント・レポートでは、パッドとビアのFabricationテストポイント設定のみが使用されます。アセンブリテストポイントレポートは、Assemblyテストポイント設定のみを使用します。

レポートは、2つの方法で生成できます:

自己完結的で汎用性の高い出力ジョブ構成ファイル内に、製造および組立テストポイント・レポート出力を含め、構成します。一度定義すれば、ボタンを押すだけでレポートを取得できます!

自己完結的で汎用性の高い出力ジョブ構成ファイル内に、製造および組立テストポイント・レポート出力を含め、構成します。一度定義すれば、ボタンを押すだけでレポートを取得できます!

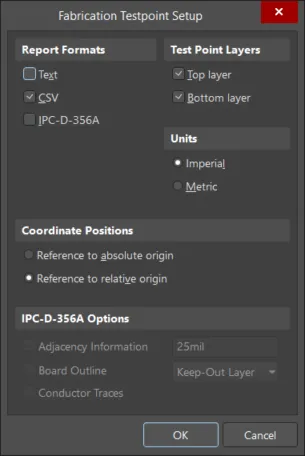

レポートの生成方法にかかわらず、レポートオプション自体は同じダイアログで定義されます。ファブリケーション・テストポイント・レポートでは、Fabrication Testpoint Setupダイアログを使用します。アセンブリテストポイントレポートでは、Assembly Testpoint Setupダイアログが使用されます。レポートオプションは、これらのダイアログ間で同じです。

関連するレポートセットアップダイアログを使用して、生成されたファイル形式を含むレポートオプションを定義します。

PCB から直接出力を生成する時、Testpoint Setupダイアログで定義された設定は、Output Job Configuration ファイルで同じ出力タイプのために定義された設定とは別個のものです。前者の場合、設定はプロジェクトファイルに保存され、後者の場合は Output Job ファイルに保存されます。

ダイアログのCoordinate Positions領域のオプションは、すべてのレポートフォーマットのテストポイント位置を、絶対ボード原点または現在のボード原点に対して相対的にエクスポートすることを可能にします。

すべてのテストポイントレポートタイプは、埋め込みボードアレイをサポートしています。複数の埋め込みボードアレイを含む PCB ドキュメントからエクスポートすると、複数の IPC-D-356A ネットリストファイルが生成されます。

IPC-D-356A ネットリストファイルの役割

テストポイントレポートの 3 種類の出力形式の 1 つに、IPC-D-356A ネットリストファイルがあります。このファイルは通常、ベアボードファブリケーションテストモードのターゲットに使用されます。IPCファイルは、フライングプローブテストデバイスを駆動するコマンドに後処理されます。

IPC-D-356Aファイルの中で、どの機能がテストポイントとして特定されているかに関係なく、基板製造会社は、一般的にファイル・データを使用して、どのようなタイプのテストでも実施することができます。