PCBレイアウトのための電気設計ルールの種類

Altium Essentials: PCB Design Rules Creation

This content is part of the official Altium Professional Training Program. For full courses, materials and certification, visit Altium Training.

Electricalカテゴリのデザインルールについて以下に説明します。

Electricalカテゴリのデザインルール。

クリアランス

デフォルトルール: 必須

このルールは、銅箔レイヤー上の任意の 2 つのプリミティブオブジェクト間に許容される最小クリアランスを定義します。クリアランスには単一の値を指定することも、専用の Minimum Clearance Matrix を使用してオブジェクトの組み合わせごとに異なるクリアランスを指定することもできます。後者は、ルールスコープと組み合わせることで、非常に厳しいクリアランス要件にも対応できる、簡潔で対象を絞ったクリアランスルール群を柔軟に構築できます。

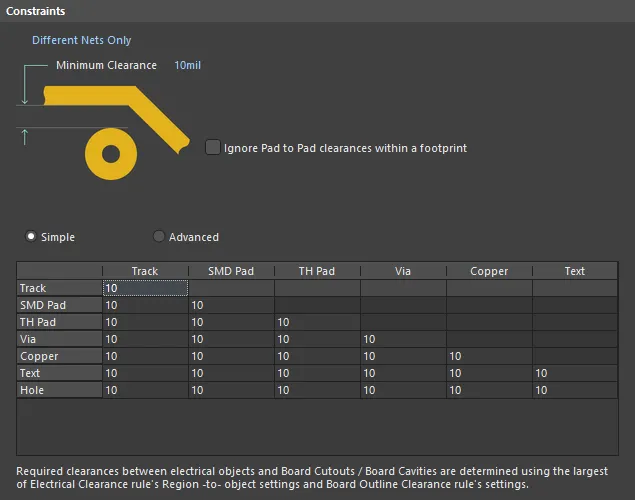

制約

ルールスコープはオブジェクトのセットを返し、以下に示す制約がそのオブジェクトセットに適用されます。

-

Connective Checking - ルールスコープによって返されたネットオブジェクトのセットは、さらに次の方法で絞り込むことができます。

-

Different Nets Only- 制約は、異なるネットに属する任意の 2 つのプリミティブオブジェクト間に適用されます(例: 異なる 2 つのネット上の 2 本のトラック)。 -

Same Net Only- 制約は、同じネットに属する任意の 2 つのプリミティブオブジェクト間に適用されます(例: 同じネット上のビアとパッドの間、または同じネット内の 2 つのトラックセグメント間)。 -

Any Net- 制約は、設計内の任意のネットに属する任意の 2 つのプリミティブオブジェクト間に適用されます。これは 3 つのオプションの中で最も包括的であり、オブジェクトが同じネットに属する場合も異なるネットに属する場合も対象となります。 - Different Differential Pair - 制約は、異なる差動ペアに属する異なるネット上の任意の 2 つのプリミティブオブジェクト間に適用されます(例: DiffPair1 上のトラックと DiffPair2 上のトラック)。このルールは、同じ差動ペア内の 2 つのネット上のプリミティブ間には適用されません(例: DiffPair1_P と DiffPair1_N)。この制約を使用して、差動ペア間のクリアランスを設定します。

-

Same Differential Pair - 制約は、同じ差動ペア内の異なるネットに属する任意の 2 つのプリミティブオブジェクト間に適用されます(例: TX_P 上のトラックと TX_N 上のトラック)。この制約を使用して、差動ペア内のネット同士を一般的なクリアランスで許容されるよりも近づける必要がある場合のクリアランスを設定します。

-

- Ignore Pad to Pad Clearances within a footprint - このオプションをオン/オフして、同じコンポーネントフットプリント内のパッド間クリアランスを無視するかどうかを指定します。このオプションはデフォルトで無効です。

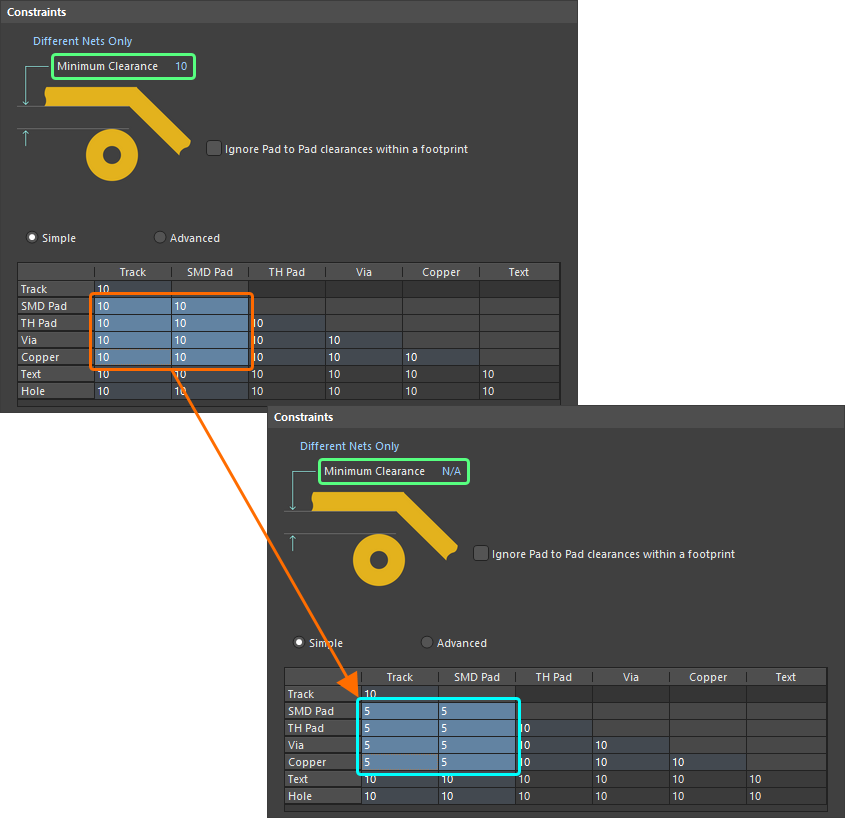

- Minimum Clearance - 必要な最小クリアランスの値です。ここに入力した値は、Minimum Clearance Matrix のすべてのセルに複製されます。逆に、マトリクス内の 1 つ以上のオブジェクト組み合わせに対して異なるクリアランス値を入力すると、単一のクリアランス値が基板全体に適用されていないことを反映して、Minimum Clearance 制約は N/A に変わります。

- Minimum Clearance Matrix - 設計内のさまざまなオブジェクト間クリアランスの組み合わせを細かく調整する機能を提供します。

Clearance Matrix の操作

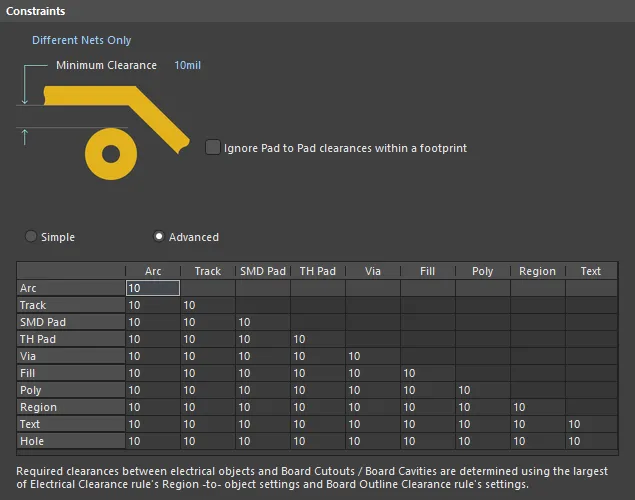

多くのユーザーにとって、Track プリミティブと Arc プリミティブに大きな違いはありません。また、Fill、Region、Polygon オブジェクトについても、多くのユーザーは単により多くの「銅箔」として捉えています。これを踏まえ、Clearance ルールの最小クリアランスマトリクスは、次の 2 つのモードで動作するよう強化されています。

- Simple - このモードでは、Track オブジェクトと Arc オブジェクト(Track Keepout および Arc Keepout オブジェクトを含む)は単一の Track エントリに統合されます。Fill、Poly、Region オブジェクト(Fill Keepout および Region Keepout オブジェクトを含む)は単一の Copper エントリに統合されます。Simple モードは、既存の設計を開く場合でも新しい設計を開く場合でも、デフォルトモードです。

- Advanced - このモードは従来のマトリクスで、すべてのオブジェクトが表示されます。

マトリクス内のクリアランス値は、次の方法で定義できます。

- 単一セル編集 - 特定のオブジェクト組み合わせに対する最小クリアランスを変更します。セルをクリックして編集対象として選択します。

-

複数セル編集 - 複数のオブジェクト組み合わせに対する最小クリアランスを変更します。

- Ctrl+Click、Shift+Click、および Click+Drag を使用して、列内の複数セルを選択します。

- Shift+Click および Click+Drag を使用して、行内の連続する複数セルを選択します。

- Click+Drag を使用して、複数の行と列にまたがる連続する複数セルを選択します。

- 行ヘッダーをクリックすると、その行のすべてのセルをすばやく選択できます。

- 列ヘッダーをクリックすると、その列のすべてのセルをすばやく選択できます。

必要な選択(単一セルまたは複数セル)ができたら、現在の値を変更するには、必要な新しい値を入力するだけです。新しく入力した値を確定するには、別のセルをクリックするか、Enter を押します。選択内のすべてのセルが新しい値で更新されます。

複数セル編集の例。1 つ以上のオブジェクト組み合わせに対して異なるクリアランス値が存在するようになると、単一のクリアランス値がすべてのオブジェクト間クリアランスの組み合わせに適用されなくなったことを反映して、Minimum Clearance 制約は N/A に変わることに注意してください。

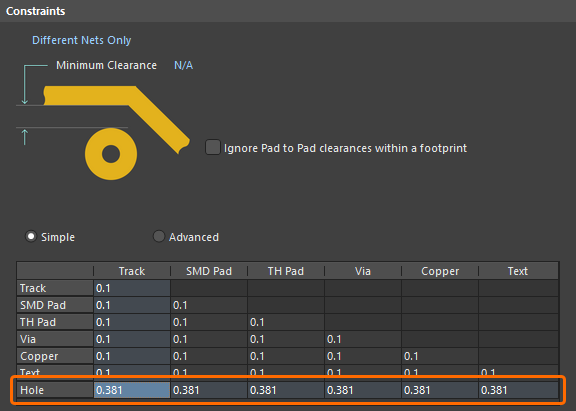

穴とオブジェクト間のクリアランスチェック

設計者は、ドリル穴のエッジと信号レイヤー上の隣接する銅箔オブジェクトとの間のクリアランスをチェックできます。これは、基板製造時のドリルのぶれによる影響を受ける可能性がある、ドリル穴に近すぎるトラック配線を防ぐうえで特に有効です。必要なクリアランスは、Clearance ルールの最小クリアランスマトリクスの最下段で定義します。

設計内でドリル穴のエッジに近すぎる銅箔オブジェクトを検出できるよう、クリアランス値を設定します。

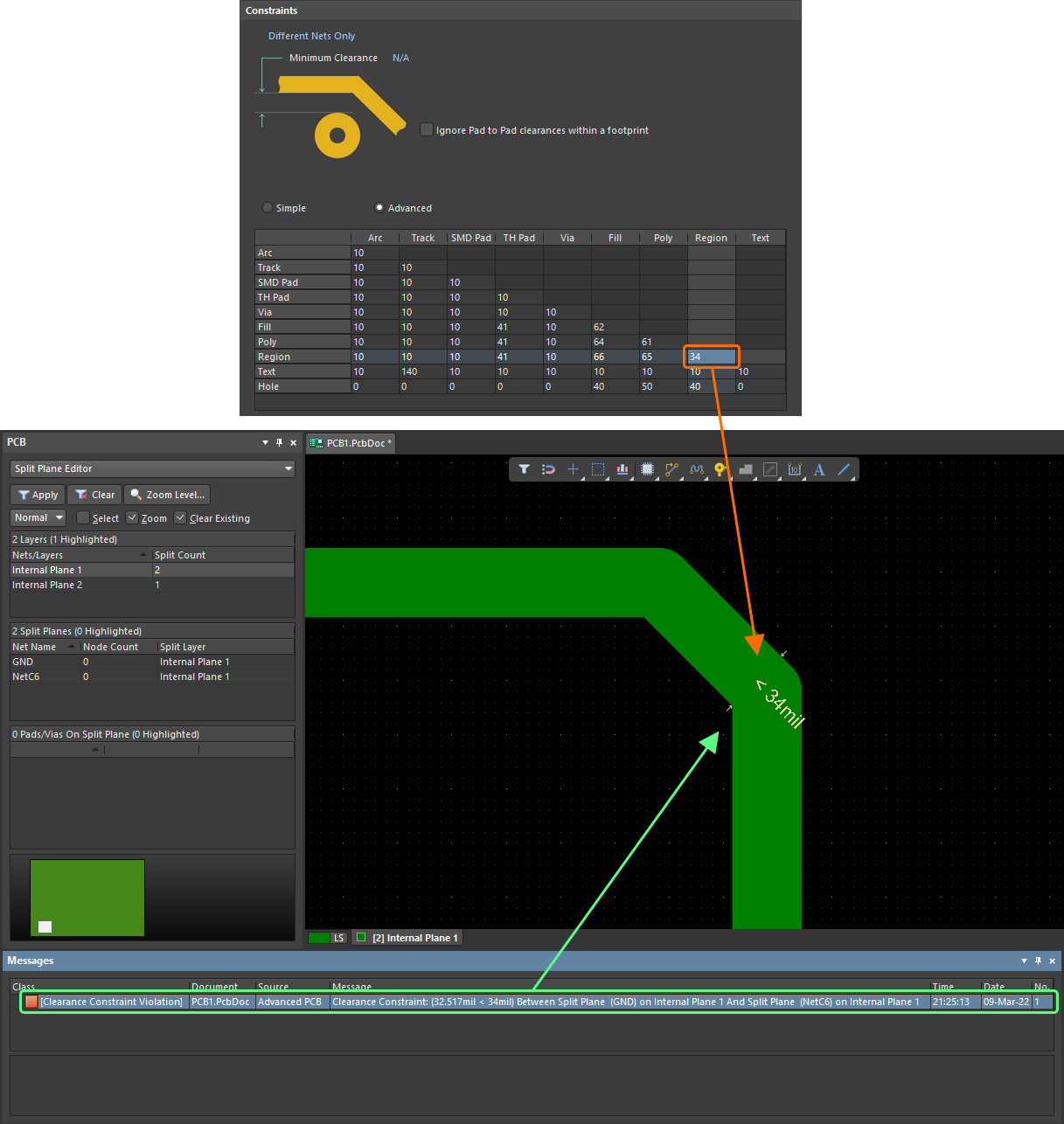

スプリットプレーンクリアランスチェック

設計者は、内部プレーンレイヤー上のスプリットプレーン領域間のクリアランスもチェックできます。クリアランスの定義方法は、最小クリアランスマトリクスをどのモードで使用しているかによって異なります。

- Simple mode - Copper-Copper セルを使用して、必要なスプリットプレーン間クリアランス値を指定します。

- Advanced mode - Region-Region セルを使用して、必要なスプリットプレーン間クリアランス値を指定します。

違反は次の形式で表示されます。

Clearance Constraint: (<CurrentClearance> < <DefinedClearance>) Between Split Plane (<NetName>) on <InternalPlaneLayerName> And Split Plane (<NetName>) on <InternalPlaneLayerName>,

たとえば次のようになります。

Clearance Constraint: (32.36mil < 34mil) Between Split Plane (GND) on Internal Plane 1 And Split Plane (NetC6) on Internal Plane 1

内部レイヤー上のスプリットプレーン領域間のクリアランスチェック。この場合、クリアランスはマトリクスの Advanced モードを使用して定義されているため、34mil の値が Region-Region セルに入力されています。

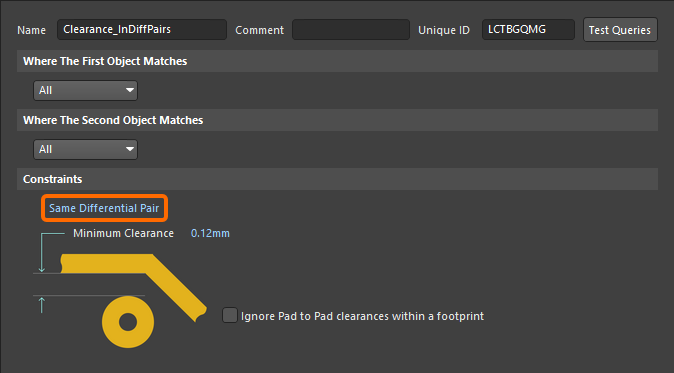

差動ペアクリアランスチェック

差動ペアには固有の設計上の課題があり、多くの場合、特定の within-pair クリアランスに加えて pair-to-pair クリアランス、さらに場合によっては pair-to-all other nets クリアランスを制御する 3 つ目のルールが必要になります。これをサポートするため、Constraints 領域には Same Differential Pair および Different Differential Pair オプションを選択できるドロップダウンが含まれています。

たとえば、差動ペア内のネットに一般的な基板クリアランスよりも厳しいクリアランスが必要な場合、以下に示すように Same Differential Pair 制約オプションを使用して実現できます。このルールスコープは設計内の All ネットオブジェクトに適用されますが、Constraint 設定によって Same Differential Pair 内のオブジェクトにのみ適用される点に注意してください。

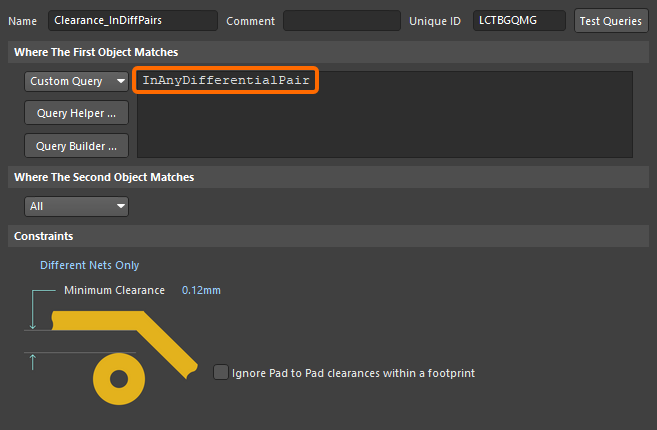

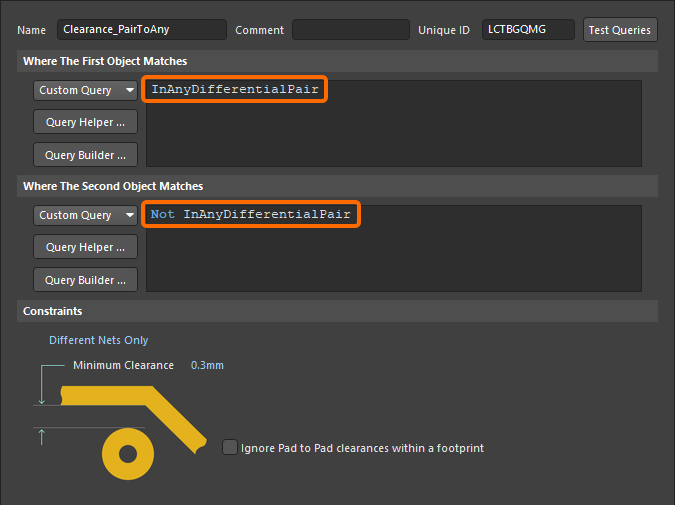

この結果は、以下に示すように、ルールスコープを差動ペアオブジェクトのみに適用すること(例: InAnyDifferentialPair)でも実現できます。ただし、このルールは差動ペア内のネットと設計内の他の任意のネットオブジェクトとの間にも適用されるため、この方法は DiffPairNet-to-DiffPairNet および/または DiffPairNet-to-Any 要件を定義する、より優先度の高い別ルールがある場合にのみ使用してください。この方法を使用する場合は、差動ペアルールの Priority も正しく設定する必要があり、より厳しいクリアランス要件を持つルールの優先度を高くする必要があります。

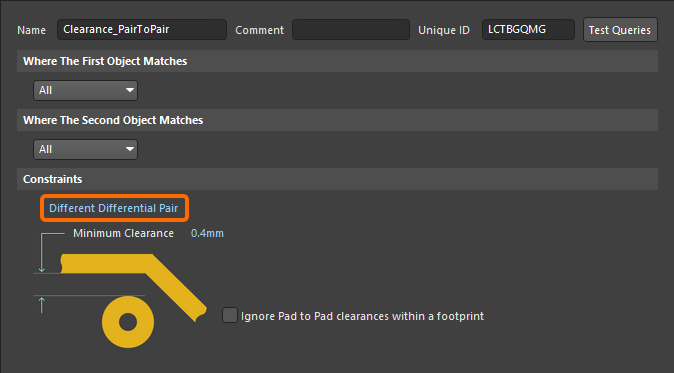

同様の方法で、差動ペア between のクリアランスを制御することもできます。以下の画像は、これを実現するために Different Differential Pair 制約をどのように使用できるかを示しています。

前の例と同様に、Different Differential Pairs 制約の代わりにルールスコープを使用して実現することもできます。より厳しいクリアランス要件を持つルールの優先度が高くなるように、ルールの優先順位を設定する必要があることを忘れないでください。

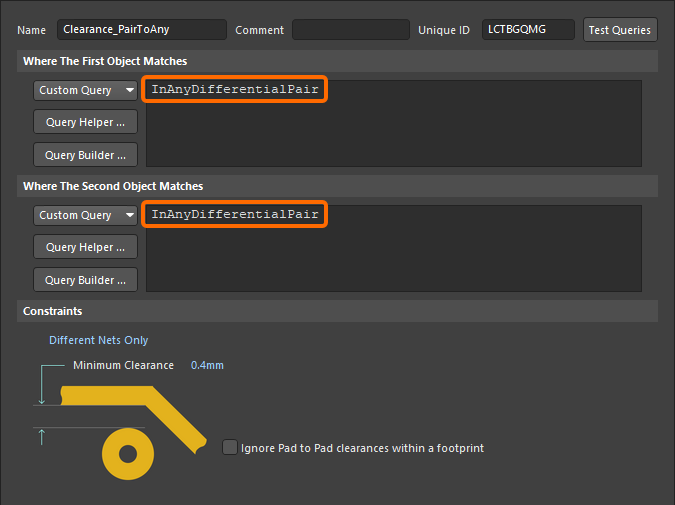

差動ペアネットから他の任意のネットオブジェクトへの異なるクリアランスを定義するには、次のルールを使用できます。

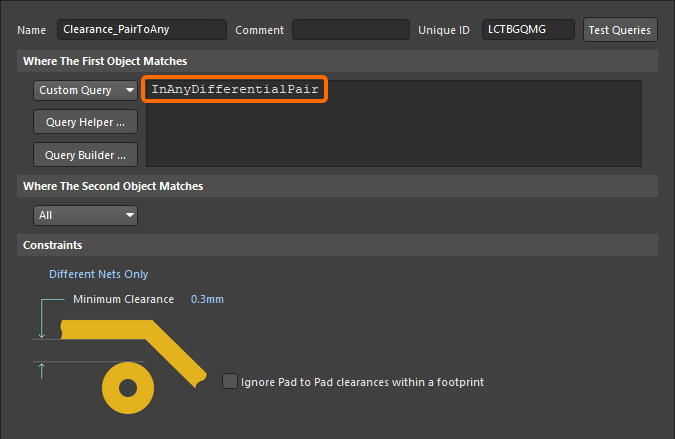

さらに絞り込んで、以下に示すように、差動ペアオブジェクトと非差動ペアオブジェクトの間にのみ適用することもできます。

差動ペアルーティング の詳細をご覧ください。差動ペア設計ルール のスコープ設定の詳細もご覧ください。

ルールの適用

オンライン DRC、バッチ DRC、インタラクティブルーティング #、オートルーティング #、およびポリゴン配置。

注記

- # DRC は、どのような種類のルールスコープを使用しても、任意のオブジェクト種別同士のクリアランスをテストできますが、ルーティングエンジンはこのレベルの細かさをサポートしていません。たとえば、基本のクリアランスルールではすべてのトラックに 1 mm のクリアランスを要求し、より高い優先度のルールでは長さが 10 mm を超えるトラックに 2 mm のクリアランスを要求する場合があります。この状況では、インタラクティブルーティングエンジンは基本のクリアランスルールに従い、長さが 10 mm を超える高優先度ルールは無視します。別の例として、コーナーにアークを使用したルーティングがあります。クリアランスルールでトラックよりアークに対して大きいクリアランスが指定されていて、コーナーにアークを使ってインタラクティブルーティングしている場合、インタラクティブルーティングエンジンはアーク設定を無視してトラック設定に従い、コーナーのアークもトラックセグメントと同じクリアランスで配置します。これらの例ではいずれも、ルーティングが完了するとすぐに Online DRC がそれらの状況を違反として報告します。

-

ルールの制約を定義する際、通常は Connective Checking オプションを

Different Nets Onlyに設定します。Same Net OnlyまたはAny Netを使用できる例としては、同一ネットまたは別ネット上で、ビアがパッドや他のビアに近すぎる位置に配置されていないかをテストする場合などがあります。 - 最小クリアランスマトリクスは、指定された接続性チェック方法に関係なく適用されます。同一ネット上のオブジェクト間に、異なるネット上のオブジェクトに対して定義されたものとは異なるクリアランスが必要な場合は、それに対応する個別のクリアランスルールを必要に応じて定義してください。

- クリアランスマトリクスの適用範囲は、ルールスコープによって異なります。たとえば、スコープが ALL-ALL の場合、マトリクス内のすべてのセルが適用対象になります(つまり、考えられるすべてのオブジェクトの組み合わせ)。一方、スコープが IsVia-IsTrack に設定されている場合は、Via-Track オブジェクトの組み合わせに対応する 1 つのセルのみが適用対象となり、マトリクス内の他のすべてのセルは未使用のままになります。

-

ポリゴンに対するクリアランスルールを定義する場合、実際にルールが適用されるのはポリゴンそのものではなく、そのポリゴンを構成するプリミティブです。この場合、Full Query には

IsPolygon(またはIsPoly)ではなく、キーワードエントリInPolygon(またはInPoly)を含める必要があります。また、特定のポリゴンクリアランスルールを有効にするには、一般的なクリアランスルールよりも高い優先度を設定する必要があります。 - 配線中(および同様の操作中)、ルールエンジンは編集中のポイント周辺に障害物がないかを常にチェックします。スキャンされる領域には、プリミティブ自体の領域に加えて、そのプリミティブの周囲に必要なクリアランス領域も含まれます。つまり、ルールで定義されたクリアランスが大きいほど、スキャンが必要な領域も大きくなり、その結果、操作は遅くなります。大きなクリアランスが必要なのが少数のオブジェクトだけである場合は、それらに対して大きなクリアランスルールを定義する代わりに、特定のオブジェクトの周囲にキープアウトを追加することで、配線エンジンの速度低下を回避できます。

- Dielectric Shapes Generator を Printed Electronics の Auto モードで使用する場合、誘電体形状は、適用される Clearance Constraint デザインルールの要件を満たすよう自動的に拡張されます。

- Printed Electronics では、ネット間クリアランスは同一レイヤー上だけでなく、すべてのレイヤーでテストされます。

Short-Circuit

デフォルトルール: 必須

このルールは、銅箔(信号およびプレーン)レイヤー上のプリミティブオブジェクト間の短絡をテストします。異なるネット名を持つ 2 つのオブジェクトが接触している場合、短絡が存在します。

Constraints

Short-Circuit ルールのデフォルト制約

Allow Short Circuit - ルールの 2 つのスコープ(フルクエリ)に該当する対象ネット同士を短絡可能にするかどうかを定義します。たとえば、設計内で 2 つのグランドシステムを接続する場合のように、異なる 2 つのネットを短絡させる必要がある場合は、このオプションが有効になっていることを確認してください。

Rule Application

Online DRC、Batch DRC、および自動配線中。

Notes

-

Printed Electronics design では、異なるネットが異なるレイヤー上で交差すると、短絡としてフラグされます。これらの交差は、非導電性レイヤー上に誘電体パッチを配置することで絶縁されます。

-

このルールは Wire Bonding にも適用されます。異なるネットのダイパッドまたは銅箔にボンドワイヤが接続されている場合、あるいは異なるネットのボンドワイヤ同士の端点が接続されている場合に違反が発生します。

Un-Routed Net

デフォルトルール: 必須

このルールは、ルールのスコープ(フルクエリ)に該当する各ネットの完了状態をテストします。ネットが未完了の場合は、各完了済みセクション(サブネット)が配線完了率とともに一覧表示されます。配線完了は次のように定義されます。

(connections complete / total number of connections) x 100

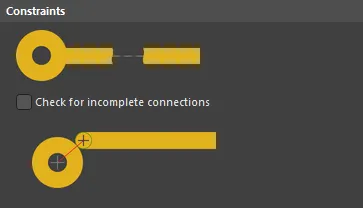

PCB Editor の Design Rule Checking システムでは通常、ネット内のすべてのノード(コンポーネントパッド)が、ネット認識可能な設計オブジェクト(トラック、アーク、パッド、ビア、ポリゴン)を介して接続されていれば、そのネットは配線済みと見なされます。これらのオブジェクトは、互いに接触していれば接続されていると見なされます。しかし、単に接触しているだけでもソフトウェア上は接続と認識される一方で、実際に基板を製造する段階では、こうした「接続」の脆弱性が重大な問題を引き起こすことがあります。特に、たとえば連続する 2 つのトラックセグメントや、パッド/ビアに入るトラックが、わずかに触れているだけの場合です。このような接続はしばしば「Bad Connections」、「Poor Connections」、または「Incomplete Connections」と呼ばれます。このルールは、そのような不十分な接続をテストするように設定することもできます。

Constraints

Un-Routed Net ルールのデフォルト制約

Check for incomplete connections - このオプションを有効にすると、該当する設計オブジェクト間の接続性について、以下の追加チェックが行われます。

- Track/Arc to Track/Arc - 接続するトラック/アークセグメントの中心線、または端部中心が一致していることをチェックします。

- Track/Arc to Via - トラック/アークセグメントの中心線、または端部中心がビアの形状上に配置されていることをチェックします。

- Track/Arc to Pad - トラック/アークセグメントの中心線、または端部中心がパッドの形状上に配置されていることをチェックします。

- Via to Pad - ビアの中心がパッドの形状上に配置されていることをチェックします。

- Via to Via - あるビアの中心が別のビアの形状上に配置されていることをチェックします。

- Polygon to Track/Arc - トラック/アークセグメントの中心線、または端部中心がポリゴンに重なっていることをチェックします。

- Polygon to Pad/Via - Pad/Via がポリゴンに直接接続されている場合、Pad/Via の中心がポリゴンに重なっていることをチェックします。

Rule Application

Batch DRC。

Notes

-

不十分な接続は、対応するメッセージが Messages パネルに表示されるとともに、詳細違反マーカー

を使用して設計空間内でフラグされます。

を使用して設計空間内でフラグされます。

-

該当する場合、ネット内で未接続のオブジェクト間に接続線が描画され、未配線ネット長に関するデータが PCB panel に反映されます(Nets mode 内)。

-

一部の DRC チェックでは、機能させるために Un-Routed Net ルールを Batch 有効にしておく必要があります。

-

Printed Electronics では、レイヤー遷移にビアは not 必要ありません。そのため、配線済みネットからビアが削除されても、ネットアナライザーはそのネットが切れていないと認識します。基板は、Layer Stack Manager で Printed Electronics オプションが有効になっている場合に Printed Electronics として定義されます。Printed Electronics の詳細をご覧ください。

-

このルールは Wire Bonding にも適用されます。同一ネットのダイパッド、ボンドワイヤ、および/または銅箔オブジェクト間に接続がない場合に違反が発生します。

未接続ピン

デフォルトルール: 必須ではありません

このルールは、ネットが割り当てられておらず、接続トラックもないピンを検出します。

制約

なし

ルールの適用

オンラインDRCおよびバッチDRC。

変更されたポリゴン

デフォルトルール: 必須

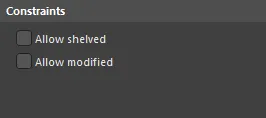

このルールは、まだシェルブされたままのポリゴン、および/または変更されたものの、まだ再ポアされていないポリゴンを検出します。

制約

変更されたポリゴンルールのデフォルト制約

- Allow shelved - 有効な場合、このデザインルールのスコープ内にあり、現在シェルブされているすべてのポリゴンは、違反としてフラグされません。

- Allow modified - 有効な場合、このデザインルールのスコープ内にあり、現在変更されているものの再ポアされていないすべてのポリゴンは、違反としてフラグされません。

ルールの適用

オンラインDRCおよびバッチDRC。

沿面距離

デフォルトルール: 必須ではありません

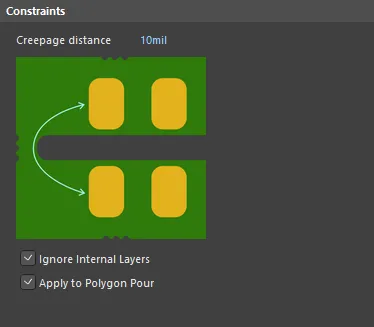

このルールは、基板表面上で、非めっき穴、切り欠き、および基板外形の周囲を通る対象信号間の沿面距離を検証します。

制約

沿面距離ルールのデフォルト制約

- Creepage distance – 第1オブジェクト上の任意の点が、第2オブジェクト上の任意の点からの距離以下である場合、ルール違反としてフラグされます。

- Ignore Internal Layers – このオプションを使用すると、ルールが外層にのみ適用されるようにできます。

- Apply to Polygon Pour – このオプションを使用すると、スコープ対象のポリゴンにルールを適用できます。

ルールの適用

オンラインDRC、バッチDRC、および自動配線中。

注記

-

沿面距離ルールは、デフォルトではオンラインまたはバッチのデザインルールチェックで有効になっていません。Design Rule Checker dialog の Tools » Design Rule Check, Electrical カテゴリで、オンライン/バッチチェックを有効にしてください。

-

ルール違反の表示も設定が必要な場合があります。PCB Editor - DRC Violation Display page (Preferences ダイアログ内)で、Violation Details(ローカライズされた違反情報)および/または Violation Overlay(違反しているオブジェクト全体のハイライト)を有効にします。

-

このルールは、対象ネット上の最も近い点を特定し、それらの間の距離を X、Y、Z 平面で確認します。

-

パッドを配置して基板スロットを作成した場合、ソフトウェアはめっきされたバレルを導電性と見なして沿面距離をそれに応じて短く計算するため、パッドプロパティで Plated オプションが無効になっていることを確認してください。

-

沿面距離デザインルールで Apply to Polygon Pour オプションを有効にしてポリゴンポアや他のオブジェクトをスコープし、さらに Clearance design rule も適用されている場合は、両方のルールが考慮され、ポリゴンのポア時にはより大きい値が適用されます。たとえば、沿面距離ルールの制約値が Clearance ルールより大きい場合、その大きい値が適用されます。

Z軸クリアランス

デフォルトルール: 必須ではありません

このルールは、異なる銅箔レイヤー上のさまざまなプリミティブ間の最小クリアランスを検証します。

制約

Z軸クリアランス距離ルールのデフォルト制約

Z-Axis Clearance – 第1オブジェクトと第2オブジェクトが異なる銅箔レイヤー上に配置されている場合、第1オブジェクト上の任意の点が第2オブジェクト上の任意の点からの距離以下であると、ルール違反としてフラグされます。

ルールの適用

オンラインDRC、バッチDRC。

注記

-

ルールに対して Violation Details の表示が有効な場合(PCB Editor – DRC Violations Display page の Preferences ダイアログ)、PCB設計空間内の違反テキストは次の形式で表示されます:

< [RuleValue] ([Actual Z-Axis Clearance Value]; XY: [Z-Axis Clearance Projected on XY]),ここで、

[RuleValue]はルールで指定された制約、[Actual Z-Axis Clearance Value]は異なるレイヤー上のプリミティブのエッジ間の最短対角距離です。ソフトウェア内の他の場所では、次の形式が使用されます:

Z-Axis Clearance: ([Actual Z-Axis Clearance Value] < [RuleValue]) Between [Object1Description] And [Object2Description] -

このルールは、ポリゴンポア(ソリッドおよびハッチ)と内部プレーンでサポートされています。なお、ポリゴンに対してボイドが作成されるのは、ポリゴンと他タイプのオブジェクト(トラック、パッドなど)との間で違反が検出された場合のみです。異なる信号レイヤー上のポリゴンポア間でもクリアランスと違反は検出されますが、この場合、ボイドは自動的には作成されません。

-

また、信号レイヤー上のオブジェクトと内部プレーンとの間でも、最短距離に基づいてクリアランスと違反が検出されますが、そのような違反は手動で解消する必要があります。

-

この機能をサポートしていない古いバージョンの Altium Designer で、定義済みの Z軸クリアランスルール/制約を含むPCBを開くと、それらのルールは失われます。

AI で翻訳

AI で翻訳