デザインルールチェッカー

Parent page: PCB ダイアログ

概要

このダイアログでは、基板のデザインルールチェックを設定できます。デザインルールチェック(DRC)は、設計の論理的整合性と物理的整合性の両方を検証する強力な自動機能です。チェックは、有効化されている任意の(またはすべての)デザインルールに対して実行され、設計中にオンラインで行うことも、バッチ処理(任意でレポート出力)として行うこともできます。この機能は、配線済みのすべての基板で使用し、最小クリアランス ルールが維持されていること、ならびにその他の設計違反がないことを確認する必要があります。特に、最終アートワークを生成する前には、必ずバッチモードのデザインルールチェックを実行することを推奨します。

アクセス

このダイアログは、PCB エディタのメインメニューから Home | Design Rules | ![]()

オプション/コントロール

このダイアログの機能は、基本的に次の 2 つの領域に分かれます。

- バッチ DRC に関するオプションの設定。

- チェックするルールの設定、およびそれらのルールをオンライン DRC と/またはバッチ DRC のどちらでチェックするかの設定。

これらの領域は左側ペインのフォルダ状の項目として表示され、そこからアクセスします。

- Run Design Rule Check - このボタンをクリックすると、バッチチェック用に有効化されたルールと、このチェック種別に対して定義された追加オプションに従って、バッチ DRC を実行します。

レポート オプション

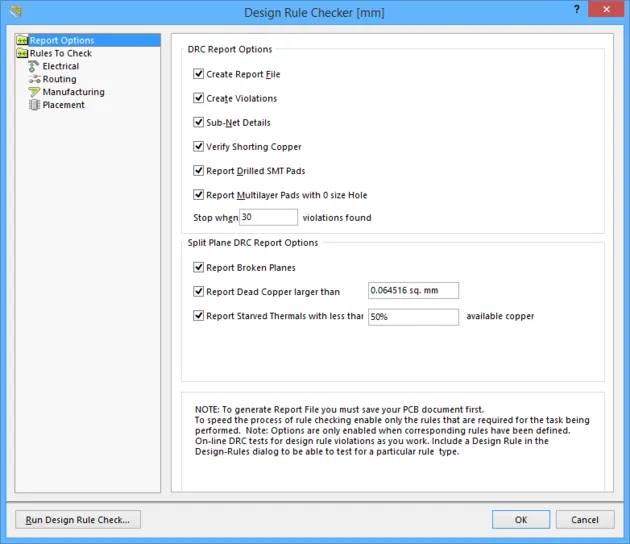

Report Options フォルダをクリックすると、バッチ DRC 実行時に利用できる追加オプションがダイアログ右側に読み込まれます。

DRC レポート オプション

- Create Report File - このオプションを有効にすると、基板のバッチ DRC 実行後にレポートを生成します。

- Create Violations - このオプションを有効にすると、定義済みの違反表示設定に従って、ワークスペース上で違反がハイライト表示されます。また、このオプションは、違反を Violations パネルの PCB Rules And Violations領域に一覧表示するためにも必要です。

- Sub-Net Details - Un-Routed Net ルールが定義されている場合、このオプションを有効にすると、DRC レポートにサブネットの詳細を含めます。

- Verify Shorting Copper - このオプションを有効にすると、設計で使用されている Net Tie コンポーネント内の短絡銅の整合性を検証します。このチェックでは、コンポーネント内の未接続銅(パッドが他のパッドを正しく短絡していないことを示唆)を検出します。

- Report Drilled SMT Pads - このオプションを有効にすると、誤ってドリル加工された SMT(Surface Mount Technology)パッドを DRC レポートに含めます。

- Report Multilayer Pads with 0 size Hole - このオプションを有効にすると、設計内で見つかった無効な多層パッドを DRC レポートに含めます。無効な多層パッドとは穴径が 0 のもので、本来であれば SMT パッドとなるものです。

- Stop when n violations found - このフィールドで、バッチ DRC プロセスを停止するまでに検出できる違反の最大数を指定します(デフォルト = 500)。報告する違反数を制限することは、チェックプロセスを管理しやすくするための重要な戦略です。

スプリットプレーン DRC レポート オプション

- Report Broken Planes - このオプションを有効にすると、バッチ ルールチェックで断線したプレーン(broken planes)を検出してレポートします。断線プレーンは、ネットへの接続性を持つプレーン領域が、プレーンの他の部分から電気的に切り離されたときに発生します。例として、スプリットプレーン上にコネクタが配置されているが接続されていない場合があります。ピン周囲のボイドが連結してプレーン銅を完全に横断し、結果としてプレーンが 2 つに分断されます。

- Report Dead Copper larger than - このオプションを有効にすると、指定面積より大きいデッドカッパー領域を検出してレポートします。デッドカッパーとは、ネットへの接続性がなく、元の親プレーンからも電気的に切り離された銅の領域を指します。例として、(プレーンに接続されていない)コネクタでピン間隔が狭い場合、ピン周囲のボイドが連結して、プレーン銅の一部領域がプレーンの他の部分から孤立することがあります。関連フィールドで、デッドカッパーの最小許容面積を指定します。これを超えるとルール違反と見なされます(デフォルト = 100 sq. mils)。

- Report Starved Thermals with less than n% available copper - このオプションを有効にすると、指定した割合を超えるスターブ(starved)状態のサーマル接続を検出してレポートします。サーマルは、プレーン銅への熱伝導を低減するため、周囲にサーマルリリーフの「切り欠き」を持つプレーンへの接続です。サーマルは、プレーンに接続する銅スポークの表面積がボイド領域によって減少すると、スターブ状態になることがあります。このオプションでは、スポークだけでなくサーマル自体の表面積についても、サーマルに侵入するボイド領域に対してチェックします。関連フィールドで、残存すべき接続銅の最小許容割合を指定します。これを下回るとルール違反と見なされます(デフォルト = 50%)。

チェックするルール

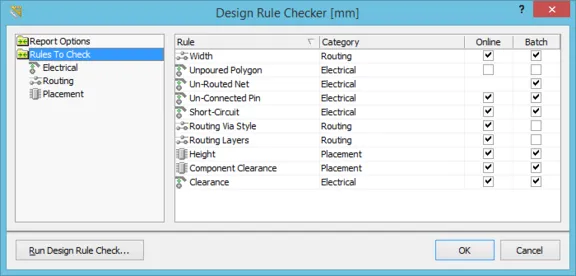

Design Rule Checker ダイアログには、チェック可能なすべてのルールが一覧表示されます。

Design Rule Checker ダイアログには、チェック可能なすべてのルールが一覧表示されます。

Rules To Check フォルダをクリックすると、チェック可能なルール種別の一覧がダイアログ右側に読み込まれます。あるいは、(フォルダの下にある)特定のカテゴリをクリックすると、そのカテゴリに関連付けられたデザインルール種別のみが一覧表示されます。

各ルール種別について、次の情報が表示されます。

- Rule - ルールの種別。

- Category - ルール種別が関連付けられている親カテゴリ。

- Online - オンライン DRC(利用可能な場合)におけるこのルール種別の現在の状態。クリックで切り替え。

- Batch - バッチ DRC におけるこのルール種別の現在の状態。クリックで切り替え。

必要に応じて、各ルール種別をオンラインおよび/またはバッチチェック用に有効化してください。

注記

- 生成されるデザインルール検証レポートには、Design Rule Checker ダイアログで指定されたとおり、バッチチェック処理中にテストされた各ルールが一覧表示されます。検出された各違反は、レイヤ、ネット名、コンポーネント デジグネータ、パッド番号などの参照情報、およびオブジェクトの位置を含む完全な詳細とともに一覧表示されます。違反オブジェクトの項目をクリックすると、ワークスペース上の該当オブジェクトへ直接クロスプローブできます。

-

ワークスペースでのルール違反表示にさらなる柔軟性を持たせるため、2 種類の違反表示(違反詳細(カスタム違反グラフィック)と違反オーバーレイ)には、それぞれ別のシステムカラーが関連付けられています。これにより、設計者は異なる明確な色で両者を区別できます。色の割り当ては、View Configurations ダイアログの Board Layers And Colors タブで行います。

- Violation Details – DRC Detail Markers システムカラーに割り当てられた色を使用します。

- Violation Overlay – DRC Error Markers システムカラーに割り当てられた色を使用します。

- バッチ DRC 実行後、Messages パネル内の違反メッセージをダブルクリックすると、ワークスペース上でその違反の原因となっているオブジェクトへクロスプローブします。

- オンラインまたはバッチ DRC の実行時、ルール違反は PCB Rules And Violations パネルの Violations 領域に一覧表示されます。

- 特定の設計オブジェクトに関連する違反は、PCB ワークスペース内で直接調査できます。カーソルを違反オブジェクト上に置き、右クリックして Violations サブメニューからコマンドを選択します。オブジェクトが関与している個別の違反を調査するか、Show All Violations コマンドを使用して関与しているすべての違反を表示するかを選べます。いずれの場合も Violation Details ダイアログが表示され、詳細な違反情報と、違反オブジェクトのハイライトおよびジャンプのためのコントロールが提供されます。

AI で翻訳

AI で翻訳