Печатная электроника

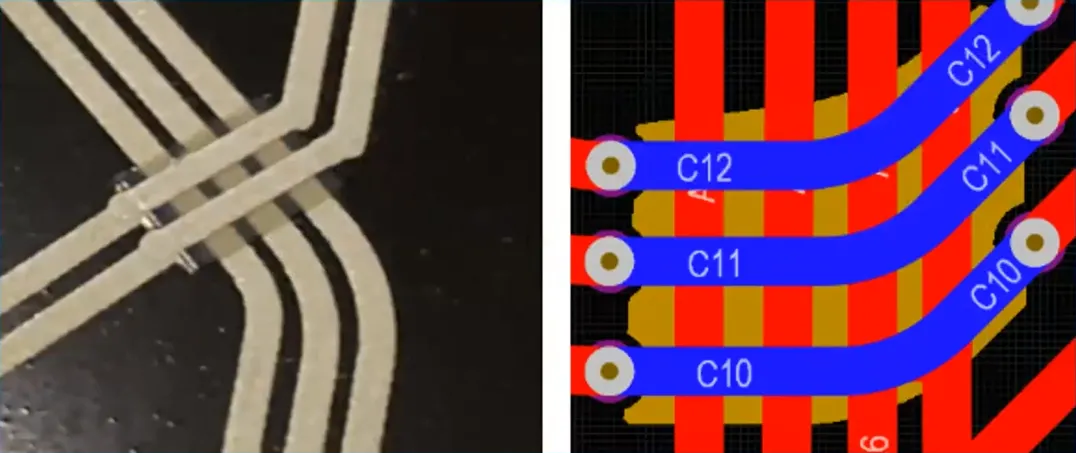

Захватывающей эволюцией в проектировании и разработке электронных изделий стала возможность печатать электронную схему непосредственно на подложке — например, на пластиковой отливке, которая становится частью изделия.

|

|

Эти слайды показывают 2D- и 3D-виды примера топологии печатной электроники. (Изображение предоставлено «csi entwicklungstechnik» из их проекта с использованием TactoTek® In-Mold Structural Electronics).

|

Эта ориентированная на поверхность техника реализации называется Printed Electronics. Хотя термин Printed Electronics не является точным описанием технологии, поскольку печать — не единственный применяемый метод её создания, этот термин широко принят в отрасли и будет использоваться на этой странице.

Существует ряд разрабатываемых подходов к созданию печатной электроники, включая: 3D-печать проводящими чернилами; штамповочные технологии, позволяющие формировать проводники, а также простые элементы схемы, такие как транзисторы; и методы лазерного осаждения, которые могут наращивать проводящие дорожки в очень малых масштабах с ультравысокой точностью.

Печатная электроника станет ключевой технологией, позволяющей интегрировать электронику в новые рынки. Печатная электроника обеспечивает тесную связь между схемой и изделием. От гибкого датчика, который крепится непосредственно к телу, до многодатчиковой отливки в форме кончика пальца, позволяющей роботизированной руке удерживать мягкий пластиковый стакан, пока в него наливают жидкость, — печатная электроника позволит разрабатывать инновационные решения во многих сегментах рынка.

Технология

С точки зрения what, что обеспечивает технология, правила игры остаются прежними: электронные компоненты соединяются между собой проводящими дорожками, образуя электронную схему, выполняющую полезную функцию. Отличается подход к построению схемы.

Ориентированная на слои технология изготовления, используемая для традиционной печатной платы, — это reductive process. Каждый проводящий слой начинается как сплошной лист проводящего материала, например меди, который затем вытравливается, оставляя только медь, формирующую требуемые проводящие дорожки. Это также многостадийный процесс: отдельные проводящие слои «сэндвичем» собираются вместе с чередующимися слоями изоляции, а также применяются различные операции сверления и последующего металлирования.

Печатная электроника — это additive process: сигнальные дорожки печатаются непосредственно на подложке. Если последующей дорожке нужно пересечь существующую, небольшой участок изоляции печатается прямо в нужном месте. Работая как крошечный мостик, он позволяет напечатать новую дорожку поверх существующей, не соединяясь с ней. Например, если в проекте используется технология DuPont InMold, сначала схема печатается на плоской пластиковой подложке, которую затем термоформуют и литьём под давлением превращают в изделие окончательной формы.

При использовании печатной электроники больше не требуется привычная жёсткая подложка печатной платы из стеклотекстолита. Вместо этого схема формируется непосредственно как часть изделия, а проводники в итоге повторяют форму и контуры поверхности изделия. Поскольку используется меньше материала и образуется меньше отходов, печатная электроника в конечном счёте во многих случаях станет более экономически эффективным подходом, чем традиционная печатная плата.

NOTE — на данном этапе функциональность проектирования печатной электроники в Altium Designer поддерживает только плоские поверхности подложки. Для полностью 3D-проектирования схем в Altium Designer уже доступен специализированный инструмент проектирования 3D-MID.

См. страницу возможностей True 3D-MID Design для обзора функциональности.

См. страницу документации 3D-MID Design, чтобы узнать больше.

Проектирование печатной электроники в Altium Designer

Помимо подложки, на которой печатается проект, в изделии печатной электроники нет физических слоёв — проводящие дорожки печатаются непосредственно на подложке. Там, где по проекту дорожки должны пересекаться, в этом месте печатается небольшой участок диэлектрического материала, с достаточным расширением за пределы зоны пересечения, чтобы обеспечить требуемый уровень изоляции между различными сигналами.

Выходные данные, необходимые для управления процессом печати, формируются с использованием стандартного формата, например Gerber.

Выходные данные будут включать файл для:

-

Каждого прохода печати проводящего слоя — по сути, аналог слоя трассировки меди в традиционной печатной плате

-

Каждого прохода печати диэлектрика — поскольку диэлектрические участки печатаются, их формы также задаются в выходном файле, например в Gerber-файле.

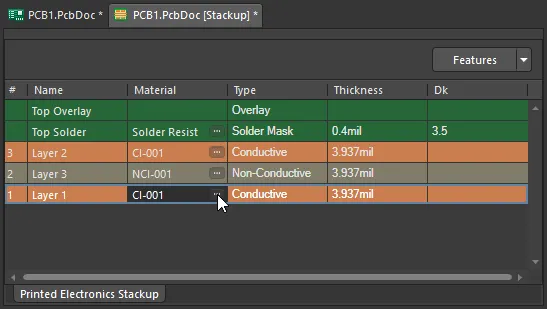

Определение стека слоёв

Итак, как эти множественные проходы печати задаются в редакторе PCB? В печатной электронике для каждого прохода печати требуется выходной файл, поэтому вместо представления в виде набора медных слоёв, разделённых диэлектрическими слоями, рассматривайте это как набор проходов печати, где каждый проход — либо проводящий слой чернил, либо непроводящий слой чернил.

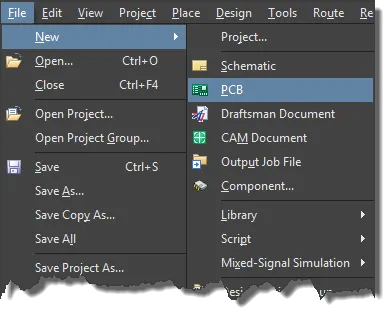

Чтобы создать проект печатной электроники, сначала создайте новую плату PCB через File » New » PCB в главном меню.

Настройка новой платы как проекта печатной электроники выполняется в Layer Stack Manager. Выберите Design » Layer Stack Manager в главном меню, чтобы открыть Layer Stack Manager. Затем используйте раскрывающийся список  и выберите Printed Electronics или выберите Tools » Features » Printed Electronics в главном меню.

и выберите Printed Electronics или выберите Tools » Features » Printed Electronics в главном меню.

Новая плата по умолчанию содержит два медных слоя, разделённых диэлектрическим слоем.

Новая плата по умолчанию содержит два медных слоя, разделённых диэлектрическим слоем.

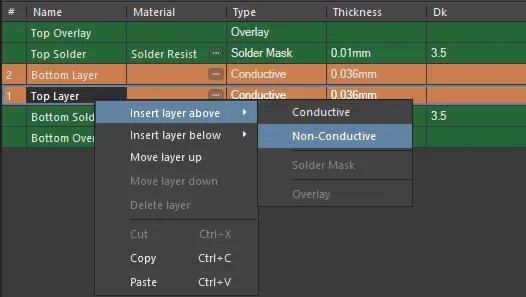

Когда включена функция Printed Electronics , диэлектрический слой между двумя медными слоями исчезает. Почему? Потому что для печатной электроники требуется выходной файл для каждого слоя, поэтому диэлектрические слои не используются, так как они не применяются для формирования выходных файлов.

Когда включена функция Printed Electronics, диэлектрический слой удаляется.

Вместо него добавляются непроводящие слои. Диэлектрические фигуры, называемые патчами, можно вручную или автоматически определять на этих слоях везде, где на проводящих слоях сигнальные дорожки должны пересекаться.

Non-Conductive слои можно вставлять между слоями Conductive , и на них определять диэлектрические патчи.

Щёлкните правой кнопкой мыши по слою, чтобы вставить слой выше или ниже, переместить слой вверх или вниз либо удалить слой. В печатной электронике не используются Bottom Solder и Bottom Overlay; они были удалены.

После добавления слоёв задайте свойства материала для каждого слоя.

Используйте кнопку с многоточием, чтобы выбрать материал для каждого печатного слоя.

Используйте кнопку с многоточием, чтобы выбрать материал для каждого печатного слоя.

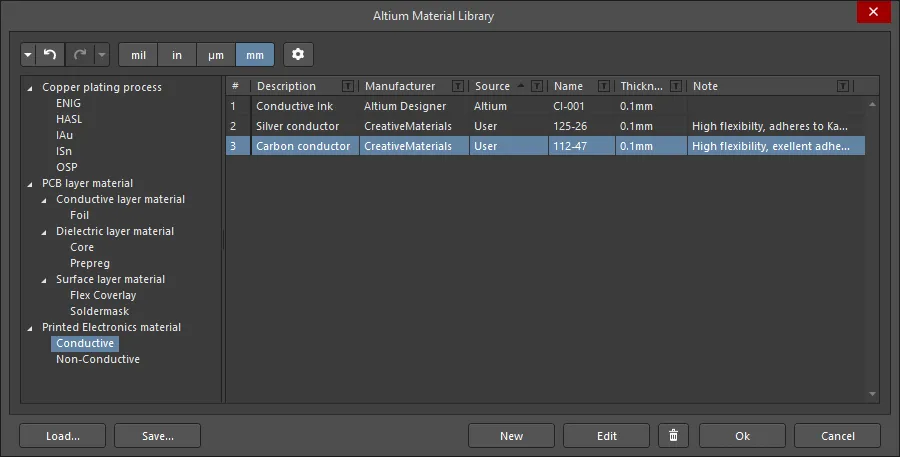

Выбор материала

Материалы, используемые как в традиционном проектировании печатных плат, так и в проектировании печатной электроники, выбираются в библиотеке материалов Layer Stack Manager.

Когда Layer Stack Manager открыт, используйте команду Tools » Material Library, чтобы открыть диалог Altium Material Library.

-

Диалог Altium Material Library содержит материалы как для проводящих, так и для непроводящих слоёв.

-

В библиотеке можно определить новые материалы — нажмите кнопку New в нижней части диалога. Если создаются пользовательские материалы, их можно сохранять в пользовательскую библиотеку материалов и загружать из неё.

-

Чтобы выбрать материал для конкретного слоя, нажмите элемент управления с многоточием (

) в ячейке Material для этого слоя в Layer Stack Manager. Откроется диалог Select Material, в котором будут показаны только материалы, подходящие для данного типа слоя. Выберите нужный материал и нажмите OK.

) в ячейке Material для этого слоя в Layer Stack Manager. Откроется диалог Select Material, в котором будут показаны только материалы, подходящие для данного типа слоя. Выберите нужный материал и нажмите OK.

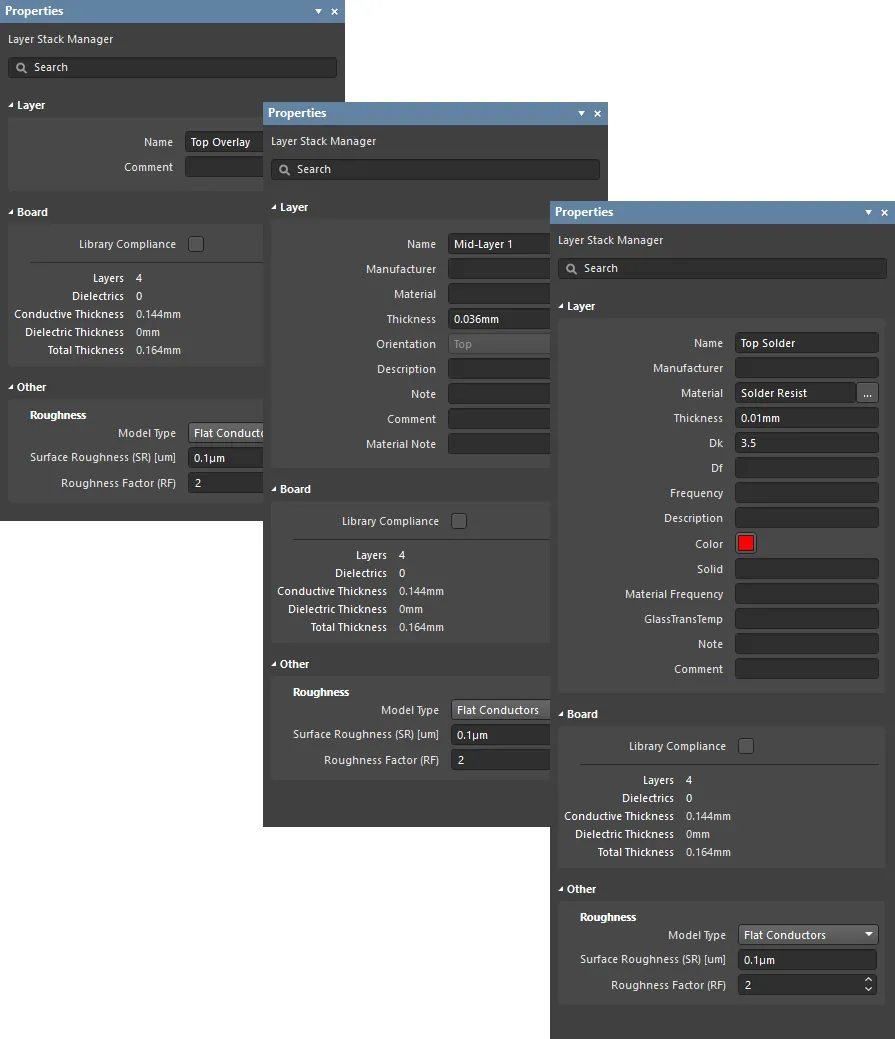

Панель Properties

Когда активна вкладка Printed Electronics Stackup документа Layer Stack, панель Properties позволяет редактировать и настраивать свойства слоёв стека для печатного проекта.

-

Layer

-

Name – имя слоя.

-

Manufacturer – производитель слоя.

-

Material – материал слоя. Он может быть заранее определён в диалоге Altium Material Library dialog (Tools » Material Library) в поле Constructions либо задан пользователем в Layer Stack. Нажмите

, чтобы открыть диалог Select Material dialog и выбрать нужный материал для текущего выбранного слоя в стеке слоёв.

, чтобы открыть диалог Select Material dialog и выбрать нужный материал для текущего выбранного слоя в стеке слоёв.

-

Thickness – толщина сигнального слоя.

-

Dk – это диэлектрическая проницаемость (также обозначается как εr в электромагнетизме). Она показывает относительную диэлектрическую проницаемость изоляционного материала, то есть его способность накапливать электрическую энергию в электрическом поле. Для целей изоляции лучше материал с меньшей диэлектрической проницаемостью, а в ВЧ-приложениях может быть желательна более высокая диэлектрическая проницаемость. Кроме того, чем ниже относительная диэлектрическая проницаемость, тем ближе характеристики материала к характеристикам воздуха. Это свойство критично для согласования требований по импедансу некоторых линий передачи.

-

Df – это коэффициент потерь (Dissipation Factor). Он характеризует эффективность изоляционного материала, показывая скорость потерь энергии для определённого режима колебаний, например механических, электрических или электромеханических. Иными словами, это свойство материала, описывающее, какая часть передаваемой энергии поглощается материалом. Чем больше тангенс угла потерь, тем больше энергии поглощается материалом. Это свойство напрямую влияет на затухание сигнала на высоких скоростях.

-

Frequency – это частота, на которой тестируется материал, и значение, которому соответствуют Dk / Df для определённой частоты. Частота также берётся из справочных данных по материалу.

-

Description – введите осмысленное описание.

-

Color – требуемый цвет паяльной маски. Нажмите, чтобы открыть раскрывающийся список и задать/изменить цвет.

-

Solid – Н/Д

-

Material Frequency – Н/Д

-

GlassTransTemp – это температура стеклования (также известная как TG) — температура, при которой смола переходит из стеклообразного состояния в аморфное, изменяя своё механическое поведение, например коэффициент расширения.

-

Note – введите любые относящиеся к делу примечания для слоя.

-

Comment– введите любые необходимые комментарии для слоя.

-

Board

-

Library Compliance – если включено, для каждого слоя, выбранного из Библиотеки материалов, текущие свойства слоя проверяются на соответствие значениям определения этого материала в библиотеке.

-

Layers – количество проводящих слоёв.

-

Dielectrics – количество диэлектриков.

-

Conductive Thickness – сумма толщин всех сигнальных слоёв и слоёв полигонов (всех медных или проводящих слоёв).

-

Dielectric Thickness – толщина диэлектрического(их) слоя(ёв).

-

Total Thickness – общая толщина готовой платы.

-

Other

Roughness – показывает шероховатость проводящих слоёв.

-

Model Type – предпочтительная модель для расчёта влияния шероховатости поверхности (дополнительные сведения о различных моделях см. в статьях ниже). Применяется ко всем медным слоям в стеке.

-

Surface Roughness – значение шероховатости поверхности (можно получить у вашего производителя). Введите значение в диапазоне от 0 до 10 мкм, значение по умолчанию — 0,1 мкм

-

Roughness Factor – характеризует ожидаемое максимальное увеличение потерь в проводнике из‑за эффекта шероховатости. Введите значение в диапазоне от 1 до 100, значение по умолчанию — 2.

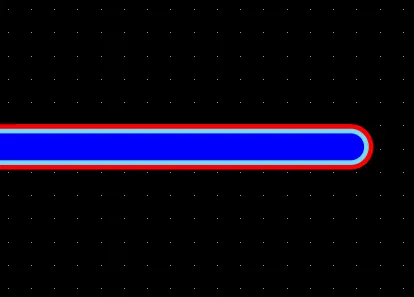

Трассировка цепей

-

Цепи в проекте печатной электроники трассируются так же, как и в традиционной печатной плате, с помощью команды Interactive Routing.

-

Переходы между проводящими слоями выполняются с помощью клавиш + и - на цифровой клавиатуре или сочетания клавиш Ctrl+Shift+Wheelroll.

-

При смене слоя во время трассировки добавляется переходное отверстие (via), а его свойства определяются применимым правилом проектирования Routing Via Style.

Нужны ли переходные отверстия?

Программе необходимо разместить via, чтобы сохранять связность цепи во время трассировки, а также управлять связностью при изменении трассировки путём проталкивания или перетаскивания. Для межслойной связности via не требуются — программа предполагает, что перекрывающиеся дорожки на разных слоях соединены.

Диаметр via можно задать таким же, как ширина трассировки.

Увеличение толщины трассы

При необходимости толщину трассы можно нарастить, например, чтобы реализовать структуру вроде печатной антенны. Это достигается размещением нескольких трасс друг над другом на разных проводящих слоях.

Добавление диэлектрических фигур

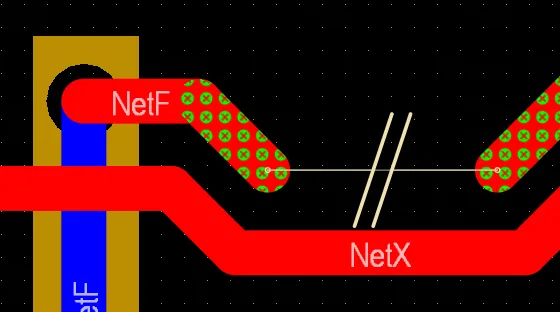

После трассировки цепей следующий шаг — создать диэлектрические «заплатки», необходимые для разделения пересечений разных цепей. Диэлектрические фигуры задаются на непроводящих слоях. Их можно определить вручную или автоматически создать с помощью Dielectric Shapes Generator.

Ручные фигуры можно создавать из дуг, линий, заливок или сплошных областей (Solid Regions). Объекты Solid Region обеспечивают наибольшую гибкость, поскольку их границы можно настраивать, формируя практически любую форму.

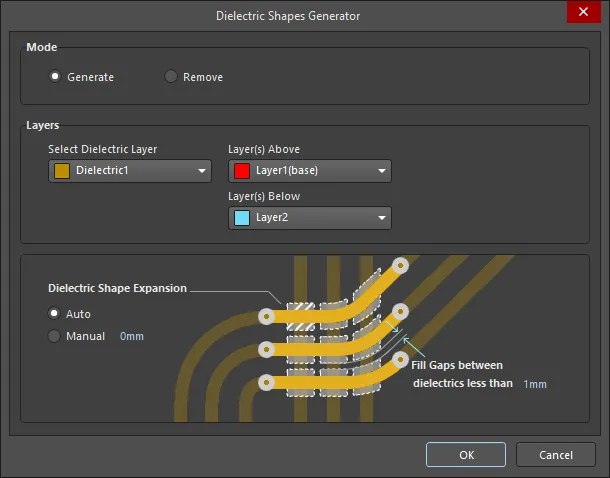

Генератор диэлектрических фигур

В ПО также предусмотрен автоматический Dielectric Shapes Generator. Идея заключается в том, чтобы сначала выполнить трассировку на проводящих слоях, при необходимости размещая via для переключения между слоями.

Чтобы получить доступ к Генератору диэлектрических фигур в Altium Designer, необходимо установить расширение ПО Printed Electronics Crossover Generator. Это расширение можно установить или удалить вручную.

Дополнительные сведения об управлении расширениями см. на странице Extending Your Installation (Altium Designer Develop, Altium Designer Agile, Altium Designer).

Когда трассировка завершена, выполните команду Tools » Printed Electronics » Generate Dielectric Patterns, чтобы открыть диалог Dielectric Shapes Generator. При запуске Генератора диэлектрических фигур он удалит все фигуры на целевом(ых) слое(ях), а затем создаст их заново. Если фигуры были определены вручную, заблокируйте их перед запуском Dielectric Shapes Generator.

Options and Controls of the Dielectric Shapes Generator Dialog

-

Mode - выберите нужный режим:

-

Generate - выберите, чтобы сгенерировать новые диэлектрические заплатки для всех включённых слоёв, указанных в области Layers .

-

Remove - выберите, чтобы удалить любые существующие фигуры, которые генератор обнаружит на слоях, указанных в области Layers , прежде чем он добавит свои.

-

Layers - генератор определит все пересечения и добавит диэлектрические заплатки в соответствии с настройками в этой области диалога.

-

Select Dielectric Layer - используйте выпадающий список, чтобы выбрать диэлектрический слой. Если выбран All , генератор ищет пересечения на любой паре проводящих слоёв и размещает заплатку на диэлектрическом слое, который находится между этими двумя проводящими слоями. Если диэлектрический слой не выбран, диэлектрические фигуры будут созданы для всех пересечений между всеми слоями на соответствующих диэлектрических слоях. Используйте Layer(s) Above и Layer(s) Below , чтобы выбрать, между какими двумя проводящими слоями генератор должен выполнять поиск пересечений. Если он обнаружит объект на Layer(s) Above, который пересекается с объектом на Layer(s) Below, он сгенерирует заплатку для размещения между ними и разместит её на слое, указанном в области Select Dielectric Layer . Параметры Layer(s) Above и Layer(s) Below недоступны, если в области Mode выбран Remove .

-

Dielectric Shape Expansion

-

Auto - в этом режиме диэлектрическая фигура автоматически расширяется, чтобы удовлетворить требование применимого правила проектирования Clearance Constraint.

-

Manual - в этом режиме генератор строит фигуру, повторяющую форму, образованную пересекающимися объектами, затем расширяет её на введённое расстояние. Например, при использовании этого режима, если есть две дорожки на разных слоях, которые расположены слишком близко и вызывают нарушение зазора, заплатка размещена не будет.

-

Fill Gaps between dielectrics less than <xx> - задайте величину, если вы хотите заполнять зазоры между диэлектриками, которые меньше указанного вами значения. Это можно использовать для объединения соседних диэлектрических заплаток в более крупные.

Связность цепей и проверки правил проектирования

Online DRC не поддерживается, когда стек слоёв настроен как Printed Electronics, из‑за иной логики определения условий нарушений; например, пересечение цепей на разных слоях помечается как короткое замыкание. После завершения трассировки и определения изоляционных заплаток нажмите кнопку Run Design Rule Check в диалоге Design Rule Checker (Tools » Design Rule Check), чтобы выполнить пакетную DRC.

Примечания о связности цепей и проверках правил проектирования:

-

Когда цепи нужно перейти на другой проводящий слой, вставьте via. Это гарантирует корректную обработку сегментов дорожек при перетаскивании или проталкивании трассировки.

-

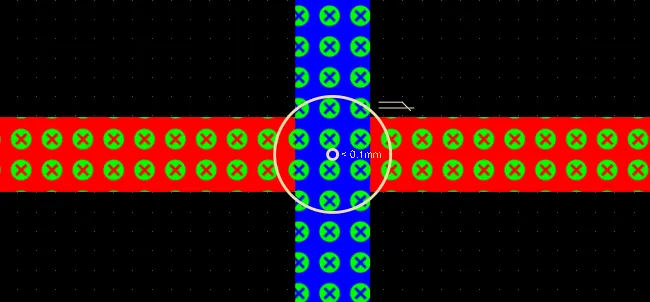

Соприкасающиеся/пересекающиеся дорожки на разных слоях считаются соединёнными. Если они относятся к одной и той же цепи, это не помечается как разрыв цепи; если к разным цепям — помечается как короткое замыкание.

-

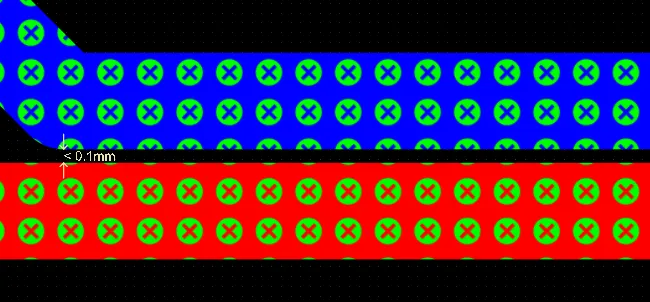

Для изоляции соприкасающихся/пересекающихся дорожек требуется диэлектрическая фигура; она размещается на непроводящем слое. Диэлектрическую фигуру можно разместить вручную или с помощью Dielectric Shape Generator. Диэлектрическая фигура должна выходить за края пересекающихся дорожек на достаточную величину, чтобы удовлетворить применимому правилу проектирования зазора (clearance constraint).

-

Для проекта печатной электроники проверки правил проектирования на короткие замыкания, нарушения зазоров и нетрассированные цепи работают так, как описано ниже.

Правило проектирования «Короткое замыкание»

В проекте Printed Electronics, когда разные цепи пересекаются на разных слоях, это помечается как короткое замыкание. Такие пересечения изолируются размещением диэлектрической заплатки на непроводящем слое.

Правило проектирования «Зазор»

Зазоры «цепь‑цепь» проверяются на всех слоях, а не только в пределах одного слоя.

Нетрассированная цепь

Переходы между слоями не требуют via — анализатор цепей распознает, что цепь не разорвана.