QuickNav - 回路図設計オブジェクト

このページでは、回路図ドキュメント(および該当する場合は回路図ライブラリドキュメント)で使用できる設計オブジェクトについて、各オブジェクトの詳細情報へすばやく移動できるように、クイックリファレンス情報を提供します。

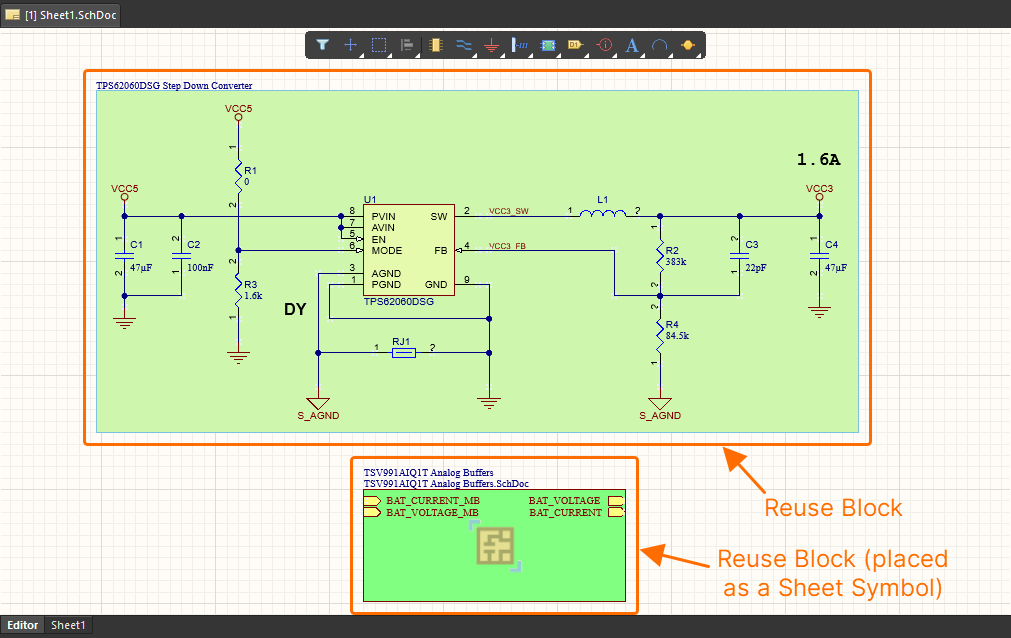

グラフィカル概要

以下の画像は、一般的によく使用される回路図設計オブジェクトをまとめて視覚的に示したものです。

回路図ドキュメント(および該当する場合は回路図ライブラリドキュメント)で一般的に使用される設計オブジェクト。

注記

-

利用可能な場合は、回路図ドキュメント上に再利用ブロックまたはスニペットを配置することもできます。詳細については、Working with Reuse Blocks および Working with Snippets を参照してください。

-

回路図エディタのメインPlace メニューから、device sheet シンボルを配置することもできます。これは配置後、実質的にはシートシンボルオブジェクトとして機能します。接続された Workspace から managed schematic sheet を配置する場合も同様です。いずれの場合も、シンボルは色分けが異なり、再利用可能なエンティティを参照していることを示すグラフィックが含まれます。

-

ピンおよび IEEE シンボルオブジェクトは、回路図ライブラリエディタ専用です。

主要オブジェクトのスライドショー

以下のスライドでは、実際の回路内でさまざまな設計オブジェクトがどのように使われているかを確認できます。各オブジェクトの概要説明に加え、より詳細な情報へのリンクも用意されています。なお、ここでは主に、論理設計をキャプチャする際に繰り返し使用する電気オブジェクトおよびディレクティブオブジェクトに焦点を当てています。

バスバスは、複数の配線接続を表すポリラインオブジェクトです。バスは、たとえばアドレスバスやデータバスのように、連続した一連のネットを束ねるために使用されます。基本要件として、バス内の各ネットには共通のベース名に続けて数値識別子を付けて命名する必要があります。上の例では、6 本の個別ネット(MB_ESC_M1 - MB_ESC_M6)が、バス MB_ESC_M[1..6] に束ねられた状態でシートに入っています。詳細はこちら... バスエントリバスエントリは、ワイヤをバスラインに接続するために使用される電気設計プリミティブです。これにより、異なる 2 つのネットをバス上の同じポイントに接続できます。これをワイヤで行うと、2 つのネットは短絡してしまいます。上の例では、入力バス(MB_ESC_M[1..6])がバスエントリを使用して構成ネットに分割されています。詳細はこちら... パートライブラリ内のパート(またはコンポーネント)は、実際のプリント基板上に配置される物理デバイスを表します。回路図シート上では、コンポーネントはその回路図シンボルモデルで表現されます。各コンポーネントには 1 つ以上のパートを含めることができます。パートには、コンポーネントの記号表現に加えて、PCB フットプリントなどのモデルへのリンクや、コンポーネントパラメータやサプライヤ情報などの詳細を記録するためのパラメータも含まれます。モデルリンクやパラメータをパートに追加する方法は、使用しているライブラリ保存形式の種類によって異なります。詳細はこちら... パート Designator と CommentDesignator フィールドは、回路図コンポーネント(パート)の子パラメータオブジェクトです。これは、配置された各パートを一意に識別し、プロジェクトの回路図ソースドキュメント全体に配置された他のすべてのパートと区別するために使用されます。詳細はこちら... Comment フィールド(これも回路図コンポーネント(パート)の子パラメータオブジェクト)は、コンポーネントに関する追加情報(部品番号や値など)を表示するために使用されます。詳細はこちら... 電源ポート電源ポートは、設計構造に関係なく、回路図プロジェクト全体にある同名の他のすべての電源ポートとの接続性を作成します。ネット名は電源ポートによって自動的に付けられます。必要に応じて、このネットを特定の回路図シートに限定することもできます。詳細はこちら... ワイヤワイヤは、回路図上の点と点の間に電気的接続を形成するために使用されるポリライン電気設計プリミティブです。ワイヤは物理的な配線に相当します。詳細はこちら... ネットラベルネットラベルは、同じ回路図シート上で同名の他のネットラベルとの接続性を作成するために使用されるネット識別子です。ネット名はネットラベルによって自動的に付けられます。ネットラベルは、コンポーネントピン、ワイヤ、およびバス上に配置できます。なお、プロジェクトオプションが Net Identifier Scope の Global を使用するよう設定されていない限り、ネットラベルはシート間では接続されません。詳細はこちら... ポートポートは、ある回路図シートから別の回路図シートへネットを接続するために使用されます。接続は、垂直方向(階層設計)または水平方向(フラット設計)にできます。Project Options ダイアログの Options タブで Allow Ports to Name Nets オプションが有効になっている場合、ポート名はネット名として使用されます。この場合、ポートは同じ回路図シート内でも接続されます。詳細はこちら... オフシートコネクタオフシートコネクタは、ある回路図シートから別のシートへネットを接続するために使用されます(同一シート内では使用しません)。サポートするのは水平方向の接続(フラット設計)のみで、ポートと比較すると機能は限定的です。詳細はこちら... シートシンボルシートシンボルは、複数シートから成る階層設計においてサブシートを表すために使用されます。階層設計とは、設計内の構造、つまりシート間の関係が表現される設計のことです。階層設計の利点は、設計の構造を示せること、そして接続性が常に子シートから親シート上のシートシンボルへ向かうため、完全に予測可能で容易に追跡できることです。さらに、階層設計には高度な設計再利用システムを実現する基盤を提供するという利点もあります。このシステムは、Workspace ベースかファイルベースかに応じて、managed schematic sheets または device sheets を通じて提供されます。いずれの場合も、配置されるシンボルは色分けが異なり、再利用可能なエンティティを参照していることを示すグラフィックが含まれますが、機能と動作は基本的に標準のシートシンボルと同じです。詳細はこちら... シートエントリシートエントリはシートシンボル内に配置され、そのシンボルが表す元の回路図サブシート上の同名ポートとの接続性を作成します。Project Options ダイアログの Options タブで Allow Sheet Entries to Name Nets オプションが有効になっている場合、シートエントリはネット名として使用されます。詳細はこちら... シートシンボル Designatorシートシンボル Designator は親シートシンボルの子オブジェクトであり、同じ回路図シート上に配置された他のシートシンボルと区別できるよう、シンボルに意味のある名前を付けるために使用されます。通常、この名前はそのシンボルが表す回路図サブシート全体の機能を反映したものになります。シートシンボルのインスタンス化を使用すると、同じサブシート上の複数チャネルを 1 つのシートシンボルから参照できます。使用される構文では、シートシンボルの Designator フィールド内で Repeat キーワードを使用します。詳細はこちら... シートシンボル ファイル名シートシンボルのファイル名は親シートシンボルの子オブジェクトであり、シートシンボルと、そのシンボルが表す回路図サブシートとの間のリンクを提供します。複数のサブシートを 1 つのシートシンボルから参照することもでき、その場合は File Name フィールド内で各ファイル名をセミコロンで区切ります。詳細はこちら... 再利用ブロック再利用ブロックを使用すると、設計回路の一部を保存し、異なるプロジェクト間で再利用できます。これには回路図回路と、その PCB 用の物理表現の両方を含めることができます。このような再利用ブロックを回路図シート上に配置すると、その物理表現は ECO プロセス中に PCB ドキュメントへ自動的に配置されます。再利用ブロックは、正式に管理される Workspace エンティティです。これらのブロックは読み取り専用で、ライフサイクル/リビジョン管理され(ブロックは更新可能)、トレーサブルです(where-used サポート)。 再利用ブロックは、回路図シート上に直接配置することも、回路図シート上のシートシンボルとして配置することもできます。後者の場合、配置されたシートシンボルには、再利用ブロック内のポートに対応するシートエントリが含まれます。再利用ブロックの内容は、シートシンボルから参照される自動作成された子回路図シート上に配置されます。配置された再利用ブロックのシートシンボルには、識別用の独自アイコンが表示されます。 詳細はこちら... シグナルハーネスシグナルハーネスは、バス、ワイヤ、その他のシグナルハーネスを含む異なる信号を論理的にグループ化するための抽象接続であり、柔軟性の向上と設計の簡素化を実現します。シグナルハーネスにより、PCB プロジェクト内のサブ回路間で、より高レベルな抽象接続を作成および操作できます。これにより、同じ回路図設計空間内でより複雑な設計が可能になり、設計の可読性が向上するとともに、再利用の可能性も高まります。詳細はこちら... ハーネスコネクタハーネスコネクタは、本質的にはさまざまな信号をまとめて、バス、ワイヤ、その他の信号ハーネスを含むシグナルハーネスを形成するためのコンテナです。ハーネスコネクタは、含まれるハーネスエントリを介してこのハーネスに接続されるすべての信号を集約する漏斗のようなものと考えてください。 Learn more... Harness Entryハーネスエントリはハーネスコネクタ内に配置され、ワイヤ、バス、その他の信号ハーネスを介した信号を結合して、より上位レベルのシグナルハーネスを形成する接続ポイントです。 Learn more... Harness Type親ハーネスコネクタの子オブジェクトであるハーネスタイプは、配置されたハーネスコネクタの種類、またはその内部で定義されたハーネスエントリのセットに名前を付けるために使用されます。ハーネスタイプとそれに関連付けられたハーネスエントリは、本質的にはネットそのものの名前ではなく、ネットを運ぶコンテナの名前です。 Learn more... Pinピンは、コンポーネント上の物理ピンを表すために Schematic Library エディタに配置されます。ピンの一端のみが電気的にアクティブであり、これはピンのホットエンドと呼ばれることがあります。 Learn more... Probeプローブは、シミュレーション可能な回路の特定の位置で測定を行うために使用されます。プローブを使用すると、該当箇所の電圧、電流、または電力、さらには電圧差分(2 つのプローブを順に配置して使用)まで調べることができます。また、プローブのインタラクティブモードを有効にすると、シミュレーション結果を含む No ERC DirectiveNo ERC デザインディレクティブは、回路内のノードに配置して、回路図プロジェクトの検証時に検出される Electrical Rule Check の警告および/またはエラー違反条件の報告をすべて抑制します。no ERC は、回路の他の部分に対して包括的なチェックを実行しつつ、警告が発生することが分かっている回路上の特定箇所(未接続ピンなど)で意図的にエラーチェックを制限するために使用します。 Learn more... Differential Pair Directive差動ペアディレクティブ(定義済みパラメータセットディレクティブ)は、回路図上で差動ペアオブジェクトを定義できるようにします。このタイプのディレクティブを、対象となるペアの正側ネットと負側ネットの両方に接続するか、または Blanket オブジェクトでペアを囲んで、1 つのディレクティブで複数のネットを対象にします。ネット自体には、_P および _N のサフィックスを付けて命名する必要があります。カスタム差動ペアサフィックスは、Project Options ダイアログのOptions タブにある Diff Pairs セクションで定義できます。

このタイプのディレクティブの各ペア(正側ネット用 1 つ、負側ネット用 1 つ)は、同期プロセス中に PCB へ転送される際、差動ペアオブジェクトを生成します。これらの差動ペアオブジェクトはそれぞれ、デフォルトの差動ペアクラス All Differential Pairs に追加されます。 生成される差動ペアオブジェクトの名前は、回路図上のネットペアのルート名になります。たとえば、上の例の回路図で Parameter Set Directiveパラメータセットディレクティブを使用すると、設計仕様を回路図設計内のネットタイプオブジェクトに関連付けることができます。たとえば、パラメータセットディレクティブを使用して、PCB レイアウト制約、差動ペア、ネットクラスを定義できます。ソフトウェアは、パラメータセットディレクティブ内にある特定の名前のパラメータの有無によって、どの設計ディレクティブを配置しているかを判断します。 Learn more... Blanket Directiveパラメータセットディレクティブは、それが接続されている特定のネットのみを対象にできますが、Blanket ディレクティブと組み合わせることで、その適用範囲をブランケット内のすべてのネットに拡張できます。Blanket ディレクティブは、複数のネットおよび/またはコンポーネントの上に配置します。単純な長方形形状または多角形形状を定義できます。後者では、シート上で必要なネットオブジェクトのカバー範囲をより正確に制御できます。その後、ブランケットに適用されたパラメータセットディレクティブは、ブランケットが覆うすべてのネットとコンポーネントに適用されます。 Learn more... Compile Mask DirectiveNo ERC ディレクティブは、設計内の少数の違反ピン、ポート、シートエントリ、またはネットを抑制するのに適しています。しかし場合によっては、コンポーネントを含む設計全体の一部分を除外したいことがあります。compile mask ディレクティブを使用すると、それが含む設計領域を Compiler から事実上隠すことができ(手動検証時)、まだ完成しておらずコンパイルエラーを生成する回路に対するエラーチェックを手動で防げます。これは、アクティブドキュメントまたはプロジェクトを検証して設計の他の特定領域の整合性を確認したい一方で、未完成部分に関連するコンパイラ生成メッセージの「ノイズ」は望まない場合に非常に有用です。 この機能は、上の例のように設計フローの一部としてシミュレーションが含まれる場合にも非常に有効です。回路シミュレーションを実行する際には電圧源と電流源が必要ですが、完成した PCB 上には不要です。回路構造を少し計画しておけば、通常はシミュレーション専用コンポーネントを設計内の 1 つのセクションにまとめることができ、その領域を compile mask ディレクティブで簡単に覆えます。 Learn more... |

Schematic Document Commenting

コメントは、回路図ドキュメント内のオブジェクト、特定のポイント、または領域に適用できます。コメントはユーザーが追加するメモであり、他のユーザーが返信できます。コメントは、そのデータ自体を変更することなくユーザー間のコラボレーションを促進します。これは、コメントが接続された Workspace によって、そのデータとは独立して保存されるためです。コメントは、Comments and Tasks パネルと連携するコンテキストコメントウィンドウを使用して、設計空間内で直接投稿、返信、管理されます。

詳細については、Document Commenting ページを参照してください。

A-Z Listing

以下は、特定の設計オブジェクトの詳細に QuickNav 形式ですばやくアクセスできるようにした、シンプルなアルファベット順リストです。

AI で翻訳

AI で翻訳