受控阻抗路由

随着器件开关速度不断提高,受控阻抗布线已成为数字设计人员的热门话题。本页介绍如何使用信号完整性分析引擎来匹配器件阻抗,以及在 PCB 编辑器中使用受控阻抗布线功能。

工程圈里有句老话——从事数字设计的电子工程师只有两种:一种是已经遇到过信号完整性问题的,另一种是将来一定会遇到的。不久之前,“信号完整性”这个术语还只是专家才会用到的,而且你只需要在高速设计中才需要处理它。然而,如今那些高速设计中的器件开关速度已不再“特殊”;它们正在迅速成为常态。随着集成电路工艺进步推动晶体管尺寸缩小,其开关速度随之提升。正是这种开关速度会影响数字信号的完整性。

好在,许多潜在的信号完整性问题可以通过遵循良好的设计原则并将设计实现为受控阻抗板来避免。要做到这一点,需要特定的设计工具能力——你需要能够检测可能出现振铃与反射问题网络的分析工具,以及能够实现正确布线阻抗的板级设计工具。Altium Designer 的 PCB 编辑器具备这些能力。

本页将帮助你理解信号完整性问题的成因,以及你的板子是否可能受到这些问题影响。还将讨论你必须采用的两种设计方法来将潜在 SI 问题降到最低——匹配器件阻抗,以及受控阻抗布线。

当布线成为电路的一部分

随着器件开关速度提高,对印制电路板设计人员和制造商的要求也随之增加。当信号的开关边沿长度短于承载该信号的 PCB 走线长度时,这条走线就必须被视为电路的一部分。该走线具有阻抗,称为characteristic impedance (Zo)特性阻抗。

管理这些附加电路要素影响的最佳方式,是将走线布线设计为在全长范围内保持一致的特性阻抗——这种技术称为controlled impedance routing受控阻抗布线。

走线布线的阻抗由以下因素定义:

- Cross-sectional area of the trace - 由线宽、高度(铜厚)以及蚀刻过程中形成的走线边缘斜率决定。

- Distance from the trace to the reference plane(s) - 信号能量的回流路径与信号路径同等重要。该回流路径会在相邻参考平面中沿着信号路径“跟随”。

- Properties of the surrounding materials - 信号能量并不只存在于走线铜箔中;由于集肤效应,它也会沿着走线周围的介质材料传播。介质材料的介电常数用于衡量介质对该能量流动的影响程度。

Simbeor 阻抗计算器会计算为实现指定阻抗所需的线宽。

我需要受控阻抗布线吗?

你可能会问:我真的需要费心做受控阻抗布线吗?

在理想情况下,从器件输出引脚出来的所有能量都会耦合进入 PCB 上连接的走线,沿着 PCB 布线流向另一端的负载输入引脚,并被负载吸收。如果能量没有被负载完全吸收,剩余能量就会反射回 PCB 布线,流回源端输出引脚。这些反射能量会与原始信号相互作用(取决于能量极性,可能叠加或相减),从而产生振铃。如果振铃足够大,就会影响信号完整性,导致电路行为不可预测并产生错误。

那么,如何判断是否可能发生这种情况?如果源端引脚能够在信号到达负载引脚之前完成边沿跃迁,那么你的设计就具备受到反射能量影响的条件。用于判断是否可能出现 SI 问题的一个常见经验法则是“1/3 上升时间”规则。该规则指出:如果走线长度超过上升时间的 1/3,就可能发生反射(振铃)。如果源端引脚上升时间为 1 nSec,那么长于 0.33 nSec(在 FR4 中约为 2 英寸)的走线必须被视为传输线,是信号完整性问题的候选对象。如果你的器件具有这种上升时间,并且你知道会有这种长度级别的布线,那么 PCB 上就可能出现信号完整性问题。

如何控制阻抗?

如何避免能量在源端与负载之间来回反射?通过阻抗匹配来避免。阻抗匹配可确保所有能量从源端耦合进入布线,并从布线耦合进入负载。以阻抗为依据进行板级布线称为受控阻抗布线;换句话说,阻抗已被管理的板称为受控阻抗 PCB。

实现阻抗匹配有两个不同要素:第一是匹配器件;第二是将板子布线为所需阻抗。

器件阻抗匹配

仅靠布线无法实现受控阻抗 PCB。首先,你必须检查并在必要时匹配器件的阻抗。

理想情况下,你希望在原理图设计阶段就检测出可能存在信号完整性问题的网络,这样在开始 PCB 设计流程之前就能加入任何额外的端接器件。由于输出引脚为低阻抗、输入引脚为高阻抗,你很可能需要在设计中添加端接器件以实现阻抗匹配。

你可以在原理图捕获阶段对设计执行信号完整性分析。当运行 Tools » Signal Integrity 命令时,通常会出现 Errors or Warnings 对话框,提示并非所有器件都已分配信号完整性模型。信号完整性分析引擎会根据器件标号自动选择默认模型,点击 Continue 使用默认值,或点击 Model Assignments 查看并更改模型。你也可以随时通过 Signal Integrity 面板中的 Model Assignments 按钮访问 Signal Integrity Model Assignments 对话框。

分析设计

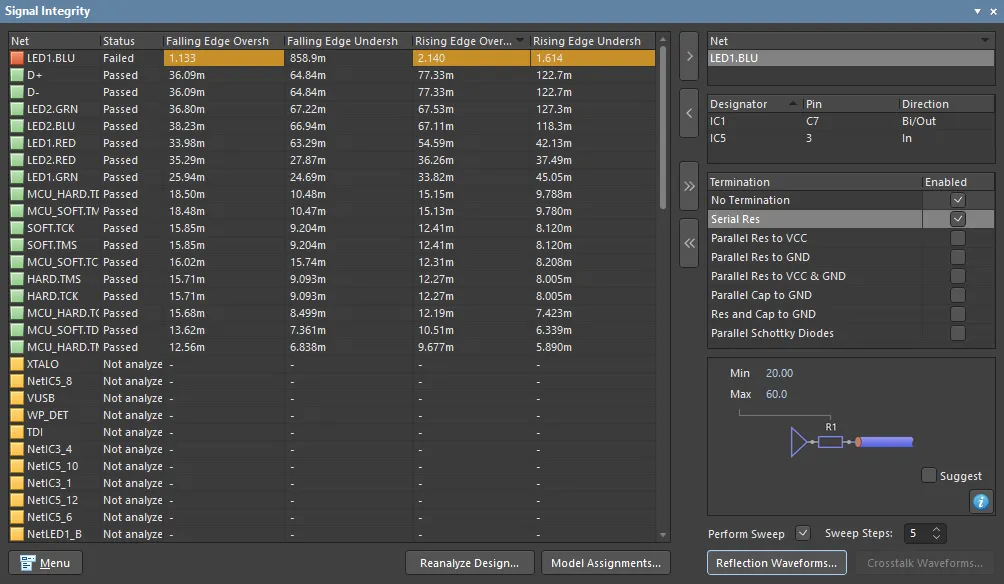

运行 Tools » Signal Integrity 命令后,将对设计进行分析,并在 Signal Integrity 面板中识别出任何潜在问题网络,如下所示。

在设计捕获阶段测试设计是否存在潜在的信号完整性问题。

在设计捕获阶段测试设计是否存在潜在的信号完整性问题。

在该面板中,你可以对选定网络(或多个网络)执行反射分析。左侧显示设计中所有网络的分析结果。选择一个网络并点击 ![]() 按钮(或双击网络名称),将该网络传送到面板右侧的 Net 字段,在那里你可以对该网络进行详细分析,包括:

按钮(或双击网络名称),将该网络传送到面板右侧的 Net 字段,在那里你可以对该网络进行详细分析,包括:

- 检查该网络中的引脚:可单击交叉探测到原理图上的该引脚,或双击检查并配置分配给该引脚的模型。

- 为该网络启用一个或多个理论端接选项。

- 对该网络执行反射分析,生成一组波形,显示该网络中各引脚处的行为。

该面板允许你尝试可能的端接配置与数值。注意,上图所示的 Signal Integrity 面板的 Termination 区域已启用 Serial Res 选项。面板下方部分显示一个串联端接电阻。在这里你可以定义用于反射分析的理论串联端接电阻最小值与最大值(取消勾选 Suggest 复选框即可输入你自己的数值)。

探索结果

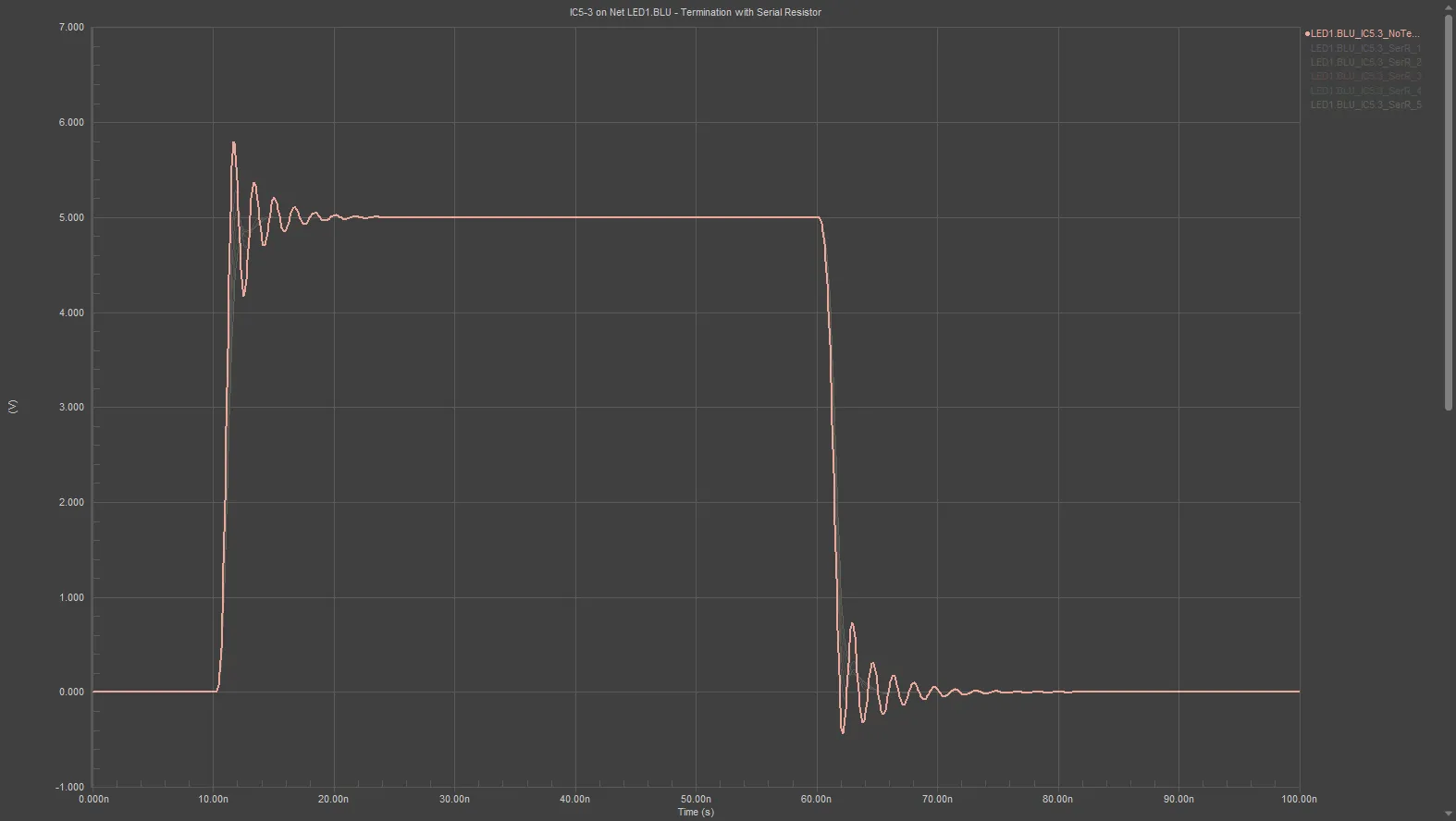

点击 Reflection Waveforms 按钮后,将对该网络执行精确的反射分析,并在新的波形窗口中显示结果(*.SDF)。

波形窗口将包括:

- 为每个被分析的网络提供一张图表;点击窗口底部的选项卡可在各图表之间切换。

- 每个图表都会为该网络中的每个引脚包含一条曲线,用于显示该引脚处的信号行为。

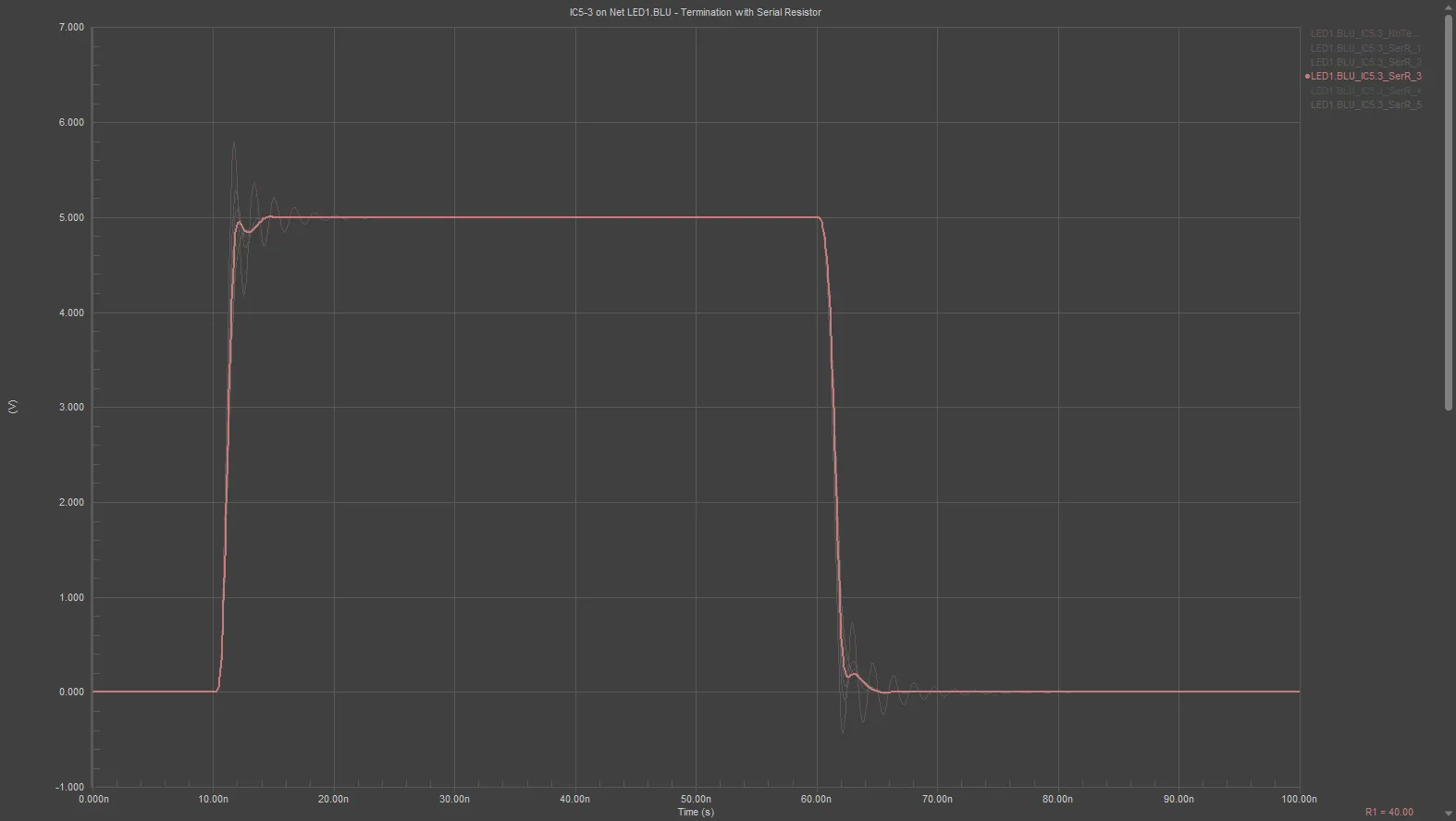

下方图片展示了在上一面板图像中所选网络的输入引脚处的两张结果图。第一张图为该网络在未端接情况下的输入引脚;第二张图显示了六次扫描:一次为原始未端接网络,随后五次为在源端引脚处加入理论串联端接电阻后的扫描结果。

共执行了五次反射分析(Sweep Steps 选项值 = 5),理论端接电阻从 Min = 20 欧姆步进到 Max = 60 欧姆。五次扫描(第一次为 20 欧姆,最后一次为 60 欧姆)列在图表右侧。点击每个标签会高亮对应结果,并在右下角显示理论端接电阻值。对于该网络,40 欧姆的串联端接电阻会得到右侧图片中所选的那条曲线。

左图显示了一个可能存在信号完整性问题的网络的反射分析;右图为同一网络,但加入了约 40 欧姆的理论串联端接电阻。

左图显示了一个可能存在信号完整性问题的网络的反射分析;右图为同一网络,但加入了约 40 欧姆的理论串联端接电阻。

什么决定了布线阻抗?

实现受控阻抗 PCB 的第二部分,是以使走线具有明确阻抗的方式来布线。影响信号布线阻抗的因素有很多,包括走线的尺寸以及用于制造 PCB 的材料特性。

PCB 编辑器包含来自 Simberian 的 Simbeor® 电磁信号完整性引擎。Simbeor 的模型精度通过用于 3D 全波分析的高级算法、基准测试以及实验验证来确认。Simbeor 引擎支持所有现代板结构与材料。

Simbeor 版本

Simbeor SFS

阻抗由 Simbeor SFS(准静态场求解器)计算。Simbeor SFS 是一种基于矩量法(Method of Moments)的先进准静态 2D 场求解器,并已通过收敛性、对比与测量验证。该求解器会对介质与导体边界进行网格划分,并求解相应方程,以构建用于电报方程的、随频率变化的 RLGC 矩阵。

Simbeor SFS 不是全波求解器,因为在 PCB 互连中评估阻抗、延迟或衰减并不需要全波求解器,这得益于其中传播波的准 TEM 特性。这类波可以通过准静态 2D 场求解器提取的 RLGC 参数进行精确仿真。

Simbeor SFS 求解器的一个独特特性是支持导体粗糙度模型。注意:它不支持多层导体模型(电镀),且粗糙度对所有导体是相同的。该求解器为准静态,是因为其解不包含在微带线中出现的高频色散(高频时电场更集中在介电常数更高的介质中)。

► 了解更多关于 Simberian 电磁信号完整性技术

支持的 PCB 结构

可对以下 PCB 结构计算阻抗:

- 微带线(Microstrip)

- 对称带状线(Symmetrical Stripline)

- 非对称带状线(Asymmetrical Stripline)

- 单端与差分共面结构

- 具有不同介电特性的多个相邻介质层。

为受控阻抗布线配置 PCB

受控阻抗布线的核心,是配置走线尺寸与板材材料属性,以实现特定阻抗。这在 PCB 编辑器的 Layer Stack Manager 中完成。要打开 Layer Stack Manager,,请从主菜单中选择 Design » Layer Stack Manager。Layer Stack Manager 会像原理图页、PCB 以及其他文档类型一样,在文档编辑器中打开。

实现特定阻抗所需的线宽,会作为阻抗配置文件的一部分进行计算,并在 Layer Stack Manager 的 Impedance 选项卡中进行配置。

计算依据:

- 你在 Impedance 选项卡中配置的 Target Impedance、Target Tolerance 和 Roughness 的数值,以及

-

在 Stackup 选项卡中定义的材料设置,包括:

- 信号层厚度,

- 周围介质层的厚度(到参考平面/参考平面组的距离),以及

- 介质材料属性(介电常数 Dk 与损耗因子 Df)。

当这些参数正确配置后,阻抗计算器就具备足够信息来计算以下内容:

- 线宽(Trace Width)

- 计算阻抗(Z)

- 共模阻抗(Zcomm)

- 阻抗偏差(Z Deviation)

- 传播延迟(Tp)

- 单位长度电感(p.u.l.)

- 单位长度电容(p.u.l.)

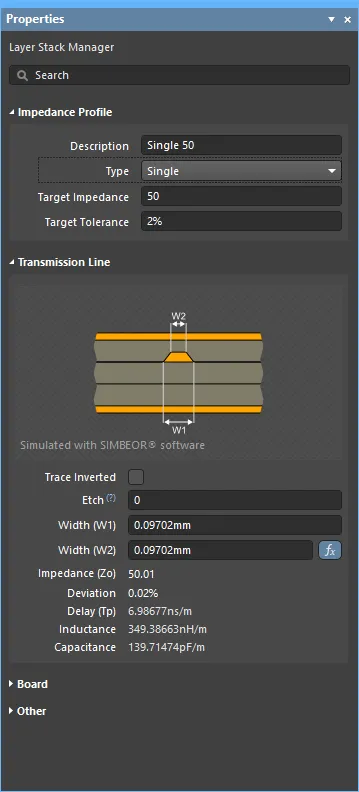

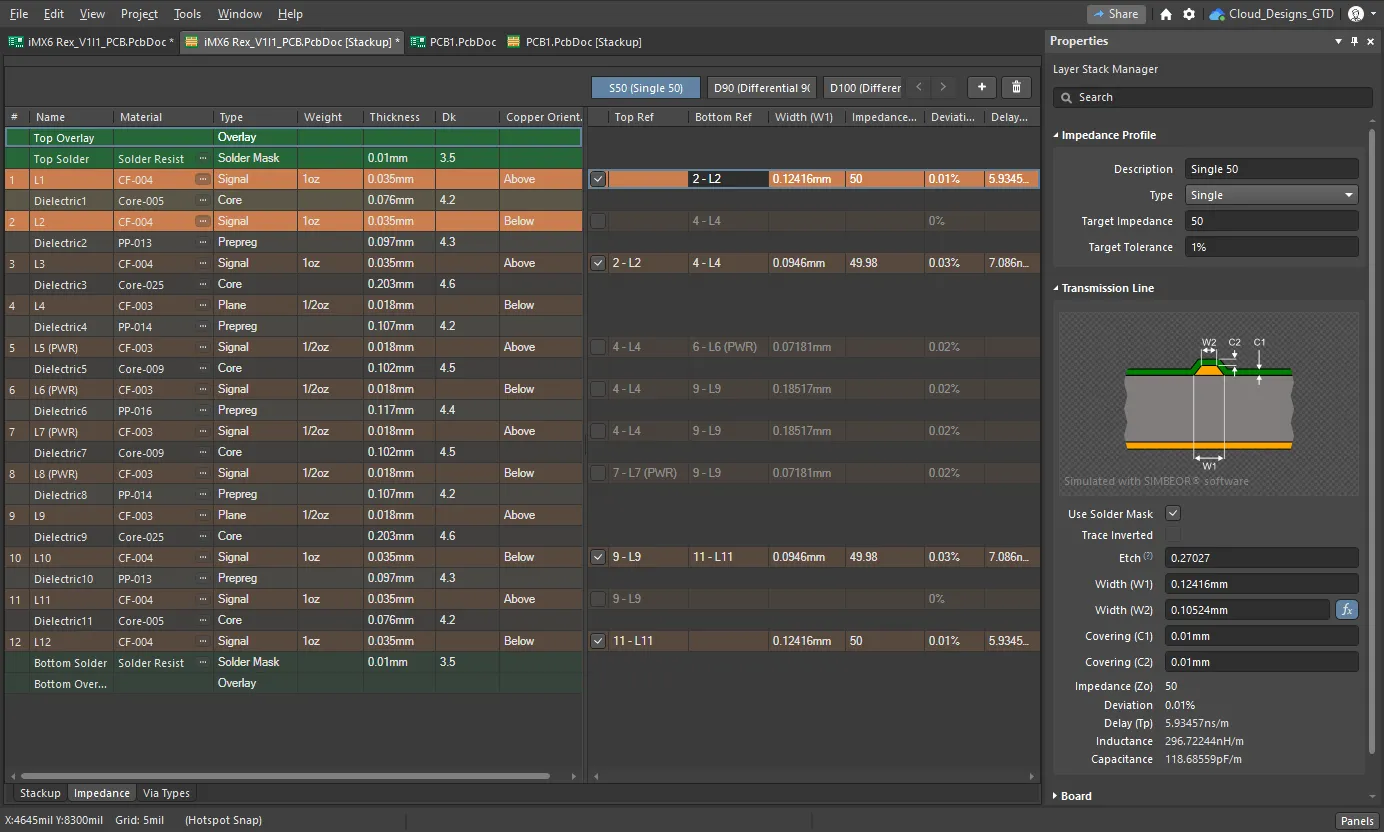

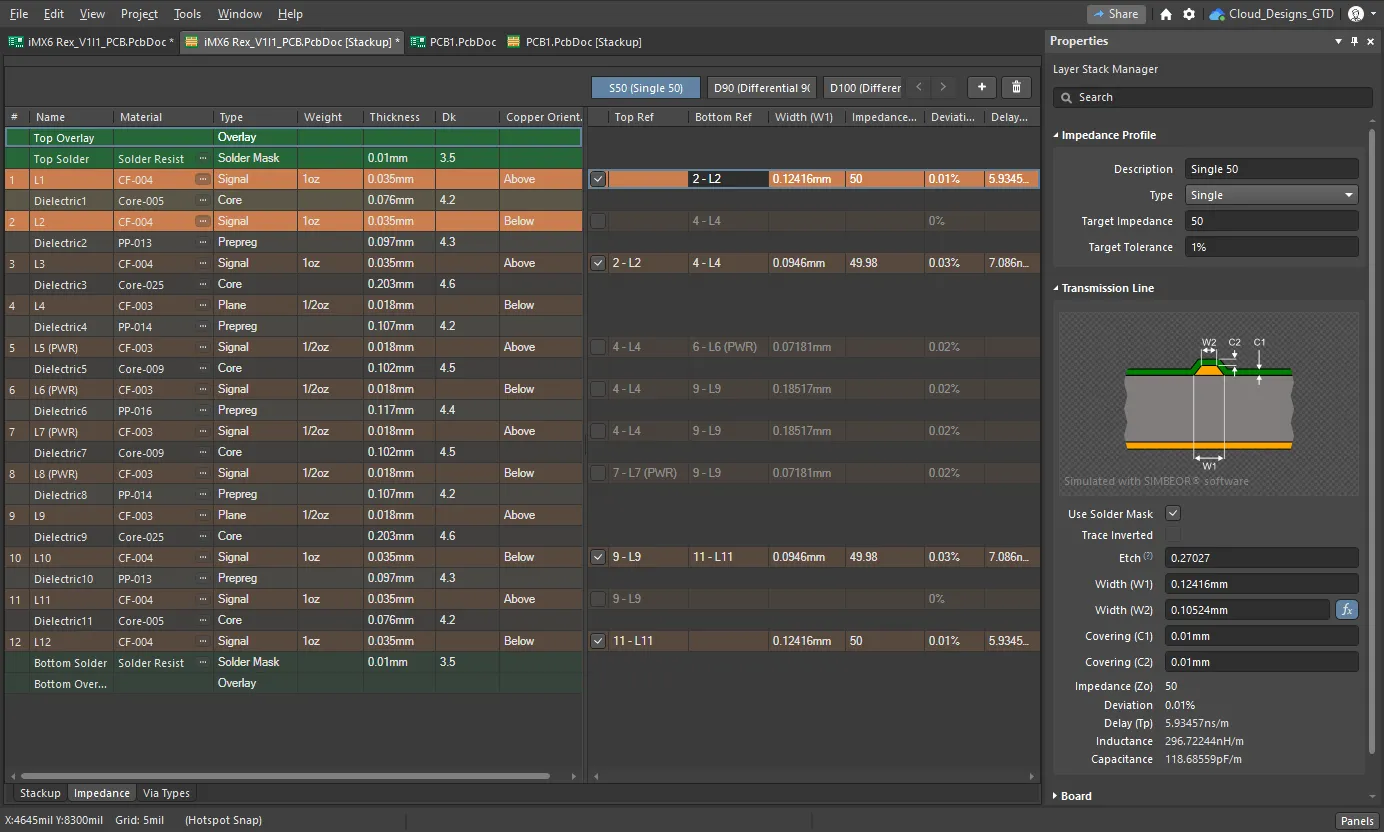

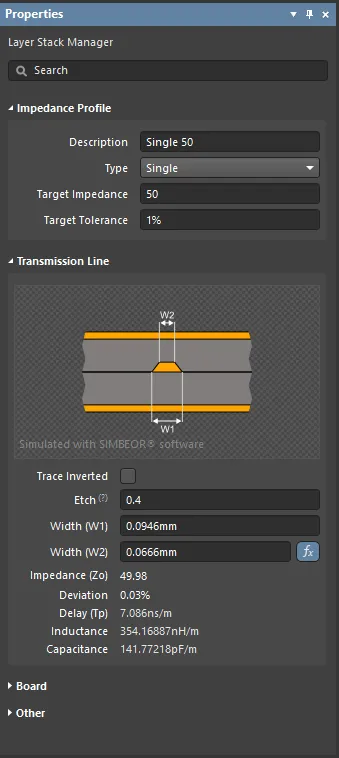

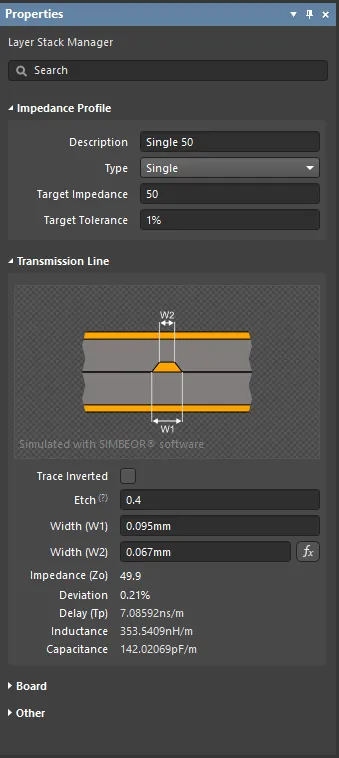

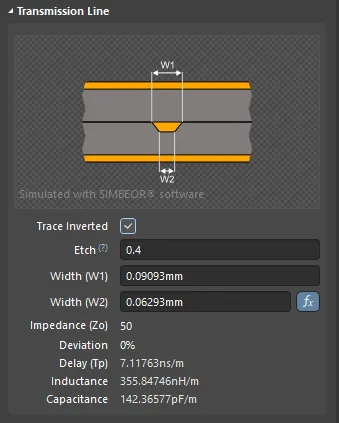

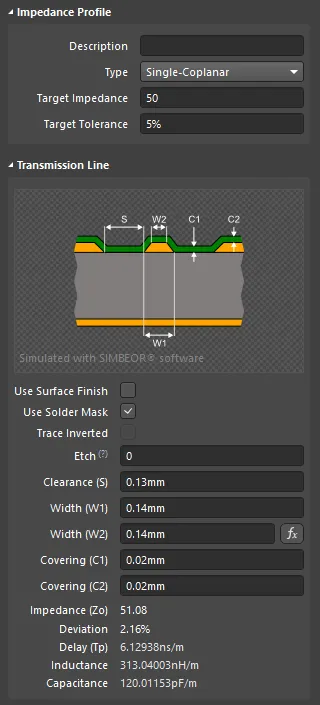

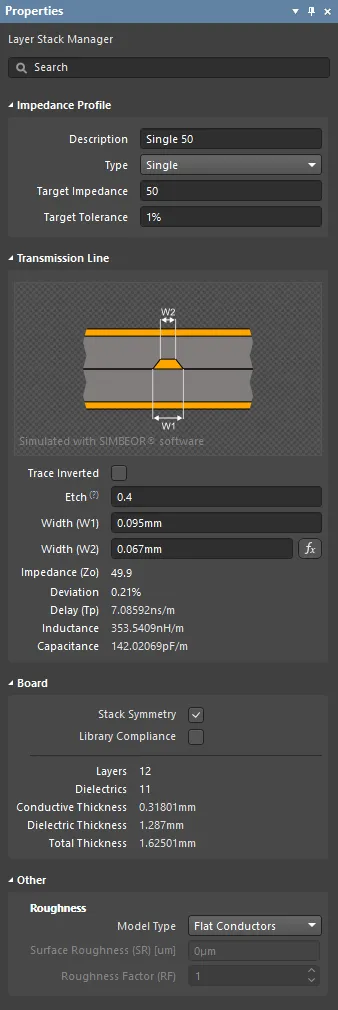

当在 Layer Stack Manager 中选择 Impedance 选项卡时,计算值会显示在 Properties 面板 的 Transmission Line 区域中,如下所示。

为在顶层布线的单根网络定义的 50Ω 阻抗配置文件。将光标悬停在图片上可显示同一配置文件在 L3 层的设置(图片来源:FEDEVEL Open Source,www.fedevel.com)。

为在顶层布线的单根网络定义的 50Ω 阻抗配置文件。将光标悬停在图片上可显示同一配置文件在 L3 层的设置(图片来源:FEDEVEL Open Source,www.fedevel.com)。

配置层叠(Layer Stackup)

Main page: 定义层叠结构

铜层与介质制造层在 Layer Stack Manager 的 Stackup 选项卡中配置。

- 在此选项卡中可添加、删除并配置层。对于刚挠结合设计,也是在此选项卡中启用与禁用层。

-

当前选中层的属性可直接在表格中编辑,或在 Properties 面板中编辑。点击设计空间底部的

按钮以启用该面板。

按钮以启用该面板。

- 在层表格中右键单击,或使用 Edit » Add Layer 命令来添加层。添加铜层时,如果相邻现有层也是铜层,则会同时添加一个介质层。

- 如果在 Properties 面板的 Board 区域中启用了 Stack Symmetry 选项,则会以围绕中间介质层对称的匹配成对方式添加层。

-

层的 Material 可以直接输入到选中的 Material 单元格中,或在 Select Material 对话框中选择;点击省略号按钮(

)打开该对话框。

)打开该对话框。

- 可为铜层添加表面处理。使用 Add Layer 子菜单将 Surface Finish 层添加到当前选中的铜层,然后点击新表面处理层的省略号按钮以选择处理类型。

- 可通过右键菜单或 Edit 菜单,在同类型层之间将所选层上移或下移。

- Properties 面板的 Board 区域包含用于强制执行 Stack Symmetry 与 Library Compliance 的选项。下文将进一步说明。

- Properties 面板的 Board 区域显示当前所选叠层(或多叠层刚挠结合设计中的子叠层)的摘要。

层叠注意事项

控制阻抗的一项基本要求,是在每条信号路径下方提供信号回流路径。Simbeor SI 引擎同时支持平面层,以及由多边形覆盖的信号层。这些回流路径层应分布在整个板层叠中。理想情况下,应布置为:每个承载受控阻抗布线的信号层旁边至少有一个相邻的回流路径层。相邻回流路径层提供信号回流路径,并且由于一些此处不展开的原因,它与该平面所分配的直流电压无关。

在平面中流动的回流电流会尝试沿着与信号层走线相同的物理路径流动,因此必须避免在任何关键走线下方的回流路径层中引入不连续性,例如分割或开窗。

除了选择合适的信号层与平面层顺序外,还需要定义每一层的材料属性,包括:

- 铜厚

- 介质厚度

- 介电常数

这些数值以及走线宽度都会影响最终阻抗。要实现所需阻抗,就需要对这些数值进行综合调节。请记住,可选的铜厚与介质厚度也可能受限于 PCB 制造商可提供的材料。

► 了解更多关于 可能的层叠方案

定义阻抗配置文件

Simbeor 引擎已内置于 PCB 编辑器的 Layer Stack Manager(Design » Layer Stack Manager)中。要为受控阻抗布线配置层叠,请切换到 Layer Stack Manager's Impedance 选项卡,在那里可以添加并配置阻抗配置文件(impedance profile)。

为在顶层布线的单独网络定义的 50Ω 阻抗配置文件。将光标悬停在图像上可显示同一配置文件在 L3 层的设置。

为在顶层布线的单独网络定义的 50Ω 阻抗配置文件。将光标悬停在图像上可显示同一配置文件在 L3 层的设置。

创建与配置 Impedance Profile 的注意事项:

- 在 Layer Stack Manager 中切换到 Impedance 选项卡,如上所示。

-

单击

按钮(如果已定义配置文件,则单击

按钮(如果已定义配置文件,则单击  按钮)以添加新的配置文件。

按钮)以添加新的配置文件。

- 在 Properties 面板中定义所需的阻抗 Type、Target Impedance 和 Target Tolerance。Description 为可选项,它会在显示 Impedance Profile 名称的所有位置一并显示。

-

层网格分为两个区域;层叠中的各层显示在左侧,然后对于层叠中的每个信号层,在右侧的 Impedance Profile 区域中都会显示一个对应层。使用 Profile 区域中的层复选框来启用该层的阻抗计算。以上图为例,并参考最左列显示的层号,

L1、L3、L10和L12层的复选框已勾选,从而启用这些层进行阻抗计算。 -

当你在 Profile 区域中单击某个已启用的层时,除用于计算该所选信号层阻抗的层之外,层叠中的其他层都会淡化显示(如上图所示)。在 Impedance Profile 区域的 Top Ref 和 Bottom Ref 列中编辑该层的参考层。注意,参考层可以是 Type 为

Plane或 Signal 的层。例如,在上图中,层叠中的L10层已启用阻抗计算,Top Ref 设为9-L9(这是一个Plane层),而 Bottom Ref 设为11-L11(这是一个 Signal 层)。软件假定:如果某个信号层被用作参考平面,则该层包含一整片连续铜面,并连接到电源或地网络。 - 对其他同样需要以该阻抗进行布线的每一层,启用 Impedance Profile 复选框并配置参考平面。将光标悬停在上图上可显示 L3 层的 S50 Impedance Profile。

- 如果计算得到的布线线宽是无法下单/加工的数值,你可以 微调线宽与间距设置。

微调线宽与间距设置

软件会根据目标阻抗与公差计算 Trace Width。计算得到的线宽出现无法下单/加工的数值并不少见,例如 0.0683mm。制造商会告知可用的材料厚度以及他们能达到的线宽精度。随后就需要从期望值出发,在将尺寸调整为可实现的数值后,测试其对计算阻抗值的影响。

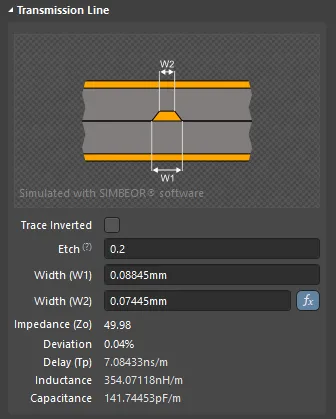

为支持这种测试与调参过程,阻抗计算器支持正向与反向阻抗计算。默认模式为正向(输入阻抗,软件计算线宽)。 ![]() 图标表示被计算的变量。

图标表示被计算的变量。

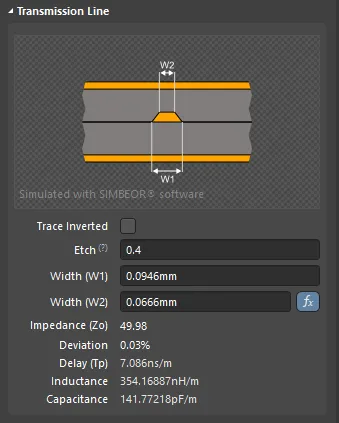

目标阻抗 50Ω 正向计算得到的线宽(W1)为 94.6µm。右侧图像显示当线宽(W1)设为 95µm 时的反向计算结果。

目标阻抗 50Ω 正向计算得到的线宽(W1)为 94.6µm。右侧图像显示当线宽(W1)设为 95µm 时的反向计算结果。

要反向计算并为所选层探索不同线宽,请输入新的 Width (W1) 值并按键盘 Enter。计算值将更新,以反映线宽变化带来的影响。单击 ![]() 按钮可将计算器返回到正向计算模式。在 Width (W2) 中输入新值会改变 Etch 的值。

按钮可将计算器返回到正向计算模式。在 Width (W2) 中输入新值会改变 Etch 的值。

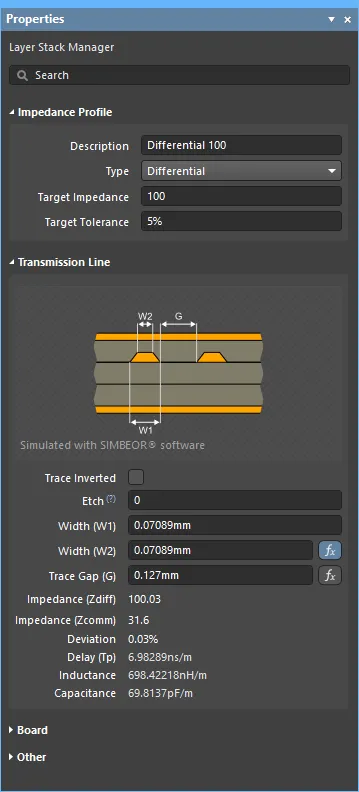

要查看差分对传输线结果,可通过单击相应的 ![]() 按钮来指定被计算的变量——Trace Width 或 Trace Gap。编辑另一个变量以改变 Target Impedance,或改为调整 Target Impedance 以探索其对另一个变量的影响。

按钮来指定被计算的变量——Trace Width 或 Trace Gap。编辑另一个变量以改变 Target Impedance,或改为调整 Target Impedance 以探索其对另一个变量的影响。

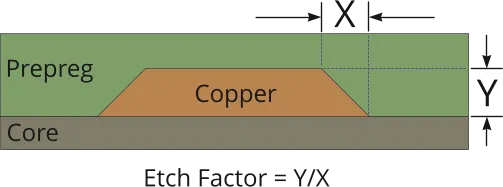

蚀刻因子(Etch Factor)

PCB 上的信号走线通过蚀刻去除多余铜箔来制造。由于蚀刻液从表面开始蚀刻,表面铜与蚀刻液接触时间更长。结果是走线成品边缘会形成斜坡,从而减小成品走线的截面积,如下图所示。

蚀刻过程中走线边缘损失的铜面积(两侧边缘)= X * Y

斜坡的程度称为蚀刻因子(Etch Factor),其中:

Etch Factor = Y/X

如果 Y = X,则 Etch Factor = 1

参见 Properties 面板中所示图像:

将光标悬停在 ? 上可显示公式。

将光标悬停在 ? 上可显示公式。

Etch Factor 的标准定义是将其指定为 trace thickness / amount of over-etching 的比值。由此得到以下公式:

Etch Factor = T/[0.5(W1-W2)]

这种方法的缺点是:若要指定“无过蚀刻”(即走线边缘为垂直),就必须为蚀刻因子输入 inf(无穷大)。为简化蚀刻量的指定,公式已取倒数,使得可以输入 0(零)来表示没有过蚀刻。

Etch = [0.5(W1-W2)]/T

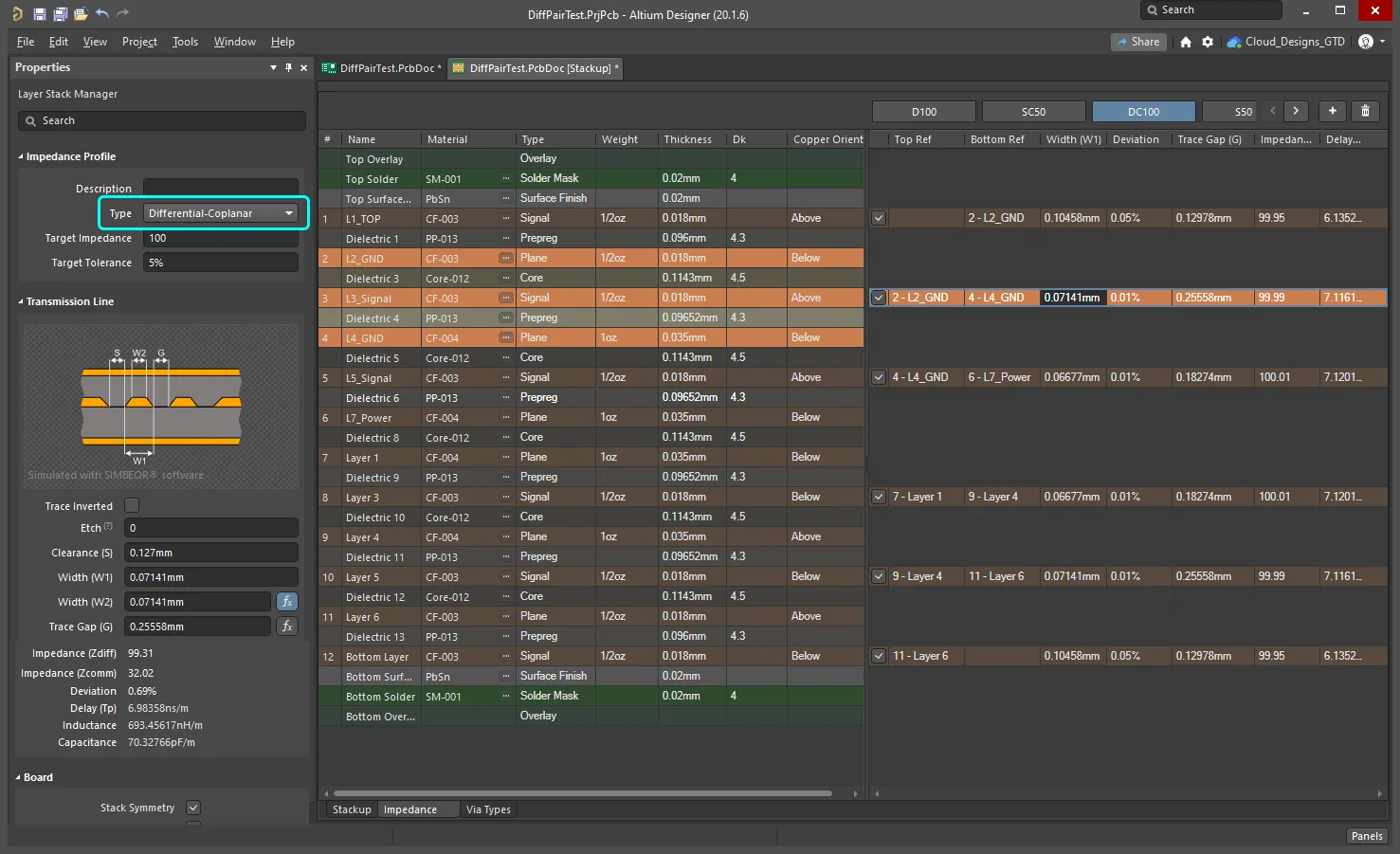

铜箔方向(Copper orientation)

另一个会影响蚀刻因子的制造细节是铜箔方向。PCB 走线是通过在覆铜介质基材上层压的一整张铜箔上蚀刻去除多余铜而形成的。铜箔方向定义了铜相对于该基材“朝外”的方向。也可以理解为铜从哪个方向被蚀刻:从上方或从下方。

单击 Trace Inverted 复选框可将 Copper Orientation 在 Above 与 Below 之间切换。

单击 Trace Inverted 复选框可将 Copper Orientation 在 Above 与 Below 之间切换。

导体表面粗糙度(Conductor Surface Roughness)

印制电路板中每一层铜的表面都具有一定粗糙度。在 PCB 制造过程中,会对铜层表面进行处理以增加粗糙度,从而提升铜与介质层之间的粘附力。当开关速率高于 10 GB/s 时,这种表面粗糙度会成为导体阻抗的重要影响因素。通过大量研究与分析,行业专家认为表面粗糙度可用由 Surface Roughness 与 Roughness Factor 值推导出的粗糙度修正系数来建模。

Roughness相关设置可在 Properties 面板的 Layer Stack Manager 模式中找到。这些参数仅用于导电层。

表面粗糙度会被纳入特性阻抗的计算。

表面粗糙度会被纳入特性阻抗的计算。

粗糙度:

-

Model Type - 用于计算表面粗糙度影响的首选模型(关于各种模型的更多信息请参阅下方文章)。适用于子叠层中的所有铜层。

-

Surface Roughness - 表面粗糙度数值(可从制造商处获得)。输入 0 到 10µm 之间的值,默认 0.1µm

-

Roughness Factor - 用于表征因粗糙度效应导致导体损耗的预期最大增幅。输入 1 到 100 之间的值;默认 2。

延伸阅读

- 用于分析导体粗糙度对互连中信号损耗与色散影响的实用方法: Y. Shlepnev, C. Nwachukwu, DesignCon2012.

- 互连导体表面粗糙度建模的统一方法: Y. Shlepnev, 2017 IEEE 第 26 届电子封装与系统电性能会议(EPEPS2017)

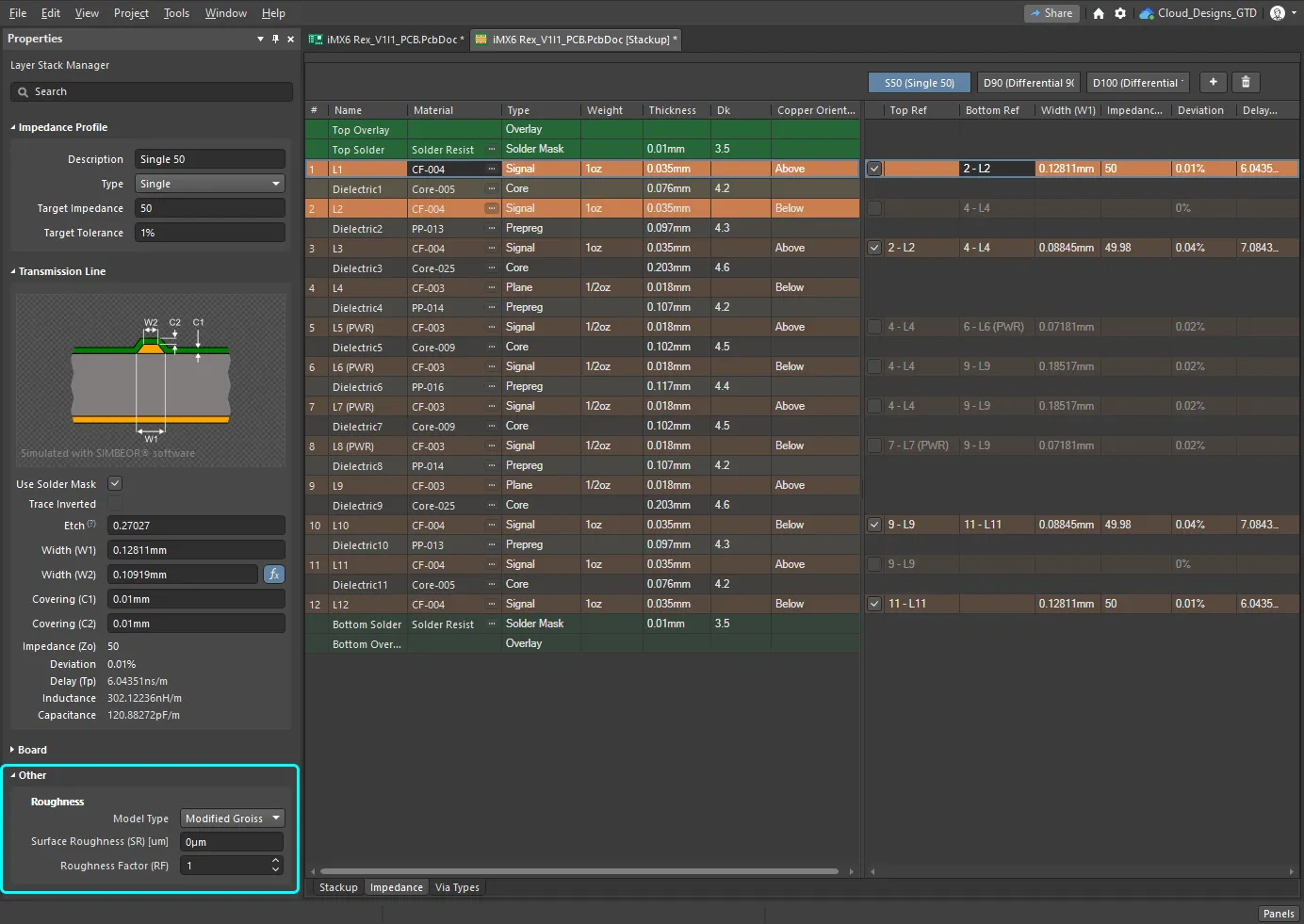

对共面传输线结构的支持

Layer Stack Manager 中的阻抗计算器支持单端与差分的共面结构。创建新的阻抗配置文件,然后在 Impedance Profile Type 下拉列表中选择 Single-Coplanar 或 Differential-Coplanar。

使用共面结构:

- 与标准单端/差分阻抗一样,每个变量的数值都会基于用户定义的 Target Impedance 与 Target Tolerance 以及板层的物理属性自动计算。这些自动计算的数值可在 Properties 面板的 Layer Stack Manager 模式中,通过在编辑框中输入新值来进行调整。

- 要将你希望以共面结构布线的信号网络作为目标,请配置一条带有已启用 Use Impedance Profile 选项并选择所需 Coplanar Impedance Profile 的 Routing Width(或 Differential Pairs Routing)设计规则。

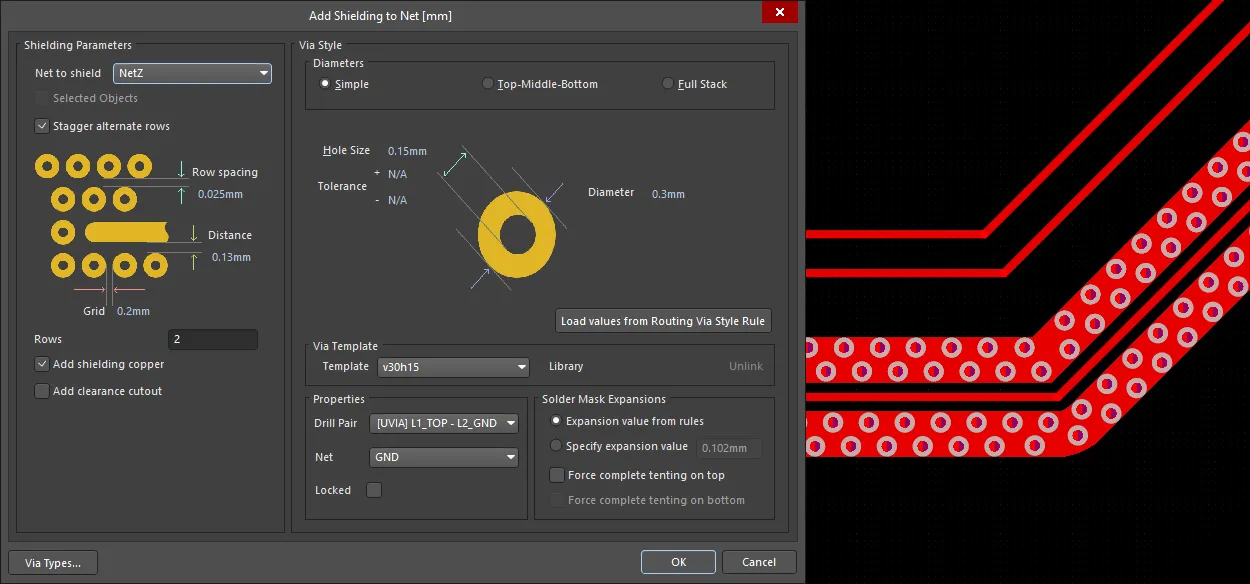

- 共面结构要求信号走线两侧都要有参考平面;这可以通过你放置的多边形来创建,或者如果添加了缝合过孔,则可通过 Add Shielding to Net 命令来创建(更多信息见下文)。如果你放置了多边形,该多边形与信号走线之间的间距由 Simbeor 阻抗计算器确定的 Clearance (S) 值定义(显示在 Properties 面板中,如上方和下方图片所示)。请配置一条 Clearance design rule 来控制参考多边形与信号走线之间的间距(show image)。

-

当共面结构接地时,通常的做法是在信号走线两侧各加一排过孔栅栏(via fence)。在 PCB 编辑器中使用 Tools » Via Stitching/Shielding » Add Shielding to Net 命令来实现。除了放置过孔外,通过启用 Add shielding copper 选项,该命令还可以在信号布线周围放置一个多边形以覆盖过孔栅栏,如下方右侧图片所示。

► 了解更多关于 Via Shielding

阻抗计算器会确定信号特性与间距(第一张图);在过孔屏蔽的 Distance 设置中使用该间距。

阻抗计算器会确定信号特性与间距(第一张图);在过孔屏蔽的 Distance 设置中使用该间距。

选择层材料

在受控阻抗设计中,选择层叠结构中使用的材料非常重要。

例如,用于制造 PCB 最常见的材料是玻璃纤维(fiberglass)增强环氧树脂,并在两侧贴合铜箔。玻璃纤维布的编织紧密程度会影响介电常数 Dk(介电率)和损耗角正切 Df 的数值及一致性。编织玻璃布周围是树脂——树脂的含量比例同样会影响材料性能。

可用的玻璃纤维编织规格范围很大。为帮助确保 PCB 制造中使用的玻璃纤维基材料的可预测性与性能,IPC 制定了编织规格标准:

IPC standard IPC-4412B: Specification for Finished Fabric Woven from "E" Glass for Printed Boards

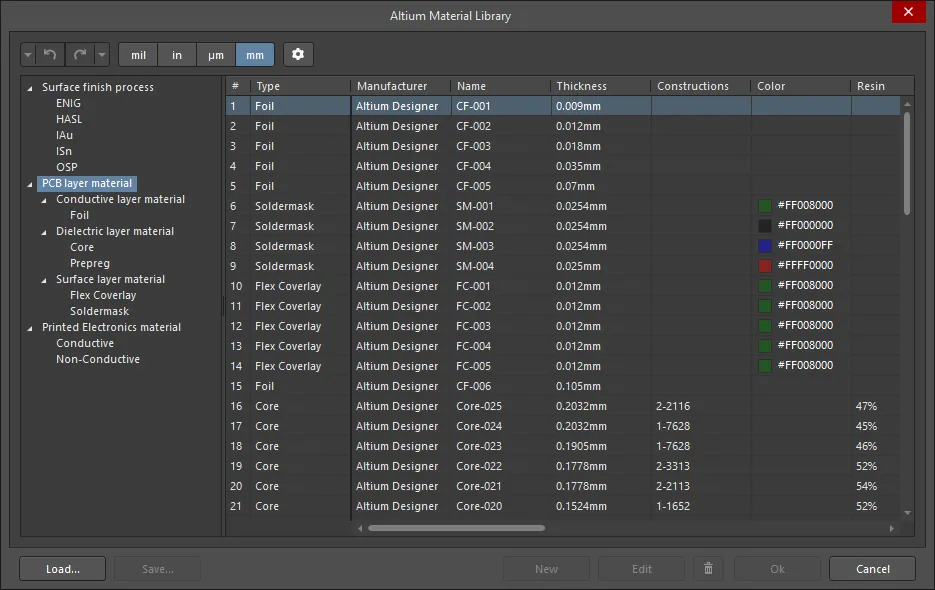

材料库

作为设计人员,你可以直接在 Layer Stack Manager 中编辑材料属性,或从 Altium Material Library 中选择材料。

可在 Altium Material Library dialog 中查看(并添加)整个库(Tools » Material Library)。

材料按用途类别组织,可通过对话框左侧的树状结构访问。在此层级之下,每个用途类别又细分为功能类别,例如在 PCB layer material 类别中的 Conductive layer material、Dielectric layer material, 和 Surface Layer Material i。

添加、保存与加载材料

当在树中选中某个特定材料类别时,可以向库中添加新材料。可加载外部材料库中定义的材料(Load 按钮),并且也可以将已在 Altium Material Library 对话框中添加的用户自定义材料保存到用户库(Save 按钮)。仅会保存用户自定义材料。

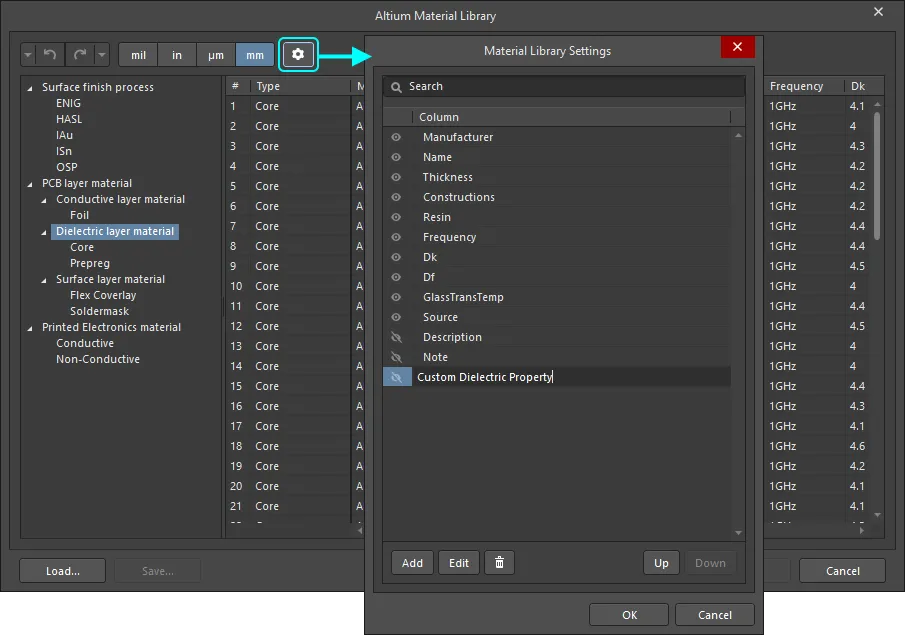

为材料添加自定义属性

可以为库中详细列出的材料(默认材料和用户自定义材料)添加自定义属性。要添加自定义属性,先在左侧树中选择正确的节点,以定义要添加到哪些材料,然后点击 ![]() 按钮打开 Material Library Settings 对话框。

按钮打开 Material Library Settings 对话框。

随后可在 Altium Material Library 对话框中将所需值添加到选定材料;选择该行并点击 Edit 按钮。

Properties Panel

当 Layer Stack 文档的 Impedance 选项卡处于活动状态时, Properties 面板允许你配置 Impedance Profile 的需求。随后可在 Routing Width 或 Differential Pairs Routing 设计规则中选择所需的 Impedance Profile。

-

Impedance Profile

- Description – 输入有意义的描述。此字段可选,并会在显示 Impedance Profile 名称的任何位置一并显示。

- Type – 使用下拉列表选择阻抗类型。可选项为 Single、Differential、Single-Coplanar 和 Differential-Coplanar。

- Target Impedance – 输入你希望实现的阻抗。

- Target Tolerance – 输入你希望实现的公差。你应与制造商沟通,以确定制造商能够实现的现实公差值。

-

Transmission Line

- Trace inverted – 启用此选项可反转走线,如 Properties 面板所示。该选项与 Stackup 选项卡处于活动状态时显示的 Copper Orientation 选项相同,用于定义铜箔层压到芯板(core)上的方向。铜的朝向定义了铜相对该基材“伸出”的方向。你也可以将其理解为铜从上方或下方被蚀刻的方向。

-

Etch – Etch Factor 为

= T/[(W1-W2)/2],它会以铜厚的平方来减少走线的总截面积。请向板厂咨询其工艺所形成的 Etch 相关信息。

-

Width (W1) / (W2) – W1 是你布线的走线宽度,W2 是该走线蚀刻后的上表面宽度,并应用了 Etch 系数。走线宽度提供正向/反向计算功能。默认根据你输入的 Target Impedance 来计算宽度(正向计算)。该宽度可能是制造商无法实现的数值,例如 5.978,而他们希望更合理的数值,例如 6.0。你可以在 Width 字段中输入 6.0,并在键盘上按 Enter 以重新计算相关数值(Impedance、Deviation 等)。此时

按钮会变灰(变为不可用),你已处于反向计算模式。如果点击该按钮使其变为可用,则会回到正向模式,Width (W1) 将恢复为计算值。该功能可让你探索更现实、可制造的线宽选项。手动输入 W2 的值会相应更新蚀刻系数。

按钮会变灰(变为不可用),你已处于反向计算模式。如果点击该按钮使其变为可用,则会回到正向模式,Width (W1) 将恢复为计算值。该功能可让你探索更现实、可制造的线宽选项。手动输入 W2 的值会相应更新蚀刻系数。

- Impedance – 软件会根据用于制作电路板的材料属性(铜、芯板和预浸料)以及走线的截面积(由走线宽度、厚度和蚀刻系数决定)来计算阻抗。

- Deviation – 这是你期望值(目标阻抗)与实际得到的值(计算阻抗)之间差异的度量。软件会根据用于制作电路板的材料属性(铜、芯板和预浸料)以及走线的截面积(由走线宽度、厚度和蚀刻系数决定)来计算阻抗偏差(即基于输入材料与尺寸你实际会得到的结果)。

- Delay – 这是信号从发送端到接收端所需的传播时间。

- Inductance – 阻抗计算器使用 Impedance 值来计算单位长度电感。

- Capacitance – 阻抗计算器使用 Impedance 值来计算单位长度电容。

-

Board

- Stack Symmetry – 启用后可围绕中间介质层成对添加匹配层。启用时,会立即检查层叠是否围绕中央介质层对称。如果任意一对与中央介质参考层等距的层不完全相同,则会打开 Stack is not symmetric dialog。

- Library Compliance – 启用后,对于从材料库中选择的每一层材料,都会将当前层属性与库中该材料定义的数值进行核对。

- Substack – 此信息针对当前选中的子叠层(层、介质、厚度等)。当你从一个子叠层切换到另一个子叠层时,这些信息会相应更新(针对当前选中的子叠层)。

- Stack Name – 输入一个有意义的子叠层名称。当 X/Y 叠层区域被分配一个层子叠层时,此字段很有用。

- Is Flex – 如果该子叠层为柔性(flex),则启用。

- Layers – 层的总数。

- Dielectrics – 介质的总数。

- Conductive Thickness – 导电层的厚度。铜信号层被称为导电层。

- Dielectric Thickness – 介质层的厚度。

- Total Thickness – 板的总厚度。

- Other

-

Roughness – 显示导电层的粗糙度。

- Model Type – 用于计算表面粗糙度影响的首选模型(关于各种模型的更多信息请参阅下方文章)。适用于叠层中的所有铜层(是否应为子叠层?)。

- Surface Roughness – 表面粗糙度的数值(可从你的板厂获取)。输入 0 到 10µm 之间的值,默认值为 0.1µm

- Roughness Factor – 表征由于粗糙度效应导致导体损耗的预期最大增幅。输入 1 到 100 之间的值;默认值为 2。

配置设计规则

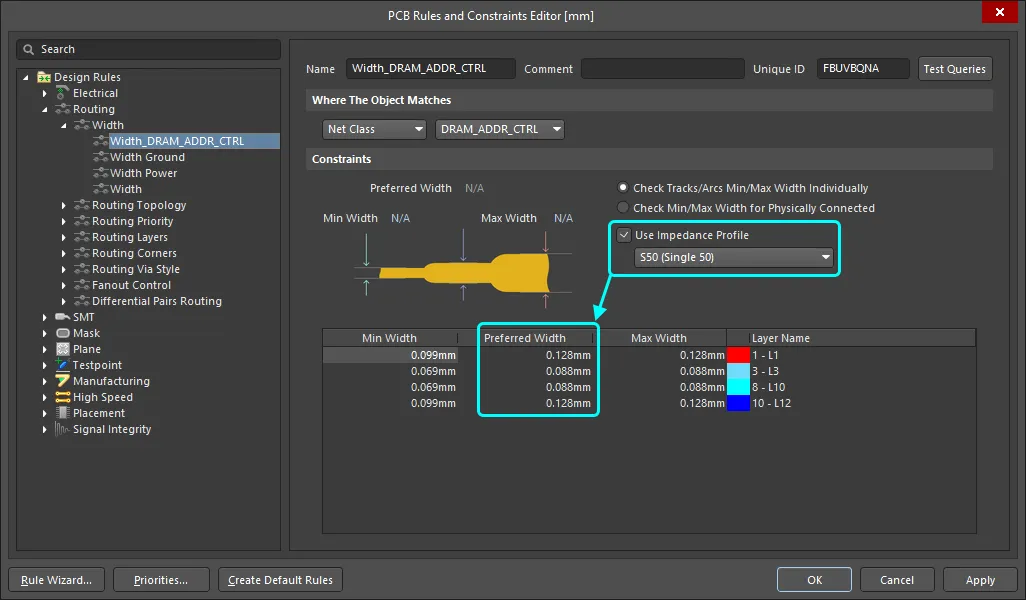

走线阻抗由走线的宽度和高度以及周围介质材料的属性决定。基于在 Layer Stack Manager 中定义的材料属性,在创建每个阻抗配置文件时会计算所需的走线宽度。根据材料属性不同,当走线层发生变化时,宽度也可能随之变化。此“随走线层变化而改变宽度”的需求,会由在 PCB Rules and Constraints Editor(Design » Rules)中配置的相应走线设计规则自动管理。

对于大多数板级设计,通常会有一组特定的网络需要以受控阻抗进行布线。常见做法是创建一个包含这些网络的网络类(net class)或差分对类(differential pair class),然后创建一条针对该类的布线规则,如下图所示。

通常,你会手动定义 Min、Max 和 Preferred Widths,要么在上方的约束设置中将其应用到所有层,要么在层网格中为每一层分别设置。对于受控阻抗布线,则改为启用 Use Impedance Profile 选项,然后从下拉列表中选择所需的 Impedance Profile。完成后,规则的 Constraints 区域会发生变化。你首先会注意到,可用层区域将不再显示板上的所有信号层,而只显示在所选 Impedance Profile 中启用的层。Preferred Width 数值(以及差分对间距)会更新,以反映为每一层计算得到的线宽(以及间距)。这些 Preferred 值不可编辑,但 Min 和 Max 值可以编辑。将它们设置为合适的更小/更大数值。随后即可按常规方式交互式布线这些网络。

走线宽度设计规则

对于单端网络,走线宽度由 Routing Width 设计规则定义。

当你选择 Use an Impedance Profile 时,可用层与 Preferred Width 由所选配置文件控制。

当你选择 Use an Impedance Profile 时,可用层与 Preferred Width 由所选配置文件控制。

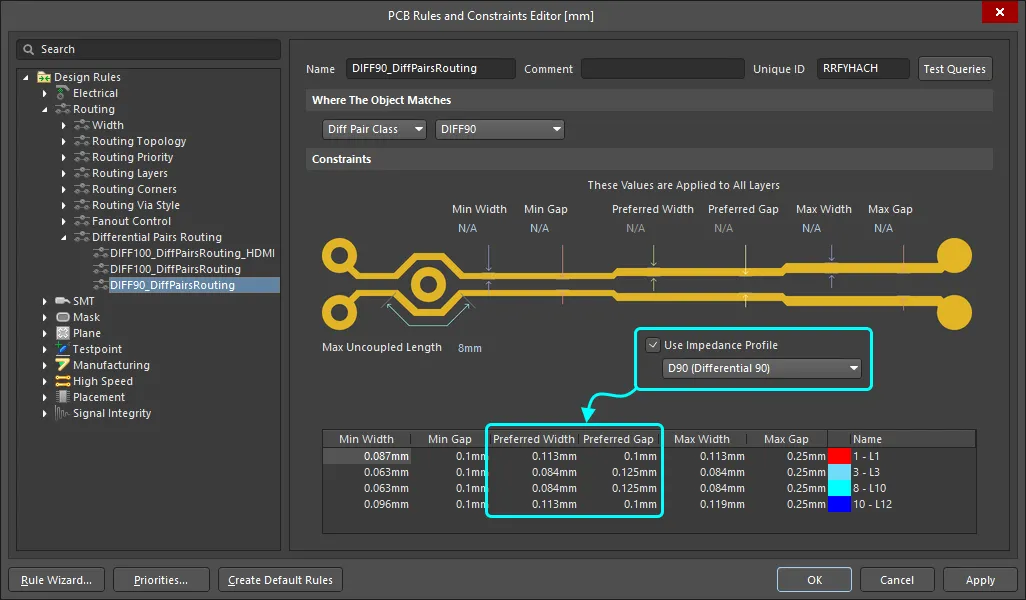

差分对布线设计规则

差分对的布线由 Differential Pair Routing 设计规则控制。

对于差分对,可用层、Preferred Width 和 Preferred Gap 由所选配置文件控制。

对于差分对,可用层、Preferred Width 和 Preferred Gap 由所选配置文件控制。

► 了解更多关于 Differential Pair Routing

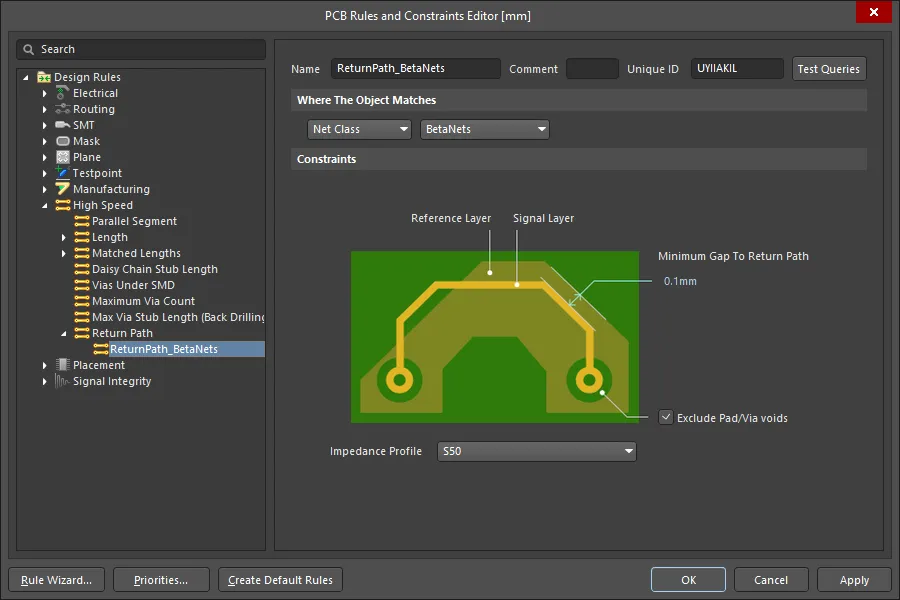

回流路径设计规则

回流路径中的断裂或颈缩可由 Return Path design rule 检测。Return Path 设计规则会检查:在规则所针对的信号上方或下方指定的参考层上,是否存在连续的信号回流路径。回流路径可由放置在参考信号层或平面层上的填充(fills)、区域(regions)和多边形覆铜(polygon pours)构成。

回流路径层是 Return Path 设计规则中所选 Impedance Profile 里定义的参考层。系统会检查这些层,以确保沿信号路径存在指定的 Minimum Gap(超出信号边缘的宽度)。在 High Speed 规则类别中添加一条新的 Return Path 设计规则。

回流路径层在所选 Impedance Profile 中定义,而路径宽度(超出信号边缘)由 Minimum Gap 定义。

回流路径层在所选 Impedance Profile 中定义,而路径宽度(超出信号边缘)由 Minimum Gap 定义。

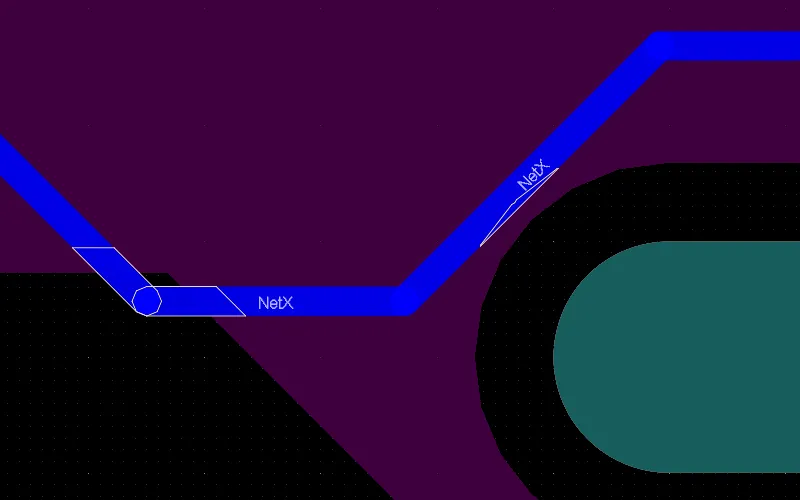

下图显示了为信号检测到的回流路径错误,NetX其 Minimum Gap 设置为 0.1mm。在 Preferences 对话框中,将 DRC Violation Display Style 配置为显示 Violation Details 但不显示 Violation Overlay(show image),会更容易定位 Return Path 错误。这样做会高亮规则失败的精确位置,而不是高亮整个违规对象。

► 了解更多关于 High Speed Design in Altium Designer

以所需阻抗布线网络

当你在布线并切换层时,软件会自动将线宽调整为实现指定阻抗所需的尺寸。这种交互式受控阻抗布线大大简化了受控阻抗 PCB 的设计工作。

走线长度调谐

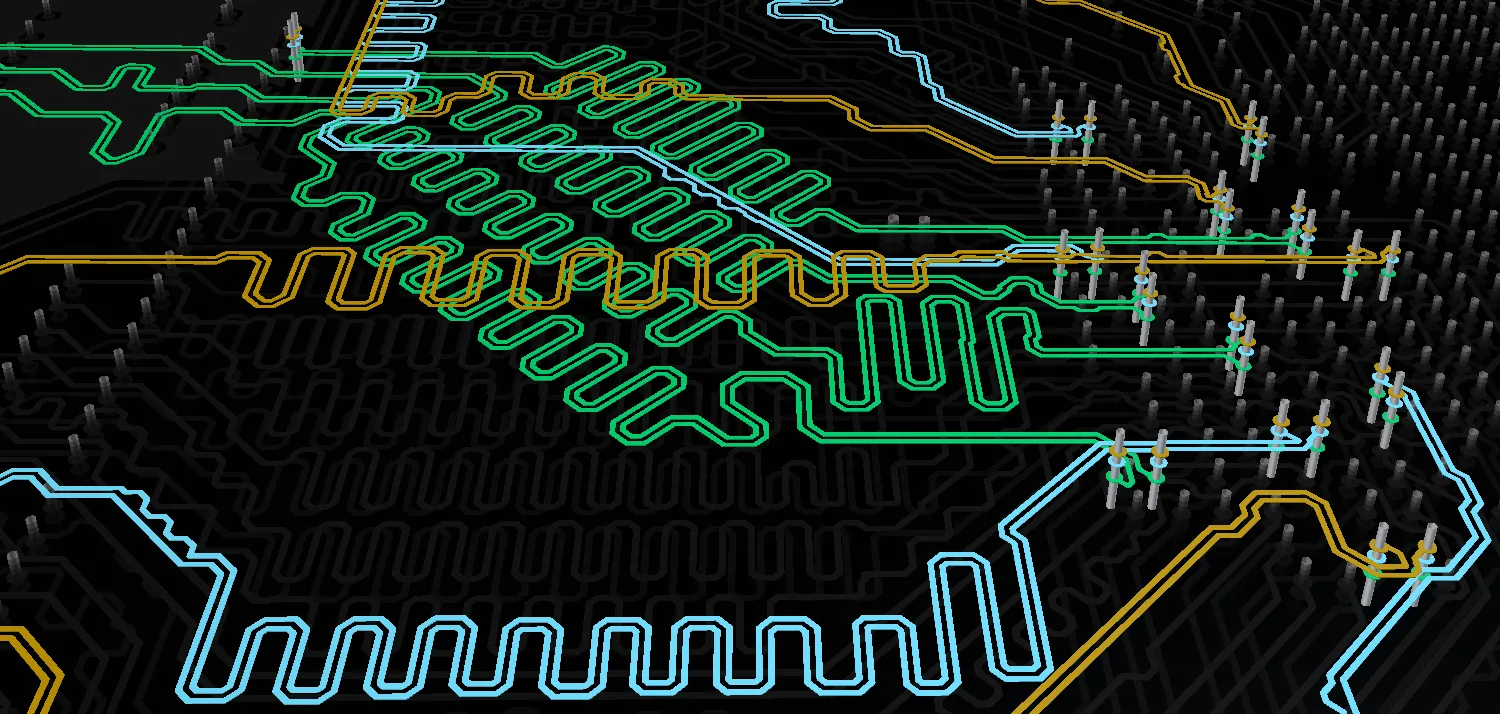

高速设计布线的两大核心挑战是:控制走线阻抗,以及匹配关键网络的长度。阻抗受控布线可确保从输出引脚发出的信号能被目标输入引脚正确接收。匹配走线长度可确保对时序敏感的信号同时到达目标引脚。对差分对布线而言,调谐与匹配走线长度同样是关键要素。

在布线中加入了手风琴(accordion)形状,以确保差分对长度匹配。

在布线中加入了手风琴(accordion)形状,以确保差分对长度匹配。

Interactive Length Tuning 和 Interactive Diff Pair Length Tuning 命令(Route 菜单)提供了一种动态方式来优化与控制网络或差分对长度:可根据设计中的可用空间、规则与障碍,插入可变振幅的波形(手风琴)。

► 了解更多关于 Length Tuning

测试已布线电路板的信号完整性

就像你在原理图设计阶段使用假设的走线长度与走线阻抗来测试网络一样,一旦布线完成,你也应在 PCB 上重复该过程,以检查潜在的阻抗不匹配与反射问题。从 PCB 编辑器的 Tools 菜单启动 Signal Integrity 命令。由于 PCB 是项目的一部分,将使用在 Layer Stack Manager 中定义的材料属性与尺寸,以及板上走线的实际宽度,来计算用于信号完整性测试的阻抗。

实现指定阻抗

除了为获得正确阻抗而进行的迭代尺寸调谐过程之外,还有其他因素会影响最终在成品 PCB 上实现的阻抗。这些因素包括:PCB 中所用介质材料的一致性与稳定性,以及蚀刻工艺的一致性与质量。如果你需要受控阻抗 PCB,应与 PCB 板厂沟通。有些板厂在你提供首选叠层(stackup)后,可以就走线几何形状给出建议。许多板厂还可以在其制作的每个拼板(panel)上加入阻抗测试条(impedance test coupon)——可用于测量板上实际实现的阻抗。

延伸阅读与资源

本文对信号完整性与受控阻抗 PCB 设计主题做了介绍。使用以下链接了解更多信息,并获取由业内公认专家开发的资源。

AI 翻译

AI 翻译