プリント基板上の接続を配線する作業は、複雑で時間のかかる工程です。 大規模または高密度の基板では、配線処理に設計者のかなりの時間を要することがあり、その点でオートルーターが役立ちます。

Altium Designer の Situs™ オートルーターは、基板空間をマッピングするためにトポロジー解析技術を使用します。これは、幾何学ベースまたは形状ベースのマッピングとは異なり、障害物の形状や座標に依存しません。トポロジカルマッピングにより、配線経路の決定においてより高い柔軟性と、制約のない配線方向が得られます。

Situs という名称は Situs Analysis に由来します。これは、通常は大きさや形状の変化の影響を受けない幾何学図形や立体の性質を研究する数学の一分野で、今日では一般にトポロジーとして知られています。

基板のオートルーティング

Situs Topological Router は、オートルーティングの課題に対して新しいアプローチをもたらします。まず高度なトポロジカルマッピングを用いて配線経路を定義し、その後、実績あるさまざまな配線アルゴリズムを呼び出して、この「人間らしい」経路を高品質な配線へと変換します。PCB Editor の統合機能として、PCB の電気ルールおよび配線ルール定義に従って動作します。

基板設定

Situs は設定と実行が簡単ですが、最適な配線結果を得るために注意すべき点がいくつかあります。

部品配置

最終的に、部品配置が配線性能に最も大きな影響を与えます。Altium Designer の PCB Editor には、動的に最適化される接続ラインなど、部品配置を微調整できる多数のツールが含まれています。最適な部品配置とは、接続ラインができるだけ短く、かつ「絡み合い」が最小限になっている状態です。

その他の優れた設計手法としては、パッドが規則的なグリッド上に並ぶように部品を配置すること(配線のためにパッド間の空きスペースを最大化するため)、両面基板では同程度のサイズの表面実装部品を正確に向かい合わせに配置すること、そしてデカップリング部品の配置ガイドラインについてデバイスメーカーのデータシートを参照することなどがあります。これは配置に関する考慮事項の完全な一覧ではなく、あくまでいくつかの提案です。

キープアウト

ルーターには、配置されたキープアウトオブジェクトで構成される閉じた境界が必要です。通常、この境界は基板外形に沿って設定されます。配置されたオブジェクトは、適用されるクリアランスルールに従って、この境界から適切な距離を保つため、設計上必要な機械的または電気的クリアランス要件を満たします。ルーターは、この外側境界内のキープアウトおよびレイヤー固有のキープアウトにも従います。

Line/Arc Primitives from Board Shape dialog を使用すると、基板外形に沿った閉じた境界を作成できます。キープアウトの詳細については、Object Specific Keepouts を参照してください。

ポリゴン注入

ポリゴン(または銅箔)注入は、ソリッド型(1つ以上の銅領域で塗りつぶされる)またはハッチ型(トラックとアークで構成される)のいずれかです。中規模から大規模のハッチ型ポリゴン注入には、多数のトラックとアークが含まれます。ルーターはそのようなポリゴン注入を含む基板でも配線できますが、それらが追加するオブジェクト数が非常に多いため、配線処理の複雑さが増します。

通常、配線前にポリゴン注入を配置するのは、それが必要な場合のみにすべきです。たとえば、特殊な形状の事前配線、商用電源入力の配線、あるいは重要なグラウンド領域の構築に使用する場合です。それ以外では、配線完了後にポリゴン注入を設計へ追加する方が望ましいです。

配線可能か?

オートルーターとは、人間が配線プロセスを理解してモデル化し、そのプロセスを自動的に再現しようとする試みです。基板内に手作業でも配線できない領域がある場合、オートルーティングでも配線できません。ルーターが特定の部品や基板の一部分で繰り返し失敗する場合は、対話配線を試してください。配置やルール設定に問題があり、そもそも配線不可能になっている可能性があります。

事前配線

重要なネットは事前に配線し、配線処理によって変更されては困る場合は、Lock All Pre-routes オプションを Situs Routing Strategies dialog で有効にしてロックしてください。ただし、不必要なロックは避けてください。ロックされたオブジェクトが多いと、配線問題がはるかに難しくなります。

差動ペアネットは、オートルーターを使用する前に手動で配線してロックしておく必要があります。そうしないと、配線が変更されて差動ペアの信号整合性が損なわれる可能性が非常に高くなります。

設計ルールの設定

default rule という用語は、クエリスコープが All のルールを表すために使用されます。

ルールに Minimum、Preferred、Maximum の値が含まれている場合、オートルーターは Preferred 値を使用します。

使用している基板技術に対して、配線設計ルールが適切であることを確認してください。対象が不適切または不適切な設計ルールは、オートルーティング性能を大きく低下させる可能性があります。なお、ルーターは Routing Corners ルールを除くすべての Electrical および Routing 設計ルールに従います。

ルールは PCB Rules and Constraints Editor dialog(Design » Rules)で定義され、このダイアログには Situs Routing Strategies dialog から直接アクセスできます。

ルールに Minimum、Preferred、Maximum の値が含まれている場合、オートルーターは Preferred 値を使用します。

Altium Designer のルールシステムは階層構造になっています。基本的な考え方は、まずすべてのオブジェクトに対するデフォルトルールを作成し、その後、異なる要件を持つ他のオブジェクトを選択的に対象とする追加ルールを加えることです。たとえば、配線幅については、基板上で最も一般的に使用される配線幅を対象とするデフォルトルールを用意し、その後で他のネットやネットクラスなどを選択的に対象とするルールを追加します。

ルールが正しいオブジェクトを対象としているか確認するには、そのルールの Query を PCB Filter panel にコピーして Apply します。ルールの対象となるオブジェクトだけがフィルターを通過し、完全な強度で表示されたままになります。あるいは、PCB Rules And Violations panel を使用して、現在の基板で定義されている任意のルールに対するルール適用状況をすばやく確認できます。

最も重要なルールは、Width ルールと Clearance ルールです。これらの配線技術設定は、配線をどれだけ高密度に「詰め込める」かを定義します。これらの選定はバランス作業です。トラック幅が広くクリアランスが大きいほど基板は製造しやすくなりますが、一方でトラック幅とクリアランスが狭いほど基板は配線しやすくなります。配線幅やクリアランスについて、どの値を下回ると製造歩留まりが低下し PCB 価格が上昇するかという、製造業者の「価格ポイント」を確認するために、製造業者へ相談することを推奨します。設計の電気的要件を満たすだけでなく、各ピンへ配線できるように、配線技術は部品技術にも適合するよう選定する必要があります。

配線技術の一部を成す3つ目のルールは、Routing Via Style です。これも、使用するトラック幅とクリアランスに適合するよう選定しつつ、選択した穴径とアニュラリングによる製造コストも考慮する必要があります。

また、過剰または不要なルールは避けるべきです。ルールが多いほど処理時間が増え、配線速度が低下します。オートルーティングに不要なルールは無効化できます。

配線幅

Width rule が存在し、その Query が All(デフォルトルール)であること、さらに Preferred 設定が最も一般的に必要となる配線幅に適していることを確認してください。この幅が、適切なクリアランスルールとの組み合わせで、すべてのパッドへ配線可能であることも確認してください。より広いまたは狭い配線幅を必要とするネットについては、追加の配線幅ルールを設定します。

ファインピッチ部品があり、そのピンがより広い配線幅のネット、たとえば電源ネットに接続されている場合は、電源ピンからの引き出し配線を試し、さらにその両隣のピンからの引き出し配線も行って、これらのピンが物理的に配線可能であることを確認してください。

クリアランス制約

標準的な基板クリアランスよりもパッド間隔が狭いファインピッチ部品など、特別なクリアランス要件がないか確認してください。これらには、適切なスコープと優先順位を持つ設計ルールで対応できます。なお、フットプリントを対象とするルールを定義することはできますが、そのフットプリントに接続される配線自体は対象になりません。先に配線幅のセクションで述べたように、部品ピンが配線可能であることを確認するために試験配線を行ってください。

Routing Via Style

Routing Via Style rule が存在し、その Query が All であり、Preferred 設定が適切であることを確認してください。デフォルトルールとは異なるビアスタイルを必要とするネットについては、より高い優先順位のルールを含めてください。

Altium Designer はブラインドビアおよびベリードビアをサポートしており、これらを使用するかどうかは、Layer Stack Manager(Design » Layer Stack Manager)で定義された Via Types によって許可されるレイヤースワップで決まります。対話配線と同様に、オートルーターが2つのレイヤー間を切り替える際には、現在の Via Type 定義を確認します。これらのレイヤーがブラインドまたはベリードのレイヤーペアとして定義されている場合、配置されるビアはそれらのレイヤーを開始層および終了層として持ちます。ブラインド/ベリードビアの使用制約を理解することが重要です。これらは製造業者と相談のうえでのみ使用すべきです。製造スタックアップ技術による制約に加えて、信頼性やテストアクセス性の考慮事項もあります。設計者によっては、ブラインド/ベリードビアを使用するよりも、配線層を増やす方がよいと考える場合もあります。

配線レイヤー

Routing Layers rule が存在し、その Query が All であることを確認してください。有効なすべての信号レイヤー(レイヤースタックで定義)は一覧表示されます。必要に応じて、配線を許可したいレイヤーを有効にしてください。特定のレイヤーのみに配線したいネットについては、より高い優先順位のルールを含めてください。

特定のネット(またはネットクラス)をオートルーターによる配線対象から除外したい場合は、そのネットまたはネットクラスを対象とする Routing Layer ルールを定義し、そのルールの Constraints 領域で、有効な各信号レイヤーに対する Allow Routing オプションが無効になっていることを確認してください。このルールの優先順位は、デフォルトルール(Query が All のもの)より高くなければなりません。

レイヤ方向

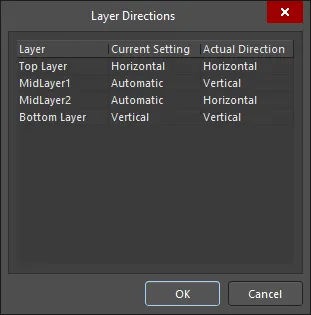

Layer Directionsダイアログでは、推奨配線方向を指定します。このダイアログには、Situs Routing Strategies dialog からアクセスします。すべての有効な信号レイヤ(レイヤスタックで定義)が一覧表示されます。

接続ラインの流れに合う適切なレイヤ方向を選択してください。Situs は配線経路の定義にトポロジカルマッピングを使用するため、水平方向および垂直方向の配線に制約されません。通常、外層は水平と垂直に設定するのが最適です。ただし、多層基板で「2時方向」の角度を持つ接続が多数ある場合は、1つ以上の内部レイヤの推奨配線方向をその角度に設定してください。特に Layer Patterns パスではこの情報が活用されるため、適切な方向を選ぶことで、時間と品質の両面で配線性能が大きく向上することがあります。なお、角度付きレイヤを使用する場合、そのレイヤに対して 90 度のパートナーレイヤを用意する必要はありません。ルータは通常、角度付きレイヤ上で障害物を回避する必要がある場合、水平方向または垂直方向に配線するためです。

Any 方向の使用は避けてください。接続をどのレイヤで配線するかは、その接続がレイヤ方向とどれだけ一致しているかに基づいて決まるため、このレイヤは最後の手段として使われるレイヤになります。Any 方向は通常、片面基板でのみ使用されます。

Layer Directionsダイアログ

Options and Controls of the Layer Directions Dialog

このダイアログには、レイヤスタックで定義された各信号レイヤを一覧表示するグリッドがあります。各レイヤについて、次の項目が表示されます。

-

Layer - 信号レイヤの名前。

-

Current Setting - 現在選択されている、そのレイヤの推奨配線方向。このフィールドは編集可能です。ドロップダウンから次のオプションを選択します: Not Used、Horizontal、Vertical、Any、1 O'Clock、2 O'Clock、4 O'Clock、5 O'Clock、45 Up、45 Down、Fan Out、Automatic。

-

Actual Direction - Situs が実際に使用している配線方向。このフィールドは読み取り専用です。通常は Current Setting フィールドでそのレイヤに対して選択された推奨配線方向に従いますが、Automatic が選択されている場合は、他のレイヤに定義された配線方向に基づいて、使用すべき最適な方向が計算されます。

配線優先度

Routing Priority rules を使用して、配線が難しいネットや、できるだけクリーンに配線したいネットに高い優先度を設定します。

SMD ファンアウト制御

クエリシステムには、IsLCC(Leadless Chip Carrier)、IsSOIC(Small Outline IC)、IsBGA(Ball Grid Array)など、さまざまな表面実装部品パッケージを特定するためのキーワードが含まれています。最も一般的なパッケージについてはデフォルトルールが自動作成され、ファンアウトパスは自動配線プロセスの早い段階で実行されるため、どの部品にも適用されないルールを残しておいてもほとんど不利益はありません。基板上に表面実装部品がある場合は、少なくとも 1 つの SMD ファンアウト制御デザインルールを設定する必要があります。すべての表面実装部品を対象とする単一ルールに適したクエリは IsSMTComponent です。各クエリキーワードがどのように部品パッケージを識別するかについては、Query Helper を開き、必要なキーワードを入力して F1 を押してください。

ファンアウトルールには、パッドを内向きにファンアウトするか、外向きにファンアウトするか、あるいはその両方を混在させるかを制御する設定が含まれています。Fanout Control ルール属性の動作に慣れるために、Route » Fanout » Component コマンドを、ネットが割り当てられていない任意の表面実装部品に対して実行できます。これにより、基板で現在定義されている配線テクノロジでその部品がどの程度うまくファンアウトできるかを確認できるだけでなく、ライブラリに事前ファンアウト済みフットプリントとして保持したい部品をファンアウトする用途にも使えます。PCB ワークスペースでファンアウトした後、部品とファンアウト配線およびビアをライブラリにコピー&ペーストしてください。

ルール優先度

ルールの優先順位は、優先度とも呼ばれ、設計者が定義します。ルール優先度は、あるオブジェクトが複数のルールの対象になっている場合に、どのルールを適用するかを決定するために使用されます。優先度が正しく設定されていないと、ルールがまったく適用されないことがあります。

たとえば、InNet('VCC') というクエリを持つルールの優先度が、All というクエリを持つルールより低い場合、VCC ネットには All ルールが適用されます。優先度を必要に応じて調整するには、PCB Rules and Constraints Editor dialog の Priorities ボタンを使用して、Edit Rule Priorities dialog にアクセスします。なお、2 つのルールスコープが重複しない(同じオブジェクトを対象にしない)場合、優先度は重要ではありません。たとえば、InNet('VCC') と InNet('GND') のどちらのルールスコープの優先度が高くても違いはありません。

黄金律

最も重要なステップは、自動配線を開始する前にデザインルールチェック(DRC)を実行することです。Route » Auto Route » Setup または Route » Auto Route » All コマンドを使用すると、Situs は独自の事前配線解析を実行し、その結果を Situs Routing Strategies dialog にレポートとして表示します。ダイアログから、その設計に対するレポートを確認し、配線時に使用するストラテジを選択できます。配線ストラテジはルータの知能に相当し、トポロジカルマップで特定された「仮想」配線経路を、基板上の高品質かつ高効率な実際の配線へ変換するために、さまざまな配線アルゴリズムのどれをいつ使用するかを定義します。

自動配線を開始する前に、Routing Setup Report に問題がないことを確認してください。

自動配線を開始する前に、Routing Setup Report に問題がないことを確認してください。

このレポートには、次のような情報が含まれます。

-

現在その設計に定義されており、自動配線で順守されるデザインルール(および各ルールの影響を受けるデザインオブジェクト数 - ネット、部品、パッド)

-

すべての信号配線レイヤに定義された配線方向

-

ドリルレイヤペアの定義

このレポートには、ルータ性能に影響する可能性のある問題点が一覧表示されます。可能な場合は、自動配線に向けて設計をより適切に準備するためのヒントも提示されます。表示されたエラー/警告/ヒントはすべて精査し、必要に応じて対応する配線ルールを調整してから、設計の配線に進んでください。

すべてのエラー、警告、ヒントを確認し、自動配線が直面する可能性のある問題を把握してください。

すべてのエラー、警告、ヒントを確認し、自動配線が直面する可能性のある問題を把握してください。

配線関連のルール違反は、自動配線を開始する前に必ず解消しておくことが重要です。違反があると、その場所で配線できなくなるだけでなく、配線不能な領域への配線をルータが繰り返し試みるため、処理速度が大幅に低下することがあります。

Situs AutoRouter 実行時の注意

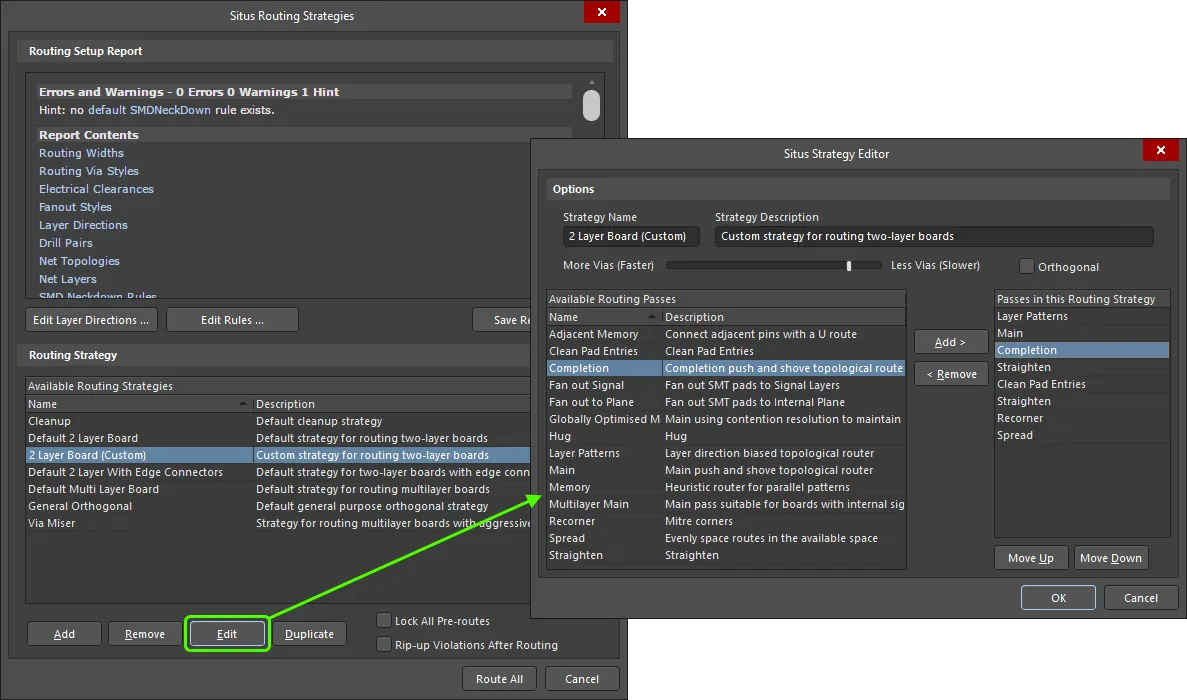

配線パスと配線ストラテジーの概要

現在定義されている配線ストラテジーは、Situs Routing Strategiesダイアログの下部領域に一覧表示されます。Addボタンをクリックすると、Situs Strategy Editorダイアログにアクセスでき、そこで新しいストラテジーに含めるパスを指定できます。あるいは、Duplicateボタンを使用して既存のストラテジーを複製し、必要に応じて編集することもできます。さまざまな配線パスをどのように含め、どの順序で使用するかが Autorouter の「知能」を構成します。これらのパスは、トポロジカルマップで特定された仮想配線経路を、ボード上の高品質な配線へと変換するために使用されます。

定義された配線ストラテジーと、それに含まれる各配線パスは、ボード全体を配線する場合にのみ適用されます。

複製したストラテジーを編集している例。

Options and Controls of the Situs Routing Strategies Dialog

このダイアログのコントロールは、2 つの主要な領域に分かれています。2 つのアクセス方法の間でコントロールにある唯一の違いは、ダイアログ下部の Cancel ボタンの左側にあるボタンです。設定のみを行うためにアクセスした場合(配線は行わない場合)、ここには標準の OK ボタンが表示されます。これをクリックすると、ユーザー定義の配線ストラテジーへの変更が保存されます。ボード全体を配線するためにアクセスした場合は、Route All ボタンが表示されます。これをクリックすると、現在選択されている配線ストラテジーに従ってボードの配線が試行されます。

配線設定レポート

-

Report Window - この領域には、設計の配線前解析に基づくレポートが表示されます。ここには、Autorouter が順守する設計上の現在のデザインルール(および各ルールの影響を受けるデザインオブジェクト - ネット、コンポーネント、パッド - の数)、すべての信号配線レイヤーに定義された配線方向、ドリルレイヤーペア定義などの情報がまとめられます。

このレポートには、ルーターの性能に影響を与える可能性のある問題が一覧表示されます。これらの警告には、配線方向が Any に設定されている配線レイヤーが含まれる場合があります。可能な場合は、自動配線に向けて設計をより適切に準備できるよう、ヒントも提供されます。一覧表示されたエラー、警告、ヒントはすべて精査し、必要に応じて対応する配線ルールを調整してから設計の配線に進む必要があります。

Autorouter を開始する前に、配線関連のルール違反をすべて解消しておくことが不可欠です。違反があると、その場所で配線できなくなるだけでなく、配線不可能な領域への配線を Autorouter が繰り返し試みるため、処理速度が大幅に低下することがあります。

レポート内のハイパーリンク項目を使用すると、特定のルール定義に対応する Edit PCB Ruleダイアログにすばやくアクセスし、そのルールの適用範囲や制約を必要に応じて調整できます。配線不能なパッドについては、レポート内の該当するハイパーリンク項目をクリックすると、デザインスペース内で問題のあるパッドをズームして中央表示します。

-

Edit Layer Directions - このボタンをクリックすると、Layer Directions dialog にアクセスでき、そこで必要に応じて信号レイヤーの配線方向を変更できます。

-

Edit Rules - このボタンをクリックすると、メインの PCB Rules and Constraints Editor dialog にアクセスできます。あるいは、既存の配線ルールを直接変更したい場合は、レポート本文内にあるそのルールのハイパーリンクをクリックしてください。

-

Save Report As - このボタンをクリックすると、レポートを HTML ドキュメントとして保存できます。標準の Save As ダイアログが表示されます。デフォルトでは、レポートは PCB 設計ファイル(DesignName.htm)と同じ場所に、同じ名前で保存されます。必要に応じて、このダイアログで名前と保存場所を変更してください。

配線ストラテジー

-

Available Routing Strategies - この領域には、Autorouter が設計を配線するために使用できる現在利用可能なすべての配線ストラテジーが一覧表示されます。各ストラテジーは、その名前と説明とともに表示されます。以下の 6 つの配線ストラテジーが定義されており、デフォルトで利用可能です。

-

Cleanup - デフォルトのクリーンアップストラテジー。

-

Default 2 Layer Board - 2 層基板を配線するためのデフォルトストラテジー。

-

Default 2 Layer With Edge Connectors - エッジコネクタ付き 2 層基板を配線するためのデフォルトストラテジー。

-

Default Multi Layer Board - 多層基板を配線するためのデフォルトストラテジー。

-

General Orthogonal - デフォルトの汎用直交ストラテジー。

-

Via Miser - ビア最小化を積極的に行う多層基板向けのデフォルトストラテジー。

一般に、2 層基板および多層基板向けのデフォルト配線ストラテジーは、ほとんどの配線状況で十分に機能します。ただし、Autorouter を実行する前に、関連する配線設計ルールが適切に設定されていることを確認することが重要です。

-

Add - このボタンをクリックすると、新しいユーザー定義の配線ストラテジーを一覧に追加します。Situs Strategy Editorダイアログが開き、そこでストラテジーを完全に定義できます。特に重要なのは、それを構成する各配線パスです。

-

Remove - このボタンをクリックすると、現在選択されているユーザー定義の配線ストラテジーを、利用可能な配線ストラテジーの一覧から削除します。

デフォルトの 6 つの配線ストラテジーは削除できません。

-

Edit - このボタンをクリックすると、現在選択されているユーザー定義の配線ストラテジーを編集します。Situs Strategy Editorダイアログが開き、必要に応じて、その構成配線パスを含むストラテジーの変更を行えます。

デフォルトの 6 つの配線ストラテジーは編集できません。

-

Duplicate - このボタンをクリックすると、現在選択されている配線ストラテジーの複製を作成します。Situs Strategy Editorダイアログが開きます。新しいストラテジーに、より意味のある独自の名前と説明を付け、必要に応じて設定を変更してください。

-

Lock All Pre-routes - このオプションを有効にすると、事前配線済みのネットが Autorouter によって削除(「リップアップ」)されて再配線されるのを防ぎます。多くの場合、特定のネットは手動で配線し、その後残りを自動配線します。

-

Rip-up Violations After Routing - このオプションを有効にすると、Autorouter の配線セッション完了後に、定義済みかつ適用対象のデザインルールに違反している配線がリップアップされます。

Situs Strategy Editor ダイアログのオプションとコントロール

オプション

-

Strategy Name - 現在のストラテジの名前です。新しい配線ストラテジを作成する場合、このフィールドにはデフォルトのエントリ New Strategy が表示されます。必要に応じて、このフィールドを編集してより意味のある名前を付けてください。

-

Strategy Description - 現在のストラテジの説明です。ストラテジの目的または適用範囲を要約した、わかりやすい説明を入力してください。

-

More/Less Vias - このスライダーバーを使用して、Autorouter によるビア使用の許容度を定義します。これは、より高速な配線と、より少ないビア使用とのトレードオフです。バーを右に動かすと、Autorouter は配置するビア数を少なくするよう制約されますが、基板の配線にかかる時間は長くなります。バーを左に動かすと、配線完了時間は短くなりますが、その代わり PCB 上に Autorouter が配置するビア数は増えます。

-

Orthogonal - このオプションを有効にすると、Autorouter は直交(90°)パスのみで配線するよう制約されます。このオプションを無効にすると、Autorouter は必要に応じて直交または非直交(45°)で配線できます。

Routing Passes

-

Available Routing Passes - この領域には、配線ストラテジで使用できる配線パス(アルゴリズム)が一覧表示されます。使用可能なパスは次のとおりです。

-

Adjacent Memory - これは接続レベルの配線パスです。単純な U 字パターンでファンアウトが必要な、隣接する同一ネットのピンを配線するために使用されます。

-

Clean Pad Entries - これは接続レベルの配線パスです。各パッドの中心から、パッドの長軸に沿って再配線します。

X 寸法と Y 寸法が異なるパッドを持つコンポーネントを含む設計では、必ず Clean Pad Entries パスを Memory パスの後に含めてください。

-

Completion - これは接続レベルの配線パスです。本質的には Main パスと同じですが、競合を解消して難しい接続を完了するために、異なるコスト設定がされています。コスト設定の違いの例としては、ビアがより低コストで、逆方向配線がより高コストになることが挙げられます。

-

Fan out Signal - これはコンポーネントレベルのパスで、Fanout Control で定義されたファンアウト設定に基づきます。パッドのパターンを確認し、クリアランス、配線幅、ビアスタイルを考慮したうえで、設計ルールで定義された要件を満たす適切なファンアウト配置(インライン列、千鳥配置など)を選択します。ファンアウト先はシグナル層のみです。

-

Fan out to Plane - これはコンポーネントレベルのパスで、Fanout Control で定義されたファンアウト設定に基づきます。パッドのパターンを確認し、クリアランス、配線幅、ビアスタイルを考慮したうえで、設計ルールで定義された要件を満たす適切なファンアウト配置(インライン列、千鳥配置など)を選択します。ファンアウト先は内部プレーン層のみです。

-

Globally Optimised Main - これは接続レベルの配線パスです。最適な配線を提供します。最初の反復では競合/違反を無視します。その後、違反がなくなるまで、競合コストを増加させながら接続を再配線します。このパスは、Orthogonal オプションを有効にして併用すると、見栄えのよい配線パターンを生成できます。角を留め加工した形状にするには、ストラテジに Recorner パスを追加してください。

-

Hug - これは接続レベルの配線パスで、可能な最小クリアランスで既存配線に沿うように各接続を再配線します。Hug パスは、利用可能な配線スペースを最大化するために使用されます。なお、このパスは非常に低速です。

-

Layer Patterns - これは接続レベルの配線パスです。層方向に一致する接続のみを(許容範囲内で)配線します。空きスペースを最大化するため、既存配線に密着または追従するようなコスト設定になっています。

-

Main - これは接続レベルの配線パスです。トポロジカルマップを使用して配線経路を見つけ、その後 push and shove router を使用して提案経路を実際の配線に変換します。

-

Memory - これは接続レベルの配線パスです。同じ層上にあり、X 座標または Y 座標を共有する、異なるコンポーネント上の 2 つのピンをチェックします。

-

Multilayer Main - これは接続レベルの配線パスです。Main パスに似ていますが、多層基板向けにコストが最適化されています。

-

Recorner - これは接続レベルの配線パスで、配線されたコーナーを留め加工するために使用されます。このパスは、ストラテジで Orthogonal オプションが有効な場合に使用され、実質的にその設定を上書きして各配線のコーナーを留め加工します。使用中のストラテジで Orthogonal オプションが無効な場合は、autorouter がデフォルトでコーナーを留め加工するため、Recorner パスを含める必要はありません。

-

Spread - これは接続レベルの配線パスで、各接続を再配線し、空きスペースを使うように配線を広げ、固定オブジェクト(コンポーネントのパッドなど)の間を通過する際に配線間隔が均等になるよう試みます。なお、このパスは非常に低速です。

-

Straighten - これは接続レベルの配線パスで、コーナー数の削減を試みます。これを行うために、配線に沿ってコーナーまでたどり、そのコーナーから(水平/垂直/45up/45down)のプローブを実行して、同じネット上の別の配線済みポイントを探索します。見つかった場合、その新しい経路によって配線長が短縮されるかどうかを確認します。

配線ストラテジには、メインタイプのパスを 1 つだけ指定する必要があります。つまり、Main、Multilayer Main、Globally Optimized Main のいずれか 1 つです。

-

Passes in this Routing Strategy - この領域には、ストラテジに含まれる実際の配線パス(アルゴリズム)が一覧表示されます。使用可能なパスの一覧から任意のパスを追加でき、特定の結果を得るために同じパスをストラテジ全体の中で複数回追加することもできます。パスは上から順に実行されます。この順序は Move Up ボタンと Move Down ボタンを使用して変更できます。

-

Add - このボタンをクリックすると、Available Routing Passes リストで現在選択されているパスを Passes in this Routing Strategy リストに追加します。パスは後者で現在選択されているパスの上に追加されます。

-

Remove - このボタンをクリックすると、Passes in this Routing Strategy リストで現在選択されているパスをストラテジから削除します。

-

Move Up - このボタンをクリックすると、Passes in this Routing Strategy リストで現在選択されているパスをリスト内で上へ移動します。つまり、配線ストラテジ内でより早い段階で使用されます。

-

Move Down - このボタンをクリックすると、Passes in this Routing Strategy リストで現在選択されているパスをリスト内で下へ移動します。つまり、配線ストラテジ内でより後の段階で使用されます。

ユーザー定義ストラテジはいつでも編集できますが、デフォルトのストラテジ - Cleanup, Default 2 Layer Board, Default 2 Layer With Edge Connectors, Default Multi Layer Board, General Orthogonal, Via Miser - は変更できません。

以下の配線パスを使用できます。パスは任意の順序で使用できますが、ガイドとして既存のストラテジを確認し、パスの順序を参照してください。

| パス |

機能 |

| Adjacent Memory |

接続レベルの配線パスです。単純な U 字パターンでファンアウトが必要な、隣接する同一ネットのピンを配線するために使用されます。 |

| Clean Pad Entries |

接続レベルの配線パスです。各パッドの中心から、パッドの長軸に沿って再配線します。X 寸法と Y 寸法が異なるパッドを持つコンポーネントがある場合は、必ず Memory パスの後に Clean Pad Entries パスを含めてください。 |

| Completion |

接続レベルの配線パスです。本質的には Main パスと同じですが、競合を解消して難しい接続を完了するために、異なるコスト設定がされています。コスト設定の違いの例としては、ビアがより低コストで、逆方向配線がより高コストになることが挙げられます。 |

| Fan Out Signal |

コンポーネントレベルのパスで、Fanout Control で定義されたファンアウト設定に基づきます。パッドのパターンを確認し、クリアランス、配線幅、ビアスタイルを考慮したうえで、設計ルールで定義された要件を満たす適切なファンアウト配置(インライン列、千鳥配置など)を選択します。ファンアウト先はシグナル層のみです。 |

| Fan out to Plane |

コンポーネントレベルのパスで、Fanout Control で定義されたファンアウト設定に基づきます。パッドのパターンを確認し、クリアランス、配線幅、ビアスタイルを考慮したうえで、設計ルールで定義された要件を満たす適切なファンアウト配置(インライン列、千鳥配置など)を選択します。ファンアウト先は内部プレーン層のみです。 |

| Globally Optimized Main |

接続レベルの配線パスです。最適な配線を提供します。最初の反復では競合/違反を無視します。その後、違反がなくなるまで、競合コストを増加させながら接続を再配線します。このパスは、Orthogonal オプションを有効にして併用すると、見栄えのよい配線パターンを生成できます。角を留め加工した形状にするには、ストラテジに Recorner パスを追加してください。 |

| Hug |

接続レベルの配線パスで、可能な最小クリアランスで既存配線に沿うように各接続を再配線します。Hug パスは、利用可能な配線スペースを最大化するために使用されます。なお、このパスは非常に低速です。 |

| Layer Patterns |

接続レベルの配線パスです。層方向に一致する接続のみを(許容範囲内で)配線します。空きスペースを最大化するため、既存配線に密着または追従するようなコスト設定になっています。 |

| Main |

接続レベルの配線パスです。トポロジカルマップを使用して配線経路を見つけ、その後 push and shove router を使用して提案経路を実際の配線に変換します。配線ストラテジには、メインタイプのパスを 1 つだけ指定する必要があります。つまり、Main、Multilayer Main、または Globally Optimized Main のいずれか 1 つです。 |

| Memory |

接続レベルの配線パスです。同じ層上にあり、X 座標または Y 座標を共有する、異なるコンポーネント上の 2 つのピンをチェックします。 |

| Multilayer Main |

接続レベルの配線パスです。Main パスに似ていますが、多層基板向けにコストが最適化されています。 |

| Recorner |

配線済みコーナーを面取りするために使用される、接続レベルの配線パスです。このパスは、ストラテジーで Orthogonal オプションが有効になっている場合に使用されます。つまり、その設定を実質的に上書きして、各配線のコーナーを面取りします。使用中のストラテジーで Orthogonal オプションが無効になっている場合は、autorouter がデフォルトでコーナーを面取りするため、Recorner パスを含める必要はありません。 |

| Spread |

各接続を再配線し、空きスペースを活用して配線を広げ、固定オブジェクト(部品パッドなど)の間を通過する際に配線間隔を均等にしようとする、接続レベルの配線パスです。このパスは非常に低速である点に注意してください。 |

| Straighten |

コーナー数の削減を試みる、接続レベルの配線パスです。これは、配線に沿ってコーナーまでたどり、そのコーナーから(水平/垂直/45度上/45度下)のプローブを実行して、同じネット上の別の配線済みポイントを探索することで行われます。見つかった場合は、この新しい経路によって配線長が短くなるかどうかを確認します。 |

関連項目