デバイスのスイッチング速度が高まるにつれて、制御インピーダンス配線はデジタル設計者にとって重要なテーマとなっています。このページでは、Signal Integrity解析エンジンを使用してコンポーネントのインピーダンスを整合させる方法と、PCBエディタにおける制御インピーダンス配線機能について紹介します。

エンジニアリングの世界では、こんな言い方があります。デジタル設計に携わる電子技術者には2種類しかいない――シグナルインテグリティの問題をすでに経験した人と、これから経験する人です。ほんの数年前までは、シグナルインテグリティという言葉は専門家向けのものであり、高速設計でのみ対処すればよいものでした。しかし、そうした高速設計で使われていたデバイスのスイッチング速度は、もはや特別なものではありません。急速に標準になりつつあります。集積回路技術の進歩によってトランジスタのサイズが小さくなるにつれ、スイッチング速度は上がっていきます。そして、このスイッチング速度こそがデジタル信号の完全性に影響を与えるのです。

幸いなことに、設計の基本原則に従い、設計を制御インピーダンス基板として実装することで、多くの潜在的なシグナルインテグリティ問題は回避できます。これを実現するには、特定の設計ツール機能が必要です。リンギングや反射の問題が起こり得るネットを検出する解析ツールと、適切な配線インピーダンスを実現できる基板設計ツールが必要になります。Altium Designer のPCBエディタには、これらの機能が備わっています。

このページでは、シグナルインテグリティ問題の原因と、基板がその影響を受ける可能性が高いかどうかを理解できるようにします。また、潜在的なSI問題を最小限に抑えるために必要な2つの設計アプローチ――コンポーネントのインピーダンス整合と、制御インピーダンス配線――についても説明します。

Controlled Impedance Routing:必要な配線インピーダンスを実現するために、配線幅やクリアランス、材料特性、寸法を設定します。

配線が回路の一部になるとき

デバイスのスイッチング速度が上がるにつれて、プリント基板設計者と製造業者に求められるものも増えていきます。信号のスイッチングエッジの長さが、それを伝送するPCBトレースの長さより短くなると、そのトレースは回路の一部として扱う必要があります。そのトレースはインピーダンスを持ち、これはcharacteristic impedance (Zo)と呼ばれます。

これらの追加的な回路要素の影響を管理する最善の方法は、特性インピーダンスが全長にわたって一定になるようにトレース配線を設計することです。この手法はcontrolled impedance routingと呼ばれます。

トレース配線のインピーダンスは、次の要素によって決まります。

-

Cross-sectional area of the trace - 幅、高さ(銅厚)、およびエッチング工程で形成されるトレース側面の傾斜によって決まります。

-

Distance from the trace to the reference plane(s) - 信号エネルギーのリターンパスは、信号そのものの経路と同じくらい重要です。このリターンパスは、隣接する基準プレーン上で信号経路に沿って流れます。

-

Properties of the surrounding materials - 信号のエネルギーはトレースの銅の中だけに存在するわけではありません。表皮効果により、トレースを取り囲む誘電体材料の中も伝わります。誘電体材料の誘電率は、その誘電体がそのエネルギーの流れにどの程度影響するかを示します。

Simbeorインピーダンス計算機は、指定したインピーダンスを実現するために必要な幅を計算します。

制御インピーダンス配線は必要か?

制御インピーダンス配線に本当に気を配る必要があるのか、と思うかもしれません。

理想的な状況では、コンポーネントの出力ピンから出たエネルギーはすべてPCB上の接続トラックに結合され、PCB配線を通って反対側の負荷入力ピンへ流れ、その負荷に吸収されます。もしエネルギーのすべてが負荷に吸収されなければ、残ったエネルギーはPCB配線内に反射して戻り、ソース出力ピンへ向かって流れる可能性があります。この反射エネルギーは元の信号と相互作用し、極性に応じて信号に加算または減算され、リンギングを引き起こします。リンギングが十分に大きい場合、信号の完全性に影響し、予測不能で誤った回路動作を招くことがあります。

では、これが起こる可能性があるかどうかは、どう判断すればよいのでしょうか。ソースピンが、信号が負荷ピンに到達する前にエッジ遷移を完了できる場合、設計が反射エネルギーの影響を受ける条件がそろっています。SI問題が起こりやすいかどうかを判断するためによく使われる経験則に、「立ち上がり時間の1/3ルール」があります。このルールでは、トレース長が立ち上がり時間に相当する長さの1/3を超えると、反射(リンギング)が発生し得るとされます。ソースピンの立ち上がり時間が1nSecであれば、0.33nSecを超える配線長(FR4で約2インチ)は伝送線路として扱う必要があり、シグナルインテグリティ問題の候補となります。デバイスの立ち上がり時間がこの程度で、かつこの長さの配線が必要になると分かっているなら、PCB上でシグナルインテグリティ問題が発生する可能性があります。

電気エネルギーが配線に沿って伝わる速度は伝搬速度と呼ばれ、次のように表されます。

Vp = 光速 / √ 誘電率

使用する値:

Time = 1/3 * 立ち上がり時間

eR = 4(FR4の近似値)

C = 11.811 in/nSec(光速、インチ/ナノ秒)

√ は平方根記号です

信号の完全性が問題になり得る配線長を求めるには:

LR = Time * Vp

LR = Time * C / √ eR

LR = .33 * 11.811 / 2

LR = 1.95 in

インピーダンスをどのように制御するか?

エネルギーがソースと負荷の間で反射を繰り返す状況を、どうすれば避けられるのでしょうか。答えは、インピーダンスを整合させることです。インピーダンス整合により、すべてのエネルギーがソースから配線へ、さらに配線から負荷へと結合されるようになります。インピーダンスを考慮して基板を配線することを制御インピーダンス配線と呼び、言い換えれば、インピーダンスが管理された基板は制御インピーダンスPCBと呼ばれます。

インピーダンス整合を実現するには、2つの明確な要素があります。1つ目はコンポーネントの整合、2つ目は必要なインピーダンスが得られるように基板を配線することです。

コンポーネントのインピーダンス整合

配線だけでは制御インピーダンスPCBは実現できません。まず、コンポーネントのインピーダンスを確認し、必要に応じて整合させる必要があります。

理想的には、基板設計プロセスを始める前に必要な終端部品を追加できるよう、設計キャプチャ段階でシグナルインテグリティ問題の可能性があるネットを検出したいところです。出力ピンは低インピーダンス、入力ピンは高インピーダンスであるため、インピーダンス整合を実現するには終端部品を設計に追加する必要がある可能性が高いです。

回路図キャプチャ段階で設計に対してシグナルインテグリティ解析を実行できます。Tools » Signal Integrityコマンドを実行すると、Errors or Warningsダイアログが表示されることがよくあります。これは、すべてのコンポーネントにシグナルインテグリティモデルが割り当てられていないことを示しています。Signal Integrity解析エンジンは、コンポーネントのデジグネータに基づいてデフォルトモデルを自動選択します。デフォルトを使用するにはContinueをクリックし、モデルを確認・変更するにはModel Assignmentsをクリックします。Signal Integrity Model Assignmentsダイアログには、Signal IntegrityパネルのModel Assignmentsボタンからいつでもアクセスできます。

Signal Integrity解析エンジンは、必要なインピーダンスと平均トラック長にデフォルト値を使用します。また、信号刺激(注入される理論上の信号の特性)についてもデフォルト値を使用します。これらのデフォルトは、Signal Integrityパネルを開いた後、パネルのMenu button » Setup Optionsコマンドを使って設定できます。このコマンドによりSI Setup Optionsダイアログ(show image![]() )が開き、そこでSupply Netsも設定できます。プロジェクトにPCBが含まれている場合は、レイヤースタック設定に加え、Supply NetsおよびSignal Stimulusの設計ルールもチェックされます。なお、Signal Integrity解析エンジンでは、基準プレーンとして電源プレーンが必要です。ポリゴンで覆われた信号層を使用することはできません。

)が開き、そこでSupply Netsも設定できます。プロジェクトにPCBが含まれている場合は、レイヤースタック設定に加え、Supply NetsおよびSignal Stimulusの設計ルールもチェックされます。なお、Signal Integrity解析エンジンでは、基準プレーンとして電源プレーンが必要です。ポリゴンで覆われた信号層を使用することはできません。

Altium Designer でSignal Integrity解析エンジンにアクセスするには、Signal Integrity Analysisシステム拡張機能がインストールされている必要があります。 この拡張機能は、Altium Designer にデフォルトでインストールされています。 手動でインストールまたは削除することもできます。

拡張機能の管理について詳しくは、 Extending Your Installation ページ(Altium Designer Develop, Altium Designer Agile, Altium Designer)を参照してください。

設計の解析

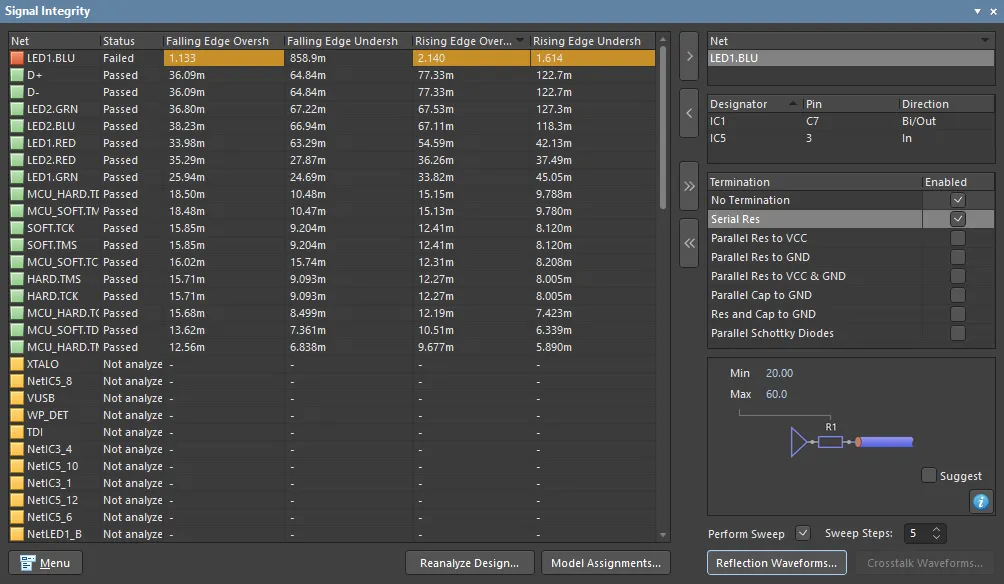

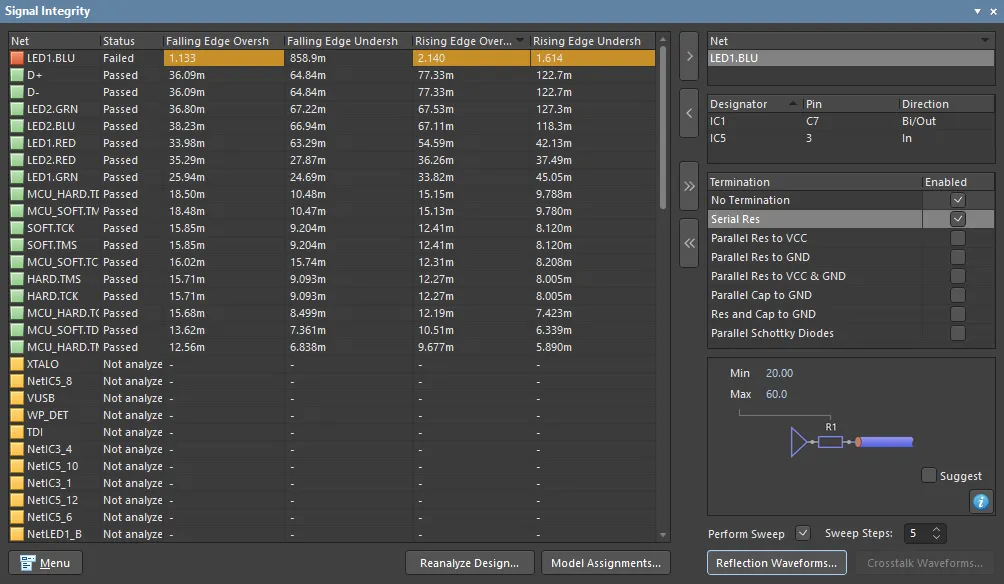

Tools » Signal Integrityコマンドを実行すると、設計が解析され、潜在的な問題のあるネットが以下のようにSignal Integrityパネルに表示されます。

設計キャプチャ中に、設計に潜在的なシグナルインテグリティ問題がないかをテストします。

設計キャプチャ中に、設計に潜在的なシグナルインテグリティ問題がないかをテストします。

このパネルから、選択したネット(または複数のネット)に対して反射解析を実行できます。左側には設計内のすべてのネットの解析結果が表示されます。ネットを選択して  ボタンをクリックするか、ネット名をダブルクリックすると、そのネットがパネル右側のNetフィールドに転送され、次のような詳細解析を実行できます。

ボタンをクリックするか、ネット名をダブルクリックすると、そのネットがパネル右側のNetフィールドに転送され、次のような詳細解析を実行できます。

-

そのネット内のピンを確認できます。シングルクリックで回路図上のそのピンへクロスプローブし、ダブルクリックでそのピンに割り当てられたモデルを確認・設定できます。

-

そのネットに対して1つ以上の理論上の終端オプションを有効にできます。

-

ネットに対して反射解析を実行し、そのネット内の各ピンでの挙動を示す波形セットを生成できます。

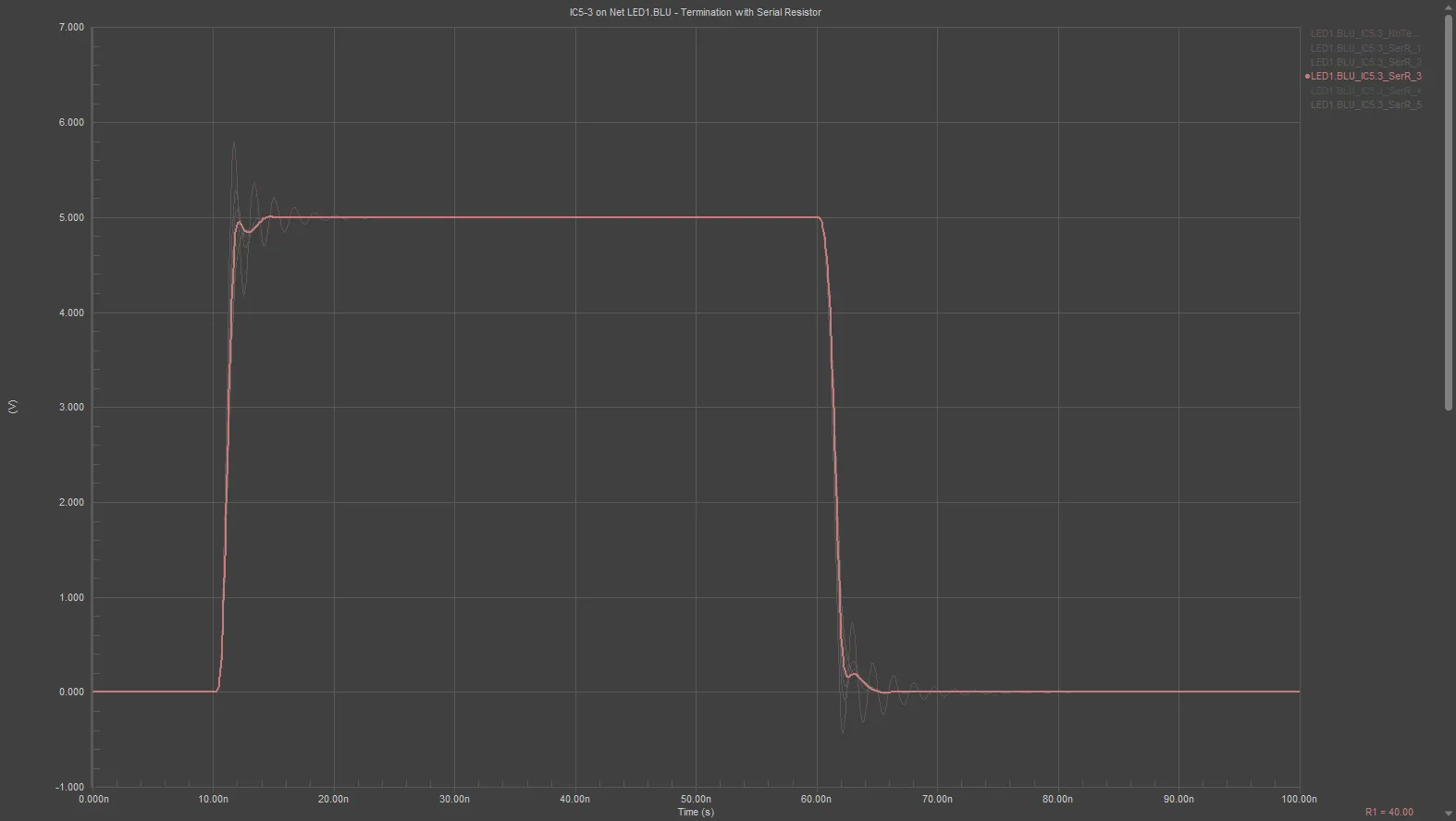

このパネルでは、可能性のある終端構成や値を試すことができます。画像上部に示されているSignal IntegrityパネルのTermination 領域では、Serial Resオプションが有効になっている点に注意してください。パネル下部のセクションには直列終端抵抗が表示されています。ここで、反射解析に使用する理論上の直列終端抵抗値の最小値と最大値を定義します(独自の値を入力するにはSuggestチェックボックスを無効にします)。

結果の確認

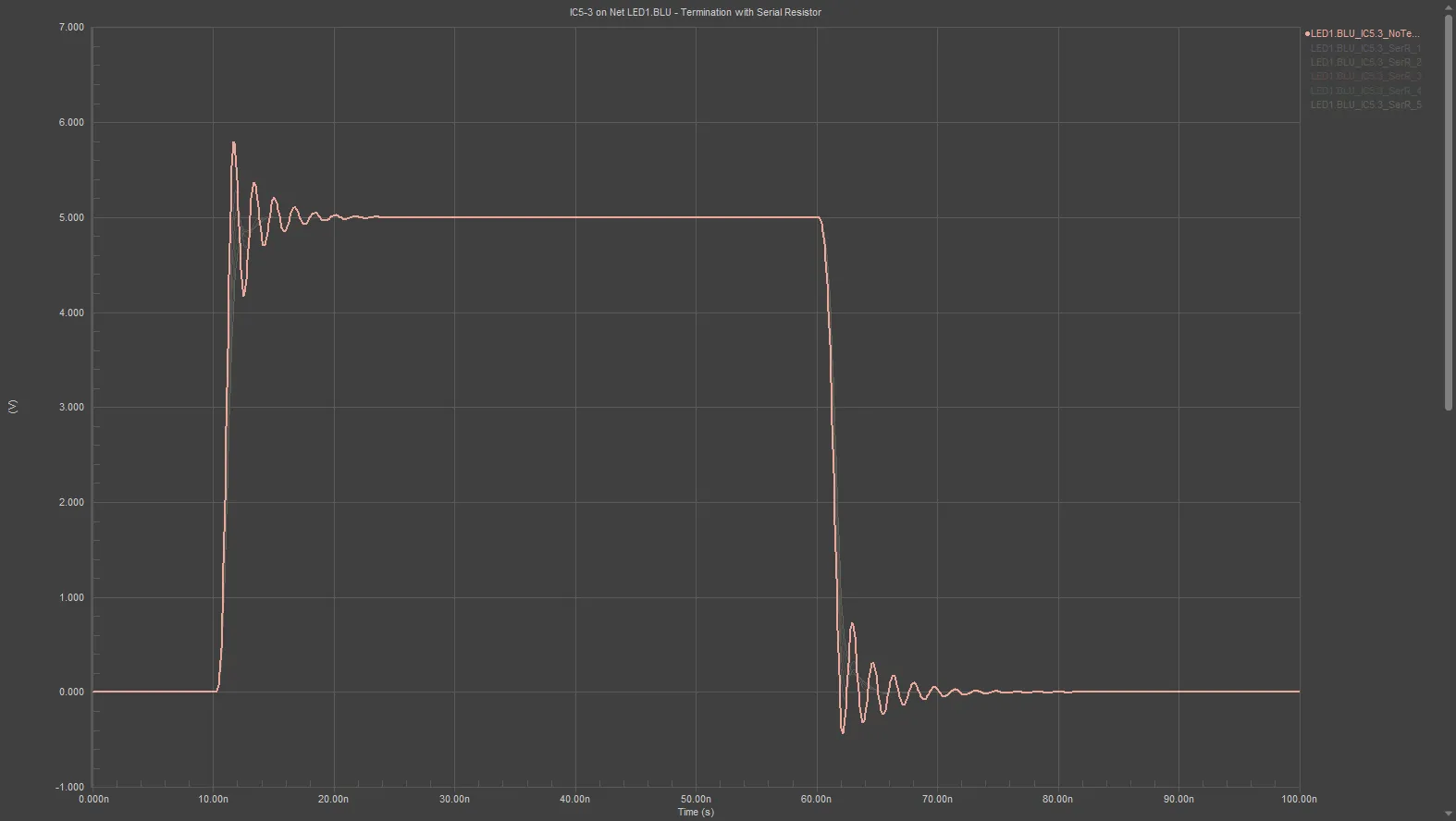

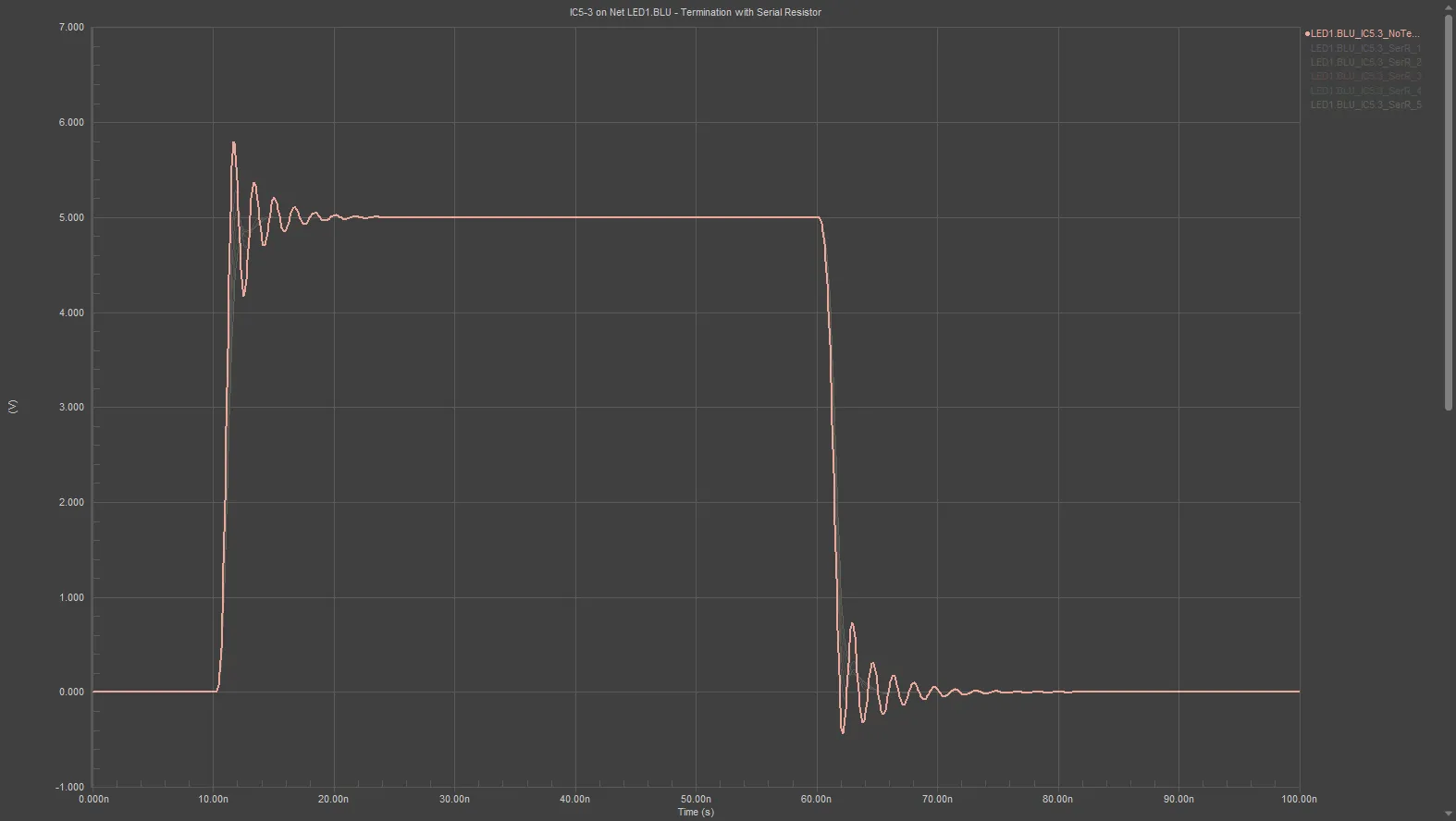

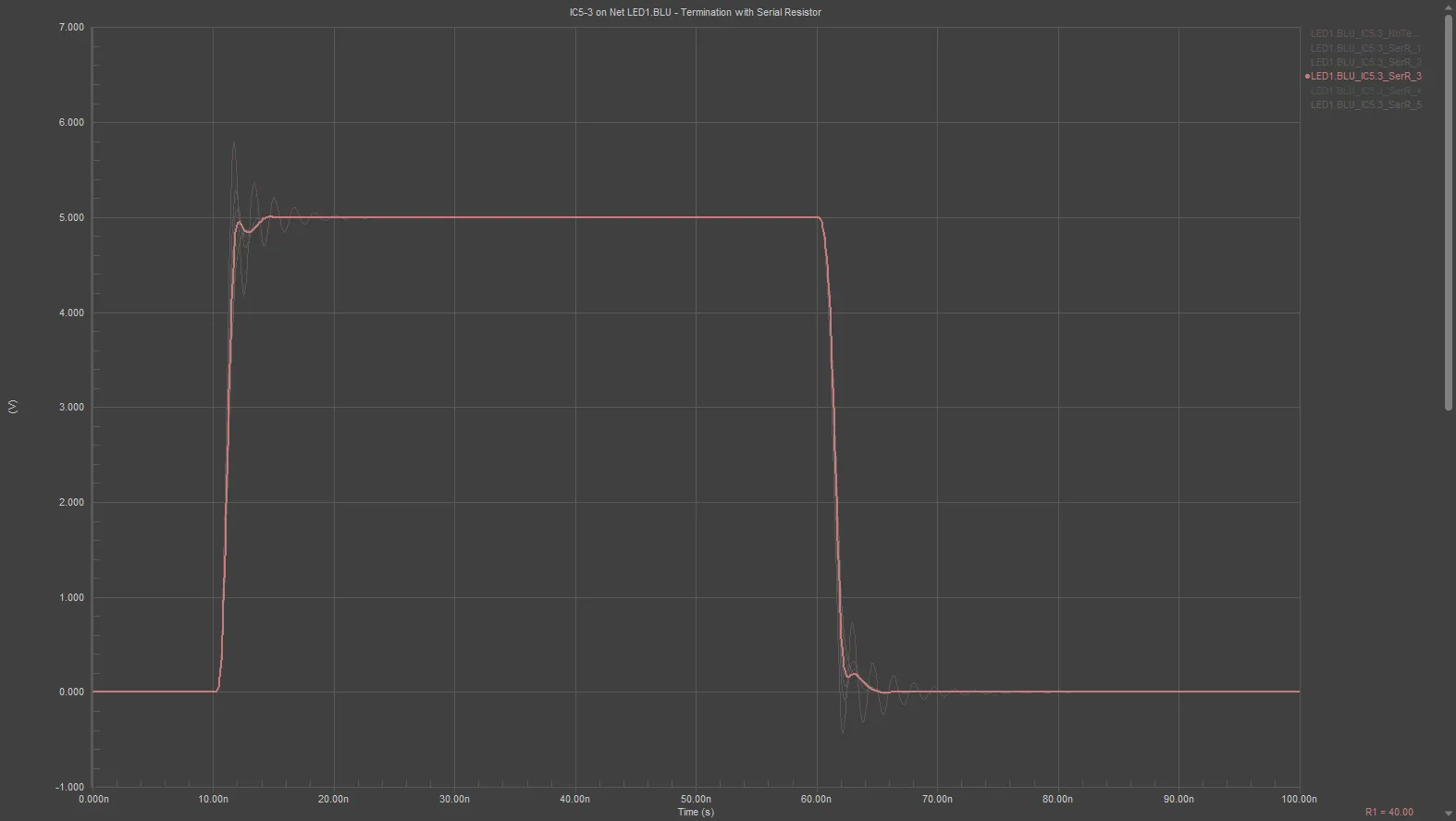

Reflection Waveformsボタンをクリックすると、そのネットに対して高精度の反射解析が実行され、結果が新しい波形ウィンドウ(*.SDF)に表示されます。

波形ウィンドウには次のものが含まれます。

-

解析対象の各ネットに対するチャート。ウィンドウ下部のタブをクリックしてチャートを切り替えます。

- 各チャートには、そのネット内の各ピンごとのプロットが含まれ、そのピンでの信号の挙動が表示されます。

以下の画像は、前のパネル画像で選択したネットの入力ピンにおける結果を示す2つのグラフです。1つ目のグラフは終端なしのネットにおける入力ピンを示し、 2つ目のグラフは6回のスイープを示しています。1回は元の終端なしネット、続く5回はソースピンに理論上の直列終端抵抗を含めたものです。

反射解析は5回実行されました(Sweep Steps オプション値 = 5)。理論上の終端抵抗は Min = 20 オームから Max = 60 オームまで段階的に変化させています。5回の解析(1回目は20オーム、最後は60オーム)はグラフの右側に一覧表示されます。各ラベルをクリックすると、その結果が強調表示され、右下に理論上の終端抵抗値が表示されます。このネットでは、40オームの直列終端抵抗により、右の画像で選択されているグラフが得られます。

左のグラフは、信号インテグリティ上の問題が生じる可能性のあるネットの反射解析を示しています。 右のグラフは、同じネットに約40オームの理論上の直列終端抵抗を追加したものです。

左のグラフは、信号インテグリティ上の問題が生じる可能性のあるネットの反射解析を示しています。 右のグラフは、同じネットに約40オームの理論上の直列終端抵抗を追加したものです。

フローティングパネルを非表示にするには、パネルがアクティブな状態(キャプションバーが色付き)で F4 を押します。パネル表示を復元するには F4 を押します。

配線インピーダンスを決定するものは何か?

制御インピーダンスPCBを実現するための第2の要素は、配線のインピーダンスが明確に定義されるように基板を配線することです。信号配線のインピーダンスに影響を与える要因はいくつかあり、配線の寸法やPCB製造に使用される材料の特性などが含まれます。

PCBエディターには、Simberian の Simbeor® 電磁界シグナルインテグリティエンジンが含まれています。Simbeor のモデル精度は、3Dフルウェーブ解析、ベンチマーク、および実験的検証のための高度なアルゴリズムによって検証されています。Simbeor エンジンは、最新のあらゆる基板構造と材料をサポートします。

Simbeor バージョン

この機能は Open Beta であり、Advanced Settings dialog で PCB.SimbeorVersion オプションを有効にすると利用できます。

遅延およびインピーダンスの計算に使用される Simbeor のバージョンは、「PCB.SimbeorVersion」詳細設定オプションに含まれる設定で制御できます。Simbeor 2020.3 を使用するにはオプション「0」を、Simbeor 2023.1 を使用するにはオプション「1」を選択します。

Simberian のサイトには、Simberian の主任開発者である Yuriy Shlepnev によって公開された広範なアプリケーションノートおよび論文ライブラリもあり、さらに業界および学術界の第一線の研究者との共同執筆論文も掲載されています。

Simbeor SFS

インピーダンスは、準静的フィールドソルバーである Simbeor SFS によって計算されます。Simbeor SFS はモーメント法に基づく高度な準静的2Dフィールドソルバーであり、収束性、比較、および測定によって検証されています。このソルバーは誘電体および導体の境界をメッシュ化し、対応する方程式を解くことで、テレグラフ方程式用の周波数依存RLGC行列を構築します。

Simbeor SFS はフルウェーブソルバーではありません。これは、PCB相互接続における波の伝搬が準TEM的であるため、インピーダンス、遅延、減衰の評価にはフルウェーブ解析が不要だからです。このような波は、準静的2Dフィールドソルバーで抽出されたRLGCパラメータにより高精度にシミュレーションできます。

Simbeor SFS ソルバーの独自の特性として、導体粗さモデルをサポートしている点があります。なお、多層導体モデル(めっき)はサポートしておらず、粗さはすべての導体で共通です。このソルバーが準静的であるのは、解にマイクロストリップ線路で生じる高周波分散(高周波でより高い誘電率を持つ誘電体中に電界がより集中する現象)が含まれていないためです。

► Simberian electromagnetic signal integrity technology

Supported PCB Structures

インピーダンスは、以下のPCB構造について計算できます。

-

マイクロストリップ

-

対称ストリップライン

-

非対称ストリップライン

-

シングルエンドおよび差動コプレーナ構造

-

異なる誘電特性を持つ複数の隣接誘電体層

制御インピーダンス配線用のPCBの設定

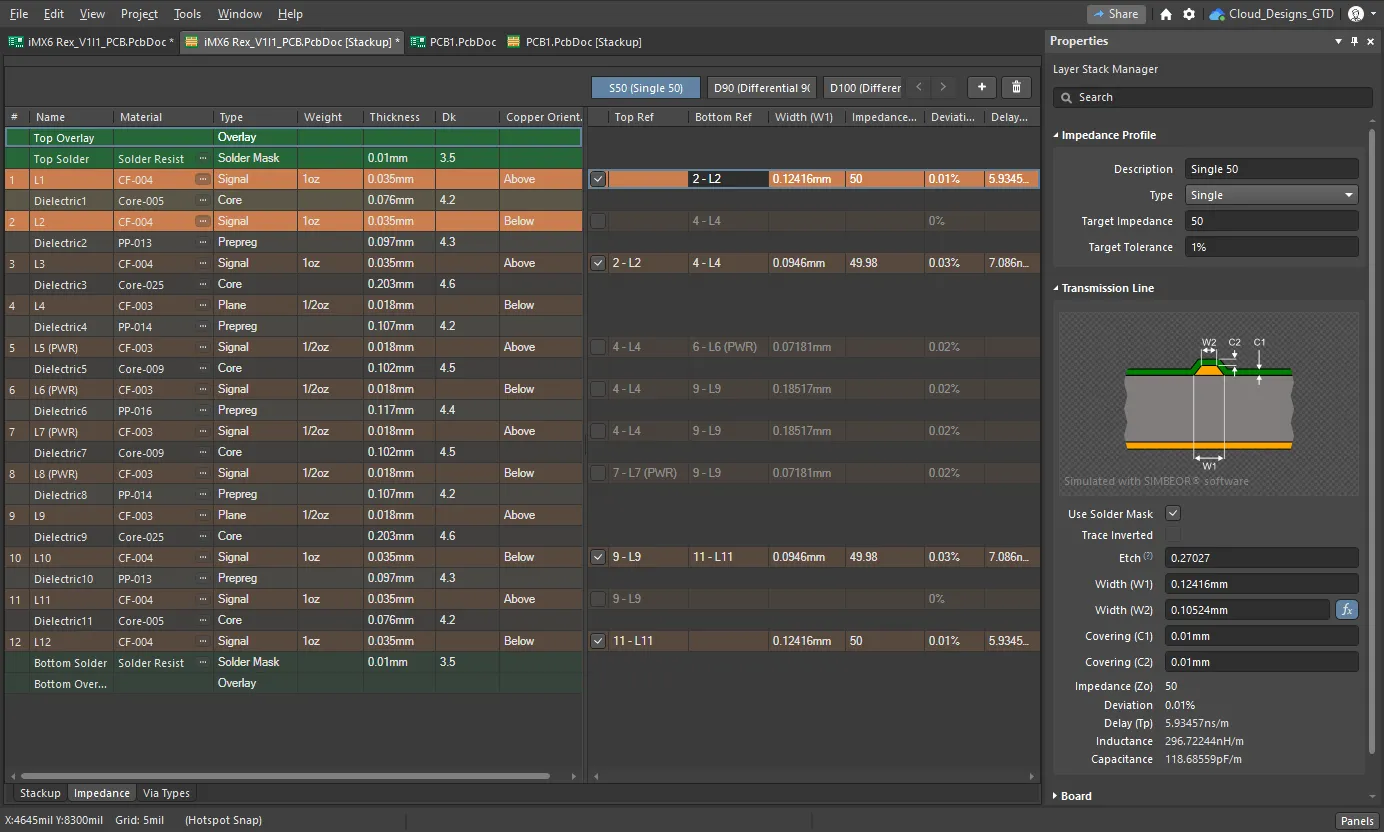

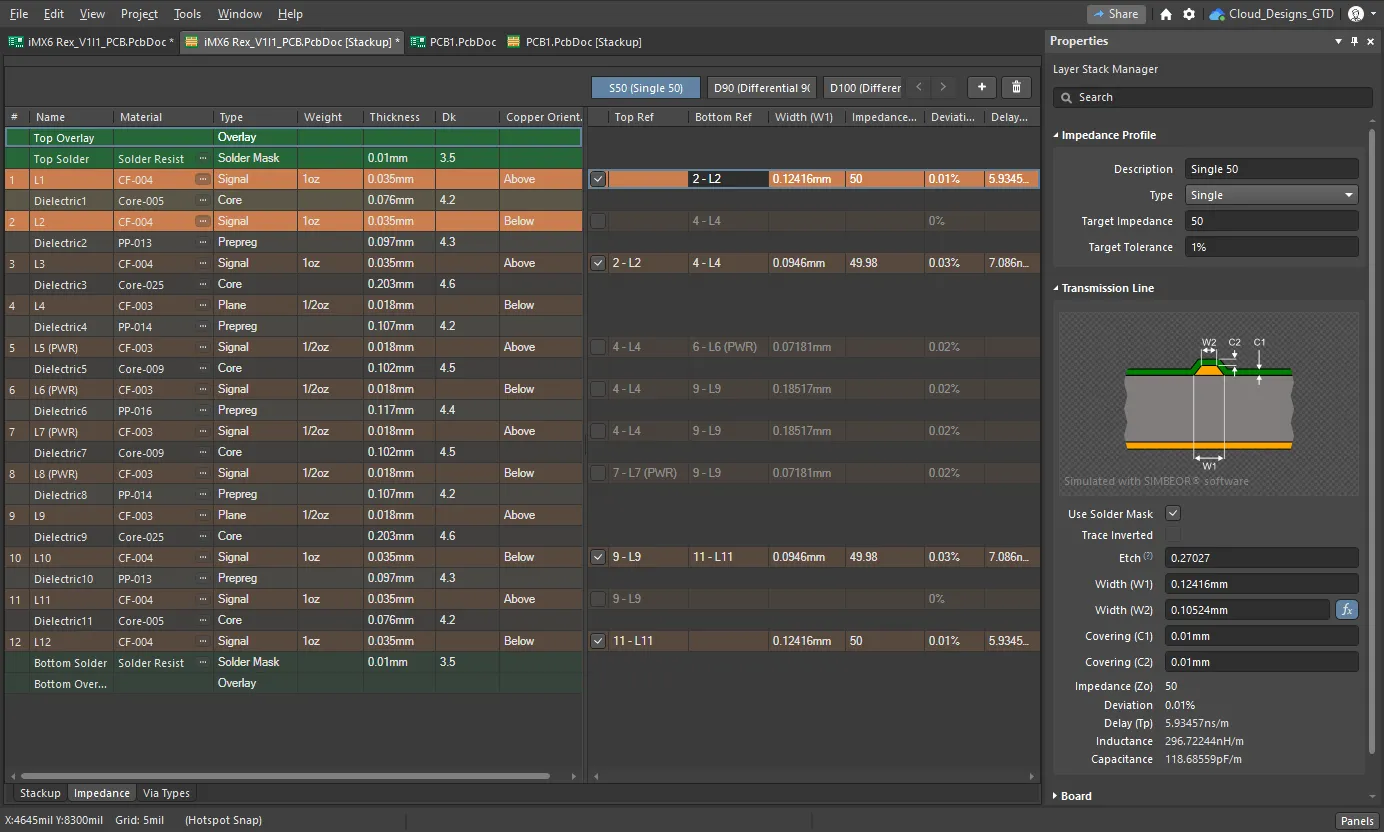

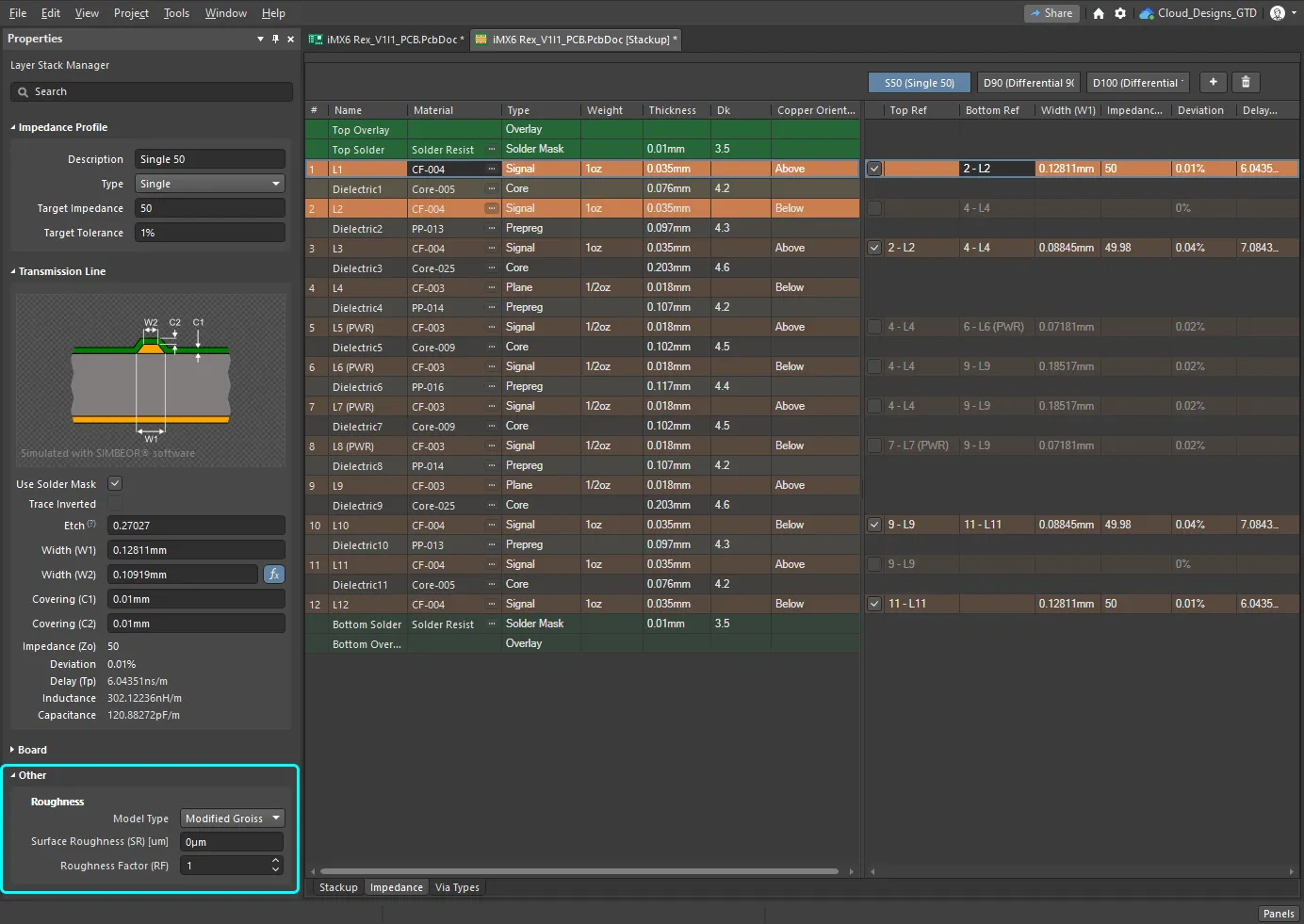

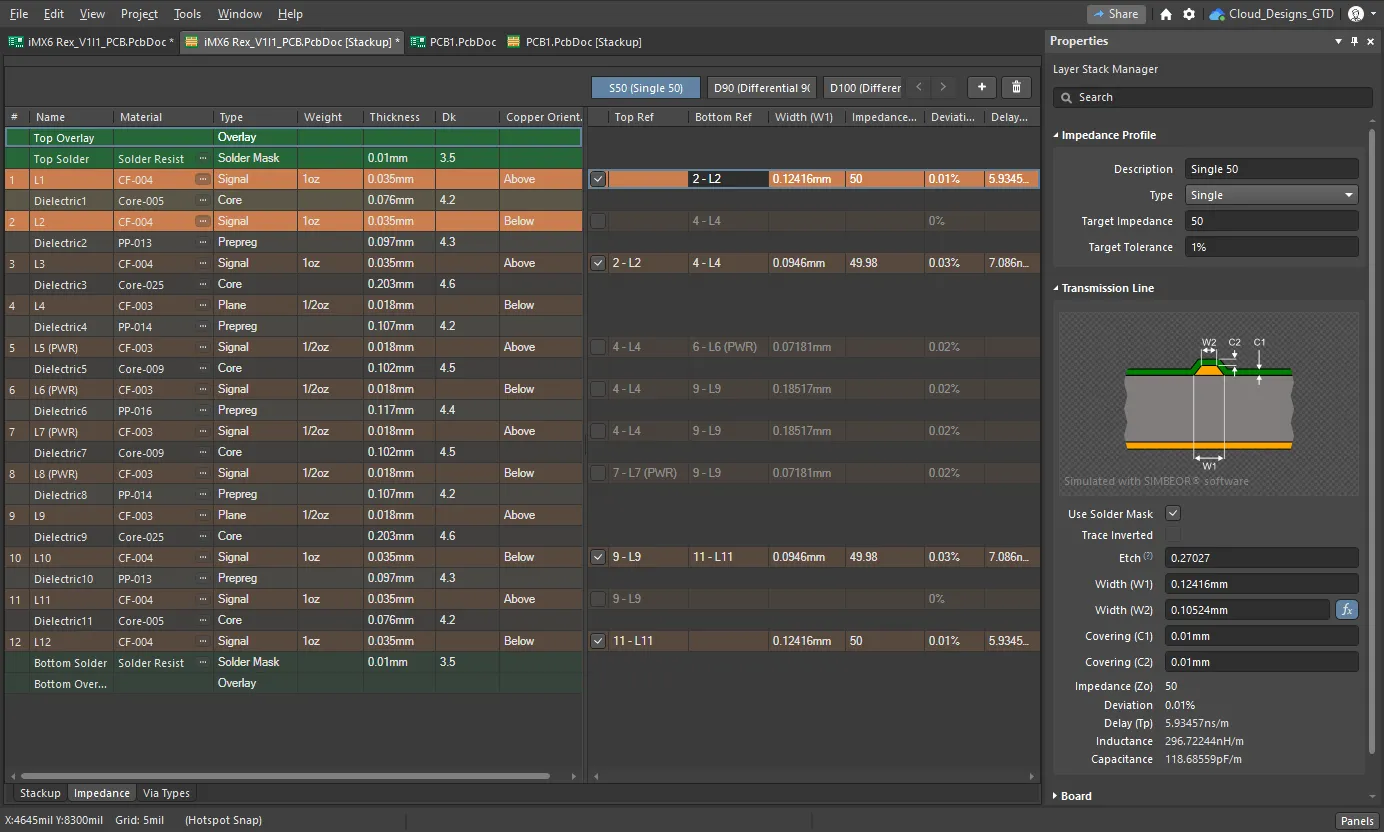

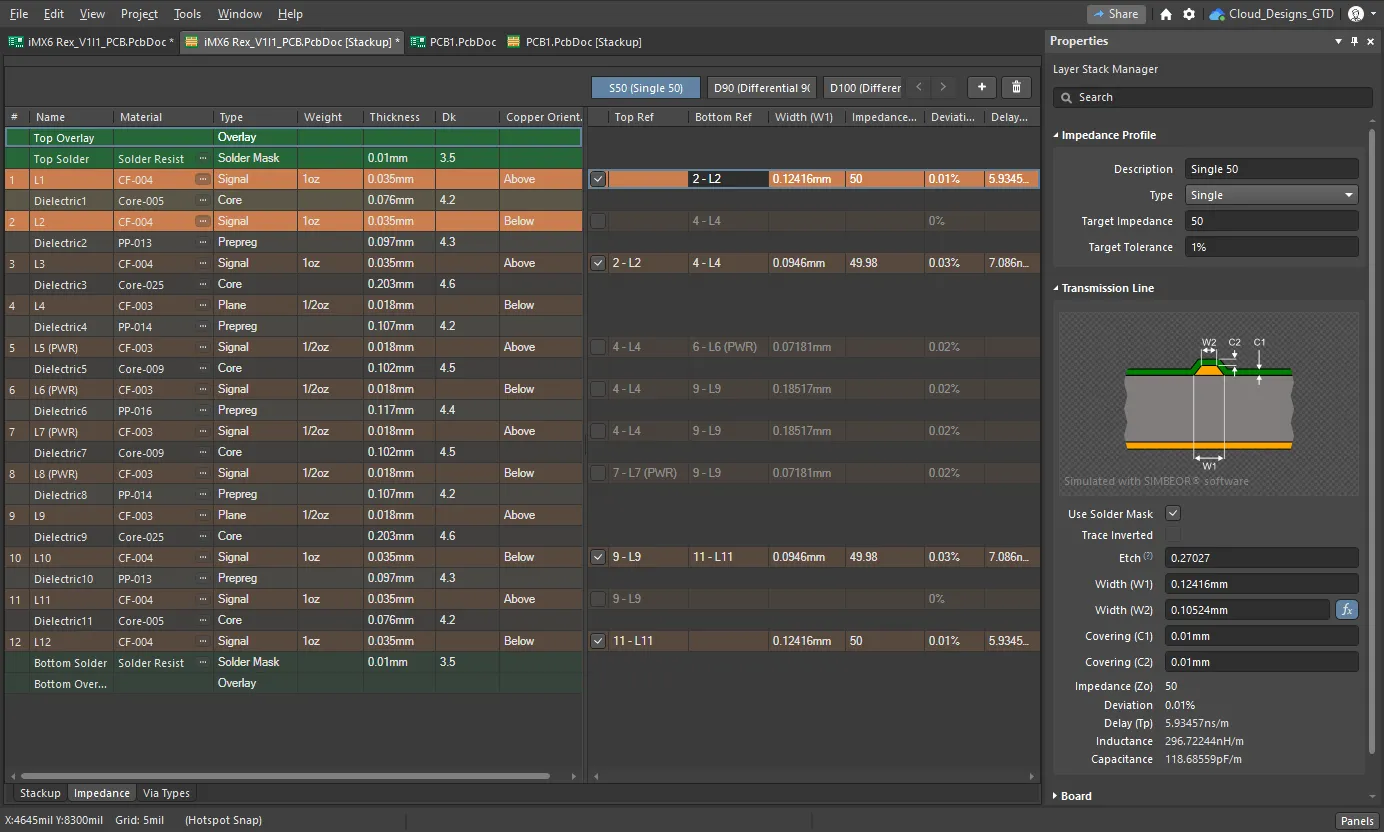

制御インピーダンス配線では、特定のインピーダンスを実現するために、配線寸法と基板材料の特性を設定することが重要です。これは PCB エディターの Layer Stack Manager で行います。Layer Stack Manager, を開くには、メインメニューから Design » Layer Stack Manager を選択します。Layer Stack Manager は、回路図シート、PCB、およびその他のドキュメントタイプと同様に、ドキュメントエディター内で開きます。

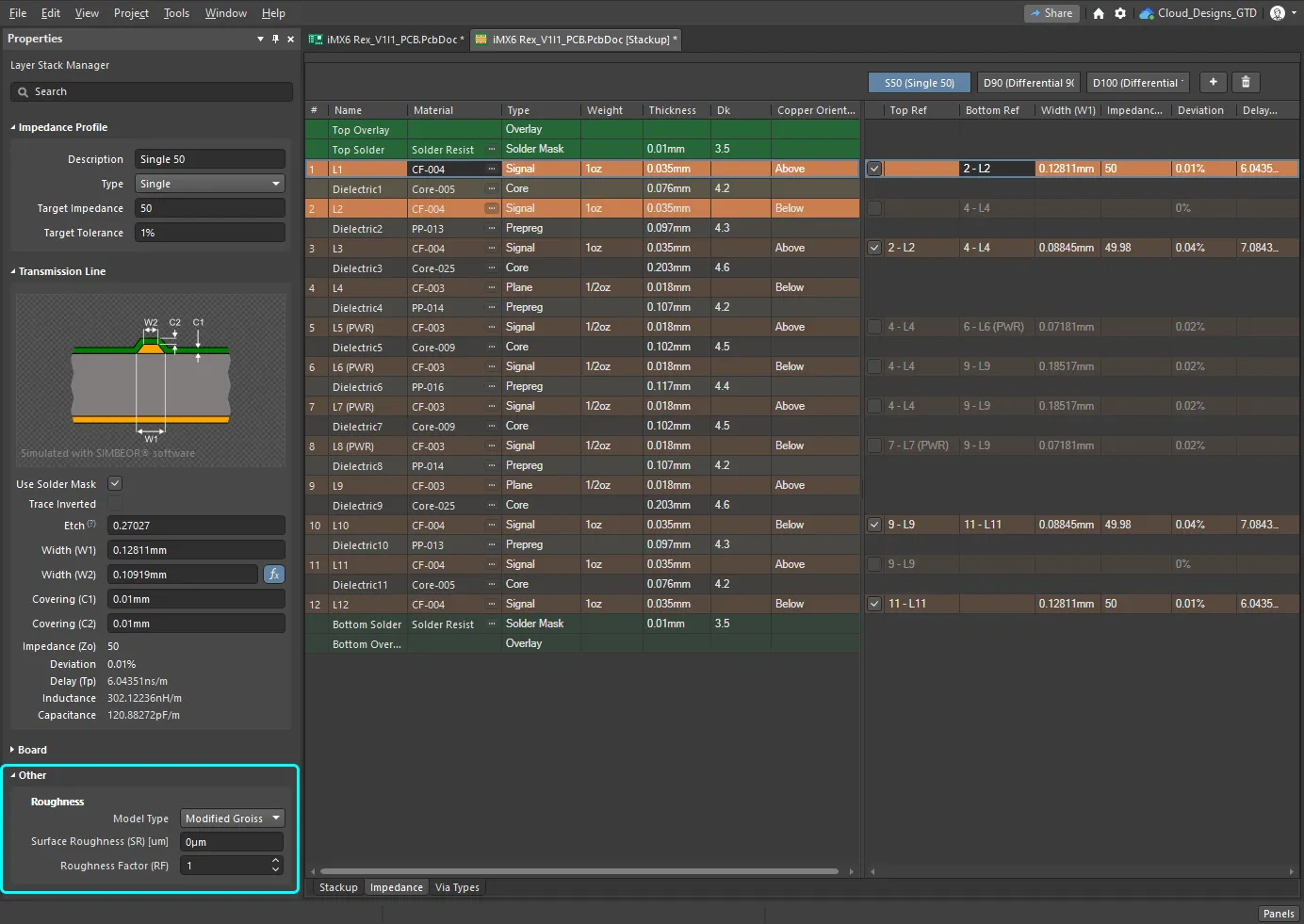

特定のインピーダンスを実現するために必要なトレース幅は、Layer Stack Manager の Impedance タブで設定するインピーダンスプロファイルの一部として計算されます。

計算の基準:

-

Impedance タブで設定する Target Impedance、Target Tolerance、および Roughness の値

-

Stackup タブで定義する材料設定。これには以下が含まれます:

-

信号層の厚さ

-

周囲の誘電体層の厚さ(基準プレーンまでの距離)および

-

誘電体材料の特性(比誘電率 Dk および損失係数 Df)

これらが正しく設定されると、インピーダンス計算機は以下を計算するのに十分な情報を持つことになります。

-

トレース幅

-

計算インピーダンス (Z)

-

コモンモードインピーダンス (Zcomm)

-

インピーダンス偏差 (Z Deviation)

-

伝搬遅延 (Tp)

-

単位長さあたりのインダクタンス (p.u.l.)

-

単位長さあたりのキャパシタンス (p.u.l.)

インピーダンスプロファイルは、計算速度を向上させるために、別スレッド(利用可能な場合)で計算されます。

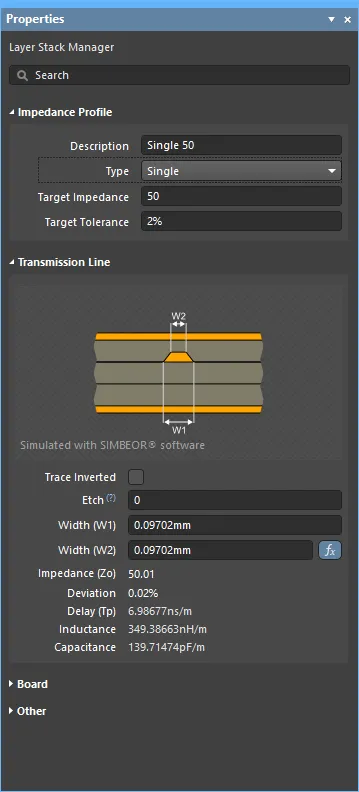

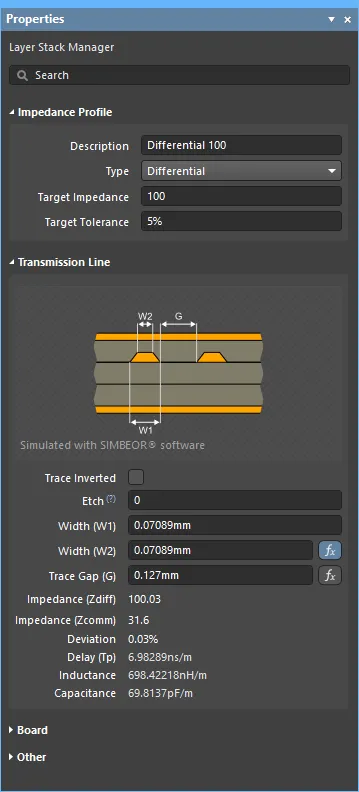

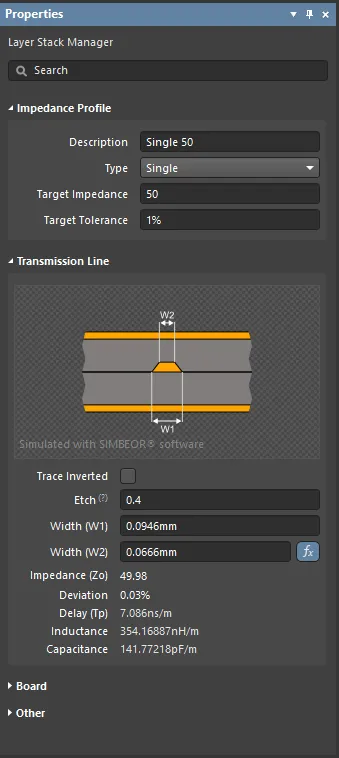

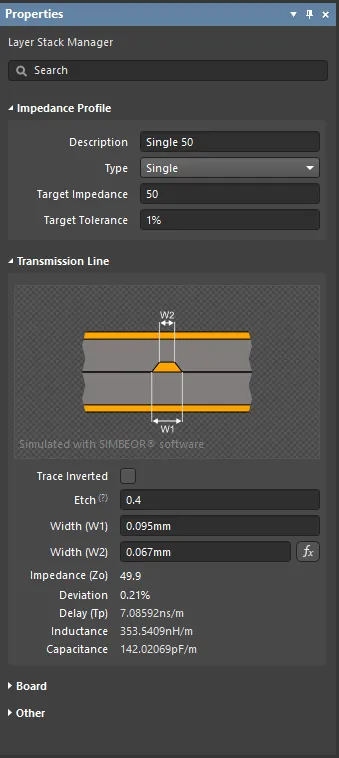

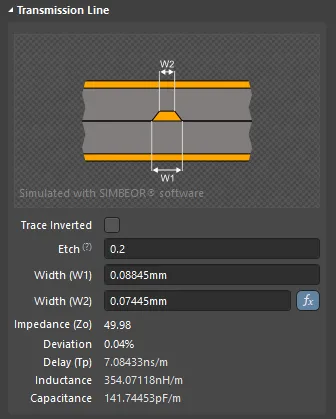

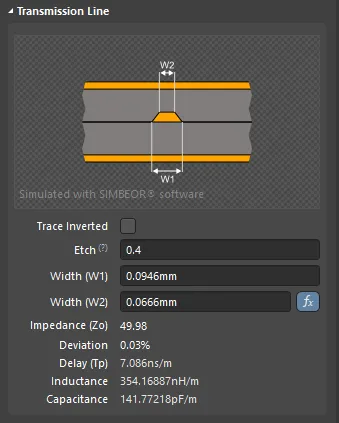

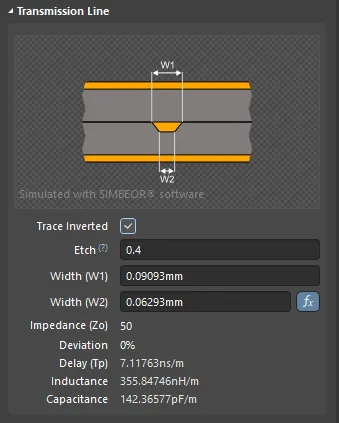

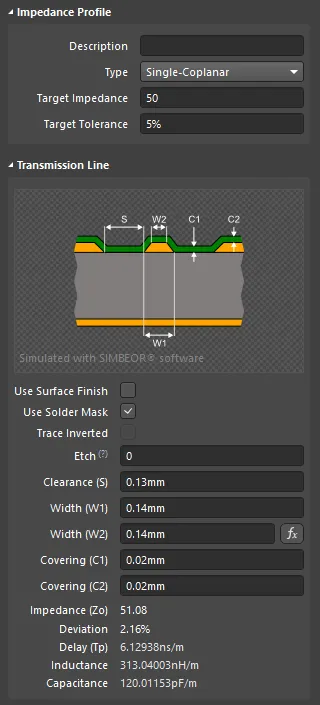

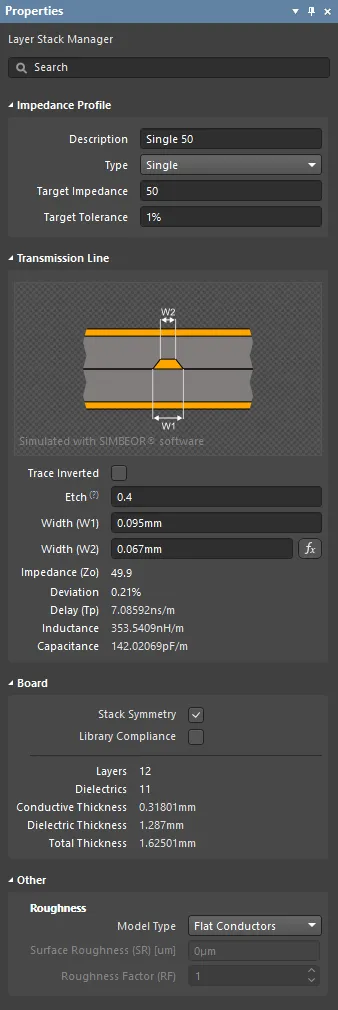

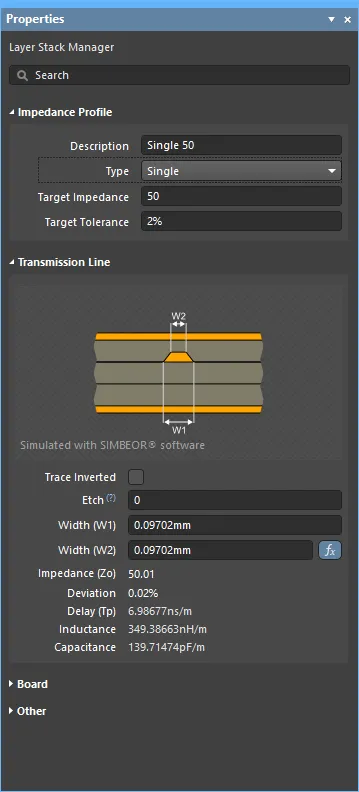

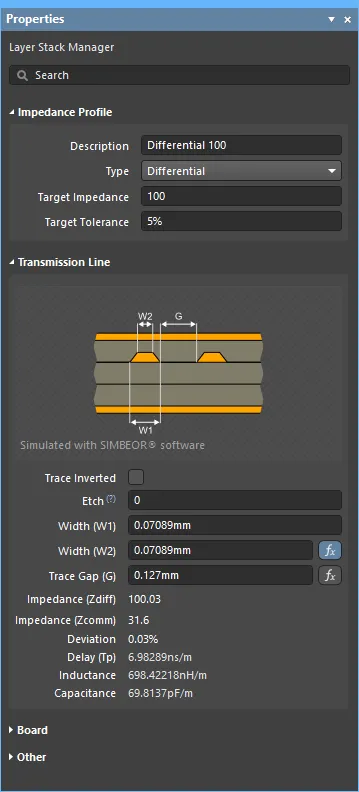

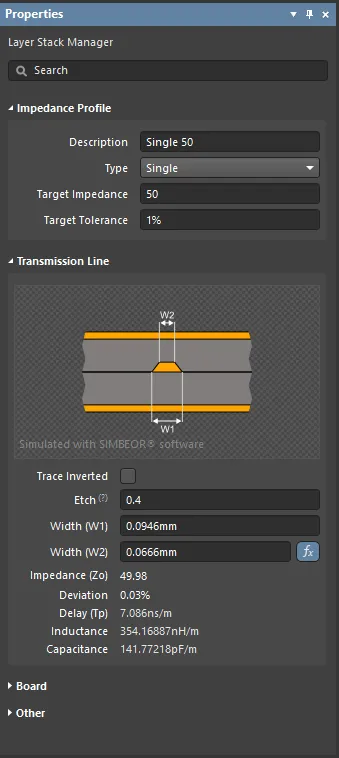

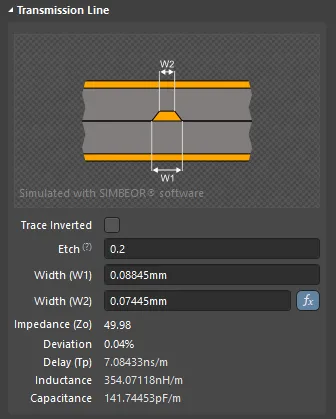

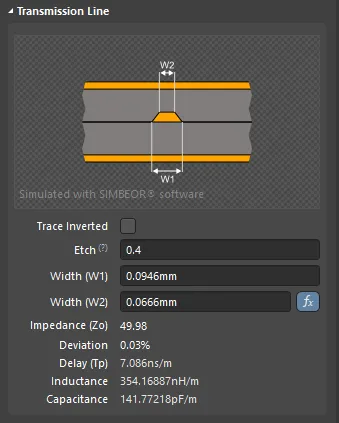

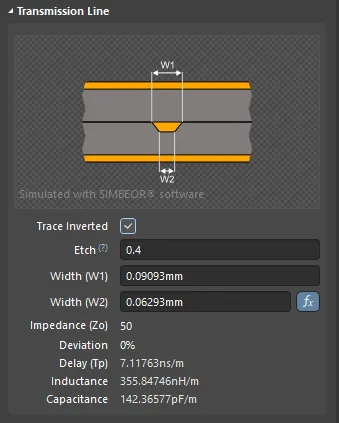

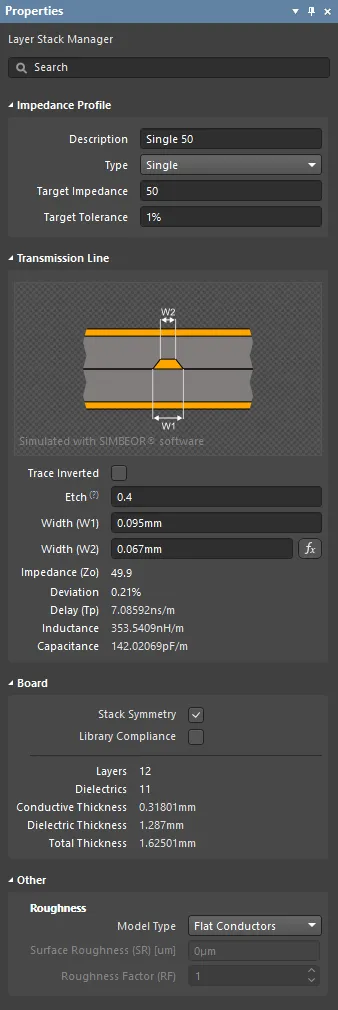

計算値は、以下に示すように、Layer Stack Manager で Impedance タブが選択されているとき、Properties パネル の Transmission Line セクションに表示されます。

トップレイヤー上で配線される単一ネット用に定義された 50Ω のインピーダンスプロファイル。画像にカーソルを合わせると、L3 層に対する同じプロファイルの設定が表示されます(画像提供: FEDEVEL Open Source、www.fedevel.com)。

トップレイヤー上で配線される単一ネット用に定義された 50Ω のインピーダンスプロファイル。画像にカーソルを合わせると、L3 層に対する同じプロファイルの設定が表示されます(画像提供: FEDEVEL Open Source、www.fedevel.com)。

レイヤースタックアップの設定

Main page: レイヤースタックの定義

銅箔層および誘電体製造層は、Layer Stack Manager の Stackup タブで設定します。

-

このタブでは、レイヤーの追加、削除、および設定を行います。リジッドフレックス設計では、このタブでレイヤーの有効化および無効化も行います。

-

現在選択されているレイヤーのプロパティは、グリッド内で直接、または Properties パネルで編集できます。パネルを有効にするには、デザインスペース下部の

ボタンをクリックします。

レイヤーグリッド内で右クリックするか、Edit » Add Layer コマンドを使用してレイヤーを追加します。銅箔層を追加する際、隣接する既存レイヤーも銅箔層である場合は、誘電体層も追加されます。

ボタンをクリックします。

レイヤーグリッド内で右クリックするか、Edit » Add Layer コマンドを使用してレイヤーを追加します。銅箔層を追加する際、隣接する既存レイヤーも銅箔層である場合は、誘電体層も追加されます。

-

Properties パネルの Board セクションで Stack Symmetry オプションが有効になっている場合、レイヤーは中央の誘電体層を中心として対になるように追加されます。

-

レイヤーの Material は、選択した Material セルに直接入力するか、Select Material ダイアログで選択できます。省略記号ボタン(

)をクリックして開きます。

)をクリックして開きます。

-

銅箔層には表面仕上げを追加できます。Add Layer サブメニューを使用して、現在選択されている銅箔層に Surface Finish レイヤーを追加し、その後、新しい表面仕上げ層の省略記号ボタンをクリックして仕上げタイプを選択します。

-

選択したレイヤーは、右クリックメニューまたは Edit メニューを使用して、同じ種類のレイヤー内で上下に移動できます。

-

Properties パネルの Board 領域には、Stack Symmetry および Library Compliance を強制するためのオプションが含まれています。これらについては後述します。

-

Properties パネルの Board 領域には、現在選択されているスタック(またはマルチスタックのリジッド/フレックス設計におけるサブスタック)の概要が表示されます。

レイヤースタックに関する考慮事項

インピーダンス制御の基本要件は、各信号経路の下に信号リターンパスを設けることです。Simbeor SI エンジンは、プレーン層と、ポリゴンで覆われた信号層の両方をサポートします。これらのリターンパス層は、基板スタックアップ全体に分散して配置する必要があります。理想的には、制御インピーダンス配線を担う各信号層に少なくとも1つのリターンパス層が隣接するように配置します。隣接するリターンパス層は信号のリターンパスを提供し、ここでは詳述しませんが、そのプレーンで分配されるDC電圧に関係なく機能します。

プレーンを流れるリターンパス電流は、信号層上の配線と同じ物理経路をたどろうとするため、重要な信号配線の下にあるリターンパス層にスプリットや切り欠きなどの不連続部を設けないことが重要です。

信号層とプレーン層の適切な順序を選択することに加え、各層の材料特性も定義する必要があります。これには以下が含まれます。

これらの値と配線幅はすべて最終的なインピーダンスに寄与します。必要なインピーダンスを実現するには、これらすべての値を調整する作業が必要になります。なお、使用可能な銅厚や誘電体厚の値は、PCB製造業者が提供可能な材料によって制限される場合があります。

► possible layer stackups

インピーダンスプロファイルの定義

Simbeor エンジンは、PCB エディターの Layer Stack Manager(Design » Layer Stack Manager)に組み込まれています。制御インピーダンス配線用にレイヤースタックを設定するには、Layer Stack Manager's Impedance タブに切り替え、そこでインピーダンスプロファイルを追加して設定します。

トップレイヤー上で配線される個別ネット向けに定義された 50Ω のインピーダンスプロファイル。画像の上にカーソルを置くと、レイヤー L3 に対する同じプロファイルの設定が表示されます。

トップレイヤー上で配線される個別ネット向けに定義された 50Ω のインピーダンスプロファイル。画像の上にカーソルを置くと、レイヤー L3 に対する同じプロファイルの設定が表示されます。

インピーダンスプロファイルの作成と設定に関する注意事項:

-

Layer Stack Manager で、上図のように Impedance タブに切り替えます。

-

新しいプロファイルを追加するには、

ボタン(すでにプロファイルが定義されている場合は

ボタン(すでにプロファイルが定義されている場合は  ボタン)をクリックします。

ボタン)をクリックします。

-

Properties パネルで、必要なインピーダンス Type、Target Impedance、および Target Tolerance を定義します。Description は任意で、インピーダンスプロファイル名が表示される場所にあわせて表示されます。

-

レイヤーのグリッドは 2 つの領域に分かれています。左側にはスタックアップ内のレイヤーが表示され、右側の Impedance Profile 領域には、スタックアップ内の各信号レイヤーに対応するレイヤーが表示されます。Profile 領域のレイヤーチェックボックスを使用して、そのレイヤーのインピーダンス計算を有効にします。上の画像を例にし、左端の列に表示されているレイヤー番号を参照すると、レイヤー

L1、L3、L10 および L12 のレイヤーチェックボックスがオンになっており、インピーダンス計算が有効になっています。

-

Profile 領域で有効化されたレイヤーをクリックすると、レイヤースタック内のすべてのレイヤーのうち、選択した信号レイヤーのインピーダンス計算に使用されるレイヤー以外はフェード表示になります(上図参照)。そのレイヤーの参照レイヤーは、Impedance Profile 領域の Top Ref 列および Bottom Ref 列で編集します。参照レイヤーは、レイヤー Type として

Plane または Signal のいずれかを持つことができます。たとえば上図では、スタックアップ内のレイヤー L10 がインピーダンス計算用に有効化されており、Top Ref は 9-L9 に設定されています。これは Plane レイヤーです。また、Bottom Ref は 11-L11 に設定されており、これは Signal レイヤーです。ソフトウェアは、信号レイヤーが参照プレーンとして使用される場合、そのレイヤーには電源ネットまたはグラウンドネットに接続された連続した銅プレーンが存在すると仮定します。

-

このインピーダンスで配線を行う他の各レイヤーについても Impedance Profile チェックボックスを有効にし、参照プレーンを設定します。上の画像にカーソルを合わせると、レイヤー L3 の S50 インピーダンスプロファイルが表示されます。

-

計算された配線トレース幅が発注できない値である場合は、幅とギャップの設定を調整できます。

幅とギャップの設定の調整

ソフトウェアは、目標インピーダンスと許容差からトレース幅を計算します。計算されたトレース幅が、たとえば 0.0683mm のように発注できない値になることは珍しくありません。基板製造業者は、利用可能な材料厚みと、トレース幅に対して達成可能な精度を案内してくれます。その後は、希望する値から開始し、利用可能な寸法に調整したときに計算インピーダンス値へどのような影響があるかを確認していく作業になります。

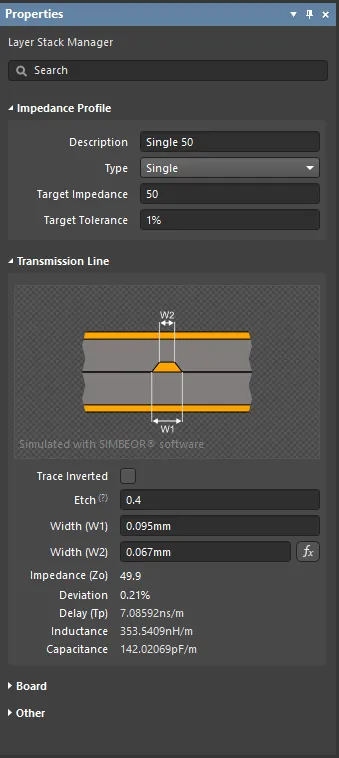

このような検証と設定調整のプロセスを支援するため、インピーダンス計算機は順方向計算と逆方向計算をサポートしています。デフォルトモードは順方向です(インピーダンスを入力すると、ソフトウェアが幅を計算します)。  アイコンは計算対象の変数を示します。

アイコンは計算対象の変数を示します。

50Ω の目標インピーダンスでは、順方向計算により幅(W1)は 94.6µm になります。右側の画像は、幅(W1)を 95µm に設定したときの逆方向計算を示しています。

50Ω の目標インピーダンスでは、順方向計算により幅(W1)は 94.6µm になります。右側の画像は、幅(W1)を 95µm に設定したときの逆方向計算を示しています。

計算を逆方向に切り替え、選択したレイヤーで異なるトレース幅を検討するには、新しい Width (W1) 値を入力し、キーボードの Enter を押します。計算値は、その幅に変更した影響を反映して更新されます。  ボタンをクリックすると、計算機は順方向計算モードに戻ります。Width (W2) に新しい値を入力すると、Etch の値が変化します。

ボタンをクリックすると、計算機は順方向計算モードに戻ります。Width (W2) に新しい値を入力すると、Etch の値が変化します。

差動ペア伝送線路の結果を確認するには、適切な  ボタンをクリックして、計算対象の変数として Trace Width または Trace Gap のいずれかを指定します。もう一方の変数を編集して Target Impedance を変更するか、あるいは Target Impedance を変更してもう一方の変数への影響を確認します。

ボタンをクリックして、計算対象の変数として Trace Width または Trace Gap のいずれかを指定します。もう一方の変数を編集して Target Impedance を変更するか、あるいは Target Impedance を変更してもう一方の変数への影響を確認します。

パネル内のフィールドに入力した値を適用するには、キーボードの Enter を押します。

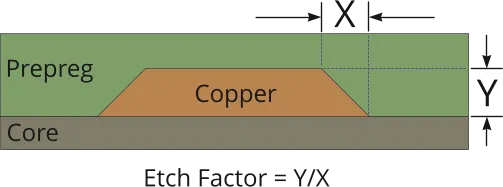

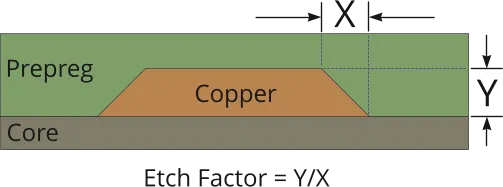

エッチファクター

PCB 上の信号トレースは、不要な銅をエッチングで除去して形成されます。エッチャントは銅表面から除去を開始するため、表面側の銅はエッチャントと接触する時間が長くなります。その結果、完成したトレースのエッジには傾斜が生じ、下図のように完成後のトレース断面積が減少します。

エッチング中に失われるトレースエッジの銅の面積(両エッジ合計) = X * Y

この傾斜の度合いは Etch Factor と呼ばれ、次のように定義されます:

Etch Factor = Y/X

Y = X の場合、Etch Factor = 1

Properties パネルに表示されている画像を参照してください:

? の上にカーソルを置くと、式が表示されます。

? の上にカーソルを置くと、式が表示されます。

Etch Factor の標準的な定義は、 trace thickness / amount of over-etching の比として指定する方法です。これにより、次の式が得られます:

Etch Factor = T/[0.5(W1-W2)]

この方法の欠点は、オーバーエッチがない状態(つまりトレースエッジが垂直)を指定するには、エッチファクターとして inf(無限大)を入力しなければならないことです。エッチ量の指定を簡単にするため、この式は反転されており、0(ゼロ)を入力することでオーバーエッチなしを示せるようになっています。

Etch = [0.5(W1-W2)]/T

-

計算から Etch Factor を除外するには(トレースエッジに傾斜が生じないことを指定するには)、値を

0 (zero) に設定します。Etch Factor には逆数値が使用されており、エッチなしの設定を簡単にしています。

-

製造プロセスで生じる Etch Factor については、基板製造業者に確認してください。

銅の向き

エッチファクターに影響するもう 1 つの製造上の要素が、銅の向きです。PCB トレースは、誘電体基材にラミネートされた連続した銅箔から不要な銅をエッチング除去して形成されます。銅の向きは、その基材から銅がどちらの方向へ突き出しているかを定義します。別の見方をすると、銅が上側からエッチングされるのか下側からエッチングされるのかを示します。

Trace Inverted チェックボックスをクリックすると、Copper Orientation を Above から Below に切り替えられます。

Trace Inverted チェックボックスをクリックすると、Copper Orientation を Above から Below に切り替えられます。

Copper Orientation は Properties パネルで編集できます: Transmission line セクション(Impedance タブがアクティブな場合)、または Layer セクション(Stackup タブがアクティブな場合)です。Grid に Copper Orientation 列が表示されている場合は、Layer Stack Manager のグリッドでも編集できます。

銅レイヤーには Orientation オプションもあります。このフィールドは、その銅レイヤーのどちら側に部品が実装されるかを定義します。リジッドフレックス設計で内部/フレックスレイヤー上に部品が実装される場合や、設計で embedded components を使用する場合に、その銅レイヤーに対して部品がどちら向きに配置されるかを示すために設定します。

►Defining and Configuring the Rigid-Flex Substacks

について詳しく見る

►Embedded Components について詳しく見る

導体表面粗さプリント基板の各銅レイヤー表面には、ある程度の粗さがあります。PCB 製造時には、銅レイヤーと誘電体レイヤーの密着性を高めるために、銅レイヤー表面に粗化処理が施されます。この表面粗さは、10 GB/s を超えるスイッチング速度では導体インピーダンスに大きく影響します。広範な研究と解析を通じて、業界の専門家は、表面粗さは Surface Roughness と Roughness Factor の値から導かれる粗さ補正係数によってモデル化できると結論づけています。

RoughnessLayer Stack Manager の設定は、Properties パネルの Layer Stack Manager モードで使用できます。これらのパラメーターは導体レイヤーに対してのみ使用されます。

表面粗さは特性インピーダンスの計算に含まれます。

表面粗さは特性インピーダンスの計算に含まれます。

粗さ:

-

Model Type - 表面粗さの影響を計算するための推奨モデルです(各種モデルの詳細については以下の記事を参照してください)。サブスタック内のすべての銅レイヤーに適用されます。

-

Surface Roughness - 表面粗さの値(製造業者から入手可能)。0 ~ 10µm の値を入力します。デフォルトは 0.1µm です。

-

Roughness Factor - 粗さ効果によって予想される導体損失の最大増加を特徴づけます。1 ~ 100 の値を入力します。デフォルトは 2 です。

参考資料

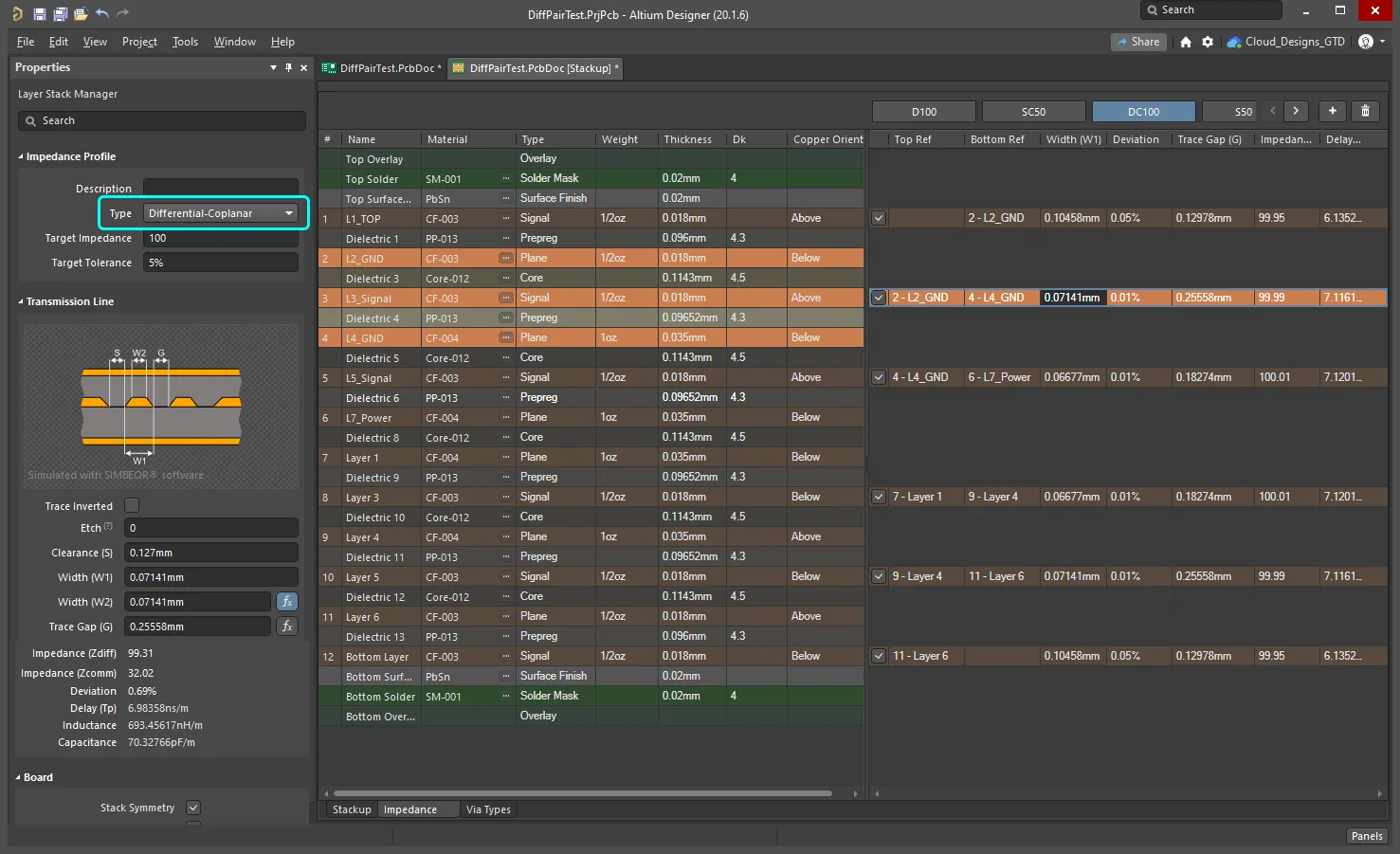

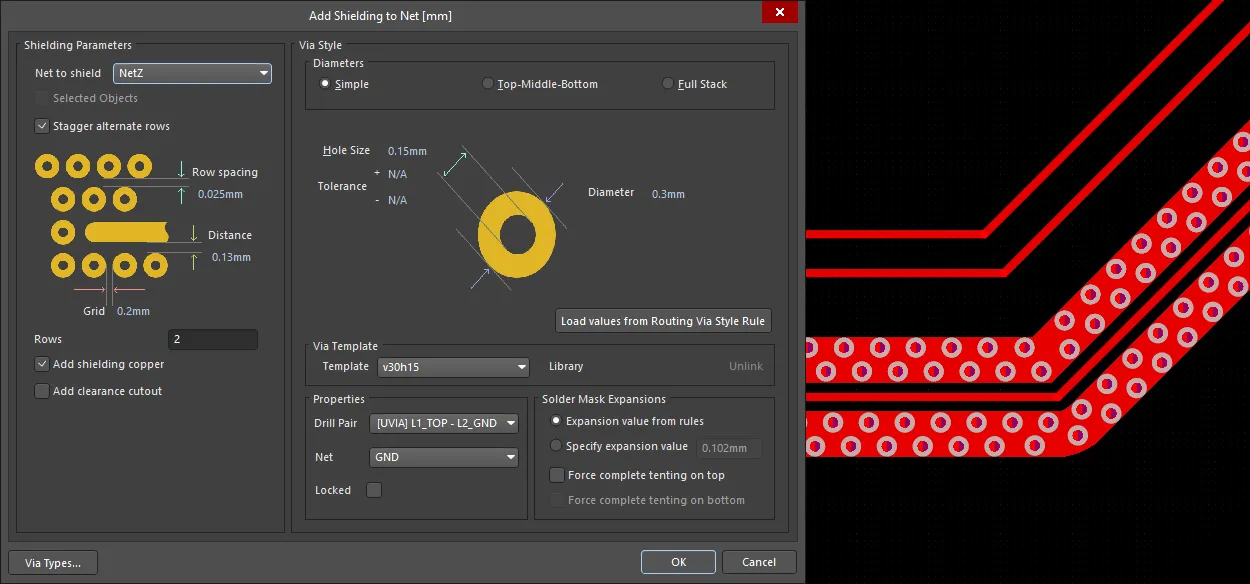

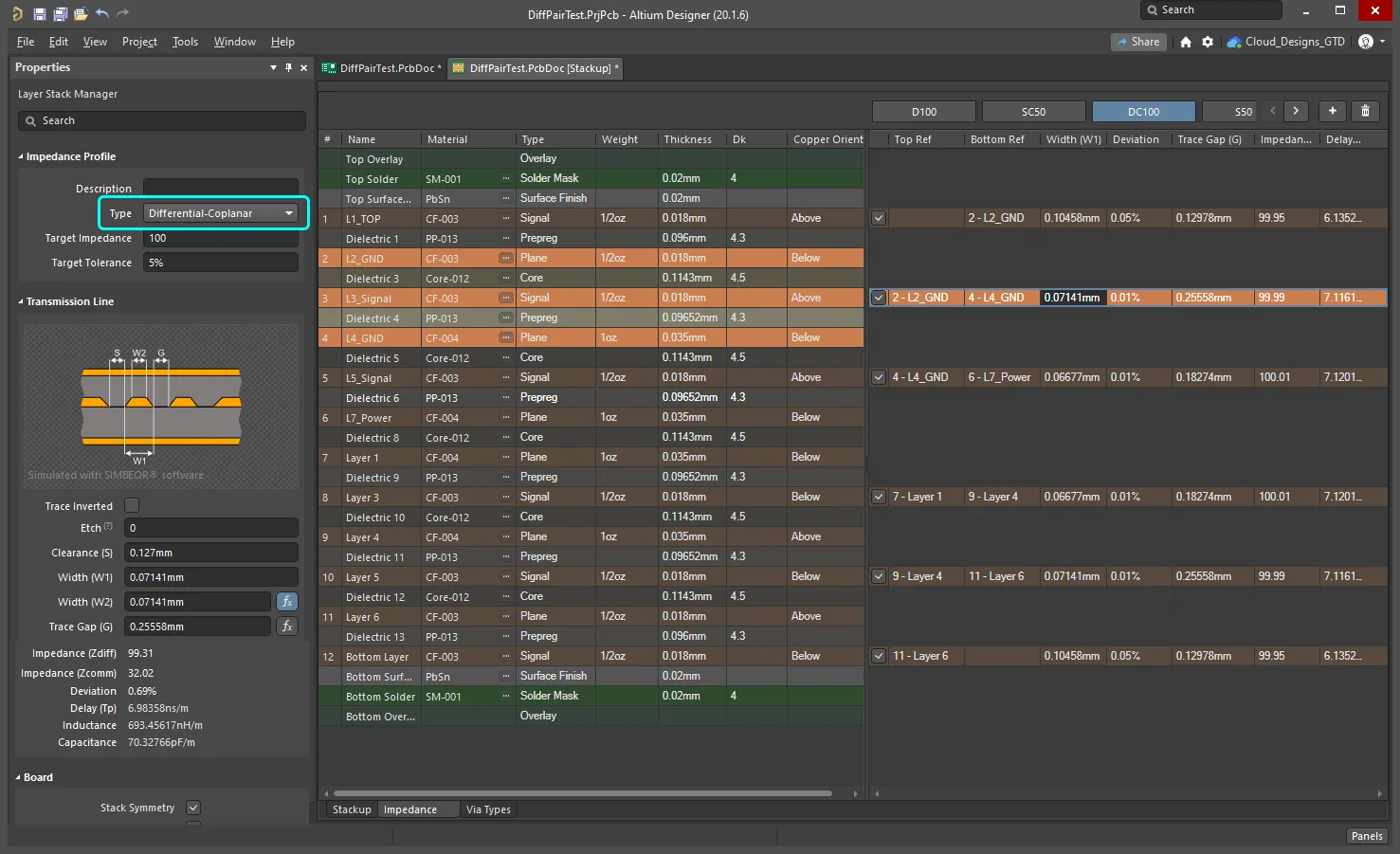

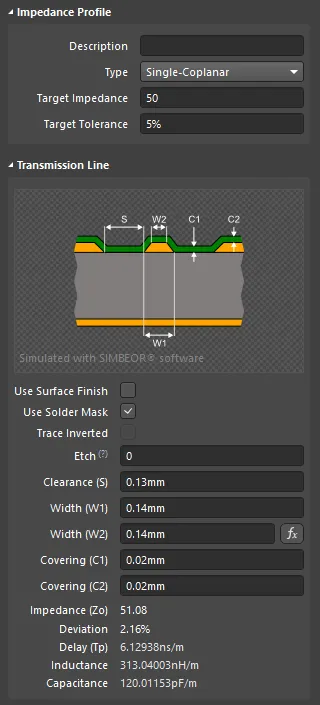

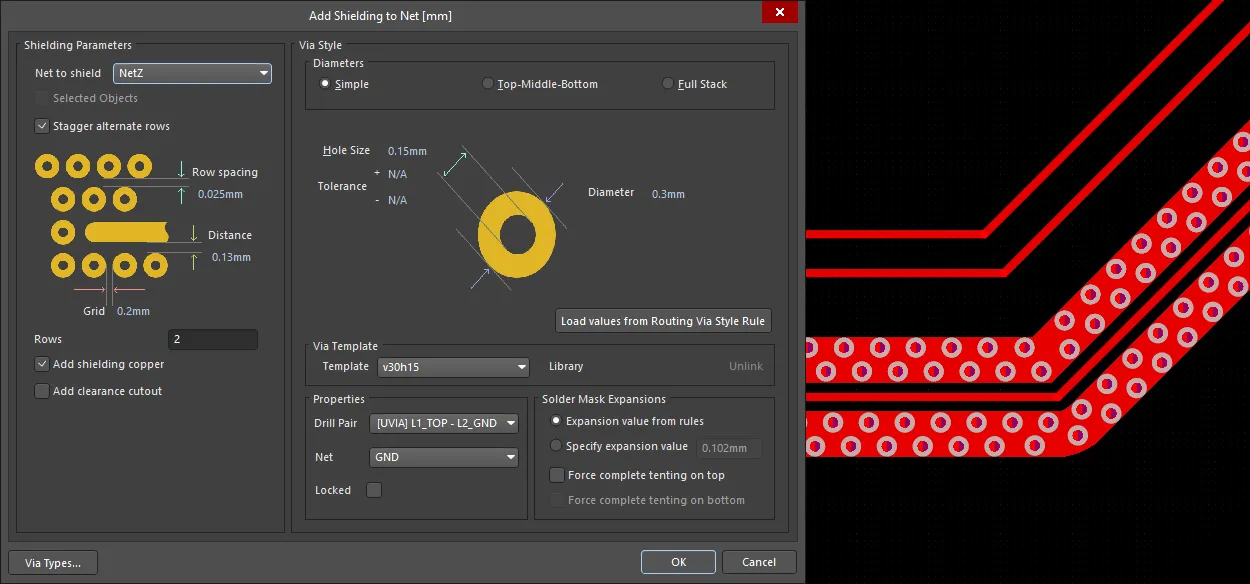

コプレーナ伝送線路構造のサポート

Layer Stack Manager のインピーダンス計算機は、シングルエンドおよび差動のコプレーナ構造をサポートしています。新しいインピーダンスプロファイルを作成し、Impedance Profile Type のドロップダウンリストから Single-Coplanar または Differential-Coplanar を選択します。

コプレーナ構造の操作:

-

標準のシングルエンドおよび差動インピーダンスと同様に、各変数の値は、ユーザー定義の Target Impedance と Target Tolerance および基板レイヤーの物理特性に基づいて自動計算されます。これらの自動計算値は、Properties パネルの Layer Stack Manager モードの編集ボックスに新しい値を入力することで調整できます。

- コプレーナ構造で配線したい信号ネットを対象にするには、Routing Width(または Differential Pairs Routing)デザインルールを設定し、Use Impedance Profile オプションを有効にして、必要な Coplanar Impedance Profile を選択します。

-

コプレーナ構造では、信号配線の両側にリファレンスプレーンが必要です。これは配置したポリゴン、またはスティッチングビアを追加する場合は Add Shielding to Net コマンド(詳細は下記)によって作成できます。ポリゴンを配置する場合、そのポリゴンと信号配線の間隔は、Simbeor インピーダンス計算機で求められる Clearance (S) 値で定義されます(Properties パネルに表示。上および下の画像を参照)。リファレンスポリゴンと信号配線の間のクリアランスを制御するには、Clearance design rule を設定します(show image

![]() )。

)。

-

コプレーナ構造が接地されている場合、信号トレースの両側にビアフェンスを設けるのが一般的です。これを行うには、PCB エディターの Tools » Via Stitching/Shielding » Add Shielding to Net コマンドを使用します。Add shielding copper オプションを有効にすると、このコマンドはビアの配置に加えて、右下の画像に示すように、ビアフェンスを覆うポリゴンを信号配線の周囲に配置することもできます。

► Via Shielding

について詳しく見る

について詳しく見る  インピーダンス計算機は信号特性とクリアランスを決定します(最初の画像)。そのクリアランスを via shielding の Distance 設定に使用してください。

インピーダンス計算機は信号特性とクリアランスを決定します(最初の画像)。そのクリアランスを via shielding の Distance 設定に使用してください。

層材料の選択

制御インピーダンス設計では、レイヤースタックアップで使用する材料の選定が非常に重要です。

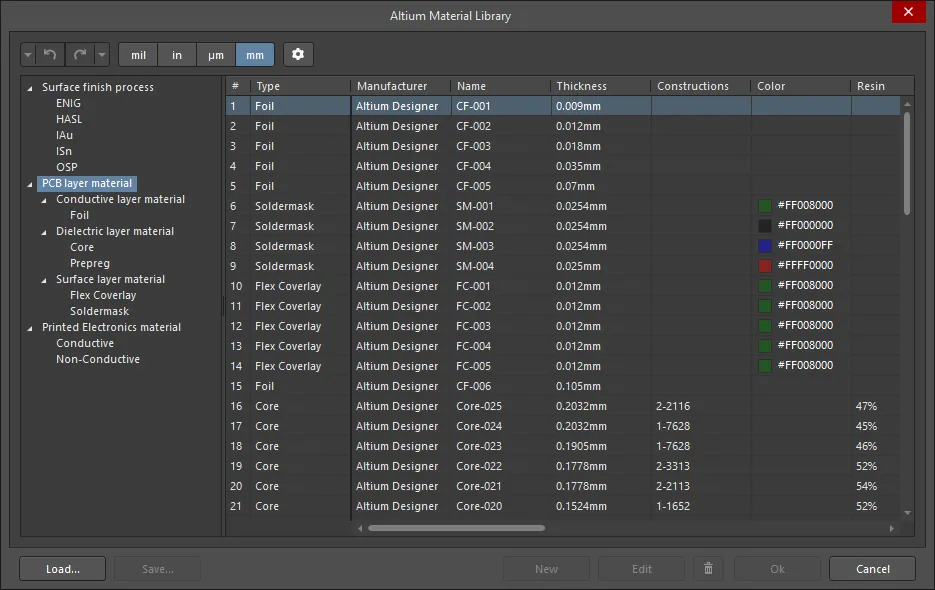

たとえば、PCB 製造で最も一般的な材料は、ガラス繊維(グラスファイバー)で強化したエポキシ樹脂の両面に銅箔を貼り合わせたものです。ガラス繊維クロスの織りの密度は、誘電率 Dk(比誘電率)および損失正接 Df の値とその一貫性に影響します。織られたガラスクロスの周囲には樹脂があり、使用される樹脂の割合も材料性能において重要です。

利用可能なガラス繊維の織りパターンは非常に多岐にわたります。PCB 製造で使用されるガラス繊維系材料の予測可能性と性能を確保しやすくするため、IPC では織りパターンに関する規格を定めています。

IPC standard IPC-4412B: Specification for Finished Fabric Woven from "E" Glass for Printed Boards

-

この規格で定義されている織り番号は、Constructions の値として Altium Material Library ダイアログに表示されます。

-

レイヤー構成が対称である場合は、Properties パネルの Board セクションで Stack Symmetry オプションを有効にします。レイヤーを追加するたびに、スタックアップの反対側にも対応するレイヤーが自動的に追加されます。

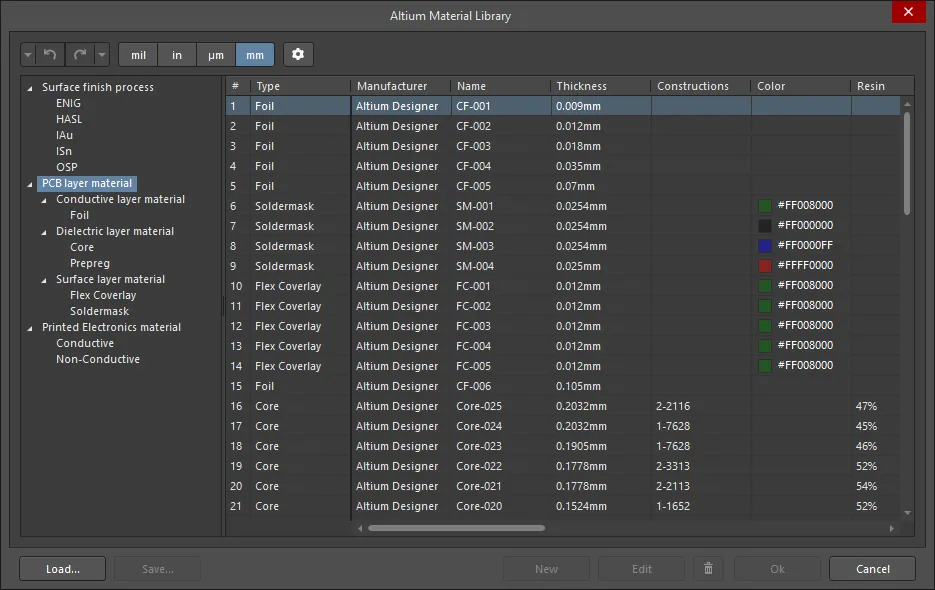

Material Library

設計者は、材料特性を Layer Stack Manager で直接編集することも、Altium Material Library から材料を選択することもできます。

ライブラリ全体は Altium Material Library dialog(Tools » Material Library)で表示でき、追加も可能です。

材料は使用カテゴリごとに整理されており、ダイアログ左側のツリー構造からアクセスできます。このレベルの下では、各使用カテゴリはさらに機能カテゴリに分かれており、たとえば PCB layer material カテゴリ内の Conductive layer material、Dielectric layer material,、Surface Layer Material i などがあります。

材料の追加、保存、読み込み

ツリーで特定の材料カテゴリを選択すると、新しい材料をライブラリに追加できます。外部の材料ライブラリで定義された材料は読み込み(Load ボタン)でき、Altium Material Library ダイアログで追加したユーザー定義材料はユーザーライブラリに保存(Save ボタン)することもできます。保存されるのはユーザー定義材料のみです。

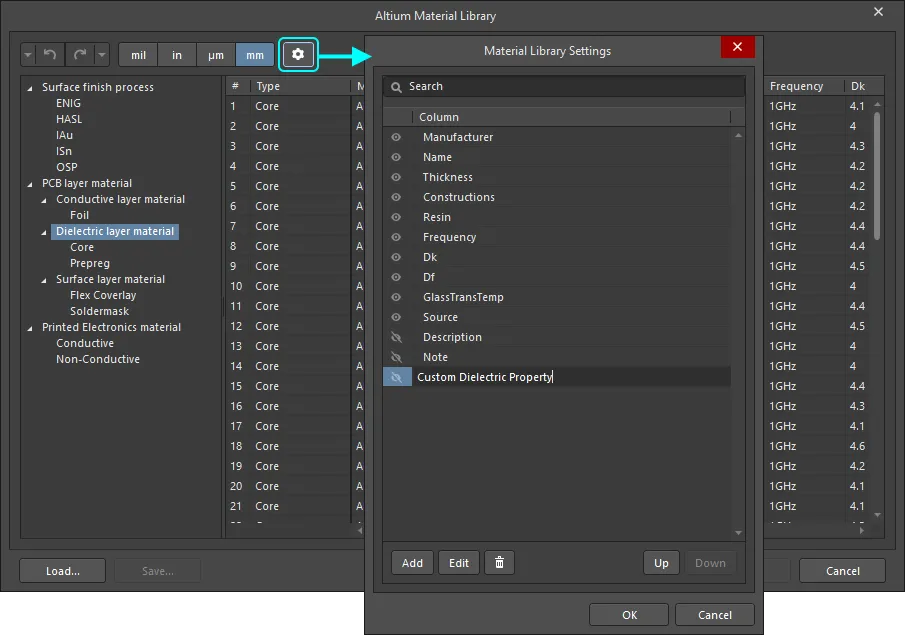

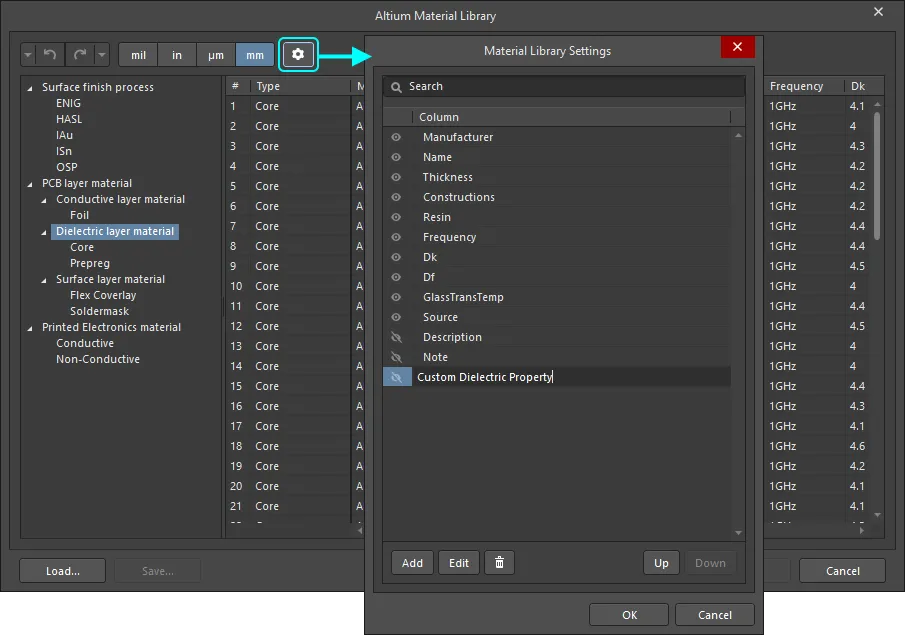

材料へのカスタムプロパティの追加

ライブラリに登録されている材料(デフォルト材料およびユーザー定義材料)には、カスタムプロパティを追加できます。カスタムプロパティを追加するには、まず左側のツリーで適切なノードを選択して、追加対象の材料を定義し、次に  ボタンをクリックして Material Library Settings ダイアログを開きます。

ボタンをクリックして Material Library Settings ダイアログを開きます。

その後、必要な値を Altium Material Library ダイアログで選択した材料に追加できます。行を選択して Edit ボタンをクリックしてください。

誘電体材料の挙動

PCB 誘電体の Dk/Df は周波数依存性があります。複合誘電体では、Dk は周波数とともに低下し、Df はわずかに増加します(この種の誘電体における緩和型の原子分極によるものです)。

周波数に対する分散は、多極 Debye モデルで表現できますが、これには複数の周波数ポイントが必要です。PCB 誘電体向けには、Djordjevic-Sarkar モデルまたは Wideband Debye モデルと呼ばれる、より簡易な連続極モデルが開発されています。このモデルは解析的かつ因果的であり、Dk/Df を 1 つの周波数ポイントで測定するだけで構築できます。より簡単でありながら高精度な手法です(詳細は Simberian Technical Presentations Library の Material World tutorial #2016_01 を参照してください)。

Layer Stack Manager's インピーダンス計算機は Wideband Debye モデルを使用し、デフォルト周波数は 1 GHz です。別の周波数が必要な場合は、積層板仕様から 1~10 GHz のいずれか 1 つの周波数ポイントにおける Dk/Df 値を選び、そのうえで 1 GHz で計算された特性インピーダンス値を使用してください。

-

すべての計算では、デフォルト周波数として 1 GHz が使用されます。

-

Df が未定義の場合、デフォルト値の 0 が使用されます。

Properties Panel

Layer Stack ドキュメントの Impedance タブがアクティブなとき、Properties パネルで Impedance Profile の要件を設定できます。設定した Impedance Profile は、その後 Routing Width または Differential Pairs Routing デザインルールで選択できます。

-

Impedance Profile

-

Description – わかりやすい説明を入力します。このフィールドは任意で、Impedance Profile 名が表示される場所であればどこでも表示されます。

-

Type – ドロップダウンを使用してインピーダンスタイプを選択します。選択肢は Single、Differential、Single-Coplanar、Differential-Coplanar です。

コプレーナ構造インピーダンスおよび標準のシングル/差動インピーダンスを扱う場合、各変数の値は、ユーザー定義の Target Impedance と Target Tolerance 、および基板レイヤーの物理特性に基づいて自動計算されます。これらの自動計算値は、Properties パネルの Layer Stack Manager モードの編集ボックスに新しい値を入力することで調整できます。

-

Target Impedance – 達成したいインピーダンスを入力します。

-

Target Tolerance – 達成したい許容差を入力します。製造業者が実現可能な現実的な許容差については、基板製造業者に確認してください。

-

Transmission Line

-

Trace inverted – このオプションを有効にすると、Properties パネルに示されているようにトレースを反転します。このオプションは、Stackup タブがアクティブなときに表示される Copper Orientation オプションと同じで、銅がコアにラミネートされる方向を定義します。銅の向きは、その基材から銅がどちらの方向へ張り出すかを定義します。言い換えると、銅が上側からエッチングされるか下側からエッチングされるか、ということです。

-

Etch – Etch Factor は

= T/[(W1-W2)/2] で、トレースの総断面積を銅厚の二乗分だけ減少させます。製造プロセスで生じる Etch については、基板製造業者に確認してください。

計算から Etch を除外するには(つまり、トレース端に傾斜が形成されないと仮定するには)、値を 0 に設定します。

-

Width (W1) / (W2) – W1 は配線するトレース幅、W2 はそのトレースがエッチングされた後の上面幅で、Etch 係数が適用された値です。トレース幅には順方向/逆方向の計算機能があります。デフォルトでは、入力した Target Impedance に基づいて幅が計算されます(順方向計算)。この幅は、たとえば 5.978 のように製造業者が実現しにくい値になることがあり、その場合は 6.0 のようなより現実的な値が求められます。Width フィールドに 6.0 を入力し、キーボードで Enter を押すと、計算値(Impedance、Deviation など)が再計算されます。

ボタンはグレー表示(非アクティブ)になり、この時点で逆方向計算モードになります。ボタンをクリックして再びアクティブにすると順方向モードに戻り、Width (W1) は計算値に戻ります。この機能により、実際に製造可能な現実的な幅の選択肢を検討できます。W2 に値を手動入力すると、それに合わせて etch factor も更新されます。

ボタンはグレー表示(非アクティブ)になり、この時点で逆方向計算モードになります。ボタンをクリックして再びアクティブにすると順方向モードに戻り、Width (W1) は計算値に戻ります。この機能により、実際に製造可能な現実的な幅の選択肢を検討できます。W2 に値を手動入力すると、それに合わせて etch factor も更新されます。

-

Impedance – ソフトウェアは、基板を構成する材料(銅、コア、プリプレグ)の特性と、トレースの断面積(トレースの幅、厚さ、etch factor により決定)に基づいてインピーダンスを計算します。

-

Deviation – これは、希望した値(目標インピーダンス)と実際に得られた値(計算インピーダンス)の差を示す指標です。ソフトウェアは、基板を構成する材料(銅、コア、プリプレグ)の特性と、トレースの断面積(トレースの幅、厚さ、etch factor により決定)に基づいて、インピーダンス偏差(入力した材料と寸法に基づいて実際に得られる値)を計算します。

-

Delay – これは、信号が送信側から受信側へ伝搬するのにかかる時間です。

-

Inductance – インピーダンス計算機は Impedance 値を使用して単位長さあたりのインダクタンスを計算します。

-

Capacitance – インピーダンス計算機は Impedance 値を使用して単位長さあたりのキャパシタンスを計算します。

-

Board

-

Stack Symmetry – 有効にすると、中間の誘電体層を中心として対応するペアでレイヤーを追加します。有効化するとすぐに、中央の誘電体層を基準にレイヤースタックの対称性がチェックされます。中央の誘電体基準層から等距離にあるレイヤーペアのいずれかが同一でない場合、Stack is not symmetric dialog が開きます。

-

Library Compliance – 有効にすると、Material Library から選択された各レイヤーについて、現在のレイヤープロパティがライブラリ内のその材料定義の値と照合されます。

Stack Symmetry が有効な場合:

– レイヤープロパティに対して行った編集操作は、対称な対応レイヤーにも自動的に適用されます。 – レイヤーを追加すると、対応する対称パートナーレイヤーも自動的に追加されます。

-

Substack – この情報は現在選択されているサブスタック(レイヤー、誘電体、厚みなど)に関するものです。サブスタックを切り替えると、この情報もそれに応じて更新されます(現在選択されているサブスタックの情報)。

Substack 領域は、Features ドロップダウンで Rigid/Flex オプションが有効になっている場合にのみ使用できます。

-

Stack Name – 意味のあるサブスタック名を入力します。このフィールドは、X/Y スタックアップ領域にレイヤーサブスタックを割り当てる際に役立ちます。

-

Is Flex – サブスタックがフレックスの場合に有効にします。

-

Layers – レイヤーの総数。

-

Dielectrics – 誘電体の総数。

-

Conductive Thickness – 導体レイヤーの厚み。銅の信号レイヤーは導体レイヤーと呼ばれます。

-

Dielectric Thickness – 誘電体レイヤーの厚み。

-

Total Thickness – 基板全体の厚み。

-

Other

-

Roughness – 導体レイヤーの粗さを表示します。

-

Model Type – 表面粗さの影響を計算するための推奨モデルです(各種モデルの詳細については以下の記事を参照してください)。スタック内のすべての銅レイヤーに適用されます(サブスタックに適用されるべきでしょうか?)。

-

Surface Roughness – 表面粗さの値(基板製造業者から入手可能)。0~10µm の値を入力します。デフォルトは 0.1µm です。

-

Roughness Factor – 粗さの影響によって導体損失が最大でどの程度増加すると見込まれるかを表します。1~100 の値を入力します。デフォルトは 2 です。

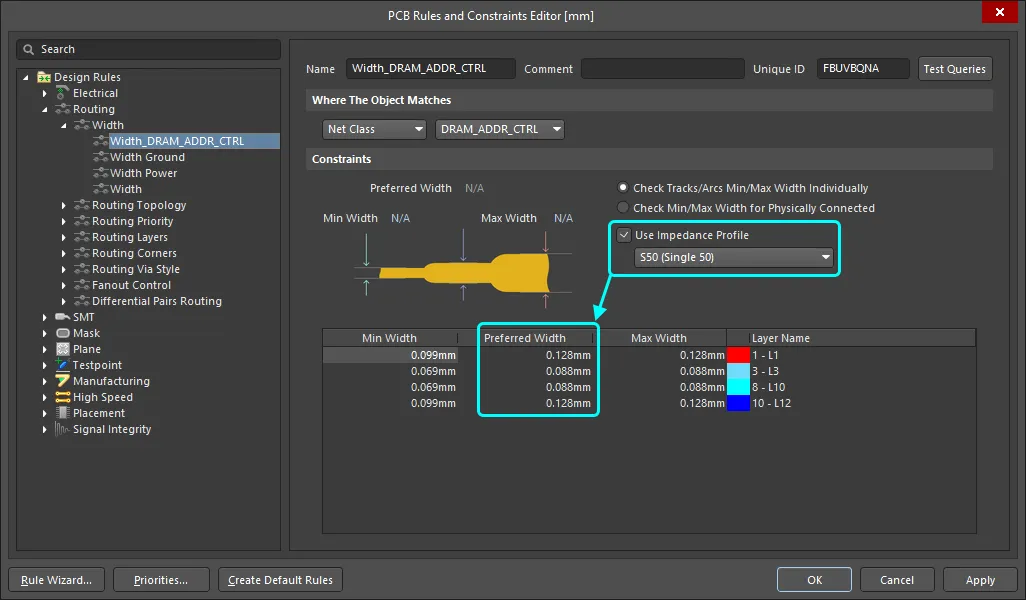

設計ルールの設定

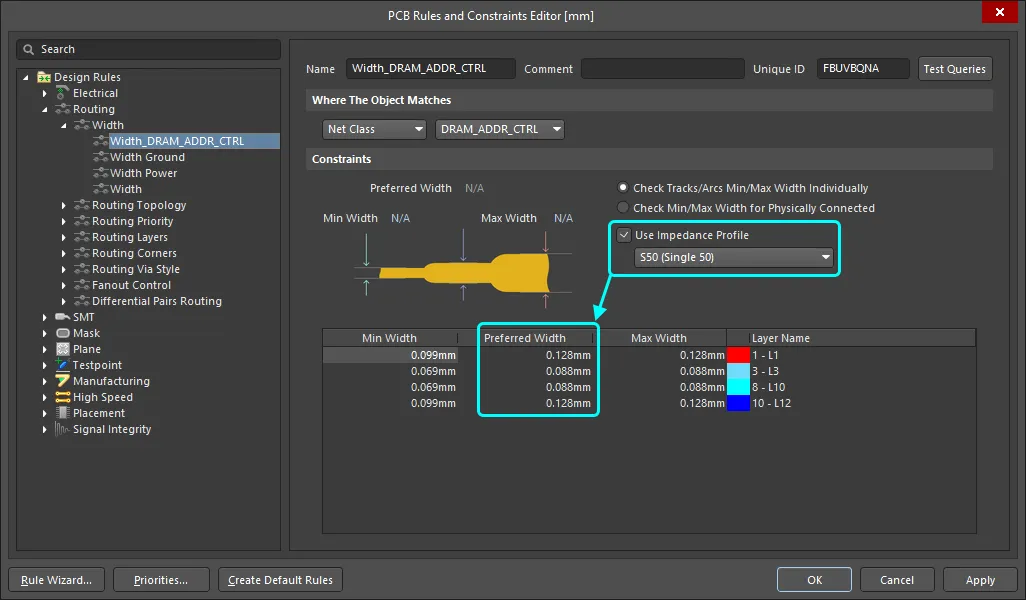

配線インピーダンスは、配線の幅と高さ、および周囲の誘電体材料の特性によって決まります。Layer Stack Manager で定義された材料特性に基づき、各インピーダンスプロファイルの作成時に必要な配線幅が計算されます。材料特性によっては、配線レイヤーが変わると幅も変化する場合があります。配線レイヤーの変更に応じて幅が変わるこの要件は、PCB Rules and Constraints Editor(Design » Rules)で設定された該当の配線設計ルールによって自動的に管理されます。

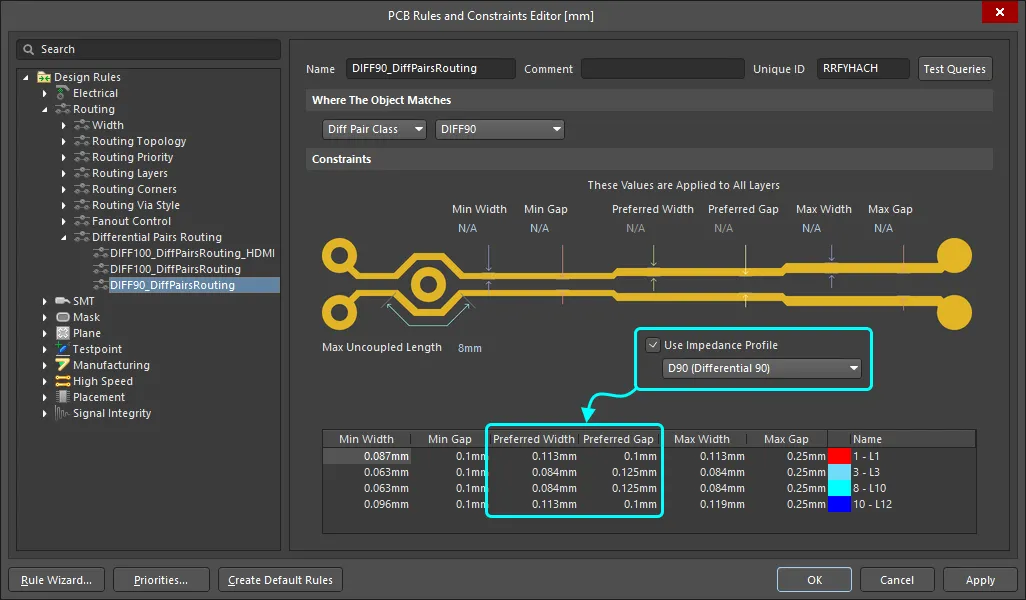

ほとんどの基板設計では、特定のネット群を制御インピーダンスで配線します。一般的な方法は、これらのネットを含むネットクラスまたは差動ペアクラスを作成し、次に以下の画像に示すように、そのクラスを対象とする配線ルールを作成することです。

通常、Min、Max、および Preferred Widths は手動で定義します。上部の制約設定で全レイヤーに適用することも、レイヤーグリッド内で各レイヤーごとに個別に設定することもできます。制御インピーダンス配線では、代わりに Use Impedance Profile オプションを有効にし、ドロップダウンから必要な Impedance Profile を選択します。これを行うと、ルールの Constraints 領域が変化します。最初に気付くのは、使用可能なレイヤー領域に基板上のすべての信号レイヤーが表示されなくなることです。代わりに、選択した Impedance Profile で有効になっているレイヤーのみが表示されます。Preferred Width の値(および差動ペアギャップ)は、各レイヤーに対して計算された幅(およびギャップ)を反映するように更新されます。これらの Preferred 値は編集できませんが、Min と Max の値は編集できます。これらには適切な小さい値/大きい値を設定してください。その後、通常どおりインタラクティブにネットを配線できます。

-

Impedance Profile が適用されると、対象ネットはそれらのレイヤー上でのみ配線されると想定されるため、他のすべての信号レイヤーは設計ルール制約から除外されます。

-

Preferred Width は Impedance Profile で計算された値に固定されますが、Min Width と Max Width の値は引き続きユーザー定義が可能です。

-

寸法がメートル法に設定されている場合、丸め誤差による誤った設計ルール違反を避けるために、Min Width と Max Width の設定をわずかに小さく/大きくする必要がある場合があります。

配線幅設計ルール

単一ネットでは、配線幅は Routing Width 設計ルールによって定義されます。

Impedance Profile を使用するように選択すると、使用可能なレイヤーと Preferred Width は選択したプロファイルによって制御されます。

Impedance Profile を使用するように選択すると、使用可能なレイヤーと Preferred Width は選択したプロファイルによって制御されます。

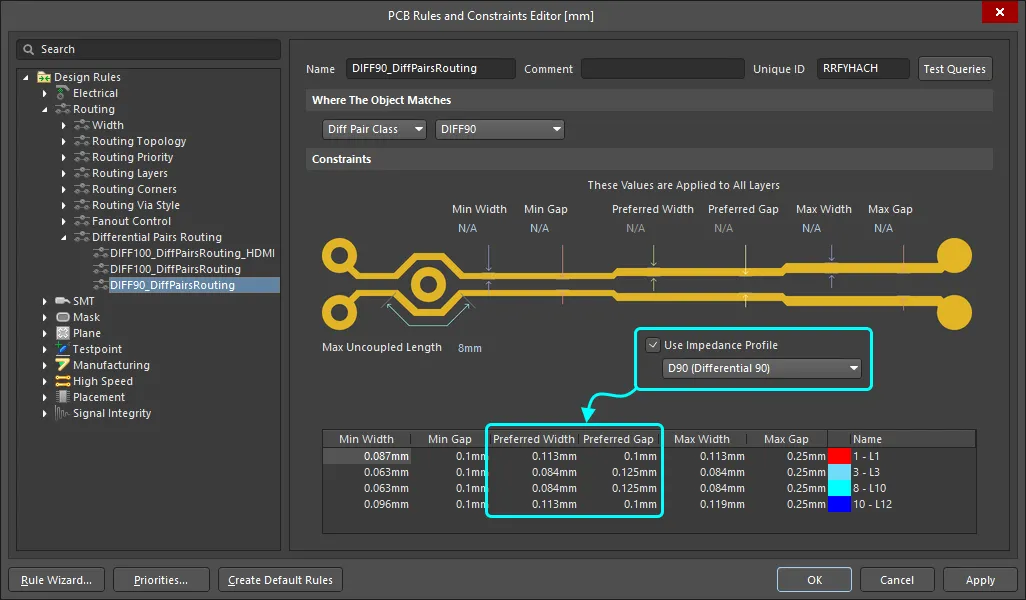

差動ペア配線設計ルール

差動ペアの配線は、Differential Pair Routing 設計ルールによって制御されます。

差動ペアでは、使用可能なレイヤー、Preferred Width、および Preferred Gap は選択したプロファイルによって制御されます。

差動ペアでは、使用可能なレイヤー、Preferred Width、および Preferred Gap は選択したプロファイルによって制御されます。

► Differential Pair Routing について詳しく見る

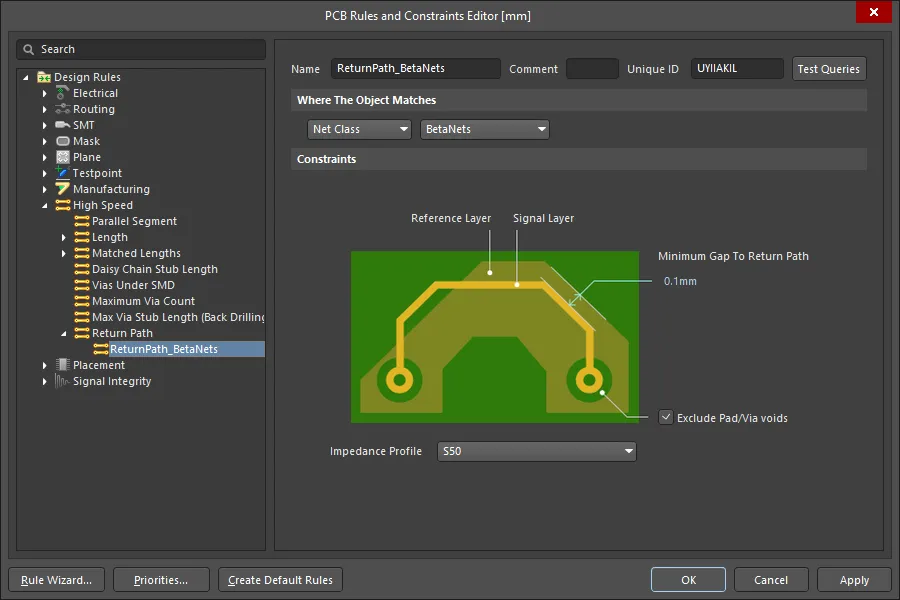

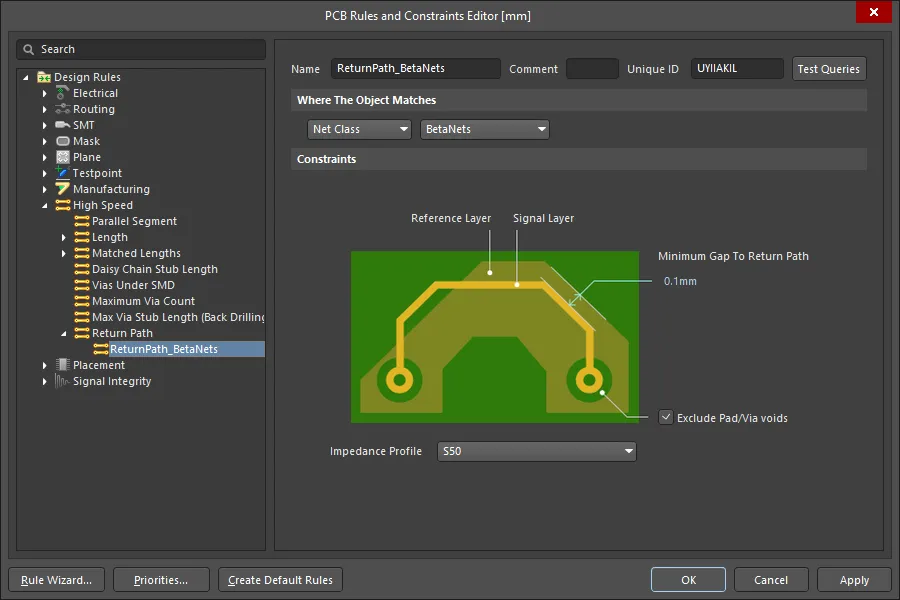

リターンパス設計ルール

リターンパス内の切れ目やくびれは、Return Path design rule によって検出できます。Return Path 設計ルールは、ルールの対象となる信号の上または下にある指定参照レイヤー上に、連続した信号リターンパスが存在するかを確認します。リターンパスは、参照信号レイヤーまたはプレーンレイヤー上に配置されたフィル、リージョン、およびポリゴン注入によって作成できます。

リターンパスレイヤーは、Return Path 設計ルールで選択された Impedance Profile に定義されている参照レイヤーです。これらのレイヤーは、指定された Minimum Gap(信号エッジを超える幅)が信号経路に沿って存在することを確認するためにチェックされます。High Speed ルールカテゴリで新しい Return Path 設計ルールを追加します。

リターンパスレイヤーは選択した Impedance Profile で定義され、パス幅(信号エッジを超える幅)は Minimum Gap で定義されます。

リターンパスレイヤーは選択した Impedance Profile で定義され、パス幅(信号エッジを超える幅)は Minimum Gap で定義されます。

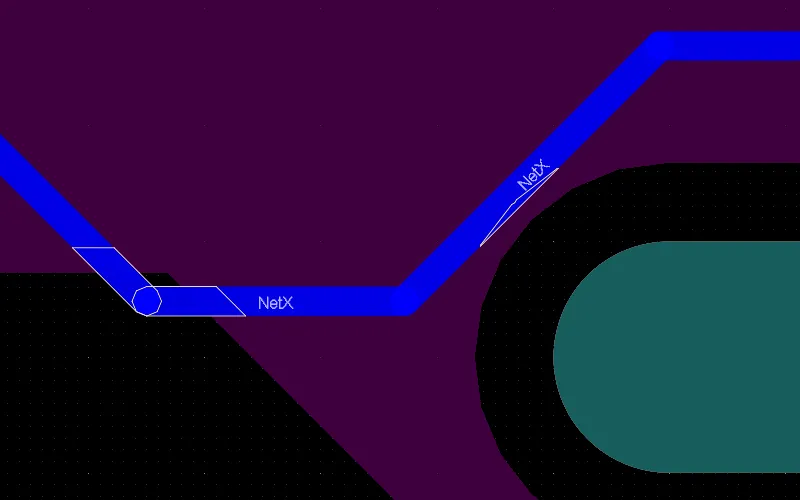

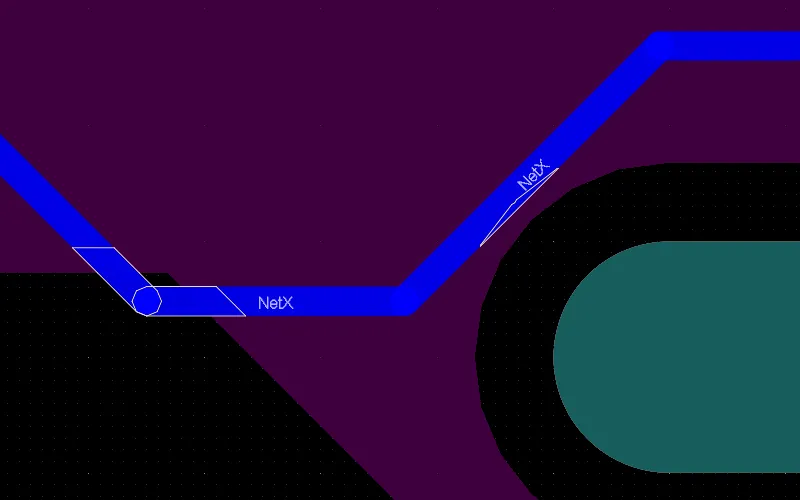

以下の画像は、信号 NetX に対して、Minimum Gap の設定が 0.1mm のときに検出されたリターンパスエラーを示しています。Preferences ダイアログ で DRC Violation Display Style を、Violation Overlay ではなく Violation Details を表示するように設定すると(show image![]() )、Return Path エラーの位置を見つけやすくなります。これにより、違反しているオブジェクト全体ではなく、ルールに失敗した正確な位置が強調表示されます。

)、Return Path エラーの位置を見つけやすくなります。これにより、違反しているオブジェクト全体ではなく、ルールに失敗した正確な位置が強調表示されます。

上の画像の斜めトラックセグメントで強調表示されている部分のような小さなエラーを検出しないようにするには、Advanced Settings dialog で PCB.Rules.ReturnPathIgnoreArea 設定を構成します。デフォルトでは、< 10 sq mils の領域は無視されます。

► High Speed Design in Altium Designer について詳しく見る

必要なインピーダンスでネットを配線する

基板を配線してレイヤーを変更すると、ソフトウェアは指定されたインピーダンスを実現するために必要なサイズにトラック幅を自動調整します。このインタラクティブな制御インピーダンス配線により、制御インピーダンス PCB の設計作業が大幅に簡素化されます。

Layer Stack Manager に統合された Simbeor インピーダンス計算機も、Signal Integrity Analysis エンジンも、計算にビアを含みません。Defining the Via Types について詳しく学んでください。

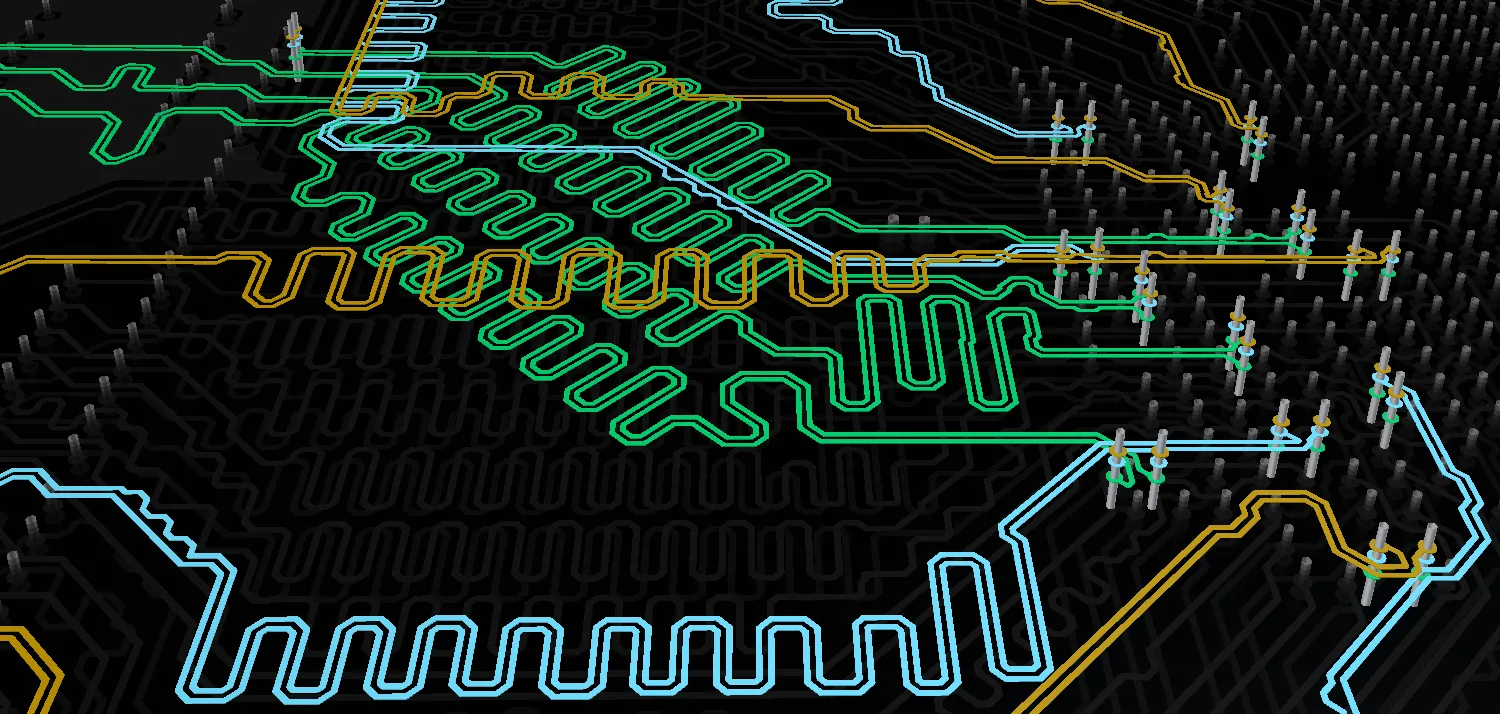

配線長のチューニング

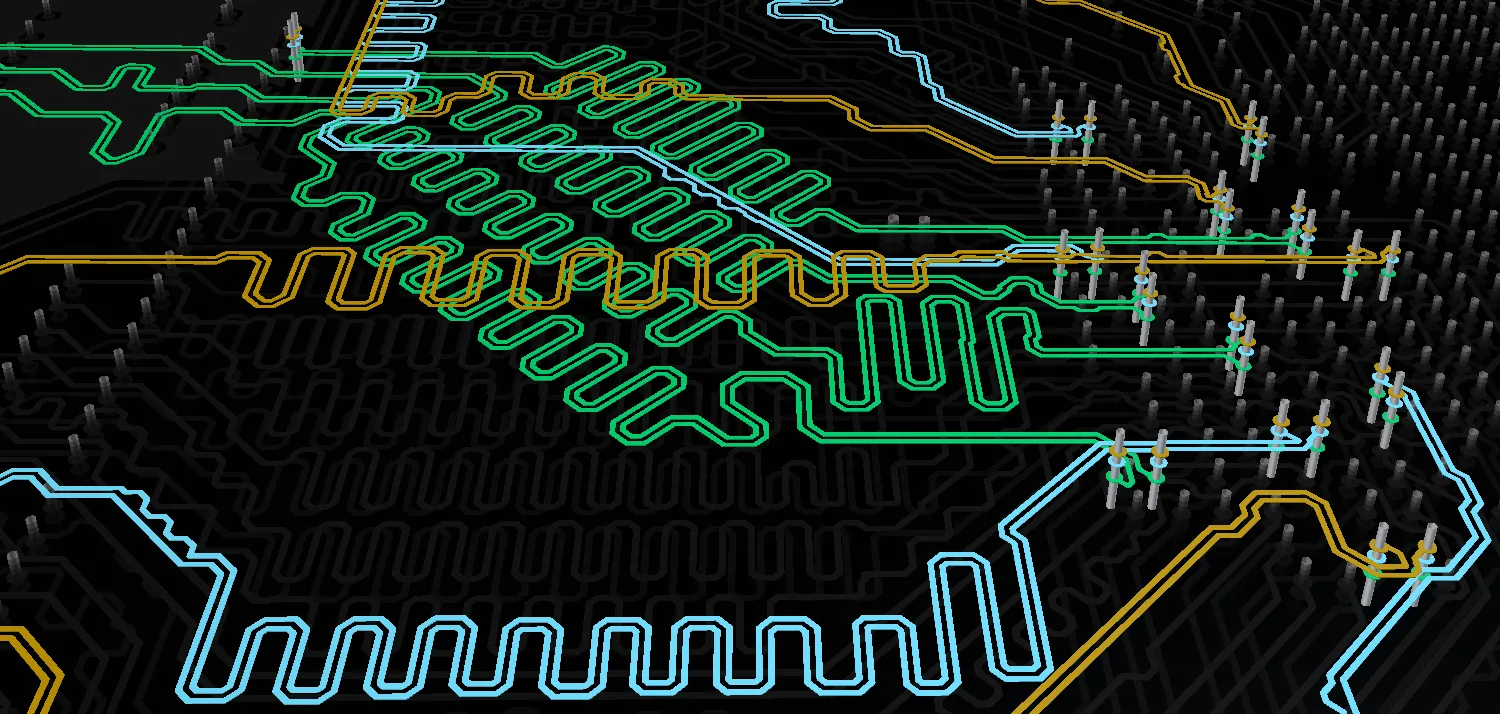

高速設計の配線における中核的な課題のうち 2 つは、配線のインピーダンスを制御することと、重要なネットの長さを一致させることです。インピーダンス制御配線により、出力ピンから出た信号が対象の入力ピンで正しく受信されることが保証されます。配線長を一致させることで、タイミングが重要な信号が対象ピンに同時に到達するようにできます。配線長のチューニングと一致は、差動ペア配線においても不可欠な要素です。

差動ペアの長さを一致させるために、配線にアコーディオンパターンが追加されています。

差動ペアの長さを一致させるために、配線にアコーディオンパターンが追加されています。

Interactive Length Tuning および Interactive Diff Pair Length Tuning コマンド(Route メニュー)は、設計内の利用可能なスペース、ルール、および障害物に応じて可変振幅の波形パターン(アコーディオン)を挿入できるようにすることで、ネットまたは差動ペアの長さを最適化および制御する動的な手段を提供します。

► Length Tuning について詳しく見る

配線済み基板のシグナルインテグリティをテストする

設計キャプチャ時に想定した配線長と配線インピーダンスを使用してネットをテストしたのと同様に、配線完了後は、潜在的なインピーダンス不整合や反射の問題を確認するために、基板上でこのプロセスを再度実行する必要があります。PCB エディターの Tools メニューから Signal Integrity コマンドを起動します。PCB はプロジェクトの一部であるため、Layer Stack Manager で定義された材料特性と寸法、および基板上の実際の配線幅が、シグナルインテグリティテストで使用されるインピーダンスの計算に使用されます。

指定インピーダンスを達成する

正しいインピーダンスを達成するために行う反復的な寸法調整プロセスに加えて、実際に製造された PCB で最終的に得られるインピーダンスに影響を与える要因が他にもあります。これには、PCB に使用される誘電体材料の一貫性と安定性、さらにエッチング工程の一貫性と品質が含まれます。制御インピーダンス PCB が必要な場合は、PCB 製造業者と相談する必要があります。製造業者によっては、希望するスタックアップを提供すれば、トラック形状について助言してくれる場合があります。また、多くの製造業者は、製造する各パネルにインピーダンステストクーポンを含めることも可能で、これを使用して基板上で実際に達成されたインピーダンスを測定できます。

追加の参考資料とリソース

この記事では、シグナルインテグリティと制御インピーダンス PCB 設計のトピックを紹介しています。以下のリンクを使用して、さらに詳しく学び、業界で認められた専門家が作成したリソースにアクセスしてください。

設計キャプチャ中に、設計に潜在的なシグナルインテグリティ問題がないかをテストします。

設計キャプチャ中に、設計に潜在的なシグナルインテグリティ問題がないかをテストします。

![]() ボタンをクリックするか、ネット名をダブルクリックすると、そのネットがパネル右側のNetフィールドに転送され、次のような詳細解析を実行できます。

ボタンをクリックするか、ネット名をダブルクリックすると、そのネットがパネル右側のNetフィールドに転送され、次のような詳細解析を実行できます。

左のグラフは、信号インテグリティ上の問題が生じる可能性のあるネットの反射解析を示しています。 右のグラフは、同じネットに約40オームの理論上の直列終端抵抗を追加したものです。

左のグラフは、信号インテグリティ上の問題が生じる可能性のあるネットの反射解析を示しています。 右のグラフは、同じネットに約40オームの理論上の直列終端抵抗を追加したものです。

トップレイヤー上で配線される単一ネット用に定義された 50Ω のインピーダンスプロファイル。画像にカーソルを合わせると、L3 層に対する同じプロファイルの設定が表示されます(画像提供: FEDEVEL Open Source、www.fedevel.com)。

トップレイヤー上で配線される単一ネット用に定義された 50Ω のインピーダンスプロファイル。画像にカーソルを合わせると、L3 層に対する同じプロファイルの設定が表示されます(画像提供: FEDEVEL Open Source、www.fedevel.com)。

ボタンをクリックします。

ボタンをクリックします。

)をクリックして開きます。

)をクリックして開きます。

トップレイヤー上で配線される個別ネット向けに定義された 50Ω のインピーダンスプロファイル。画像の上にカーソルを置くと、レイヤー L3 に対する同じプロファイルの設定が表示されます。

トップレイヤー上で配線される個別ネット向けに定義された 50Ω のインピーダンスプロファイル。画像の上にカーソルを置くと、レイヤー L3 に対する同じプロファイルの設定が表示されます。

ボタン(すでにプロファイルが定義されている場合は

ボタン(すでにプロファイルが定義されている場合は  ボタン)をクリックします。

ボタン)をクリックします。

![]() アイコンは計算対象の変数を示します。

アイコンは計算対象の変数を示します。

50Ω の目標インピーダンスでは、順方向計算により幅(W1)は 94.6µm になります。右側の画像は、幅(W1)を 95µm に設定したときの逆方向計算を示しています。

50Ω の目標インピーダンスでは、順方向計算により幅(W1)は 94.6µm になります。右側の画像は、幅(W1)を 95µm に設定したときの逆方向計算を示しています。

![]() ボタンをクリックすると、計算機は順方向計算モードに戻ります。Width (W2) に新しい値を入力すると、Etch の値が変化します。

ボタンをクリックすると、計算機は順方向計算モードに戻ります。Width (W2) に新しい値を入力すると、Etch の値が変化します。

![]() ボタンをクリックして、計算対象の変数として Trace Width または Trace Gap のいずれかを指定します。もう一方の変数を編集して Target Impedance を変更するか、あるいは Target Impedance を変更してもう一方の変数への影響を確認します。

ボタンをクリックして、計算対象の変数として Trace Width または Trace Gap のいずれかを指定します。もう一方の変数を編集して Target Impedance を変更するか、あるいは Target Impedance を変更してもう一方の変数への影響を確認します。

? の上にカーソルを置くと、式が表示されます。

? の上にカーソルを置くと、式が表示されます。

Trace Inverted チェックボックスをクリックすると、Copper Orientation を Above から Below に切り替えられます。

Trace Inverted チェックボックスをクリックすると、Copper Orientation を Above から Below に切り替えられます。

について詳しく見る

について詳しく見る

AI で翻訳

AI で翻訳