Setting Up & Running a DRC

Altium Essentials: PCB Design Rule Checks

This content is part of the official Altium Professional Training Program. For full courses, materials and certification, visit Altium Training.

Настройка DRC

Настройка проверки правил проектирования выполняется в диалоговом окне Design Rule Checker, доступ к которому из документа PCB осуществляется командой Tools » Design Rule Check.

Диалоговое окно Design Rule Checker показывает настройки по умолчанию, при которых некоторые проверки Online DRC отключены для повышения производительности редактора PCB. Используйте соответствующие параметры, чтобы включить тип правила проектирования для проверки в составе Online DRC и/или Batch DRC.

На панели дерева папок в левой части диалогового окна все категории правил проектирования, типы правил которых можно проверять, перечислены в папке Rules To Check. Щелкните эту папку верхнего уровня, чтобы вывести справа в диалоговом окне все типы правил, доступные для проверки. Либо щелкните конкретную категорию под этой папкой, чтобы вывести только те типы правил проектирования, которые относятся к данной категории. Используйте диалоговое окно, чтобы включать/отключать проверку Online (где доступно) и/или в пакетном режиме для каждого типа правила, который требуется проверять.

Использование Online DRC

Проверка правил проектирования Online выполняется в фоновом режиме, в реальном времени, отмечая и/или автоматически предотвращая нарушения правил проектирования. Это особенно полезно при интерактивной трассировке платы, поскольку позволяет сразу подсвечивать нарушения зазоров, ширины и параллельных сегментов. Чтобы правило подпадало под Online DRC, должны выполняться следующие три требования:

-

Правило должно быть включено. Это можно сделать либо в диалоговом окне PCB Rules and Constraints Editor dialog, убедившись, что для правила установлен параметр Enabled , либо на панели PCB Rules and Violations panel, убедившись, что для правила установлен параметр On .

Убедитесь, что правила проектирования, которые должны контролироваться Online DRC, действительно включены для использования в проекте.

Убедитесь, что правила проектирования, которые должны контролироваться Online DRC, действительно включены для использования в проекте.

-

Тип правила должен быть включен для онлайн-проверки в диалоговом окне Design Rule Checker.

-

Функция Online DRC должна быть включена. Для этого включите параметр Online DRC на странице PCB Editor - General page диалогового окна Preferences.

Если будут обнаружены объекты, нарушающие применимое правило проектирования, включенное для онлайн-проверки, они будут подсвечены в рабочем пространстве проекта в соответствии с заданными параметрами отображения нарушений.

Использование Batch DRC

Настоятельно рекомендуется всегда выполнять пакетную проверку правил проектирования перед формированием финальных производственных файлов. Online DRC обнаруживает только новые нарушения — те, которые возникают после включения этой функции, — тогда как Batch DRC позволяет вручную запускать проверку в любой момент процесса проектирования платы. Поэтому, хотя хорошие разработчики знают ценность Online DRC, они также знают, что проектирование платы должно начинаться и заканчиваться Batch DRC.

При необходимости включите типы правил для пакетной проверки в диалоговом окне Design Rule Checker (см. раздел Настройка DRC). При запуске Batch DRC доступны различные дополнительные параметры, включая возможность создания файла отчета. Доступ к этим параметрам осуществляется щелчком по папке Report Options на панели дерева папок диалогового окна. Два ключевых параметра (выделены на следующем изображении):

-

Create Report File - включите этот параметр, чтобы после выполнения Batch DRC для платы был создан отчет. Включите подпараметр Report PCB Health Issues, чтобы включить в создаваемый отчет проблемы, обнаруженные средством PCB Health Check Monitor.

Отчет имеет формат HTML и будет называться

Design Rule Check - <PCBDocumentName>.html. После завершения процесса Batch DRC он автоматически откроется как активный документ. -

Create Violations - включите этот параметр, чтобы нарушения подсвечивались в рабочем пространстве проекта в соответствии с заданными параметрами отображения нарушений. Этот параметр также необходим, чтобы нарушения отображались в области Violations панели PCB Rules And Violations panel.

Доступны следующие дополнительные параметры:

-

Sub-Net Details – если было определено правило Un-Routed Net, включите этот параметр, чтобы включать сведения о подсетях в отчет DRC.

-

Verify Shorting Copper – включите этот параметр, чтобы проверить целостность закорачивающей меди в любых компонентах Net Tie, используемых в проекте. Эта проверка ищет любую неподключенную медь в компоненте (что указывает на то, что площадка неправильно закорачивает другую площадку или площадки).

-

Report Drilled SMT Pads – включите этот параметр, чтобы включать в отчет DRC любые SMT-площадки (Surface Mount Technology), которые были ошибочно просверлены.

-

Report Multilayer Pads with 0 size Hole – включите этот параметр, чтобы включать любые недопустимые многослойные площадки, найденные в проекте. Недопустимая многослойная площадка — это площадка с нулевым размером отверстия, которая в противном случае считалась бы SMT-площадкой.

-

Stop when n violations found – используйте это поле, чтобы определить максимальное количество нарушений, которое может быть обнаружено до остановки процесса пакетной DRC-проверки (по умолчанию =

500). Ограничение количества сообщаемых нарушений — одна из ключевых стратегий, позволяющих сохранить управляемость процесса проверки. -

Report Broken Planes – включите этот параметр, чтобы пакетная проверка правил выполняла поиск разорванных полигонов и сообщала о них. Разорванные полигоны возникают, когда область полигона, имеющая связь с цепью, становится электрически отсоединенной от остальной части полигона. Пример такой ситуации — разъем, размещенный поперек разделенного полигона, но не подключенный к нему. Пустоты вокруг выводов объединяются и полностью прорезают медь полигона, фактически разделяя его на две части.

-

Report Dead Copper larger than – включите этот параметр, чтобы пакетная проверка правил выполняла поиск и сообщала об изолированных медных областях, площадь которых превышает указанное значение. Под изолированной медью понимаются участки меди, не имеющие связи с цепью и при этом электрически отсоединенные от исходного родительского полигона. Пример такой ситуации — разъем (не подключенный к полигону) с близко расположенными выводами, где пустоты вокруг выводов объединяются и изолируют области меди полигона от остальной части полигона. Используйте связанное поле, чтобы указать значение максимально допустимой площади изолированной меди; превышение этого значения считается нарушением правила (по умолчанию =

100 sq. mils). -

Report Starved Thermals with less than n% available copper – включите этот параметр, чтобы пакетная проверка правил выполняла поиск и сообщала о «ослабленных» тепловых соединениях, превышающих указанный процент. Тепловые соединения — это соединения с полигоном, имеющие вокруг себя тепловые разгрузочные «вырезы» для уменьшения теплопроводности к меди полигона. Тепловое соединение может стать «ослабленным», когда площадь поверхности медных спиц, соединяющих его с полигоном, уменьшается из-за пустот. Этот параметр также проверяет площадь поверхности самого теплового соединения (а не только спиц) на наличие пустот, заходящих в область теплового соединения. Используйте связанное поле, чтобы указать значение минимально допустимого процента соединяющей меди, который должен оставаться; значение ниже этого считается нарушением правила (по умолчанию =

50%). -

Run Design Rule Check – нажмите эту кнопку, чтобы выполнить Batch DRC в соответствии с правилами, включенными для пакетной проверки, и дополнительными параметрами, заданными для этого типа проверки.

DRC-проверка в пакетном режиме запускается нажатием кнопки Run Design Rule Check в левом нижнем углу диалогового окна. Если вы выбрали эту возможность, будет создан отчет DRC и автоматически открыт (если это настроено) как активный документ в главном окне проекта. В отчете перечислены все правила, которые были проверены, как указано в диалоговом окне Design Rule Checker . Правила, отсутствующие в проекте, не проверяются.

Отчеты DRC

Включение параметра Create Report File в диалоговом окне Design Rule Checker dialog приведет к созданию отчета DRC при выполнении Batch DRC. Параметры, доступные на странице PCB Editor - Reports page диалогового окна Preferences, позволяют задать формат отчета и определить, будет ли отчет автоматически отображаться после создания.

Создать отчет DRC как часть процесса Batch DRC.

Поддерживаются следующие форматы:

-

TXT – создается файл Design Rule Check - <PCBDocumentName>.drc.

-

HTML – создается файл Design Rule Check - <PCBDocumentName>.html.

-

XML – создается файл <PCBDocumentName>.xml.

В отчете перечислены все правила, которые были проверены в ходе пакетной проверки, как указано в диалоговом окне Design Rule Checker. Каждое найденное нарушение приводится с полными сведениями обо всей справочной информации, такой как слой, имя цепи, позиционное обозначение компонента и номер площадки, а также местоположение объекта.

Параметры отображения нарушений

Проверка проекта на соответствие заданным правилам проектирования — это одно, но что происходит, когда одно или несколько из этих правил нарушаются? Независимо от того, выполняется ли Online DRC в процессе проектирования или вручную запускается Batch DRC, должно быть какое-то визуальное указание на то, где возникают такие нарушения правил. PCB Editor включает мощные параметры отображения нарушений, позволяющие ясно и наглядно показывать места их возникновения.

Пользовательская графика нарушений

Большинство правил проектирования, которые могут быть включены в Online и/или Batch проверку правил проектирования, имеют связанную пользовательскую графику нарушений, отображаемую в рабочем пространстве проекта при нарушении конкретного правила. Эта графика обеспечивает более чистое визуальное представление DRC. Когда нарушается определенное правило проектирования, соответствующая пользовательская графика нарушений (где применимо) отображается только на слое(ях), задействованном(ых) в этом нарушении.

В некоторых случаях графика показывает не только место возникновения нарушения, но и его причину — отображая значение ограничения, заданное для правила, и указывая, насколько проблемный примитив(ы) находится ниже или выше этого значения.

Пример, иллюстрирующий пользовательскую графику, используемую для нарушений правил ширины и минимального кольцевого пояска.

Пример, иллюстрирующий пользовательскую графику, используемую для нарушений правил ширины и минимального кольцевого пояска.

Другая графика, включая ту, что используется для представления нарушений правил Net Antennae, Short-Circuit, Un-Routed Net, Room Definition, Layer Pairs и Vias Under SMD, будет просто графическим обозначением, поскольку для отображения нет определяемого значения ограничения.

Дополнительные примеры пользовательской графики нарушений. Слева направо: нарушение Net Antennae; нарушение Short-Circuit; нарушение Un-Routed Net.

Дополнительные примеры пользовательской графики нарушений. Слева направо: нарушение Net Antennae; нарушение Short-Circuit; нарушение Un-Routed Net.

Наложение нарушений

В дополнение к пользовательской графике нарушений доступно для настройки и использования «наложение» нарушений. Наложение рисуется поверх примитивов проекта. Вы можете выбрать, какой шаблон отображать на примитивах, из набора стилей.

Используйте наложение нарушений как альтернативу пользовательской графике нарушений при отображении нарушений DRC.

Используйте наложение нарушений как альтернативу пользовательской графике нарушений при отображении нарушений DRC.

Полезным может оказаться использование комбинации этих двух типов отображения нарушений, поскольку это дает «грубую» и «точную» индикацию нарушений. При уменьшенном масштабе наложение нарушений может указать, где существует нарушение, а затем можно увеличить масштаб, чтобы увидеть детали, предоставляемые соответствующей пользовательской графикой нарушения.

Настройка параметров отображения нарушений

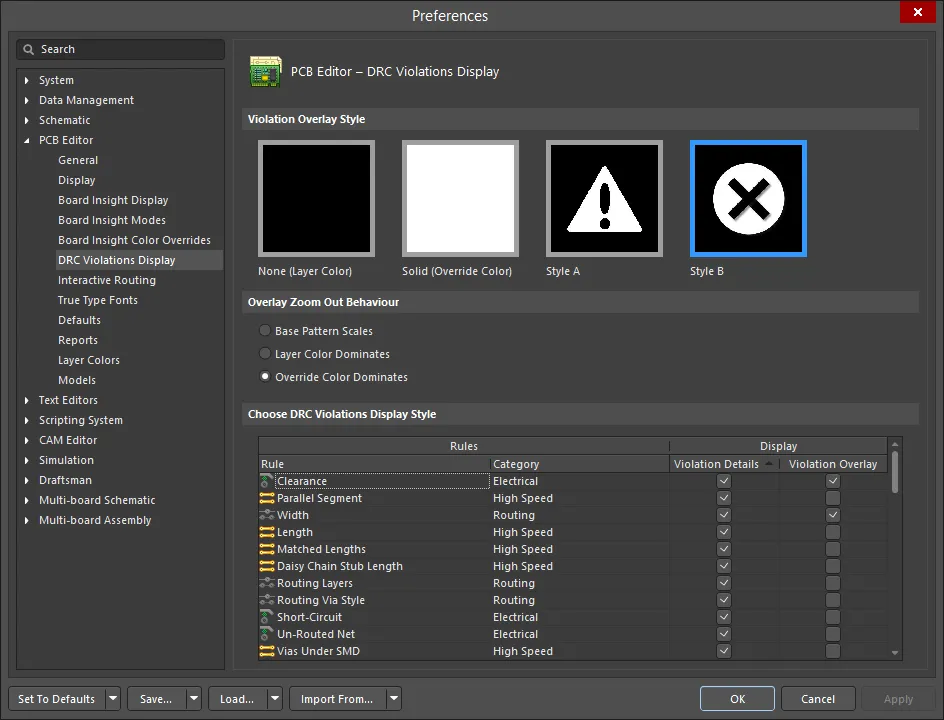

Управление тем, как отображаются нарушения DRC — с использованием пользовательской графики нарушений и/или заданного наложения нарушений — задается на странице PCB Editor - DRC Violations Display page диалогового окна Preferences.

Настройте отображение нарушений DRC в рабочем пространстве проекта — с использованием пользовательской графики и/или заданного наложения нарушений — в составе параметров программы.

Доступные параметры позволяют:

-

Выбрать стиль используемого наложения нарушений с помощью Violation Overlay Style — маркеры ошибок могут отображаться одним из следующих четырех способов. Щелкните, чтобы выбрать предпочтительный стиль:

-

None (Layer Color) — маркеры ошибок отображаются цветом слоя и поэтому не видны.

-

Solid (Override Color) — маркеры ошибок отображаются цветом слоя Error Marker.

-

Style A — маркеры ошибок отображаются в виде предупреждающего треугольника.

-

Style B — маркеры ошибок отображаются в виде точки с крестом внутри.

-

-

Определить поведение отображения наложения нарушений при уменьшении масштаба с помощью Overlay Zoom Out Behavior — при уменьшении масштаба маркеры ошибок будут вести себя следующим образом:

-

Base Pattern Scales — маркеры ошибок масштабируются независимо от уровня увеличения (тип маркера определяется выбранным выше стилем Violation Overlay Style).

-

Layer Color Dominates — при уменьшении масштаба маркеры ошибок превращаются в сплошную цветную область цвета слоя.

-

Override Color Dominates — при уменьшении масштаба маркеры ошибок превращаются в сплошную цветную область цвета слоя Error Marker.

-

-

Выбрать стиль отображения, используемый для каждого правила отдельно, в области Choose DRC Violations Display Style. Включение параметра Violation Details для типа правил приведет к использованию соответствующей пользовательской графики нарушений для отображения нарушений DRC этого правила. Включение параметра Violation Overlay приведет к отображению нарушений с использованием заданного стиля наложения. По умолчанию стиль отображения Violation Details включен для всех типов правил, а отображение Violation Overlay Style включено только для правил Clearance, Width и Component Clearance.

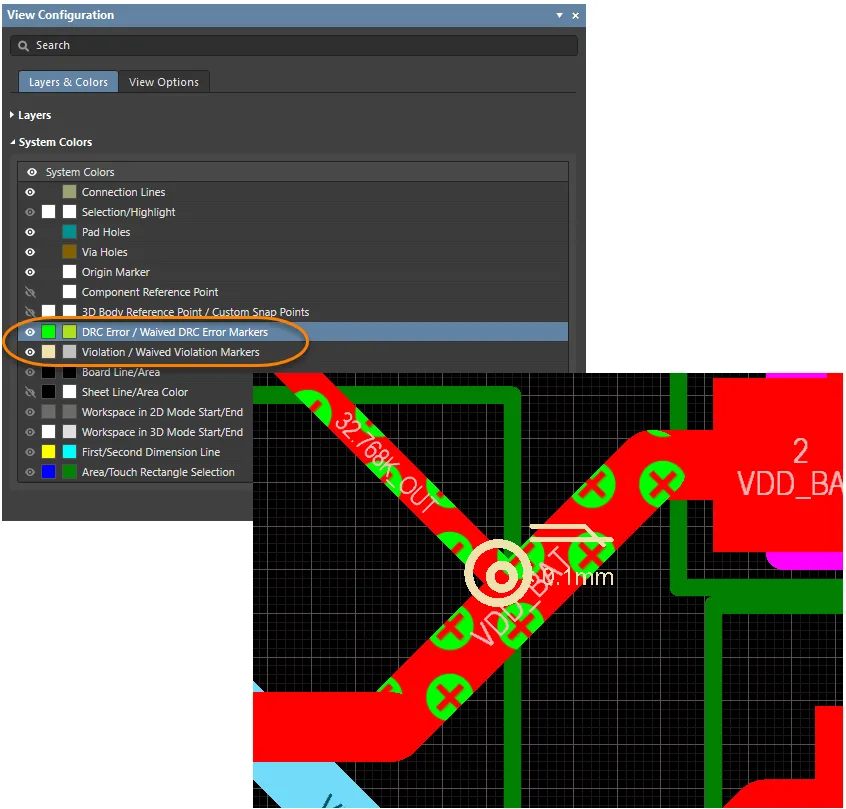

Настройка цветов нарушений

Для большей гибкости при отображении нарушений правил в рабочем пространстве проекта два типа отображения нарушений — детали нарушения (пользовательская графика нарушений) и наложение нарушений — имеют отдельные связанные системные цвета. Это позволяет различать их с помощью разных, отчетливых цветов. Назначение цветов выполняется в разделе System Colors на вкладке Layers & Colors панели View Configuration panel:

-

Violation Details — использует системный цвет Violation Markers (для отклоненных нарушений, использующих этот стиль отображения, используется системный цвет Waived Violation Markers).

-

Violation Overlay — использует системный цвет DRC Error Markers (для отклоненных нарушений, использующих этот стиль отображения, используется системный цвет Waived DRC Error Markers).

Задайте разные цвета для двух типов отображения нарушений и при необходимости включайте/отключайте их отображение.

Задайте разные цвета для двух типов отображения нарушений и при необходимости включайте/отключайте их отображение.

Локализовано с помощью ИИ

Локализовано с помощью ИИ